Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

April 1984 Revised March 2000

# DM74AS169A Synchronous 4-Bit Binary Up/Down Counter

## **General Description**

These synchronous presettable counters feature an internal carry look ahead for cascading in high speed counting applications. The DM74AS169 is a 4-bit binary up/down counter. The carry output is decoded to prevent spikes during normal mode of counting operation. Synchronous operation is provided so that outputs change coincident with each other when so instructed by count enable inputs and internal gating. This mode of operation eliminates the output counting spikes which are normally associated with asynchronous (ripple clock) counters. A buffered clock input triggers the four flip-flops on the rising (positive going) edge of clock input waveform.

These counters are fully programmable; that is, the outputs may each be preset either HIGH or LOW. The load input circuitry allows loading with carry-enable output of cascaded counters. As loading is synchronous, setting up a LOW level at the load input disables the counter and causes the outputs to agree with the data inputs after the next clock pulse.

The carry look-ahead circuitry permits cascading counters for n-bit synchronous applications without additional gating. Both count enable inputs  $(\overline{P}$  and  $\overline{T})$  must be LOW to count. The direction of the count is determined by the level of the up/down input. When the input is HIGH, the counter counts UP; when LOW, it counts DOWN. Input T is fed forward to enable the carry outputs. The carry output thus enabled will produce a LOW level output pulse with a duration approximately equal to the HIGH portion of the QA output when counting UP, and approximately equal to the LOW portion of the QA output when counting DOWN. This LOW level overflow carry pulse can be used to enable successively cascaded stages. Transitions at the enable  $\overline{P}$  or  $\overline{T}$  inputs are allowed regardless of the level of the clock input.

The control functions for these counters are fully synchronous. Changes at control inputs (enable  $\overline{P}$ , enable  $\overline{T}$ , load, up/down) which modify the operating mode have no effect until clocking occurs. The function of the counter (whether enabled, disabled, loading or counting) will be dictated solely by the conditions meeting the stable setup and hold

### **Features**

- Switching Specifications at 50 pF

- $\blacksquare$  Switching Specifications guaranteed over full temperature and  $V_{CC}$  range

- Advanced oxide-isolated, ion-implanted Schottky TTL process

- Functionally and pin-for-pin compatible with Schottky and low power Schottky TTL counterpart

- Improved AC performance over Schottky and low power Schottky counterparts

- Synchronously programmable

- Internal look ahead for fast counting

- Carry output for n-bit cascading

- Synchronous counting

- Load control line

- ESD inputs

## **Ordering Code:**

| Order Number | Package Number | Package Description                                                         |  |  |  |

|--------------|----------------|-----------------------------------------------------------------------------|--|--|--|

| DM74AS169AM  | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |  |  |  |

| DM74AS169AN  | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |  |  |  |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

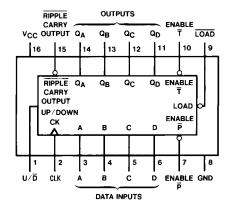

# **Connection Diagram**

# Logic Diagram

#

## **Absolute Maximum Ratings**(Note 1)

Supply Voltage 7V Input Voltage 7V

Operating Free Air Temperature Range 0°C to +70°C -65°C to +150°C

Storage Temperature Range

Typical  $\theta_{JA}$

N Package 71.5°C/W M Package 101.0°C/W

Note 1: The "Absolute Maximum Ratings" are those values beyond which Note 1: Ine "Absolute Maximum Hatings" are mose values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol            | Parameter                        |                  | Min | Nom | Max | Units |

|-------------------|----------------------------------|------------------|-----|-----|-----|-------|

| V <sub>CC</sub>   | Supply Voltage                   |                  | 4.5 | 5   | 5.5 | V     |

| V <sub>IH</sub>   | HIGH Level Input Voltage         |                  | 2   |     |     | V     |

| V <sub>IL</sub>   | LOW Level Input Voltag           | е                |     |     | 0.8 | V     |

| I <sub>OH</sub>   | HIGH Level Output Current        |                  |     |     | -2  | mA    |

| I <sub>OL</sub>   | LOW Level Output Current         |                  |     |     | 20  | mA    |

| f <sub>CLK</sub>  | Clock Frequency                  |                  | 0   |     | 75  | MHz   |

| <sup>t</sup> su   | t <sub>setup</sub> , Set-up Time | Data; A, B, C, D | 8   |     |     | ns    |

|                   |                                  | En P, En T       | 8   |     |     | ns    |

|                   |                                  | LOAD             | 8   |     |     | ns    |

|                   |                                  | U/D              | 11  |     |     | ns    |

| <sup>t</sup> H    | t <sub>hold</sub> , Hold Time    | Data; A, B, C, D | 0   |     |     | ns    |

|                   |                                  | En P, En T       | 0   |     |     | ns    |

|                   |                                  | LOAD             | 0   |     |     | ns    |

|                   |                                  | U/D              | 0   |     |     | ns    |

| t <sub>WCLK</sub> | Width of Clock Pulse             |                  | 6.7 |     |     | ns    |

| t <sub>A</sub>    | Free Air Operating Temperature   |                  | 0   |     | 70  | °C    |

## **Electrical Characteristics**

over recommended operating free air temperature range. All typical values are measured at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$

| Symbol                  | Parameter                | Conditions                               |                                | Min                 | Тур  | Max  | Units |

|-------------------------|--------------------------|------------------------------------------|--------------------------------|---------------------|------|------|-------|

| V <sub>IK</sub>         | Input Clamp Voltage      | $V_{CC} = 4.5V$ , $I_I = -18 \text{ mA}$ |                                |                     |      | -1.2 | V     |

| V <sub>OH</sub>         | HIGH Level               | $I_{OH} = -2 \text{ mA},$                |                                | V <sub>CC</sub> - 2 |      |      | V     |

|                         | Output Voltage           | $V_{CC} = 4.5V \text{ to } 5.5V$         | V <sub>CC</sub> = 4.5V to 5.5V |                     |      |      | ٧     |

| V <sub>OL</sub>         | LOW Level                | V <sub>CC</sub> = 4.5V,                  | V <sub>CC</sub> = 4.5V,        |                     | 0.35 | 0.5  | V     |

|                         | Output Voltage           | $I_{OL} = 20 \text{ mA}$                 |                                |                     | 0.33 | 0.5  | \ \ \ |

| I <sub>I</sub>          | Input Current @ Max      | $V_{CC} = 5.5V,$                         | LOAD, ENT, U/D                 |                     |      | 0.2  | mA    |

|                         | Input Voltage            | $V_{IH} = 7V$                            | Others                         |                     |      | 0.1  | IIIA  |

| I <sub>IH</sub>         | HIGH Level Input Current | $V_{CC} = 5.5V$ ,                        | LOAD, ENT, U/D                 |                     |      | 40   | μА    |

|                         |                          | $V_{IH} = 2.7V$                          | Others                         |                     |      | 20   | μΛ    |

| I <sub>IL</sub>         | LOW Level Input Current  | V <sub>CC</sub> = 5.5V,                  | CLK, DATA, ENP                 |                     |      | -0.5 | mA    |

|                         |                          | $V_{IL} = 0.4V$                          | LOAD, ENT, U/D                 |                     |      | -1   | IIIA  |

| I <sub>O</sub> (Note 2) | Output Drive Current     | $V_{CC} = 5.5V, V_{O} = 2.25V$           |                                | -30                 |      | -112 | mA    |

| I <sub>CC</sub>         | Supply Current           | V <sub>CC</sub> = 5.5V                   |                                |                     | 46   | 63   | mA    |

Note 2: The output conditions have been chosen to produce a current that closely approximates one half of the true short circuit output current, I<sub>OS</sub>.

# **Switching Characteristics**

over recommended operating free air temperature range

| Symbol           | Parameter                | Conditions                     | From     | То             | Min | Max  | Units |

|------------------|--------------------------|--------------------------------|----------|----------------|-----|------|-------|

| f <sub>MAX</sub> | Maximum Clock Frequency  | V <sub>CC</sub> = 4.5V to 5.5V |          |                | 75  |      | MHz   |

| t <sub>PLH</sub> | Propagation Delay Time   | $R_L = 500\Omega$              | Clock    | RIPPLE Carry   | 3   | 16.5 | ns    |

|                  | LOW-to-HIGH Level Output | $C_L = 50 pF$                  | Clock    | THIFF LL Carry | 3   | 10.5 | 115   |

| t <sub>PHL</sub> | Propagation Delay Time   |                                | Clock    | RIPPLE Carry   | 2   | 13   | ns    |

|                  | HIGH-to-LOW Level Output |                                | Clock    | Thirr LE Carry |     | 13   | 115   |

| t <sub>PLH</sub> | Propagation Delay Time   |                                | Clock    | Any Q          | 1   | 7    | ns    |

|                  | LOW-to-HIGH Level Output |                                | Olook    | 7 tily Q       |     | ,    | 110   |

| t <sub>PHL</sub> | Propagation Delay Time   |                                | Clock    | Any Q          | 2   | 13   | ns    |

|                  | HIGH-to-LOW Level Output |                                | Olook    | 7 , Q          | -   | .0   | 1.0   |

| t <sub>PLH</sub> | Propagation Delay Time   |                                | En T     | RIPPLE Carry   | 1.5 | 9    | ns    |

|                  | LOW-to-HIGH Level Output |                                | EII 1    | NIFFLE Carry   | 1.5 | 9    | 115   |

| t <sub>PHL</sub> | Propagation Delay Time   |                                | En T     | DIDDLE Comm    | 1.5 | 9    |       |

|                  | HIGH-to-LOW Level Output |                                | Eni      | RIPPLE Carry   | 1.5 | 9    | ns    |

| t <sub>PLH</sub> | Propagation Delay Time   |                                | U/D      | DIDDLE 0       |     | 40   |       |

|                  | LOW-to-HIGH Level Output |                                | (Note 3) | RIPPLE Carry   | 2   | 12   | ns    |

| t <sub>PHL</sub> | Propagation Delay Time   |                                | U/D      | DIDDLE Commi   | 0   | 10   |       |

|                  | HIGH-to-LOW Level Output |                                | (Note 3) | RIPPLE Carry   | 2   | 13   | ns    |

Note 3: Propagation delay time from up/down to ripple carry must be measured with the counter at either a minimum or a maximum count. As the logic level of the up/down input is changed, the ripple carry output will follow. If the count is minimum (0), the ripple carry output transition will be in phase. If the count is maximum, the ripple carry output will be out of phase.

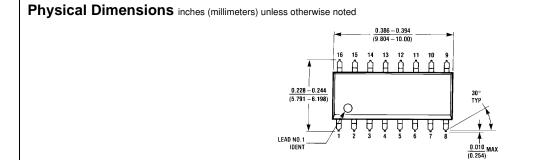

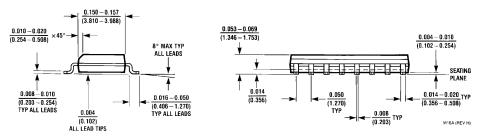

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow Package Number M16A

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

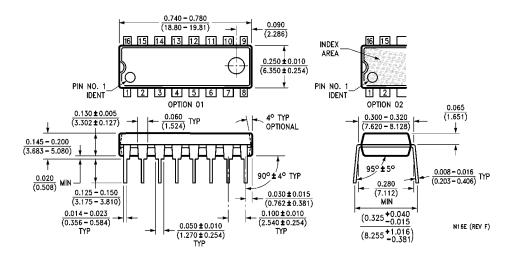

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.