# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

August 1986 Revised April 2000

### FAIRCHILD

SEMICONDUCTOR

### DM74LS164 8-Bit Serial In/Parallel Out Shift Register

### **General Description**

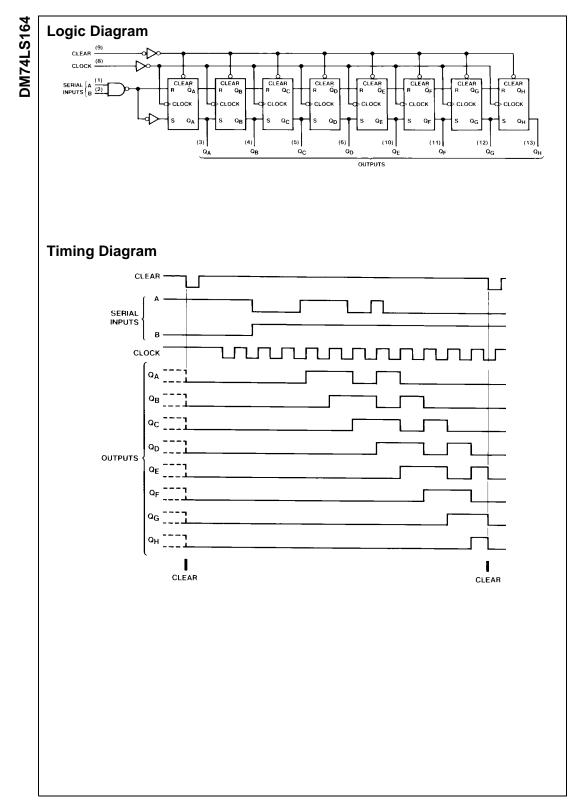

These 8-bit shift registers feature gated serial inputs and an asynchronous clear. A low logic level at either input inhibits entry of the new data, and resets the first flip-flop to the low level at the next clock pulse, thus providing complete control over incoming data. A high logic level on either input enables the other input, which will then determine the state of the first flip-flop. Data at the serial inputs may be changed while the clock is HIGH or LOW, but only information meeting the setup and hold time requirements will be entered. Clocking occurs on the LOW-to-HIGH level transition of the clock input. All inputs are diode-clamped to minimize transmission-line effects.

### **Features**

- Gated (enable/disable) serial inputs

- Fully buffered clock and serial inputs

- Asynchronous clear

- Typical clock frequency 36 MHz

- Typical power dissipation 80 mW

# DM74LS164 8-Bit Serial In/Parallel Out Shift Register

### **Ordering Code:**

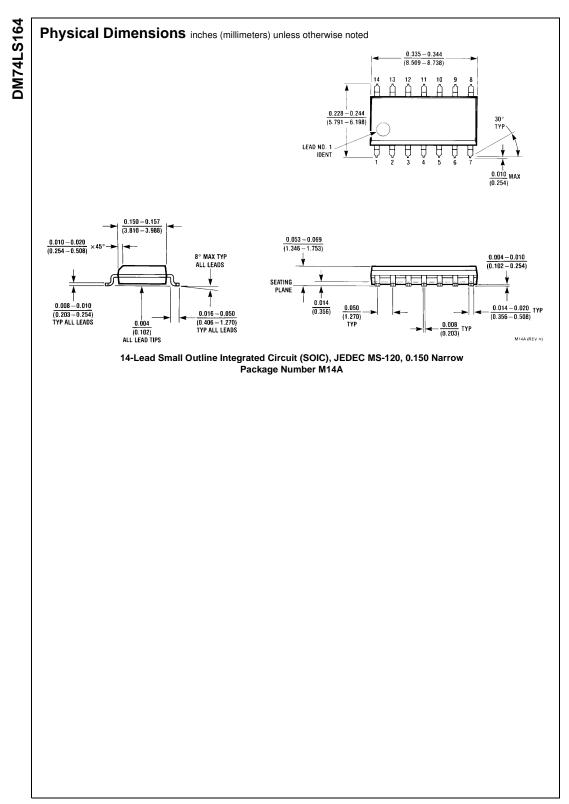

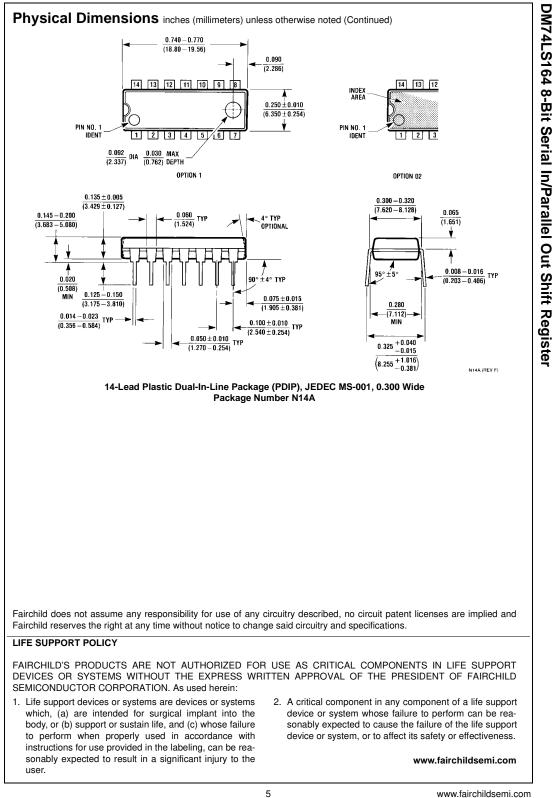

| Order Number           | Package Number           | Package Description                                                         |

|------------------------|--------------------------|-----------------------------------------------------------------------------|

| DM74LS164M             | M14A                     | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow |

| DM74LS164N             | N14A                     | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |

| Dovidos also available | in Tana and Roal Specify | by appanding the suffix latter "Y" to the ordering and                      |

8

QD

GND

es also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code

### **Connection Diagram** OUTPUTS CLEAR CLOCK ٧cc QH QG Qc QE 12 10 9 14 13 11 2 3 4 5 6 7

в

SERIAL INPUTS

QA

$Q_B$

QC

OUTPUTS

А

### **Function Table**

|       | Inputs     |   |   |                 | Outputs         |  |                 |  |

|-------|------------|---|---|-----------------|-----------------|--|-----------------|--|

| Clear | Clock      | Α | В | Q <sub>A</sub>  | QB              |  | Q <sub>H</sub>  |  |

| L     | Х          | Х | Х | L               | L               |  | L               |  |

| Н     | L          | Х | Х | Q <sub>A0</sub> | $Q_{B0}$        |  | Q <sub>H0</sub> |  |

| Н     | $\uparrow$ | н | Н | Н               | Q <sub>An</sub> |  | Q <sub>Gn</sub> |  |

| Н     | $\uparrow$ | L | Х | L               | Q <sub>An</sub> |  | Q <sub>Gn</sub> |  |

| н     | ↑ (        | Х | L | L               | Q <sub>An</sub> |  | Q <sub>Gn</sub> |  |

H = HIGH Level (steady state)

L = LOW Level (steady state) X = Don't Care (any input, including transitions)

$\uparrow = \text{Transition from LOW-to-HIGH level}$

$\mathsf{Q}_{A0},\,\mathsf{Q}_{B0},\,\mathsf{Q}_{H0}$  = The level of  $\mathsf{Q}_A,\,\mathsf{Q}_B,\,\text{or}\;\mathsf{Q}_H,$  respectively, before the

indicated steady-state input conditions were established.

$\mathsf{Q}_{An},\,\mathsf{Q}_{Gn}=$  The level of  $\mathsf{Q}_A$  or  $\mathsf{Q}_G$  before the most recent  $\uparrow$  transition of the clock; indicates a one-bit shift.

© 2000 Fairchild Semiconductor Corporation DS006398 www.fairchildsemi.com

www.fairchildsemi.com

2

### Absolute Maximum Ratings(Note 1)

| Supply Voltage                       | 7V                                |

|--------------------------------------|-----------------------------------|

| Input Voltage                        | 7V                                |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$    |

| Storage Temperature Range            | $-65^{\circ}C$ to $+150^{\circ}C$ |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" tables will define the conditions for actual device operation.

# DM74LS164

### **Recommended Operating Conditions**

| Symbol           | Parameter                      |       | Min  | Nom | Max  | Units |

|------------------|--------------------------------|-------|------|-----|------|-------|

| V <sub>CC</sub>  | Supply Voltage                 |       | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub>  | HIGH Level Input Voltage       |       | 2    |     |      | V     |

| V <sub>IL</sub>  | LOW Level Input Voltage        |       |      |     | 0.8  | V     |

| I <sub>OH</sub>  | HIGH Level Output Current      |       |      |     | -0.4 | mA    |

| I <sub>OL</sub>  | LOW Level Output Current       |       |      |     | 8    | mA    |

| f <sub>CLK</sub> | Clock Frequency (Note 2)       |       | 0    |     | 25   | MHz   |

| t <sub>W</sub>   | Pulse Width                    | Clock | 20   |     |      | 20    |

|                  | (Note 2)                       | Clear | 20   |     |      | ns    |

| t <sub>SU</sub>  | Data Setup Time (Note 2)       |       | 17   |     |      | ns    |

| t <sub>H</sub>   | Data Hold Time (Note 2)        |       | 5    |     |      | ns    |

| t <sub>REL</sub> | Clear Release Time (Note 2)    |       | 30   |     |      | ns    |

| T <sub>A</sub>   | Free Air Operating Temperature |       | 0    |     | 70   | °C    |

Note 2:  $T_A=25^\circ C$  and  $V_{CC}=5V.$

### **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                         | Conditions                                   | Min | Typ<br>(Note 3) | Max  | Units |

|-----------------|-----------------------------------|----------------------------------------------|-----|-----------------|------|-------|

| VI              | Input Clamp Voltage               | $V_{CC} = Min, I_I = -18 \text{ mA}$         |     |                 | -1.5 | V     |

| V <sub>OH</sub> | HIGH Level                        | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max | 2.7 | 3.4             |      | v     |

|                 | Output Voltage                    | $V_{IL} = Max, V_{IH} = Min$                 | 2.7 | 3.4             |      | v     |

| V <sub>OL</sub> | LOW Level                         | V <sub>CC</sub> = Min, I <sub>OL</sub> = Max |     | 0.35            | 0.5  | v     |

|                 | Output Voltage                    | $V_{IL} = Max, V_{IH} = Min$                 |     | 0.35            |      |       |

|                 |                                   | $I_{OL} = 4 \text{ mA}, V_{CC} = \text{Min}$ |     | 0.25            | 0.4  | İ     |

| I <sub>I</sub>  | Input Current @ Max Input Voltage | $V_{CC} = Max, V_I = 7V$                     |     |                 | 0.1  | mA    |

| I <sub>IH</sub> | HIGH Level Input Current          | $V_{CC} = Max, V_I = 2.7V$                   |     |                 | 20   | μΑ    |

| IL              | LOW Level Input Current           | $V_{CC} = Max, V_I = 0.4V$                   |     |                 | -0.4 | mA    |

| I <sub>OS</sub> | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 4)               | -20 |                 | -100 | mA    |

| I <sub>CC</sub> | Supply Current                    | V <sub>CC</sub> = Max (Note 5)               |     | 16              | 27   | mA    |

Note 3: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 4: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 5: I<sub>CC</sub> is measured with all outputs OPEN, the SERIAL input grounded, the CLOCK input at 2.4V, and a momentary ground, then 4.5V, applied to the CLEAR input.

### **Switching Characteristics**

at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$

| Symbol           | Parameter                                          | From (Input)<br>To (Output) |                        |     |                        |     |       |

|------------------|----------------------------------------------------|-----------------------------|------------------------|-----|------------------------|-----|-------|

|                  |                                                    |                             | C <sub>L</sub> = 15 pF |     | C <sub>L</sub> = 50 pF |     | Units |

|                  |                                                    |                             | Min                    | Max | Min                    | Max |       |

| f <sub>MAX</sub> | Maximum Clock Frequency                            |                             | 25                     |     |                        |     | MHz   |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | Clock to Output             |                        | 27  |                        | 30  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Clock to Output             |                        | 32  |                        | 40  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | Clear to Output             |                        | 36  |                        | 45  | ns    |

www.fairchildsemi.com