# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

DS21349 3.3V T1/J1 Line Interface Unit

#### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

The DS21349 is a fully integrated LIU for longhaul or short-haul T1 applications over twistedpair installations. It interfaces to two twisted-pair lines—one pair for transmit and one pair for receive through an appropriate network interface. The device can be configured for control through software or hardware mode. Software control is accomplished over a serial port in hardware mode; individual pin settings allow stand-alone operation. The device provides a precise, crystal-less jitter attenuator that can be placed in either the transmit or receive path.

#### **APPLICATIONS**

Routers Data Service Units (DSUs) Channel Service Units (CSUs) Muxes Switches Channel Banks T1/E1 Test Equipment

#### **PIN CONFIGURATION**

#### FEATURES

- Fully Integrated Line Interface Unit (LIU)

- Pin Compatible with LevelOne LXT362

- Supports Both Long Haul and Short Haul

- Crystal-Less Jitter Attenuator

- Jitter Attenuator Programmable for Transmit or Receive Path

- Meets ANSI T1.102, T1.403, T1.408, and AT&T 62411

- Usable Receive Sensitivity of 0dB to -36dB That Allows the Device to Operate on 0.63mm (22AWG) Cables Up to 6k Feet in Length

- Five Line Build-Out Settings for Short-Haul Applications

- Four CSU Filters from 0dB to -22.5dB

- Transmit/Receive Performance Monitors with Driver-Fail, Monitor-Open, and Lossof-Signal Outputs

- Bipolar or NRZ Interface

- Programmable B8ZS Encoder/Decoder

- QRSS Generator/Detector

- Local, Remote, and Analog Loopbacks

- Generates and Detects In-Band Loop-Up and Loop-Down Codes

- Serial Interface Provides Access to Control Registers

#### **ORDERING INFORMATION**

| PART       | TEMP<br>RANGE  | PIN-<br>PACKAGE |

|------------|----------------|-----------------|

| DS21349Q   | 0°C to +70°C   | 28 PLCC         |

| DS21349Q+  | 0°C to +70°C   | 28 PLCC         |

| DS21349QN  | -40°C to +85°C | 28 PLCC         |

| DS21349QN+ | -40°C to +85°C | 28 PLCC         |

+Denotes lead-free/RoHS-compliant package.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <u>www.maxim-ic.com/errata</u>.

### TABLE OF CONTENTS

| 1. D        |                                                                 | 4  |

|-------------|-----------------------------------------------------------------|----|

| 2. C        | OPERATING MODES                                                 | 5  |

| 3. II       | NITIALIZATION AND RESET                                         | 9  |

|             | REGISTER DEFINITIONS                                            |    |

|             | RANSMITTER.                                                     |    |

| <b>5</b> .1 | TRANSMIT DIGITAL DATA INTERFACE                                 |    |

| 5.1         | TRANSMIT DIGITAL DATA INTERFACE                                 |    |

| 5.2         | TRANSMIT MONITORING                                             |    |

| 5.3<br>5.4  | TRANSMIT IDLE MODE                                              |    |

| -           |                                                                 |    |

| <b>6</b> .1 | RECEIVE EQUALIZER                                               |    |

| 6.2         | RECEIVE EQUALIZER.                                              |    |

| 6.3         | RECEIVE DATA RECOVERY                                           |    |

| 6.4         | RECEIVE DIGITAL-DATA INTERFACE.                                 |    |

| -           |                                                                 |    |

|             |                                                                 |    |

|             | IARDWARE MODE                                                   |    |

|             | OFTWARE MODE                                                    |    |

| 9.1         | INTERRUPT HANDLING                                              |    |

| 10. C       | DIAGNOSTIC MODE OPERATION                                       | 22 |

| 10.1        | LOOPBACK MODES                                                  |    |

|             | Local Loopback (LLB)                                            |    |

|             | ? Analog Loopback (ALB)                                         |    |

|             | Remote Loopback (RLB)                                           |    |

|             | Network Loopback                                                |    |

|             | 5 Dual Loopback                                                 |    |

| 10.2        | INTERNAL PATTERN GENERATION AND DETECTION                       |    |

|             | Quasirandom Signal Source (QRSS)                                |    |

|             | In-Band Network Loop-Up or Loop-Down Code Generator             |    |

| 10.3        | ERROR INSERTION AND DETECTION.                                  |    |

|             | Bipolar Violation Insertion (INSBPV)                            |    |

|             | 2 Logic Error Insertion (INSLE)                                 |    |

| 10.3.3      | B Logic Error Detection (QPD)                                   | 25 |

|             | Bipolar Violation Detection (BPV)                               |    |

|             | ALARM MONITORING                                                |    |

|             | Receive-Carrier Loss (RCL)                                      |    |

|             | ? Alarm-Indication-Signal Detection (AIS)                       |    |

|             | 3 Driver-Fail Monitor-Open (DFMO)                               |    |

| 10.4.4      | Jitter Attenuator Limit Trip (JALT)<br>OTHER DIAGNOSTIC REPORTS |    |

|             | Receive Line-Attenuation Indication                             |    |

|             |                                                                 |    |

|             |                                                                 |    |

|             |                                                                 |    |

|             |                                                                 | 35 |

| 13.1        | 28-PIN PLCC ( <u>56-G4001-001</u> )                             | 35 |

### LIST OF FIGURES

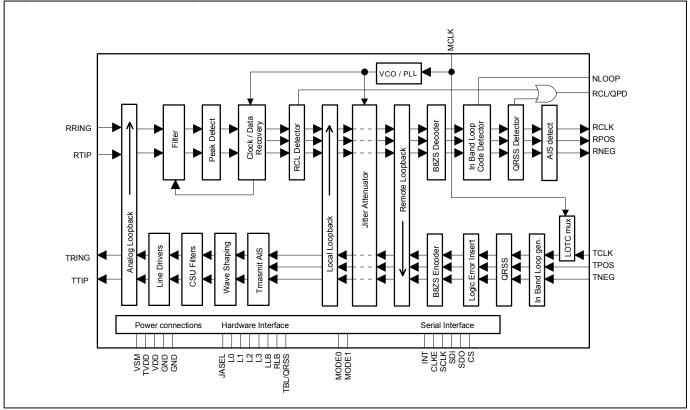

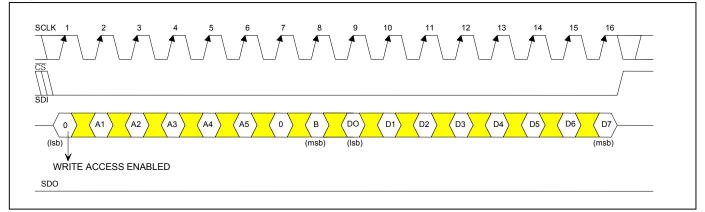

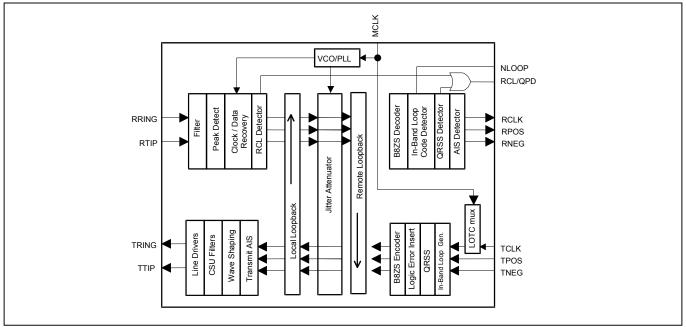

| Figure 1-1. Block Diagram                               | 4    |

|---------------------------------------------------------|------|

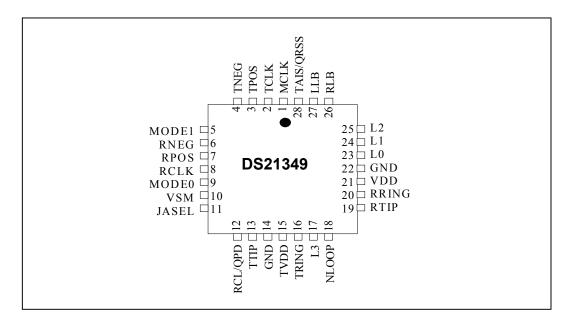

| Figure 2-1. Hardware Mode Pinout                        | 6    |

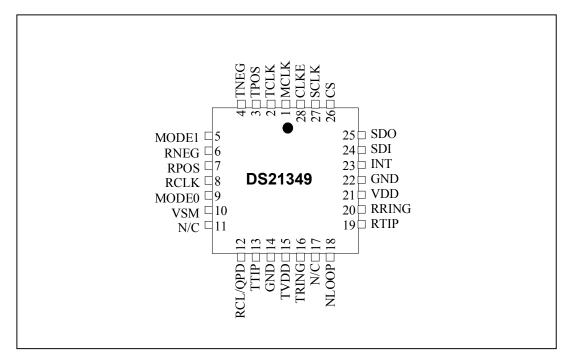

| Figure 2-2. Serial Port Mode Pinout                     | 6    |

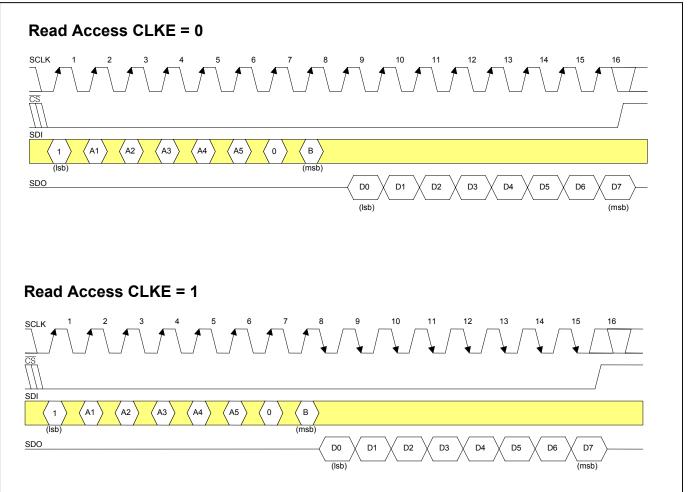

| Figure 9-1. Serial Data Port Operation for Read Access  | . 20 |

| Figure 9-2. Serial Data Port Operation for Write Access | . 20 |

| Figure 10-1. Loopbacks in the DS21349 Block Diagram     | . 24 |

| Figure 11-1. Basic Network Interface                    | . 28 |

| Figure 11-2. T1 Transmit Pulse Template                 | . 29 |

| Figure 11-3. Jitter Tolerance                           | . 30 |

| Figure 11-4. Jitter Attenuation                         | . 30 |

| Figure 12-1. Serial Bus Read Timing (MODE1 = 1)         | . 32 |

| Figure 12-2. Serial Bus Write Timing (MODE1 = 1)        | . 32 |

| Figure 12-3. AC Characteristics for Receive Side        | . 33 |

| Figure 12-4. AC Characteristics for Transmit Side       | . 34 |

### LIST OF TABLES

| Table 2-A. Operating Modes                                | 5  |

|-----------------------------------------------------------|----|

| Table 2-B. Control Pins for Hardware and Software Modes   | 5  |

| Table 2-C. Signal Descriptions                            | 7  |

| Table 4-A. Register Map                                   | 10 |

| Table 4-B. Register Bit Positions                         | 10 |

| Table 4-C. Jitter Attenuator Selection                    | 11 |

| Table 4-D. Line Code and Interface Selection              | 11 |

| Table 4-E. Line Build-Out Selection                       | 11 |

| Table 4-F. Data Pattern Selection                         | 12 |

| Table 9-A. CLKE Pin Selection                             | 19 |

| Table 9-B. Control and Operation Mode Selection           | 21 |

| Table 10-A. Diagnostic Modes                              | 22 |

| Table 11-A. Specifications for Receive Transformer        | 27 |

| Table 11-B. Specifications for Transmit Transformer       | 27 |

| Table 11-C. Transformer Turns Ratio vs. Series Resistance | 27 |

### 1. DETAILED DESCRIPTION

The DS21349 is a complete T1 line interface unit (LIU) for short-haul and long-haul applications. Receive sensitivity adjusts automatically to the incoming signal and can be limited to -18dB, -26dB, or -36dB. The device can generate the necessary DSX-1 line build-outs or CSU line build-outs of 0dB, -7.5dB, -15dB, and -22.5dB. The on-board crystal-less jitter attenuator requires a 1.544MHz reference clock. The jitter attenuator FIFO is selectable to either 32 bits or 128 bits in depth and can be placed in either the transmit or receive data paths. The DS21349 has diagnostic capabilities such as loopbacks and QRSS pattern generation and detection. The device can also generate and detect the in-band loop-up and loop-down codes specified in AT&T 62411. The device can be configured for control using a serial interface, or for hardware mode. The device fully meets all of the latest T1 specifications including ANSI T1.102-1999, ANSI T1.403-1999, ANSI T1.408, and AT&T 62411.

### Figure 1-1. Block Diagram

### 2. OPERATING MODES

The DS21349 has several pins with multiple functions and names according to the selected operating mode. These operating modes are summarized in the tables below.

| PIN | QRSS DIS | SABLED | QRSS ENABLED |       |  |  |  |

|-----|----------|--------|--------------|-------|--|--|--|

| PIN | BIPOLAR  | NRZ    | BIPOLAR      | NRZ   |  |  |  |

| 1   |          | M      | CLK          |       |  |  |  |

| 2   |          | TC     | CLK          |       |  |  |  |

| 3   | TPOS     | TDATA  | INSI         | LER   |  |  |  |

| 4   | TNEG     | INSBPV | INSBPV       |       |  |  |  |

| 6   | RNEG     | BPV    | RNEG         | BPV   |  |  |  |

| 7   | RPOS     | RDATA  | RPOS         | RDATA |  |  |  |

| 8   |          | RC     | CLK          |       |  |  |  |

| 13  |          | TTIP   |              |       |  |  |  |

| 16  | TRING    |        |              |       |  |  |  |

| 19  | RTIP     |        |              |       |  |  |  |

| 20  |          | RR     | ING          |       |  |  |  |

#### **Table 2-A. Operating Modes**

Control pins are affected by serial port and hardware modes.

#### HARDWARE MODE **SERIAL PORT MODE** PIN NRZ **QRSS** NRZ **QRSS** 5 MODE1 MODE1 9 MODE0 MODE0 11 JASEL N.C. RCL/QPD 12 RCL RCL RCL/QPD 23 L0 INT 24 L1 SDI 25 L2 SDO 17 L3 N.C. 18 NLOOP NLOOP NLB 26 RLB CS 27 LLB ALB SCLK 28 TAIS QRSS CLKE

#### Table 2-B. Control Pins for Hardware and Software Modes

Figure 2-1. Hardware Mode Pinout

Figure 2-2. Serial Port Mode Pinout

### Table 2-C. Signal Descriptions

| PIN      | NAME         | I/O            | FUNCTION                                                                                                                                                                                                                                          |  |  |  |

|----------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1        | MCLK         | Ι              | Master Clock. A 1.544MHz clock source with TTL levels is applied at this pin. This clock is used internally for both clock/data recovery and for jitter attenuation. <sup>1</sup>                                                                 |  |  |  |

| 2        | TCLK         | Ι              | Fransmit Clock. A 1.544MHz primary clock. Used to clock data through the transmit side formatter. Can be sourced internally by MCLK or RCLK.                                                                                                      |  |  |  |

|          | TPOS         |                | Transmit Positive Data. Sampled on the falling edge of TCLK for data to be transmitted out onto the line.                                                                                                                                         |  |  |  |

| 3        | TDATA        | Ι              | Transmit NRZ Data. Sampled on the falling edge of TCLK for data to be transmitted onto the line.                                                                                                                                                  |  |  |  |

|          | INSLER       |                | Transmit Insert Logic Error. Rising edge on INSLER inserts a logic error into the outbound QRSS pattern. Sampled on falling edge of TCLK.                                                                                                         |  |  |  |

| 4        | TNEG         | Ţ              | Transmit Negative Data. Sampled on the falling edge of TCLK for data to be transmitted out onto the line.                                                                                                                                         |  |  |  |

| 4        | INSBPV       | - I            | Transmit Insert Bipolar Violation. INSBPV is sampled on the falling edge of TCLK.<br>Rising edge inserts one BPV.                                                                                                                                 |  |  |  |

| 5        | MODE1        | I <sup>2</sup> | Mode Select 1. Connect low to select hardware mode. Connect high to select serial port mode. See also MODE0.                                                                                                                                      |  |  |  |

| 6        | RNEG         | 0              | Receive Negative Data. Updated on the rising edge ( $CCR2.0 = 0$ ) or the falling edge ( $CCR2.0 = 1$ ) of RCLK with the bipolar data out of the line interface. Always valid on rising edge of RCLK in hardware mode.                            |  |  |  |

|          | BPV          |                | Receive Bipolar Violation. Transitions high for one clock cycle marking an inbound bipolar violation. Valid on rising edge of RCLK.                                                                                                               |  |  |  |

|          | RPOS         |                | Receive Positive Data. Updated on the rising edge ( $CCR2.0 = 0$ ) or the falling edge ( $CCR2.0 = 1$ ) of RCLK with bipolar data out of the line interface. Always valid on rising edge of RCLK in hardware mode.                                |  |  |  |

| 7        | 7<br>RDATA   |                | Receive Data. RDATA is the NRZ output from the line interface. Set NRZE (CCR1.6) to a 1 for NRZ applications. In NRZ mode, data is output on RPOS while a received error causes a positive-going pulse synchronous with RCLK at RNEG (Section 6). |  |  |  |

| 8        | RCLK         | 0              | Receive Clock. Buffered recovered clock from the line. Synchronous to MCLK in absence of signal at RTIP and RRING.                                                                                                                                |  |  |  |

| 9        | MODE0        | I <sup>2</sup> | Mode Select 0. Set high to disable all output pins (including the serial control port).<br>Set low for normal operation. Useful in board level testing. See also MODE1.                                                                           |  |  |  |

| 10       | VSM          | Ι              | Voltage Supply Mode. Connect high for 3.3V operation. Has $10k\Omega$ pullup.                                                                                                                                                                     |  |  |  |

| 11       | JASEL        | I <sup>2</sup> | Jitter Attenuator Select<br>0 = Place the jitter attenuator on the transmit side<br>1 = Place the jitter attenuator on the receive side<br>Float = Disable jitter attenuator<br>Not used in software mode                                         |  |  |  |

|          | RCL          |                | Receive Carrier Loss. An output that toggles high during a receive carrier loss.                                                                                                                                                                  |  |  |  |

| 12       | QPD          | 0              | <b>QPD</b> . Output high when QRSS detector is searching for QRSS data pattern. Output high for one-half clock cycle on bit error. Connect to external counter to count bit errors.                                                               |  |  |  |

| 13/      | TTIP/        | 0              | Transmit Tip and Ring. Analog line driver outputs. These pins connect through a                                                                                                                                                                   |  |  |  |

| 16<br>14 | TRING<br>VSS | <u> </u>       | step-up transformer to the line (Section <u>5</u> ).<br>Ground for Transmitter Block                                                                                                                                                              |  |  |  |

| 15       | TVDD         | <u> </u>       | Positive Supply. $3.3V \pm 5\%$ for the transmitter block. See also VSM pin 10.                                                                                                                                                                   |  |  |  |

| PIN                                                                                | NAME           | I/O                                                                                                                                                                                               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |                                                                       |  |  |  |

|------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------------------------------------------------------|--|--|--|

| 17                                                                                 | L3             | Ι                                                                                                                                                                                                 | LBO3. LBO0 through LBO3 are used to select transmitter output pulse, and receiver gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |                                                                       |  |  |  |

| 18                                                                                 | NLOOP          | 0                                                                                                                                                                                                 | Network Loopback Active. Output high when RLB is activated by in-band loop-up command present for 5 seconds. Output is reset when RLP is deactivated by in-ban loop-down command present for 5 seconds. Activation of remote loopback through hardware pin 26 or control bit RLB releases the NLOOP output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |                                                                       |  |  |  |

| 19/<br>20                                                                          | RTIP/<br>RRING | Ι                                                                                                                                                                                                 | Receive Tip and Ring. Analog inputs for clock recovery circuitry. These pins connect through a 1:1 transformer to the line (Section $\underline{6}$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |                                                                       |  |  |  |

| 21                                                                                 | VDD            |                                                                                                                                                                                                   | Positive Supply. $3.3V \pm 5\%$ . See also VSM pin 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |                                                                       |  |  |  |

| 22                                                                                 | VSS            |                                                                                                                                                                                                   | Signal Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |                                                                       |  |  |  |

| 23                                                                                 | LO             | I/O                                                                                                                                                                                               | LBO0. LBO0 through LBO3 are used to select transmitter output pulse, and receiver gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |                                                                       |  |  |  |

|                                                                                    | INT            |                                                                                                                                                                                                   | INT. Used to alert the host when one or more bits are set in the status register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |                                                                       |  |  |  |

| 24                                                                                 | L1             | т                                                                                                                                                                                                 | LBO1. LBO0 through LBO3 are used to select transmitter output pulse, and receiver gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |                                                                       |  |  |  |

| 24                                                                                 | SDI            | I                                                                                                                                                                                                 | Serial Data Input. Input for serial address and data stream. Sampled on rising of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |                                                                       |  |  |  |

|                                                                                    | L2             |                                                                                                                                                                                                   | LBO2. LBO0 through LBO3 are used to select transmitter output pulse, and receiver gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |                                                                       |  |  |  |

| 25 SDO                                                                             |                | 0                                                                                                                                                                                                 | Serial Data Output. Updated on falling edge of SCLK if CLKE is connected high.<br>Updated on rising edge of SCLK if CLKE is connected low. SDO is high-Z during<br>write cycle or when CS is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |                                                                       |  |  |  |

| 26                                                                                 | RLB            | I <sup>2</sup>                                                                                                                                                                                    | Remote Loopback. Used to invoke remote loopback. When held high, the transmitter inputs are ignored and inbound data received at RTIP and RRING is routed to the transmitter outputs, TTIP and TRING and transmitted at the inbound recovered clock rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |                                                                       |  |  |  |

|                                                                                    |                |                                                                                                                                                                                                   | NLB         Network Loopback. Enables network loopback detection whether the second secon |  | Network Loopback. Enables network loopback detection when RLB floats. |  |  |  |

|                                                                                    |                |                                                                                                                                                                                                   | Chip Select. Must be low to read or write to the device. $\overline{CS}$ is an active-low signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |                                                                       |  |  |  |

| 27     LLB     Local Loopback. Use<br>TPOS and TNEG are<br>if enabled. Floating th |                | I <sup>2</sup>                                                                                                                                                                                    | Local Loopback. Used to invoke local loopback. When held high, digital inputs<br>TPOS and TNEG are looped back to RPOS and RNEG, through the jitter attenuator<br>if enabled. Floating this input invokes analog loopback. The analog output signal at<br>TTIP and TRING is routed to the receive inputs RTIP and RRING.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |                                                                       |  |  |  |

|                                                                                    | SCLK           |                                                                                                                                                                                                   | Serial Clock Input. Input clock to operate serial port. Max clock rate, 2.048MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |                                                                       |  |  |  |

|                                                                                    | TAIS           |                                                                                                                                                                                                   | Transmit AIS. Input high forces transmitter to output unframed all ones. Unavailable in remote loopback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |                                                                       |  |  |  |

|                                                                                    | QRSS           |                                                                                                                                                                                                   | QRSS. Floating this pin enables QRSS pattern generator and detector. Input low enables normal transmission of data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |                                                                       |  |  |  |

| 28                                                                                 | CLKE           | Clock Edge Select<br>0 = Update RNEG/RPOS on falling edge of RCLK, SDO updated on rising edge of<br>SCLK.<br>1 = Update RNEG/RPOS on rising edge of RCLK, SDO updated on falling edge of<br>SCLK. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |                                                                       |  |  |  |

**Note 1:** G.703 requires an accuracy of ±50ppm for T1. TR62411 and ANSI specifications require an accuracy of ±32ppm for T1 interfaces. **Note 2:** Input pins have three operating modes.

### 3. INITIALIZATION AND RESET

During power-up, all control registers are cleared, disabling the transmitter outputs. The device requires a master clock supplied to the MCLK input pin to operate the PLL. This master clock must be independent, free-running, and jitter free.

A reset initializes the status and state machines for the RCL, AIS, NLOOP, and QRSS blocks. Under software control, setting the RESET bit (CR2.7) clears all registers. Allow up to 100ms for the receiver to recover from initialization.

### 4. REGISTER DEFINITIONS

The DS21349 contains eight registers for configuring the device and reading status. These are accessible using the serial port. <u>Table 4-A</u> lists the register names and addresses.

Reading or writing to the internal registers requires writing one address/command byte prior to transferring register data. The first bit written (LSb) of the address/command byte specifies whether the access is a read (1) or a write (0). The next 6 bits identify the register address.

The last bit (MSb) of the address/command byte is the burst mode bit. When the burst bit is enabled (set to 1) and a READ operation is performed, addresses 10h through 17h are read sequentially, starting at address 10h. And when the burst bit is enabled and a WRITE operation is performed, addresses 10h through 17h are written sequentially, starting at address 10h. Burst operation is stopped once address 17h is read. All data transfers are initiated by driving the  $\overline{CS}$  input low. All data transfers are terminated if the  $\overline{CS}$  input transitions high. Port control logic is disabled and SDO is tri-stated when  $\overline{CS}$  is high.

#### Table 4-A. Register Map

| REGISTER                   | SYMBOL | ADDRESS |

|----------------------------|--------|---------|

| Control Register 1         | CR1    | B010000 |

| Control Register 2         | CR2    | B010001 |

| Control Register 3         | CR3    | B010010 |

| Interrupt Mask Register    | IMR    | B010011 |

| Transition Status Register | TSR    | B010100 |

| Status Register            | SR     | B010101 |

| Information Register       | IR     | B010110 |

| Control Register 4         | CR4    | B010111 |

#### Table 4-B. Register Bit Positions

| SYMBOL | 7 (MSb) | 6      | 5      | 4        | 3        | 2       | 1     | 0 (LSb) |

|--------|---------|--------|--------|----------|----------|---------|-------|---------|

| CR1    | JASEL1  | JASEL0 | ENCENB | UNIENB   | L3       | L2      | L1    | LO      |

| CR2    | RESET   | PAT1   | PAT0   | TAIS     | ENLOOP   | ALB     | LLB   | RLB     |

| CR3    | JA6HZ   | TPD    | —      | EQZMON20 | EQZMON26 | JA128   | LIRST | TAOZ    |

| IMR    | Z16D    | JALT   | DFMO   | B8ZSD    | QRSS     | AIS     | NLOOP | RCL     |

| TSR    | Z16D    | JALT   | DFMO   | B8ZSD    | QRSS     | AIS     | NLOOP | RCL     |

| SR     | —       | —      | DFMO   | —        | QRSS     | AIS     | NLOOP | RCL     |

| IR     | RL3     | RL2    | RL1    | RL0      | LUP      | LDN     | TSCD  | LOTC    |

| CR4    |         |        |        |          |          | RCL2048 | XFMR2 | XFMR1   |

Note: Set unused bits to 0 for normal operation.

### CR1 (B010000): Control Register 1

| MSb    |        |          |                                                |                                               |         |    | LSb |  |

|--------|--------|----------|------------------------------------------------|-----------------------------------------------|---------|----|-----|--|

| JASEL1 | JASEL0 | ENCENB   | UNIENB                                         | L3                                            | L2      | L1 | LO  |  |

|        |        |          |                                                |                                               |         |    |     |  |

| SYMB   | OL     | POSITION |                                                |                                               | FUNCTIO | DN |     |  |

| JASE   | L1     | CR1.7    | Jitter attenuator select (Table 4-C)           |                                               |         |    |     |  |

| JASE   | LO     | CR1.6    | Jitter attenu                                  | Jitter attenuator select ( <u>Table 4-C</u> ) |         |    |     |  |

| ENCE   | NB     | CR1.5    | B8ZS and NRZ control (Table 4-D)               |                                               |         |    |     |  |

| UNIE   | NB     | CR1.4    | CR1.4 BPV and NRZ control ( <u>Table 4-D</u> ) |                                               |         |    |     |  |

| L3     |        | CR1.3    | Line build-out control (Table 4-E)             |                                               |         |    |     |  |

| L2     |        | CR1.2    | Line build-out control ( <u>Table 4-E</u> )    |                                               |         |    |     |  |

| L1     |        | CR1.1    | Line build-out control ( <u>Table 4-E</u> )    |                                               |         |    |     |  |

| L0     |        | CR1.0    | Line build-                                    | Line build-out control (Table 4-E)            |         |    |     |  |

#### Table 4-C. Jitter Attenuator Selection

| JASEL1 | <b>JASEL0</b> | JITTER ATTENUATOR FUNCTION |  |

|--------|---------------|----------------------------|--|

| 0      | 1             | Transmit path              |  |

| 1      | 1             | Receive path               |  |

| X      | 0             | Disabled                   |  |

#### Table 4-D. Line Code and Interface Selection

| UNIENB | ENCENB | LINE CODE | INTERFACE |

|--------|--------|-----------|-----------|

| 0      | 0      | AMI       | Bipolar   |

| 1      | 0      | AMI       | NRZ       |

| Х      | 1      | B8ZS      | NRZ       |

### Table 4-E. Line Build-Out Selection

| L3 | L2 | L1 | LO | APPLICATION                        | OUTPUT SIGNAL          | Rx GAIN (dB) |

|----|----|----|----|------------------------------------|------------------------|--------------|

| 0  | 0  | 0  | 0  | T1 Long Haul 0dB                   |                        | 36           |

| 0  | 0  | 1  | 0  | T1 Long Haul                       | -7.5dB                 | 36           |

| 0  | 1  | 0  | 0  | T1 Long Haul                       | -15dB                  | 36           |

| 0  | 1  | 1  | 0  | T1 Long Haul                       | -22.5dB                | 36           |

| 0  | 0  | 0  | 1  | T1 Long Haul                       | 0dB                    | 26           |

| 0  | 0  | 1  | 1  | T1 Long Haul                       | -7.5dB                 | 26           |

| 0  | 1  | 0  | 1  | T1 Long Haul                       | -15dB                  | 26           |

| 0  | 1  | 1  | 1  | T1 Long Haul                       | -22.5dB                | 26           |

| 1  | 0  | 0  | 1  | D4 Short Haul                      | 6V                     | 18           |

| 1  | 0  | 1  | 1  | T1 Short Haul                      | DSX-1 (0ft to 133ft)   | 18           |

| 1  | 1  | 0  | 0  | T1 Short Haul                      | DSX-1 (133ft to 266ft) | 18           |

| 1  | 1  | 0  | 1  | T1 Short Haul DSX-1 (266ft to 399f |                        | 18           |

| 1  | 1  | 1  | 0  | T1 Short Haul                      | DSX-1 (399ft to 533ft) | 18           |

| 1  | 1  | 1  | 1  | T1 Short Haul                      | DSX-1 (533ft to 655ft) | 18           |

| MSb          | -          |      | _                                                                                 |                  |                     |      | LSb |  |  |

|--------------|------------|------|-----------------------------------------------------------------------------------|------------------|---------------------|------|-----|--|--|

| RESET        | PAT1       | PAT0 | TAIS                                                                              | ENLOOP           | ALB                 | LLB  | RLB |  |  |

| SYMBOL       | POSI       | TION |                                                                                   | FU               | NCTION              |      |     |  |  |

| RESET        | CR         | 2.7  | Resets device                                                                     | states and clear | rs all registe      | ers. |     |  |  |

| PAT1         | CR         | 2.6  | Selects output                                                                    | data pattern (]  | <u>[able 4-F]</u> . |      |     |  |  |

| PAT0         | CR         | 2.5  | Selects output data pattern (Table 4-F).                                          |                  |                     |      |     |  |  |

| TAIS         | TAIS CR2.4 |      | 0 = Transmit data normally<br>1 = Transmit unframed all ones                      |                  |                     |      |     |  |  |

| ENLOOP CR2.3 |            | 2.3  | 0 = Disable in-band loop-code detection<br>1 = Enable in-band loop-code detection |                  |                     |      |     |  |  |

| ALB CR2.2    |            | 2.2  | 0 = Disable analog loopback<br>1 = Enable analog loopback                         |                  |                     |      |     |  |  |

| LLB CR2.1    |            | 2.1  | 0 = Disable local loopback<br>1 = Enable local loopback                           |                  |                     |      |     |  |  |

| RLB CR2.0    |            |      | 0 = Disable ren1 = Enable ren                                                     |                  | -                   |      |     |  |  |

### CR2 (B010001): Control Register 2

### Table 4-F. Data Pattern Selection

| РАТО | PAT1 | DATA SOURCE           |  |  |  |

|------|------|-----------------------|--|--|--|

| 0    | 0    | TPOS/TNEG             |  |  |  |

| 0    | 1    | Transmit QRSS         |  |  |  |

| 1    | 0    | In-band loop-up 00001 |  |  |  |

| 1    | 1    | In-band loop-down 001 |  |  |  |

### CR3 (B010010): Control Register 3

| MSb   |     |          |          |       |       | LSb  |

|-------|-----|----------|----------|-------|-------|------|

| JA6HZ | TPD | EQZMON20 | EQZMON26 | JA128 | LIRST | TAOZ |

| SYMBOL   | POSITION | FUNCTION                                                                  |  |  |  |

|----------|----------|---------------------------------------------------------------------------|--|--|--|

|          |          | 0 = Set bandwidth of jitter attenuator to $3$ Hz                          |  |  |  |