# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## DS21Q59 E1 Quad Transceiver

#### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

The DS21Q59 E1 quad transceiver contains all the necessary functions for connecting to four E1 lines. The DS21Q59 is a direct replacement for the DS21Q50, with the addition of signaling access and improved interrupt handling. It is composed of a line interface unit (LIU), framer, and a TDM backplane interface, and is controlled through an 8-bit parallel port configured for Intel or Motorola bus operations or serial port operation.

#### **APPLICATIONS**

DSLAMs Routers IMA and WAN Equipment

#### **PIN CONFIGURATION**

#### FEATURES

- Four Complete E1 (CEPT) PCM-30/ISDN-PRI Transceivers

- Pin Compatible with the DS21Q50

- Long-Haul and Short-Haul Line Interfaces

- 32-Bit or 128-Bit Crystal-Less Jitter Attenuator

- Frames to FAS, CAS, and CRC4 Formats

- CAS/CCS Signaling Support

- 4MHz/8MHz/16MHz Clock Synthesizer

- Flexible System Clock with Automatic Source Switching on Loss-of-Clock Source

- Two-Frame Elastic-Store Slip Buffer on the Receive Side

- Interleaving PCM Bus Operation Up to 16.384MHz

- Configurable Parallel and Serial Port Operation

- Detects and Generates Remote and AIS Alarms

- Fully Independent Transmit and Receive Functionality

- Four Separate Loopback Functions

- PRBS Generation/Detection/Error Counting

- 3.3V Low-Power CMOS

- Large Counters for Bipolar and Code Violations, CRC4 Codeword Errors, FAS Word Errors, and E Bits

- Eight Additional User-Configurable Output Pins

- 100-Pin (14mm) LQFP Package

#### **ORDERING INFORMATION**

| PART      | TEMP RANGE     | PIN-PACKAGE |

|-----------|----------------|-------------|

| DS21Q59L  | 0°C to +70°C   | 100 LQFP    |

| DS21Q59LN | -40°C to +85°C | 100 LQFP    |

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <u>www.maxim-ic.com/errata</u>.

## TABLE OF CONTENTS

| 1.          | ACRONYMS                         |    |  |  |  |  |  |

|-------------|----------------------------------|----|--|--|--|--|--|

| 2.          | DETAILED DESCRIPTION             | 6  |  |  |  |  |  |

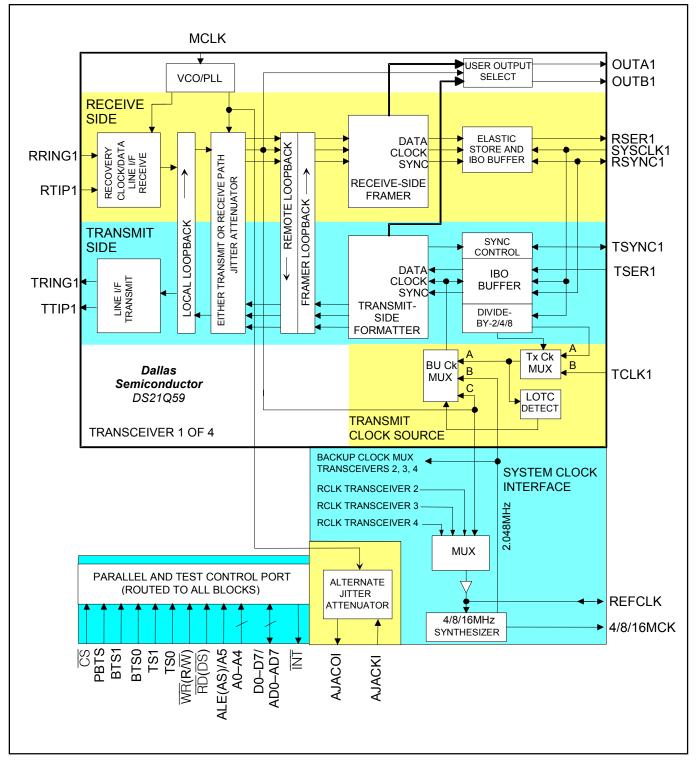

| 3.          | BLOCK DIAGRAM                    | 7  |  |  |  |  |  |

| 4.          | PIN DESCRIPTION                  | 8  |  |  |  |  |  |

| 4.1         | PIN FUNCTION DESCRIPTIONS        | 12 |  |  |  |  |  |

| 5.          | FUNCTIONAL DESCRIPTION           | 13 |  |  |  |  |  |

| <b>6</b> .  | HOST INTERFACE PORT              | 14 |  |  |  |  |  |

| 6.1         | PARALLEL PORT OPERATION          | 14 |  |  |  |  |  |

| 6.2         | SERIAL PORT OPERATION            | 14 |  |  |  |  |  |

| 7.          | REGISTER MAP                     | 16 |  |  |  |  |  |

| 8.          | CONTROL, ID, AND TEST REGISTERS  | 17 |  |  |  |  |  |

| 8.1         | POWER-UP SEQUENCE                | 18 |  |  |  |  |  |

| 8.2         | FRAMER LOOPBACK                  | 21 |  |  |  |  |  |

| 8.3         | AUTOMATIC ALARM GENERATION       | 22 |  |  |  |  |  |

| 8.4         | <b>REMOTE LOOPBACK</b>           | 22 |  |  |  |  |  |

| 8.5         | LOCAL LOOPBACK                   | 23 |  |  |  |  |  |

| 9.          | STATUS AND INFORMATION REGISTERS |    |  |  |  |  |  |

| 9.1         | INTERRUPT HANDLING               | 28 |  |  |  |  |  |

| 9.2         |                                  |    |  |  |  |  |  |

| 10.         | ERROR COUNT REGISTERS            | 34 |  |  |  |  |  |

| 10.         | 1 BPV or CV Counter              | 34 |  |  |  |  |  |

| 10.         |                                  |    |  |  |  |  |  |

| 10.         |                                  | 35 |  |  |  |  |  |

| 10.         |                                  |    |  |  |  |  |  |

| 11.         | SIGNALING OPERATION              |    |  |  |  |  |  |

| 11.         |                                  |    |  |  |  |  |  |

| 11.         |                                  |    |  |  |  |  |  |

| 11.         |                                  |    |  |  |  |  |  |

| 12.         | DS0 MONITORING FUNCTION          |    |  |  |  |  |  |

| 13.         | PRBS GENERATION AND DETECTION    |    |  |  |  |  |  |

| 14.         | SYSTEM CLOCK INTERFACE           | 40 |  |  |  |  |  |

| 15.         | TRANSMIT CLOCK SOURCE            | 41 |  |  |  |  |  |

| <b>16</b> . | IDLE CODE INSERTION              | 41 |  |  |  |  |  |

| 17.                                                         | PER-CHANNEL LOOPBACK                                 | 42                    |

|-------------------------------------------------------------|------------------------------------------------------|-----------------------|

| 18.                                                         | ELASTIC STORE OPERATION                              | 42                    |

| 19.                                                         | ADDITIONAL (Sa) AND INTERNATIONAL (Si) BIT OPERATION | 43                    |

| 20.                                                         | USER-CONFIGURABLE OUTPUTS                            | 45                    |

| 21.                                                         | LINE INTERFACE UNIT                                  | 47                    |

| 21.                                                         | .1 RECEIVE CLOCK AND DATA RECOVERY                   | 47                    |

| 2                                                           | 21.1.1 Termination                                   | 47                    |

| 21.                                                         | 2 TRANSMIT WAVESHAPING AND LINE DRIVING              | 48                    |

| 21.                                                         | 3 JITTER ATTENUATORS                                 | 50                    |

| 2                                                           | 21.3.1 Clock and Data Jitter Attenuators             | 50                    |

| 2                                                           | 21.3.2 Undedicated Clock Jitter Attenuator           |                       |

| <b>22</b> .                                                 | CODE MARK INVERSION (CMI)                            | 52                    |

| 23.                                                         | INTERLEAVED PCM BUS OPERATION                        | 54                    |

| ~ ~                                                         |                                                      |                       |

| 24.                                                         | FUNCTIONAL TIMING DIAGRAMS                           | 56                    |

| <b>24.</b> 24.                                              |                                                      |                       |

|                                                             | 1 RECEIVE                                            | 56                    |

| 24.                                                         | 1 RECEIVE                                            | 56<br>58              |

| 24.<br>24.                                                  | 1 RECEIVE                                            | 56<br>58<br><b>62</b> |

| 24.<br>24.<br><b>25.</b>                                    | 1 RECEIVE<br>2 TRANSMIT<br>OPERATING PARAMETERS      |                       |

| 24.<br>24.<br><b>25.</b><br><b>26.</b>                      | <ol> <li>RECEIVE</li></ol>                           |                       |

| 24.<br>24.<br><b>25.</b><br><b>26.</b><br>26.               | <ol> <li>RECEIVE</li></ol>                           |                       |

| 24.<br>24.<br><b>25.</b><br><b>26.</b><br>26.<br>26.        | <ol> <li>RECEIVE</li></ol>                           |                       |

| 24.<br>24.<br><b>25.</b><br><b>26.</b><br>26.<br>26.        | <ol> <li>RECEIVE</li></ol>                           |                       |

| 24.<br>24.<br><b>25.</b><br>26.<br>26.<br>26.<br>26.        | <ol> <li>RECEIVE</li></ol>                           |                       |

| 24.<br>24.<br><b>25.</b><br>26.<br>26.<br>26.<br>26.<br>26. | <ol> <li>RECEIVE</li></ol>                           |                       |

## LIST OF FIGURES

| Figure 3-1. Block Diagram                                                      | 7  |

|--------------------------------------------------------------------------------|----|

| Figure 6-1. Serial Port Operation Mode 1                                       |    |

| Figure 6-2. Serial Port Operation Mode 2                                       |    |

| Figure 6-3. Serial Port Operation Mode 3                                       |    |

| Figure 6-4. Serial Port Operation Mode 4                                       |    |

| Figure 21-1. External Analog Connections (Basic Configuration)                 | 48 |

| Figure 21-2. External Analog Connections (Protected Interface)                 | 49 |

| Figure 21-3. Transmit Waveform Template                                        | 50 |

| Figure 21-4. Jitter Tolerance                                                  | 51 |

| Figure 21-5. Jitter Attenuation                                                | 51 |

| Figure 22-1. CMI Coding                                                        |    |

| Figure 22-2. Example of CMI Code Violation (CV)                                | 53 |

| Figure 23-1. IBO Configuration Using Two DS21Q59 Transceivers (Eight E1 Lines) | 55 |

| Figure 24-1. Receive Frame and Multiframe Timing                               |    |

| Figure 24-2. Receive Boundary Timing (With Elastic Store Disabled)             | 56 |

| Figure 24-3. Receive Boundary Timing (With Elastic Store Enabled)              | 56 |

| Figure 24-4. Receive Interleave Bus Operation                                  |    |

| Figure 24-5. Transmit Frame and Multiframe Timing                              |    |

| Figure 24-6. Transmit Boundary Timing                                          | 58 |

| Figure 24-7. Transmit Interleave Bus Operation                                 |    |

| Figure 24-8. Framer Synchronization Flowchart                                  |    |

| Figure 24-9. Transmit Data Flow                                                |    |

| Figure 26-1. Intel Bus Read AC Timing (PBTS = 0)                               |    |

| Figure 26-2. Intel Bus Write Timing (PBTS = 0)                                 | 64 |

| Figure 26-3. Motorola Bus AC Timing (PBTS = 1)                                 |    |

| Figure 26-4. Intel Bus Read Timing (PBTS = 0)                                  |    |

| Figure 26-5. Intel Bus Write Timing (PBTS = 0)                                 | 67 |

| Figure 26-6. Motorola Bus Read Timing (PBTS = 1)                               |    |

| Figure 26-7. Motorola Bus Write Timing (PBTS = 1)                              |    |

| Figure 26-8. Serial Bus Timing (BTS1 = 1, BTS0 = 0)                            | 68 |

| Figure 26-9. Receive AC Timing (Receive Elastic Store Disabled)                | 70 |

| Figure 26-10. Receive AC Timing (Receive Elastic Store Enabled)                | 71 |

| Figure 22-11. Transmit AC Timing (IBO Disabled)                                | 73 |

| Figure 22-12. Transmit AC Timing (IBO Enabled)                                 |    |

| Figure 26-13. NRZ Input AC Timing                                              | 74 |

## LIST OF TABLES

| Table 4-A. Pin Description (Sorted by Function)                 | 8   |

|-----------------------------------------------------------------|-----|

| Table 4-B. Pin Assignments (Sorted by Number)                   | .10 |

| Table 4-C. System (Backplane) Interface Pins                    | .12 |

| Table 4-D. Alternate Jitter Attenuator                          | .12 |

| Table 4-E. Clock Synthesizer                                    | .12 |

| Table 4-F. Parallel Port Control Pins                           | .12 |

| Table 4-G. Serial Port Control Pins                             | .13 |

| Table 4-H. Line Interface Pins                                  | .13 |

| Table 4-I. Supply Pins                                          | .13 |

| Table 6-A. Bus Mode Select                                      | 14  |

| Table 7-A. Register Map (Sorted by Address)                     | .16 |

| Table 8-A. Sync/Resync Criteria                                 | .19 |

| Table 8-B. G.703 Function                                       |     |

| Table 8-C. Output Modes                                         | 25  |

| Table 9-A. Alarm Criteria                                       |     |

| Table 13-A. Transmit PRBS Mode Select                           |     |

| Table 13-B. Receive PRBS Mode Select                            |     |

| Table 14-A. Synthesizer Output Select                           | .40 |

| Table 14-B. System Clock Selection                              |     |

| Table 20-A. OUTA and OUTB Function Select                       |     |

| Table 21-A. Line Build-Out Select in LICR                       |     |

| Table 21-B. Transformer Specifications                          | .48 |

| Table 23-A. IBO System Clock Select                             |     |

| Table 23-B. IBO Device Assignment                               | 54  |

| Table 26-A. AC Characteristics—Multiplexed Parallel Port        |     |

| Table 26-B. AC Characteristics—Nonmultiplexed Parallel Port     |     |

| Table 26-C. AC Characteristics—Serial Port (BTS1 = 1, BTS0 = 0) |     |

| Table 26-D. AC Characteristics—Receiver                         |     |

| Table 26-E. AC Characteristics—Transmit                         |     |

| Table 26-F. AC Characteristics—Special Modes                    | 74  |

## 1. ACRONYMS

The following abbreviations are used throughout this data sheet:

| FAS   | Frame Alignment Signal                                                                                                                                                |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAS   | Channel Associated Signaling                                                                                                                                          |

| MF    | Multiframe                                                                                                                                                            |

| Si    | International Bits                                                                                                                                                    |

| CRC4  | Cyclical Redundancy Check                                                                                                                                             |

| CCS   | Common Channel Signaling                                                                                                                                              |

| Sa    | Additional bits                                                                                                                                                       |

| E-Bit | CRC4 Error Bits                                                                                                                                                       |

| LOC   | Loss of Clock                                                                                                                                                         |

| TCLK  | This generally refers to the transmit rate clock and can reference an actual input signal to the device (TCLK) or an internally derived signal used for transmission. |

| RCLK  | This generally refers to the recovered network clock and can be a reference to an actual output signal from the device or an internal signal.                         |

#### 2. DETAILED DESCRIPTION

The LIU is composed of a transmit interface, receive interface, and a jitter attenuator. The transmit interface generates the necessary waveshapes for driving the network, depending on the type of media used. E1 waveform generation includes G.703 waveshapes for both  $75\Omega$  coax and  $120\Omega$  twisted cables. The receive interface recovers clock and data from the network. The receive sensitivity adjusts automatically to the incoming signal. The jitter attenuator removes phase jitter from the transmitted or received signal. The crystal-less jitter attenuator only requires a 2.048MHz MCLK and can be placed in either the transmit or receive data paths. An additional feature of the LIU is a code mark inversion (CMI) coder/decoder for interfacing to optical networks.

On the transmit side, the backplane interface section provides clock/data and frame-sync signals to the framer. The framer inserts the appropriate synchronization framing patterns, alarm information, calculates and inserts the CRC codes, and provides the HDB3 (zero code suppression) and alternate mark inversion (AMI) line coding. The receive-side framer decodes AMI and HDB3 line coding, synchronizes to the data stream, reports alarm information, counts framing/coding/CRC errors, and provides clock/data and frame-sync signals to the backplane interface section.

The backplane interface provides a versatile method of sending and receiving data from the host system. The receive elastic store provides a method for interfacing to asynchronous systems. The elastic store also manages slip conditions (asynchronous interface). An interleave bus option (IBO) is provided to allow multiple E1 lines to share a high-speed backplane.

The parallel port provides access for control and configuration of all the DS21Q59's features. Diagnostic capabilities include loopbacks, PRBS pattern generation/detection, and 16-bit loop-up and loop-down code generation and detection. The device fully meets all the latest E1 specifications, including ITU-T G.703, G.704, G.706, G.823, G.732 and I.431 ETS 300 011, ETS 300 233, and ETS 300 166 as well as CTR12 and CTR4.

The DS21Q59 is optimized for high-density termination of E1 lines. Two significant features are included for this type of application: the IBO and a system clock synthesizer feature. The IBO allows up to eight E1 data streams to be multiplexed onto a single high-speed PCM bus without additional external logic. The system clock synthesizer allows any of the E1 lines to be selected as the master source of the clock for the system and for all the transmitters. This is also accomplished without the need of external logic. Each of the four transceivers has a clock and data jitter attenuator that can be assigned to either the transmit or receive path. In addition there is a single, undedicated clock jitter attenuator that can be hardware configured as needed by the user. Each transceiver also contains a PRBS pattern generator and detector. Figure 23-1 shows a simplified typical application that terminates eight E1 lines (transmit and receive pairs) and combines the data into a single 16.384MHz PCM bus. The 16.384MHz system clock is derived and phase-locked to one of the eight E1 lines. On the receive side of each port, an elastic store provides logical management of any slip conditions due to the asynchronous relationship of the eight E1 lines. In this application all eight transmitters are timed to the selected E1 line.

## 3. BLOCK DIAGRAM

#### Figure 3-1. Block Diagram

## 4. PIN DESCRIPTION

Table 4-A. Pin Description (Sorted by Function)

| PIN | NAME                     |                        |            |                                                            |

|-----|--------------------------|------------------------|------------|------------------------------------------------------------|

| FIN | PARALLEL<br>PORT ENABLED | SERIAL PORT<br>ENABLED | TYPE       | FUNCTION<br>[SERIAL PORT MODE IN BRACKETS]                 |

| 71  | 4/8/16MCK                | —                      | 0          | 4.096MHz, 8.192MHz, or 16.384MHz Clock                     |

| 45  | A0                       | ICES                   |            | Address Bus Bit 0/Serial Port [Input-Clock Edge Select]    |

| 46  | A1                       | OCES                   |            | Address Bus Bit 1/Serial Port [Output-Clock Edge Select]   |

| 47  | A2                       | —                      |            | Address Bus Bit 2                                          |

| 48  | A3                       | —                      |            | Address Bus Bit 3                                          |

| 49  | A4                       | —                      |            | Address Bus Bit 4                                          |

| 70  | AJACKI                   | —                      |            | Alternate Jitter Attenuator Clock Input                    |

| 69  | AJACKO                   | —                      | 0          | Alternate Jitter Attenuator Clock Output                   |

| 50  | ALE (AS)/A5              | —                      |            | Address Latch Enable/Address Bus Bit 5                     |

| 96  | BTS0                     | —                      |            | Bus Type Select 0                                          |

| 97  | BTS1                     | —                      |            | Bus Type Select 1                                          |

| 98  | CS                       | _                      |            | Chip Select                                                |

| 19  | D0/AD0                   | _                      | I/O        | Data Bus Bit 0/Address/Data Bus Bit 0                      |

| 20  | D1/AD1                   | _                      | I/O        | Data Bus Bit 1/Address/Data Bus Bit 1                      |

| 21  | D2/AD2                   | _                      | I/O        | Data Bus Bit 2/Address/Data Bus Bit 2                      |

| 22  | D3/AD3                   | _                      | I/O        | Data Bus Bit 3/Address/Data Bus Bit 3                      |

| 23  | D4/AD4                   |                        | I/O        | Data Bus Bit 4/Address/Data Bus Bit 4                      |

| 24  | D5/AD5                   | _                      | I/O        | Data Bus Bit 5/Address/Data Bus Bit 5                      |

| 25  | D6/AD6                   |                        | I/O        | Data Bus Bit 6/Address/Data Bus Bit 6                      |

| 44  | D7/AD7                   | SDO                    | I/O        | Data Bus Bit 7/Address/Data Bus Bit 7 [Serial Data Output] |

| 84  | DVDD1                    |                        | 1 <u> </u> | Digital Positive Supply                                    |

| 59  | DVDD2                    | _                      | —          | Digital Positive Supply                                    |

| 34  | DVDD3                    |                        | —          | Digital Positive Supply                                    |

| 9   | DVDD4                    |                        | 1 <u> </u> | Digital Positive Supply                                    |

| 83  | DVSS1                    | _                      | _          | Digital Signal Ground                                      |

| 58  | DVSS2                    |                        | 1 <u> </u> | Digital Signal Ground                                      |

| 33  | DVSS3                    | _                      | —          | Digital Signal Ground                                      |

| 8   | DVSS4                    |                        | 1 <u> </u> | Digital Signal Ground                                      |

| 94  | INT                      | _                      | 0          | Interrupt                                                  |

| 73  | MCLK                     |                        |            | Master Clock Input                                         |

| 61  | OUTA1                    |                        | 0          | User-Selectable Output A                                   |

| 36  | OUTA2                    |                        | 0          | User-Selectable Output A                                   |

| 11  | OUTA3                    |                        | 0          | User-Selectable Output A                                   |

| 86  | OUTA4                    |                        | 0          | User-Selectable Output A                                   |

| 60  | OUTB1                    |                        | 0          | User-Selectable Output B                                   |

| 35  | OUTB2                    | _                      | 0          | User-Selectable Output B                                   |

| 10  | OUTB3                    | _                      | 0          | User-Selectable Output B                                   |

| 85  | OUTB4                    | —                      | 0          | User-Selectable Output B                                   |

| 95  | PBTS                     | —                      |            | Parallel Bus Type Select                                   |

| 75  | RD (DS)                  | SCLK                   |            | Read Input (Data Strobe) [Serial Port Clock]               |

| 72  | REFCLK                   | _                      | I/O        | Reference Clock                                            |

| 67  | RRING1                   | _                      |            | Receive Analog Ring Input                                  |

| 42  | RRING2                   | _                      | 1          | Receive Analog Ring Input                                  |

| 17  | RRING3                   | _                      |            | Receive Analog Ring Input                                  |

| 92  | RRING4                   | _                      |            | Receive Analog Ring Input                                  |

| 63  | RSER1                    |                        | 0          | Receive Serial Data                                        |

| 38  | RSER2                    | _                      | 0          | Receive Serial Data                                        |

| 13  | RSER3                    |                        | 0          | Receive Serial Data                                        |

| 88  | RSER4                    |                        | 0          | Receive Serial Data                                        |

| 64  | RSYNC1                   |                        | 1/0        | Receive Sync                                               |

| 39  | RSYNC2                   |                        | I/O        | Receive Sync                                               |

| 14  | RSYNC3                   |                        | 1/O        | Receive Sync                                               |

|         | NA                                                 | NAME                   |          | <b>EUNIQUION</b>                                         |

|---------|----------------------------------------------------|------------------------|----------|----------------------------------------------------------|

| PIN     | PARALLEL<br>PORT ENABLED                           | SERIAL PORT<br>ENABLED | TYPE     | FUNCTION<br>[SERIAL PORT MODE IN BRACKETS]               |

| 89      | RSYNC4                                             | _                      | I/O      | Receive Sync                                             |

| 66      | RTIP1                                              | _                      | I        | Receive Analog Tip Input                                 |

| 41      | RTIP2                                              | _                      | I        | Receive Analog Tip Input                                 |

| 16      | RTIP3                                              |                        |          | Receive Analog Tip Input                                 |

| 91      | RTIP4                                              |                        | I        | Receive Analog Tip Input                                 |

| 93      | RVDD1                                              | _                      |          | Receive Analog Positive Supply                           |

| 68      | RVDD2                                              |                        |          | Receive Analog Positive Supply                           |

| 43      | RVDD3                                              | _                      |          | Receive Analog Positive Supply                           |

| 18      | RVDD4                                              |                        |          | Receive Analog Positive Supply                           |

| 90      | RVSS1                                              | _                      |          | Receive Analog Signal Ground                             |

| 65      | RVSS2                                              | _                      | _        | Receive Analog Signal Ground                             |

| 40      | RVSS3                                              | _                      | _        | Receive Analog Signal Ground                             |

| 15      | RVSS4                                              | _                      | _        | Receive Analog Signal Ground                             |

| 62      | SYSCLK1                                            | _                      | I        | Transmit/Receive System Clock                            |

| 37      | SYSCLK2                                            |                        |          | Transmit/Receive System Clock                            |

| 12      | SYSCLK3                                            |                        |          | Transmit/Receive System Clock                            |

| 87      | SYSCLK4                                            |                        |          | Transmit/Receive System Clock                            |

| 80      | TCLK1                                              |                        | i        | Transmit Clock                                           |

| 55      | TCLK2                                              |                        | i        | Transmit Clock                                           |

| 30      | TCLK3                                              |                        | i        | Transmit Clock                                           |

| 5       | TCLK4                                              | _                      | · ·      | Transmit Clock                                           |

| 79      | TRING1                                             |                        | 0        | Transmit Analog Ring Output                              |

| 54      | TRING2                                             |                        | 0        | Transmit Analog Ring Output                              |

| 29      | TRING3                                             |                        | 0        | Transmit Analog Ring Output                              |

| 4       | TRING4                                             |                        | 0        | Transmit Analog Ring Output                              |

| 99      | TS0                                                |                        | 1        | Transceiver Select 0                                     |

| 100     | TS1                                                | _                      | 1        | Transceiver Select 1                                     |

| 81      | TSER1                                              |                        | 1        | Transmit Serial Data                                     |

| 56      | TSER2                                              |                        | 1        | Transmit Serial Data                                     |

| 31      | TSER3                                              |                        | 1        | Transmit Serial Data                                     |

| 6       | TSER4                                              |                        |          | Transmit Serial Data                                     |

| 82      | TSYNC1                                             |                        | I/O      | Transmit Sync                                            |

| 57      | TSYNC2                                             |                        | 1/O      | Transmit Sync                                            |

| 32      | TSYNC3                                             |                        | I/O      | Transmit Sync                                            |

| 7       | TSYNC4                                             |                        | 1/O      | Transmit Sync                                            |

| 76      | TTIP1                                              |                        | 0        | Transmit Sync                                            |

| 51      | TTIP1                                              |                        | 0        | Transmit Analog Tip Output                               |

| 26      | TTIP2                                              | _                      | 0        |                                                          |

| <u></u> | TTIP3                                              |                        | 0        | Transmit Analog Tip Output<br>Transmit Analog Tip Output |

|         |                                                    |                        |          |                                                          |

| 78      | TVDD1<br>TVDD2                                     | —                      | —        | Transmit Analog Positive Supply                          |

| 53      | TVDD2                                              |                        |          | Transmit Analog Positive Supply                          |

| 28      | TVDD3                                              | —                      | —        | Transmit Analog Positive Supply                          |

| 3       | TVDD4                                              | —                      | -        | Transmit Analog Positive Supply                          |

| 77      | TVSS1                                              |                        |          | Transmit Analog Signal Ground                            |

| 52      | TVSS2                                              | —                      | <u> </u> | Transmit Analog Signal Ground                            |

| 27      | TVSS3                                              | _                      |          | Transmit Analog Signal Ground                            |

| 2       | TVSS4                                              | —                      |          | Transmit Analog Signal Ground                            |

| 74      | $\overline{\text{WR}}$ (R/ $\overline{\text{W}}$ ) | SDI                    |          | Write Input (Read/Write) [Serial Data Input]             |

Note: EQVSS lines are wired to RVSS lines.

|     | NAME                     |                        |      |                                                            |

|-----|--------------------------|------------------------|------|------------------------------------------------------------|

| PIN | PARALLEL<br>PORT ENABLED | SERIAL PORT<br>ENABLED | TYPE | FUNCTION<br>[Serial Port Mode in Brackets]                 |

| 1   | TTIP4                    |                        | 0    | Transmit Analog Tip Output                                 |

| 2   | TVSS4                    | —                      | _    | Transmit Analog Signal Ground                              |

| 3   | TVDD4                    | —                      | _    | Transmit Analog Positive Supply                            |

| 4   | TRING4                   | _                      | 0    | Transmit Analog Ring Output                                |

| 5   | TCLK4                    | _                      | I    | Transmit Clock                                             |

| 6   | TSER4                    | —                      | I    | Transmit Serial Data                                       |

| 7   | TSYNC4                   | —                      | I/O  | Transmit Sync                                              |

| 8   | DVSS4                    | —                      |      | Digital Signal Ground                                      |

| 9   | DVDD4                    | —                      | _    | Digital Positive Supply                                    |

| 10  | OUTB3                    | —                      | 0    | User-Selectable Output B                                   |

| 11  | OUTA3                    | —                      | 0    | User-Selectable Output A                                   |

| 12  | SYSCLK3                  | —                      | Ι    | Transmit/Receive System Clock                              |

| 13  | RSER3                    | —                      | 0    | Receive Serial Data                                        |

| 14  | RSYNC3                   | —                      | I/O  | Receive Sync                                               |

| 15  | RVSS4                    | —                      | _    | Receive Analog Signal Ground                               |

| 16  | RTIP3                    | —                      | I    | Receive Analog Tip Input                                   |

| 17  | RRING3                   | _                      | I    | Receive Analog Ring Input                                  |

| 18  | RVDD4                    | —                      | _    | Receive Analog Positive Supply                             |

| 19  | D0/AD0                   | _                      | I/O  | Data Bus Bit 0/Address/Data Bus Bit 0                      |

| 20  | D1/AD1                   | —                      | I/O  | Data Bus Bit 1/Address/Data Bus Bit 1                      |

| 21  | D2/AD2                   | _                      | I/O  | Data Bus Bit 2/Address/Data Bus Bit 2                      |

| 22  | D3/AD3                   | _                      | I/O  | Data Bus Bit 3/Address/Data Bus Bit 3                      |

| 23  | D4/AD4                   | _                      | I/O  | Data Bus Bit 4/Address/Data Bus Bit 4                      |

| 24  | D5/AD5                   | _                      | I/O  | Data Bus Bit 5/Address/Data Bus Bit 5                      |

| 25  | D6/AD6                   | _                      | I/O  | Data Bus Bit 6/Address/Data Bus Bit 6                      |

| 26  | TTIP3                    | _                      | 0    | Transmit Analog Tip Output                                 |

| 27  | TVSS3                    | _                      | _    | Transmit Analog Signal Ground                              |

| 28  | TVDD3                    | —                      | _    | Transmit Analog Positive Supply                            |

| 29  | TRING3                   | —                      | 0    | Transmit Analog Ring Output                                |

| 30  | TCLK3                    | —                      | I    | Transmit Clock                                             |

| 31  | TSER3                    | —                      | I    | Transmit Serial Data                                       |

| 32  | TSYNC3                   | —                      | I/O  | Transmit Sync                                              |

| 33  | DVSS3                    | —                      |      | Digital Signal Ground                                      |

| 34  | DVDD3                    | —                      | _    | Digital Positive Supply                                    |

| 35  | OUTB2                    | —                      | 0    | User-Selectable Output B                                   |

| 36  | OUTA2                    | —                      | 0    | User-Selectable Output A                                   |

| 37  | SYSCLK2                  | —                      | Ι    | Transmit/Receive System Clock                              |

| 38  | RSER2                    |                        | 0    | Receive Serial Data                                        |

| 39  | RSYNC2                   | _                      | I/O  | Receive Sync                                               |

| 40  | RVSS3                    | —                      | _    | Receive Analog Signal Ground                               |

| 41  | RTIP2                    | —                      | I    | Receive Analog Tip Input                                   |

| 42  | RRING2                   | —                      | I    | Receive Analog Ring Input                                  |

| 43  | RVDD3                    | _                      | —    | Receive Analog Positive Supply                             |

| 44  | D7/AD7                   | SDO                    | I/O  | Data Bus Bit 7/Address/Data Bus Bit 7 [Serial Data Output] |

| 45  | A0                       | ICES                   | I    | Address Bus Bit 0/Serial Port [Input-Clock Edge Select]    |

| 46  | A1                       | OCES                   | I    | Address Bus Bit 1/Serial Port [Output-Clock Edge Select]   |

| 47  | A2                       | _                      | I    | Address Bus Bit 2                                          |

| 48  | A3                       | —                      |      | Address Bus Bit 3                                          |

| 49  | A4                       | _                      |      | Address Bus Bit 4                                          |

| 50  | ALE (AS)/A5              | _                      | I    | Address Latch Enable/Address Bus Bit 5                     |

| 51  | TTIP2                    | _                      | 0    | Transmit Analog Tip Output                                 |

| 52  | TVSS2                    | _                      |      | Transmit Analog Signal Ground                              |

| 53  | TVDD2                    | _                      | —    | Transmit Analog Positive Supply                            |

| 54  | TRING2                   | —                      | 0    | Transmit Analog Ring Output                                |

Table 4-B. Pin Assignments (Sorted by Number)

| NAME |                                                    | ΛE                     |      | FUNCTION                                     |

|------|----------------------------------------------------|------------------------|------|----------------------------------------------|

| PIN  | PARALLEL<br>PORT ENABLED                           | SERIAL PORT<br>ENABLED | TYPE | FUNCTION<br>[Serial Port Mode in Brackets]   |

| 55   | TCLK2                                              | _                      | I    | Transmit Clock                               |

| 56   | TSER2                                              | _                      | I    | Transmit Serial Data                         |

| 57   | TSYNC2                                             | _                      | I/O  | Transmit Sync                                |

| 58   | DVSS2                                              | _                      | —    | Digital Signal Ground                        |

| 59   | DVDD2                                              | —                      | —    | Digital Positive Supply                      |

| 60   | OUTB1                                              | _                      | 0    | User-Selectable Output B                     |

| 61   | OUTA1                                              |                        | 0    | User-Selectable Output A                     |

| 62   | SYSCLK1                                            | _                      | I    | Transmit/Receive System Clock                |

| 63   | RSER1                                              |                        | 0    | Receive Serial Data                          |

| 64   | RSYNC1                                             | _                      | I/O  | Receive Sync                                 |

| 65   | RVSS2                                              | _                      | —    | Receive Analog Signal Ground                 |

| 66   | RTIP1                                              |                        | I    | Receive Analog Tip Input                     |

| 67   | RRING1                                             | —                      | I    | Receive Analog Ring Input                    |

| 68   | RVDD2                                              | _                      | —    | Receive Analog Positive Supply               |

| 69   | AJACKO                                             | —                      | 0    | Alternate Jitter Attenuator Clock Output     |

| 70   | AJACKI                                             | _                      | I    | Alternate Jitter Attenuator Clock Input      |

| 71   | 4/8/16MCK                                          | _                      | 0    | 4.096MHz, 8.192MHz, or 16.384MHz Clock       |

| 72   | REFCLK                                             | _                      | I/O  | Reference Clock                              |

| 73   | MCLK                                               | _                      | I    | Master Clock Input                           |

| 74   | $\overline{\text{WR}}$ (R/ $\overline{\text{W}}$ ) | SDI                    | I    | Write Input (Read/Write) [Serial Data Input] |

| 75   | RD (DS)                                            | SCLK                   | I    | Read Input (Data Strobe) [Serial Port Clock] |

| 76   | TTIP1                                              | _                      | 0    | Transmit Analog Tip Output                   |

| 77   | TVSS1                                              | _                      | _    | Transmit Analog Signal Ground                |

| 78   | TVDD1                                              | _                      | _    | Transmit Analog Positive Supply              |

| 79   | TRING1                                             | _                      | 0    | Transmit Analog Ring Output                  |

| 80   | TCLK1                                              | _                      | I    | Transmit Clock                               |

| 81   | TSER1                                              | _                      | I    | Transmit Serial Data                         |

| 82   | TSYNC1                                             | _                      | I/O  | Transmit Sync                                |

| 83   | DVSS1                                              | _                      | —    | Digital Signal Ground                        |

| 84   | DVDD1                                              | _                      | —    | Digital Positive Supply                      |

| 85   | OUTB4                                              | _                      | 0    | User-Selectable Output B                     |

| 86   | OUTA4                                              | _                      | 0    | User-Selectable Output A                     |

| 87   | SYSCLK4                                            |                        | I    | Transmit/Receive System Clock                |

| 88   | RSER4                                              | _                      | 0    | Receive Serial Data                          |

| 89   | RSYNC4                                             | _                      | I/O  | Receive Sync                                 |

| 90   | RVSS1                                              |                        | _    | Receive Analog Signal Ground                 |

| 91   | RTIP4                                              | _                      | I    | Receive Analog Tip Input                     |

| 92   | RRING4                                             | —                      | I    | Receive Analog Ring Input                    |

| 93   | RVDD1                                              | —                      | _    | Receive Analog Positive Supply               |

| 94   | ĪNT                                                | —                      | 0    | Interrupt                                    |

| 95   | PBTS                                               | _                      | I    | Parallel Bus Type Select                     |

| 96   | BTS0                                               |                        | _    | Bus Type Select 0                            |

| 97   | BTS1                                               | _                      | _    | Bus Type Select 1                            |

| 98   | CS                                                 |                        | I    | Chip Select                                  |

| 99   | TS0                                                |                        | l    | Transceiver Select 0                         |

| 100  | TS1                                                |                        | I    | Transceiver Select 1                         |

Note: EQVSS lines are wired to RVSS.

## 4.1 Pin Function Descriptions

| NAME   | TYPE | FUNCTION                                                                                                                                                                                                                                                                                        |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLK   | I    | <b>Transmit Clock.</b> TCLK is a 2.048MHz primary clock that is used to clock data through the transmit formatter.                                                                                                                                                                              |

| TSER   | Ι    | <b>Transmit Serial Data.</b> Transmit NRZ serial data. TSER is sampled on the falling edge of TCLK when IBO disabled. It is sampled on the falling edge of SYSCLK when the IBO function is enabled.                                                                                             |

| TSYNC  | I/O  | <b>Transmit Sync.</b> As an input, pulse at this pin establishes either frame or multiframe boundaries for the transmitter. As an output, it can be programmed to output either a frame or multiframe pulse.                                                                                    |

| RSER   | 0    | <b>Receive Serial Data.</b> RSER is the received NRZ serial data. RSER is updated on the rising edges of RCLK when the receive elastic store is disabled. It is updated on the rising edges of SYSCLK when the receive elastic store is enabled.                                                |

| RSYNC  | I/O  | <b>Receive Sync.</b> An extracted pulse one RCLK wide is output at this pin that identifies either frame or CAS/CRC4 multiframe boundaries. If the receive elastic store is enabled, this pin can be enabled to be an input at which a frame-boundary pulse synchronous with SYSCLK is applied. |

| SYSCLK | I    | <b>System Clock.</b> SYSCLK is a 2.048MHz clock used to clock data out of the receive elastic store. When the IBO is enabled SYSCLK can be a 4.096MHz, 8.192MHz, or 16.384MHz clock.                                                                                                            |

| OUTA   | 0    | <b>User-Selectable Output A.</b> OUTA is a multifunction pin the host can program to output various alarms, clocks, or data, or be used to control external circuitry.                                                                                                                          |

| OUTB   | 0    | <b>User-Selectable Output B.</b> OUTB is a multifunction pin the host can program to output various alarms, clocks, or data, or be used to control external circuitry.                                                                                                                          |

#### Table 4-C. System (Backplane) Interface Pins

#### Table 4-D. Alternate Jitter Attenuator

| NAME   | TYPE | FUNCTION                                                                                             |

|--------|------|------------------------------------------------------------------------------------------------------|

| AJACKI | I    | Alternate Jitter Attenuator Clock Input. AJACKI is clock input to the alternate jitter attenuator.   |

| AJACKO | 0    | Alternate Jitter Attenuator Clock Output. AJACKO is clock output of the alternate jitter attenuator. |

#### Table 4-E. Clock Synthesizer

| NAME      | TYPE | FUNCTION                                                                                                                                                                                                                |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4/8/16MCK | 0    | <b>4.096MHz/8.192MHz/16.384MHz Clock Output.</b> 4/8/16MCK is a 4.096MHz, 8.192MHz, or 16.384MHz clock output that is referenced to one of the four recovered line clocks (RCLKs) or to an external 2.048MHz reference. |

| REFCLK    | I/O  | <b>Reference Clock.</b> REFCLK can be configured as an output to source a 2.048MHz reference clock or as an input to supply a 2.048MHz reference clock from an external source to the clock synthesizer.                |

#### Table 4-F. Parallel Port Control Pins

| NAME              | TYPE | FUNCTION                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ĪNT               | 0    | Interrupt. INT flags the host controller during conditions and change of conditions defined in status registers 1 and 2 and the HDLC status register. It is an active-low, open-drain output.                                                                                      |  |  |  |  |  |

| BTS0              | I    | <b>Bus Type Select Bit 0.</b> BTS0 is used with BTS1 to select between muxed, nonmuxed, serial bus operation, and output high-Z mode.                                                                                                                                              |  |  |  |  |  |

| BTS1              | I    | <b>Bus Type Select Bit 1.</b> BTS1 is used with BTS0 to select between muxed, nonmuxed, serial bus operation, and output high-Z mode.                                                                                                                                              |  |  |  |  |  |

| TS0               | I    | Transceiver Select Bit 0. TS0 is used with TS1 to select one of four transceivers.                                                                                                                                                                                                 |  |  |  |  |  |

| TS1               | I    | Transceiver Select Bit 1. TS1 is used with TS0 to select one of four transceivers.                                                                                                                                                                                                 |  |  |  |  |  |

| PBTS              | I    | Parallel Bus Type Select. PBTS is used to select between Motorola and Intel parallel bus types.                                                                                                                                                                                    |  |  |  |  |  |

| AD0 to<br>AD7/SDO | I/O  | <b>Data Bus or Address/Data Bus [D0 to D6], Data Bus or Address/Data Bus [D7]/Serial Port Output.</b><br>In nonmultiplexed bus operation (MUX = 0), these pins serve as the data bus. In multiplexed bus operation (MUX = 1), they serve as an 8-bit multiplexed address/data bus. |  |  |  |  |  |

| A0 to A4          | I    | Address Bus. In nonmultiplexed bus operation, these pins serve as the address bus. In multiplexed bus operation, these pins are not used and should be wired low.                                                                                                                  |  |  |  |  |  |

| RD (DS)/SCLK      | I    | <b>Read Input—Data Strobe/Serial Port Clock.</b> RD and DS are active-low signals. DS is active high when in multiplexed mode (Section <u>26</u> ).                                                                                                                                |  |  |  |  |  |

| CS                | I    | Chip Select. $\overline{CS}$ must be low to read or write to the device. It is an active-low signal.                                                                                                                                                                               |  |  |  |  |  |

| ALE (AS)/A5       | I    | Address Latch Enable (Address Strobe) or A6. In nonmultiplexed bus operation, this pin serves as the upper address bit. In multiplexed bus operation, it demultiplexes the bus on a positive-going edge.                                                                           |  |  |  |  |  |

| WR (R/W)/SDI      | I    | Write Input (Read/Write)/Serial Port Data Input, Active Low                                                                                                                                                                                                                        |  |  |  |  |  |

#### Table 4-G. Serial Port Control Pins

| NAME | TYPE | FUNCTION                                                                                           |  |  |  |  |

|------|------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| SDO  | 0    | Serial Port Data Output. Data at this output can be updated on the rising or falling edge of SCLK. |  |  |  |  |

| SDI  | I    | Serial Port Data Input. Data at this input can be sampled on the rising or falling edge of SCLK.   |  |  |  |  |

| ICES | 1    | Input Clock-Edge Select. ICES is used to select which SCLK clock edge samples data at SDI.         |  |  |  |  |

| OCES | I    | Output Clock-Edge Select. OCES is used to select which SCLK clock edge updates data at SDO.        |  |  |  |  |

| SCLK | I    | Serial Port Clock. SCLK is used to clock data into and out of the serial port.                     |  |  |  |  |

#### Table 4-H. Line Interface Pins

| NAME              | TYPE | FUNCTION                                                                                                                                                                                            |  |  |  |  |

|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MCLK              | I    | Master Clock Input. A 2.048MHz (±50ppm) clock source with TTL levels is applied at this pin. This clock is used internally for both clock/data recovery and for jitter attenuation.                 |  |  |  |  |

| RTIP and<br>RRING | I    | <b>Receive Tip and Ring.</b> RTIP and RRING are analog inputs for clock recovery circuitry. These pins connect through a 1:1 step-up transformer to the E1 line. See Section <u>21</u> for details. |  |  |  |  |

| TTIP and<br>TRING | 0    | <b>Transmit Tip and Ring.</b> TTIP and TRING are analog line-driver outputs. These pins connect through a 1:2 step-up transformer to the E1 line. See Section <u>21</u> for details.                |  |  |  |  |

#### Table 4-I. Supply Pins

| NAME | TYPE   | FUNCTION                                                                              |

|------|--------|---------------------------------------------------------------------------------------|

| DVDD | Supply | Digital Positive Supply. 3.3V ±5%. Should be wired to the RVDD and TVDD pins.         |

| RVDD | Supply | Receive Analog Positive Supply. 3.3V ±5%. Should be wired to the DVDD and TVDD pins.  |

| TVDD | Supply | Transmit Analog Positive Supply. 3.3V ±5%. Should be wired to the RVDD and DVDD pins. |

| DVSS | Supply | Digital Signal Ground. 0V. Should be wired to the RVSS and TVSS pins.                 |

| RVSS | Supply | Receive Analog Signal Ground. 0V. Should be wired to DVSS and TVSS.                   |

| TVSS | Supply | Transmit Analog Signal Ground. 0V. Should be wired to DVSS and RVSS.                  |

## 5. FUNCTIONAL DESCRIPTION

The analog AMI/HDB3 waveform off the E1 line is transformer-coupled into the DS21Q59's RRING and RTIP pins. The device recovers clock and data from the analog signal and passes it through the jitter attenuation mux to the receive framer, where the digital serial stream is analyzed to locate the framing/multiframe pattern. The DS21Q59 contains an active filter that reconstructs the analog-received signal for the nonlinear losses that occur in transmission. The device has a usable receive sensitivity of 0dB to -43dB, which allows the device to operate on cables over 2km in length. The receive framer locates FAS frame and CRC and CAS multiframe boundaries as well as detects incoming alarms including carrier loss, loss of synchronization, AIS, and remote alarm. If needed, the receive elastic store can be enabled to absorb the phase and frequency differences between the recovered E1 data stream and an asynchronous backplane clock, which is provided at the SYSCLK input. The clock applied at the SYSCLK input can be either a 2.048MHz/4.096MHz/8.192MHz or 16.384MHz clock. The transmit framer is independent of the receive framer in both the clock requirements and characteristics. The transmit formatter provides the necessary frame/multiframe data overhead for E1 transmission.

**Note:** This data sheet assumes a particular nomenclature of the E1 operating environment. In each 125µs frame, there are 32 8-bit time slots numbered 0 to 31. Time slot 0 is transmitted first and received first. These 32 time slots are also referred to as channels with a numbering scheme of 1 to 32. Time slot 0 is identical to channel 1, time slot 1 is identical to channel 2, and so on. Each time slot (or channel) is made up of eight bits that are numbered 1 to 8. Bit number 1, MSB, is transmitted first. Bit number 8, the LSB, is transmitted last. The term "locked" is used to refer to two clock signals that are phase-locked or frequency-locked or derived from a common clock (i.e., an 8.192MHz clock can be locked to a 2.048MHz clock if they share the same 8kHz component).

## 6. HOST INTERFACE PORT

The DS21Q59 is controlled through either a nonmultiplexed bus, a multiplexed bus, or serial interface bus by an external microcontroller or microprocessor. The device can operate with either Intel or Motorola bus timing configurations. See <u>Table 6-A</u> for a description of the bus configurations. Motorola bus signals are listed in parentheses (). See the timing diagrams in the *AC Electrical Characteristics* in Section <u>26</u> for more details.

| PBTS | BTS1 | BTS0 | PARALLEL PORT MODE      |

|------|------|------|-------------------------|

| 0    | 0    | 0    | Intel Multiplexed       |

| 0    | 0    | 1    | Intel Nonmultiplexed    |

| 1    | 0    | 0    | Motorola Multiplexed    |

| 1    | 0    | 1    | Motorola Nonmultiplexed |

| Х    | 1    | 0    | Serial                  |

| Х    | 1    | 1    | TEST (Outputs High-Z)   |

#### Table 6-A. Bus Mode Select

#### 6.1 Parallel Port Operation

When using the parallel interface on the DS21Q59 (BTS1 = 0) the user has the option for either multiplexed bus operation (BTS1 = 0, BTS0 = 0) or nonmultiplexed bus operation (BTS1 = 0, BTS0 = 1). The DS21Q59 can operate with either Intel or Motorola bus timing configurations. If the PBTS pin is wired low, Intel timing is selected; if wired high, Motorola timing is selected. All Motorola bus signals are listed in parentheses (). See the timing diagrams in Section  $\underline{26}$  for more details.

#### 6.2 Serial Port Operation

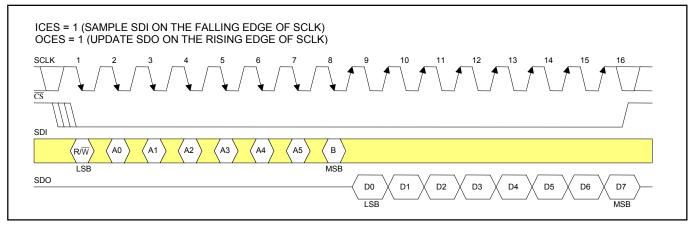

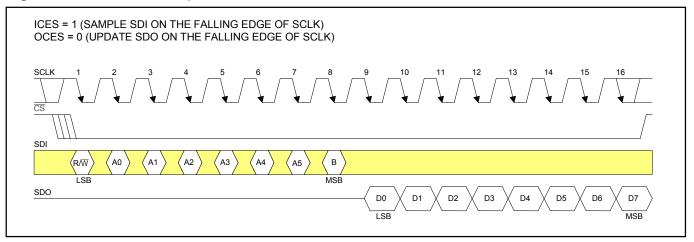

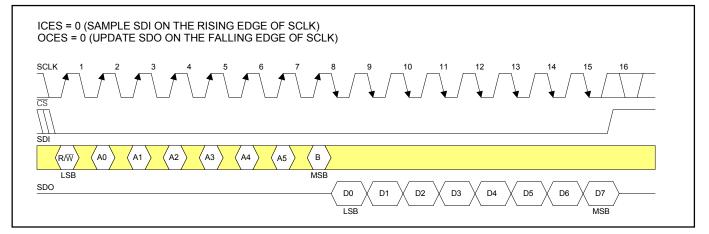

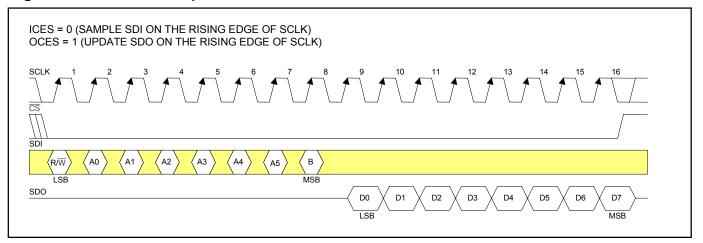

Setting the BTS1 pin = 1 and BTS0 pin = 0 enables the serial bus interface on the DS21Q59. Port read/write timing is unrelated to the system transmit and receive timing, allowing asynchronous reads or writes by the host. See Section <u>26</u> for the AC timing of the serial port. All serial port accesses are LSB first. See <u>Figure 6-1</u>, <u>Figure 6-2</u>, <u>Figure 6-3</u>, and <u>Figure 6-4</u> for more details.

Reading or writing to the internal registers requires writing one address/command byte prior to transferring register data. The first bit written (LSB) of the address/command byte specifies whether the access is a read (1) or a write (0). The next five bits identify the register address. The next bit is reserved and must be set to 0 for proper operation. The last bit (MSB) of the address/command byte enables the burst mode when set to 1. The burst mode causes all registers to be consecutively written or read.

All data transfers are initiated by driving the  $\overline{CS}$  input low. When input-clock edge select (ICES) is low, input data is latched on the rising edge of SCLK; when ICES is high, input data is latched on the falling edge of SCLK. When output-clock edge select (OCES) is low, data is output on the falling edge of SCLK; when OCES is high, data is output on the rising edge of SCLK. Data is held until the next falling or rising edge. All data transfers are terminated if the  $\overline{CS}$  input transitions high. Port control logic is disabled and SDO is tri-stated when  $\overline{CS}$  is high.

#### Figure 6-1. Serial Port Operation Mode 1

#### Figure 6-2. Serial Port Operation Mode 2

#### Figure 6-3. Serial Port Operation Mode 3

#### Figure 6-4. Serial Port Operation Mode 4

## 7. REGISTER MAP

Table 7-A. Register Map (Sorted by Address)

| ADDRESS  | R/W | NAME               | FUNCTION                                        |  |  |

|----------|-----|--------------------|-------------------------------------------------|--|--|

| 00       | R   | VCR1               | BPV or Code Violation Count 1                   |  |  |

| 01       | R   | VCR2               | BPV or Code Violation Count 2                   |  |  |

| 02       | R   | CRCCR1             | CRC4 Error Count 1                              |  |  |

| 03       | R   | CRCCR2             | CRC4 Error Count 2                              |  |  |

| 04       | R   | EBCR1              | E-Bit Count 1/PRBS Error Count 1                |  |  |

| 05       | R   | EBCR2              | E-Bit Count 2/PRBS Error Count 2                |  |  |

| 06       | R   | FASCR1             | FAS Error Count 1                               |  |  |

| 07       | R   | FASCR2             | FAS Error Count 2                               |  |  |

| 08       | R/W | RIR                | Receive Information                             |  |  |

| 09       | R   | SSR                | Synchronizer Status                             |  |  |

| 0A       | R/W | SR1                | Status 1                                        |  |  |

| 0B       | R/W | SR2                | Status 2                                        |  |  |

| 0C       | _   | _                  | Unused                                          |  |  |

| 0D       |     | _                  | Unused                                          |  |  |

| 0E       |     |                    | Unused                                          |  |  |

| 0F       | R   | IDR                | Device ID (Note 1)                              |  |  |

| 10       | R/W | RCR                | Receive Control                                 |  |  |

| 11       | R/W | TCR                | Transmit Control 1                              |  |  |

| 12       | R/W | CCR1               | Common Control 1                                |  |  |

| 13       | R/W | CCR2               | Common Control 2                                |  |  |

| 14       | R/W | CCR3               | Common Control 3                                |  |  |

| 15       | R/W | CCR4               | Common Control 4                                |  |  |

| 16       | R/W | CCR5               | Common Control 5                                |  |  |

| 17       | R/W | LICR               | Line Interface Control Register                 |  |  |

| 18       | R/W | IMR1               | Interrupt Mask 1                                |  |  |

| 19       | R/W | IMR2               | Interrupt Mask 2                                |  |  |

| 10<br>1A | R/W | OUTAC              | Output A Control                                |  |  |

| 1B       | R/W | OUTBC              | Output B Control                                |  |  |

| 1D<br>1C | R/W | IBO                | Interleave Bus Operation Register               |  |  |

| 10<br>1D | R/W | SCICR              | System Clock-Interface Control Register (Note 1 |  |  |

| 1E       | R/W | TEST3 (set to 00h) | Test 2 (Note 2)                                 |  |  |

| 1F       | R/W | CCR7               | Common Control 7                                |  |  |

| 20       | R/W | TAF                | Transmit Align Frame                            |  |  |

| 20       | R/W | TNAF               |                                                 |  |  |

| 21       | R   | TDS0M              | Transmit Nonalign Frame<br>Transmit DS0 Monitor |  |  |

| 23       | R/W | TIDR               | Transmit Idle Definition                        |  |  |

| 23       | R/W | TIR1               | Transmit Idle 1                                 |  |  |

| 24       | R/W | TIR2               | Transmit Idle 2                                 |  |  |

| 26       | R/W | TIR3               | Transmit Idle 3                                 |  |  |

| 20       | R/W | TIR4               | Transmit Idle 4                                 |  |  |

| 28       | R   | RAF                | Receive Align Frame                             |  |  |

| 28       | R   | RNAF               | Receive Nonalign Frame                          |  |  |

| 29<br>2A | R   | RDS0M              | Receive DS0 Monitor                             |  |  |

| 2A<br>2B | R/W | PCLB1              | Per-Channel Loopback Control 1                  |  |  |

|          |     |                    |                                                 |  |  |

| 2C       | R/W | PCLB2              | Per-Channel Loopback Control 2                  |  |  |

| 2D       | R/W | PCLB3              | Per-Channel Loopback Control 3                  |  |  |

| 2E       | R/W | PCLB4              | Per-Channel Loopback Control 4                  |  |  |

| 2F       | R/W | CCR6               | Common Control 6                                |  |  |

| 30       | R/W | SA1                | Signaling Access Register 1                     |  |  |

| 31       | R/W | SA2                | Signaling Access Register 2                     |  |  |

| 32       | R/W | SA3                | Signaling Access Register 3                     |  |  |

| 33       | R/W | SA4                | Signaling Access Register 4                     |  |  |

| 34       | R/W | SA5                | Signaling Access Register 5                     |  |  |

| 35       | R/W | SA6                | Signaling Access Register 6                     |  |  |

| 36       | R/W | SA7                | Signaling Access Register 7                     |  |  |

| ADDRESS | R/W | NAME | FUNCTION                     |

|---------|-----|------|------------------------------|

| 37      | R/W | SA8  | Signaling Access Register 8  |

| 38      | R/W | SA9  | Signaling Access Register 9  |

| 39      | R/W | SA10 | Signaling Access Register 10 |

| 3A      | R/W | SA11 | Signaling Access Register 11 |

| 3B      | R/W | SA12 | Signaling Access Register 12 |

| 3C      | R/W | SA13 | Signaling Access Register 13 |

| 3D      | R/W | SA14 | Signaling Access Register 14 |

| 3E      | R/W | SA15 | Signaling Access Register 15 |

| 3F      | R/W | SA16 | Signaling Access Register 16 |

**Note 1:** The device ID register and the system clock-interface control register exist in Transceiver 1 only (TS0, TS1 = 0).

Note 2: Only the factory uses the test register; this register must be cleared (set to all zeros) on power-up initialization to ensure proper operation.

## 8. CONTROL, ID, AND TEST REGISTERS

The DS21Q59 operation is configured through a set of nine control registers. Typically, registers are only accessed when the system is first powered up. Once the device has been initialized, the control registers only need to be accessed when there is a change in the system configuration. There is one receive control register (RCR), one transmit control register (TCR), and seven common control registers (CCR1 to CCR7). Each of these registers is described in this section.

Address 0Fh has a device identification register (IDR). The four MSBs of this read-only register are fixed to 1 0 0 1, indicating that a DS21Q59 E1 quad transceiver is present. The lower 4 bits of the IDR are used to identify the revision of the device. This register exists in Transceiver 1 only (TS0, TS1 = 0).

The factory in testing the DS21Q59 uses the test register at addresses 1E. On power-up, the test register should be set to 00h for the DS21Q59 to properly operate.

| Register Name:<br>Register Description:<br>Register Address: |     | IDR<br>Devid<br>0F He |             | ation Regis          | ster           |               |               |             |

|--------------------------------------------------------------|-----|-----------------------|-------------|----------------------|----------------|---------------|---------------|-------------|

| Bit #                                                        | 7   | 6                     | 5           | 4                    | 3              | 2             | 1             | 0           |