# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

DSC2110 | DSC2210

#### **General Description**

**Block Diagram**

DSC2110 DSC2210 The and series of high-performance programmable, CMOS oscillators utilize a proven silicon MEMS technology to provide excellent jitter and stability while incorporating high output flexibility frequency and drive strength control. DSC2110 and DSC2210 allow the user to modify the frequency and CMOS drive I<sup>2</sup>C using or SPI strength interface, respectively. User can also select from two pre-programmed default output frequencies using the control pin.

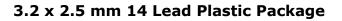

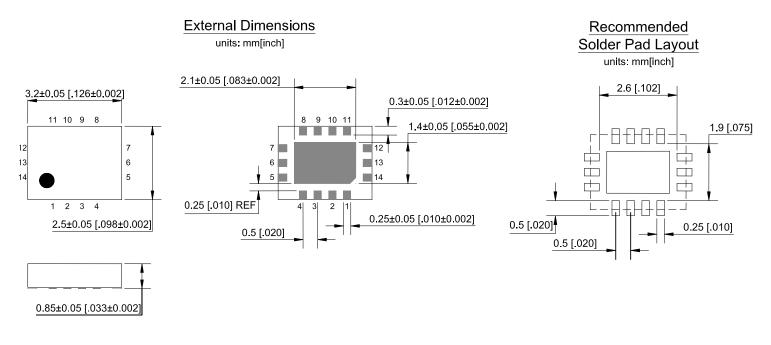

DSC2110 and DSC2210 are packaged in 14pin 3.2x2.5 mm QFN packages and available in temperature grades from Ext. Commercial to Automotive.

#### Pin 14 Pin 13 Pin 12 FS VDD VDD2 Pin 1 Pin 11 Temp. Sensor & NC Enable Compensation Circuitry Pin 2 Pin 10 NC NC Divider MEMS PLL Oscillator Driver Pin 3 Pin 9 see table NC below Pin 4 Pin 8 GND Output Pin 6 Pin 5 Pin 7 see table see table see table below below below

| Pin # | DSC2110 (I <sup>2</sup> C) | DSC2210 (SPI) |

|-------|----------------------------|---------------|

| 3     | NC                         | SCLK          |

| 5     | SDA                        | MOSI          |

| 6     | SCL                        | MISO          |

| 7     | CS_bar                     | SS            |

#### **Features**

• Low RMS Phase Jitter: <1 ps (typ)

discera

Datasheet

- High Stability: ±10, ±25, ±50 ppm

- Wide Temperature Range

- $_{\odot}$  Automotive: -55° to 125° C

- $_{\odot}$  Ext. Industrial: -40° to 105° C

- $\circ$  Industrial: -40° to 85° C

- $_{\odot}$  Ext. commercial: -20° to 70° C

- High Supply Noise Rejection: -50 dBc

- I<sup>2</sup>C/SPI Programmable Freq & Drive

- Short Lead Times: 2 Weeks

- Wide Freq. Range: • CMOS Output: 2.3 to 170 MHz

- Miniature Footprint of 3.2x2.5mm

- Excellent Shock & Vibration Immunity • Qualified to MIL-STD-883

- High Reliability • 20x better MTF than quartz oscillators

- Supply Range of 2.25 to 3.6 V

- Lead Free & RoHS Compliant

### **Applications**

- Consumer Electronics

- Storage Area Networks

SATA, SAS, Fibre Channel

- Passive Optical Networks • EPON, 10G-EPON, GPON, 10G-PON

- Ethernet o 1G, 10GBASE-T/KR/LR/SR, and FCoE

- HD/SD/SDI Video & Surveillance

- PCI Express

#### **Pin Description**

| Pin No.    | Pin Name | Pin Type | Description                                        |

|------------|----------|----------|----------------------------------------------------|

| 1          | Enable   | Ι        | Enables outputs when high and disables when low    |

| 2          | NC       | NA       | Leave unconnected or grounded                      |

| 3          | NC       | NA       | DSC2110: Leave unconnected or grounded             |

| 5          | SCLK     | Ι        | DSC2210: Serial clock from master                  |

| 4          | GND      | Power    | Ground                                             |

| 5          | SDA      | Ι        | DSC2110: I <sup>2</sup> C Serial Data              |

| 5          | MOSI     |          | DSC2210: SPI Serial Data from Master to Slave      |

| 6          | SCL      | Ι        | DSC2110: I <sup>2</sup> C Serial Clock             |

| 0          | MISO     | 0        | DSC2210: SPI Serial Data from Slave to Master      |

| 7 CS_bar I |          | Ι        | DSC2110: I <sup>2</sup> C Chip Select (Active Low) |

| /          | SS       | Ι        | DSC2210: SPI Slave Select (Active Low)             |

| 8          | Output1  | 0        | CMOS output 1                                      |

| 9          | NC       | NA       | Leave unconnected or grounded                      |

| 10         | NC       | NA       | Leave unconnected or grounded                      |

| 11         | NC       | NA       | Leave unconnected or grounded                      |

| 12         | VDD2     | Power    | Power Supply                                       |

| 13         | VDD      | Power    | Power Supply                                       |

| 14         | FS       | I        | Default output clock frequency bit                 |

#### **Operational Description**

The DSC2110/2210 is a CMOS oscillator consisting of a MEMS resonator and a support PLL IC. The CMOS output is generated through independent 8-bit programmable dividers from the output of the internal PLL.

DSC2110/2210 allows for easy programming of the output frequencies using I<sup>2</sup>C/SPI interface. Upon power-up, the initial output frequency is controlled by an internal preprogrammed memory (OTP). This memory stores all coefficients required by the PLL for two different default frequencies. The control pin (FS) selects the initial frequency. Once the device is powered up, a new output frequency can be programmed. Programming details are provided in the **Programming Guide**. Standard default frequencies are described in the following sections. Discera supports customer defined versions of the DSC2110/2210.

When Enable (pin 1) is floated or connected to VDD, the DSC2110/2210 is in operational

mode. Driving Enable to ground will disable both output drivers (hi-impedance mode).

The DSC2110/2210 has programmable output drive strength, which can be controlled via  $I^2C/SPI$ . Table 1 displays typical rise / fall times for the output with a 15pf load capacitance as a function of these control bits at VDD=3.3V and room temperature.

Table 1. Rise/Fall times for drive strengths

|         | Output Drive Strength Bits                  |     |     |   |     |     |     |     |

|---------|---------------------------------------------|-----|-----|---|-----|-----|-----|-----|

|         | [OXS2, OXS1, OXS0] - Default [ <b>111</b> ] |     |     |   |     |     |     |     |

|         | X=1 for output1, and 2 for output2          |     |     |   |     |     |     |     |

|         | 000 001 010 011 100 101 110 <b>111</b>      |     |     |   |     |     |     |     |

| tr (ns) | ns) 2.1 1.7 1.6 1.4 1.3 1.3 1.2 <b>1.1</b>  |     |     |   |     |     |     |     |

| tf (ns) | 2.5                                         | 2.4 | 2.4 | 2 | 1.8 | 1.6 | 1.3 | 1.3 |

#### **Output Clock Frequencies**

Table 2 lists the standard frequency configurations and the associated ordering information to be used in conjunction with the ordering code. Customer defined combinations are available.

| Ordering | Freq             | Select Bit [FS] -                              | - Default is [1] |  |

|----------|------------------|------------------------------------------------|------------------|--|

| Info     | (MHz)            | 0                                              | 1                |  |

| A0001    | f <sub>out</sub> | 27                                             | 24               |  |

| A0002    | f <sub>out</sub> | 155.52                                         | 106.25           |  |

| A0003    | f <sub>out</sub> | 25                                             | 75               |  |

| A0004    | f <sub>out</sub> | 72                                             | 74.25            |  |

| A0005    | f <sub>out</sub> | 27                                             | 50               |  |

| A0006    | f <sub>out</sub> | 16                                             | 13.56            |  |

| A0007    | f <sub>out</sub> | 96                                             | 55               |  |

| A0008    | f <sub>out</sub> | 25                                             | 50               |  |

| A0009    | f <sub>out</sub> | 55.296                                         | 27.648           |  |

| A00010   | f <sub>out</sub> | 27.648                                         | 55.296           |  |

| AXXXX    | f <sub>out</sub> | Contact factory for additional configurations. |                  |  |

Table 2. Pre-programmed pin-selectable output frequency combinations

Frequency select bit are weakly tied high so if left unconnected the default setting will be [1] and the device will output the associated frequency highlighted in **Bold**.

📰 discera

**i**discera

#### **Absolute Maximum Ratings**

| Item           | Min  | Мах                  | Unit | Condition  |

|----------------|------|----------------------|------|------------|

| Supply Voltage | -0.3 | +4.0                 | V    |            |

| Input Voltage  | -0.3 | V <sub>DD</sub> +0.3 | V    |            |

| Junction Temp  | -    | +150                 | °C   |            |

| Storage Temp   | -55  | +150                 | °C   |            |

| Soldering Temp | -    | +260                 | °C   | 40sec max. |

| ESD            | -    |                      | V    |            |

| HBM            |      | 4000                 |      |            |

| MM             |      | 400                  |      |            |

| CDM            |      | 1500                 |      |            |

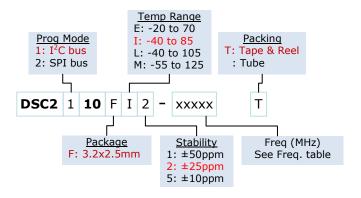

#### **Ordering Code**

Note: 1000+ years of data retention on internal memory

#### **Specifications** (Unless specified otherwise: T=25° C, max CMOS drive strength)

| Parameter                                                     |                                    | Condition                                                                                    | Min.                      | Тур.               | Max.                      | Unit              |

|---------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------|---------------------------|--------------------|---------------------------|-------------------|

| Supply Voltage <sup>1</sup>                                   | $V_{DD}$                           |                                                                                              | 2.25                      |                    | 3.6                       | V                 |

| Supply Current                                                | I <sub>DD</sub>                    | EN pin low – output is disabled                                                              |                           | 21                 | 23                        | mA                |

| Frequency Stability                                           | Δf                                 | Includes frequency variations due<br>to initial tolerance, temp. and<br>power supply voltage |                           |                    | ±10<br>±25<br>±50         | ppm               |

| Aging                                                         | Δf                                 | 1 year @25°C                                                                                 |                           |                    | ±5                        | ppm               |

| Startup Time <sup>2</sup>                                     | t <sub>su</sub>                    | T=25°C                                                                                       |                           |                    | 5                         | ms                |

| Input Logic Levels<br>Input logic high<br>Input logic low     | V <sub>IH</sub><br>V <sub>IL</sub> |                                                                                              | 0.75xV <sub>DD</sub><br>- |                    | -<br>0.25xV <sub>DD</sub> | v                 |

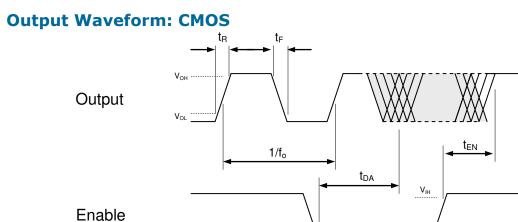

| Output Disable Time <sup>3</sup>                              | t <sub>DA</sub>                    |                                                                                              |                           |                    | 5                         | ns                |

| Output Enable Time                                            | t <sub>EN</sub>                    |                                                                                              |                           |                    | 20                        | ns                |

| Pull-Up Resistor <sup>4</sup>                                 |                                    | Pull-up exists on all digital IO                                                             |                           | 40                 |                           | kΩ                |

|                                                               |                                    | CMOS Output                                                                                  |                           |                    |                           |                   |

| Supply Current <sup>4</sup>                                   | $I_{DD}$                           | EN pin high – output is enabled $C_L=15pF$ , $F_O=125 MHz$                                   |                           | 31                 | 35                        | mA                |

| Output Logic Levels<br>Output logic high<br>Output logic low  | V <sub>OH</sub><br>V <sub>OL</sub> | I=±6mA                                                                                       | 0.9xV <sub>DD</sub><br>-  |                    | -<br>0.1xV <sub>DD</sub>  | v                 |

| Output Transition time <sup>3</sup><br>Rise Time<br>Fall Time | t <sub>R</sub><br>t <sub>F</sub>   | 20% to 80%<br>C <sub>L</sub> =15pf                                                           |                           | 1.1<br>1.3         | 2<br>2                    | ns                |

| Frequency                                                     | f <sub>0</sub>                     | Commercial/Industrial temp range<br>Automotive temp range                                    | 2.3                       |                    | 170<br>100                | MHz               |

| Output Duty Cycle                                             | SYM                                |                                                                                              | 45                        |                    | 55                        | %                 |

| Period Jitter                                                 | J <sub>PER</sub>                   | F <sub>o</sub> =125 MHz                                                                      |                           | 3                  |                           | ps <sub>RMS</sub> |

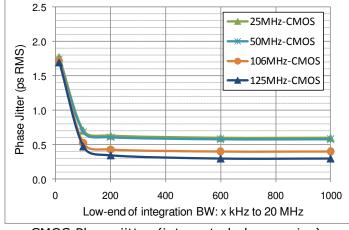

| Integrated Phase Noise                                        | J <sub>CC</sub>                    | 200kHz to 20MHz @ 125MHz<br>100kHz to 20MHz @ 125MHz<br>12kHz to 20MHz @ 125MHz              |                           | 0.3<br>0.38<br>1.7 | 2                         | ps <sub>rms</sub> |

Notes:

1. Pin 4  $V_{\mbox{\scriptsize DD}}$  should be filtered with 0.01uf capacitor.

$t_{su}$  is time to 100PPM stable output frequency after  $V_{\text{DD}}$  is applied and outputs are enabled. Output Waveform and Test Circuit figures below define the parameters. Output is enabled if Enable pad is floated or not connected.

2. 3.

4.

#### Nominal Performance Parameters (Unless specified otherwise: T=25° C, V<sub>DD</sub>=3.3 V)

CMOS Phase jitter (integrated phase noise)

VIL

📰 discera

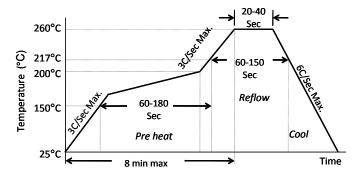

#### **Solder Reflow Profile**

| MSL 1 @ 260°C refer to JSTD-020C  |              |  |  |  |  |

|-----------------------------------|--------------|--|--|--|--|

| Ramp-Up Rate (200°C to Peak Temp) | 3°C/Sec Max. |  |  |  |  |

| Preheat Time 150°C to 200°C       | 60-180 Sec   |  |  |  |  |

| Time maintained above 217°C       | 60-150 Sec   |  |  |  |  |

| Peak Temperature                  | 255-260°C    |  |  |  |  |

| Time within 5°C of actual Peak    | 20-40 Sec    |  |  |  |  |

| Ramp-Down Rate                    | 6°C/Sec Max. |  |  |  |  |

| Time 25°C to Peak Temperature     | 8 min Max.   |  |  |  |  |

#### **Package Dimensions**

#### **Disclaimer:**

Discera makes no warranty of any kind, express or implied, with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Discera reserves the right to make changes without further notice to materials described herein. Discera does not assume any liability arising from the application or use of any product or circuit described herein. Discera does not authorize its products for use a critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Discera's product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Discera against all charges.

| DISCERA, Inc. •          | 1961 Concourse Drive, San Jose, California 95131    | • | USA             |

|--------------------------|-----------------------------------------------------|---|-----------------|

| Phone: +1 (408) 432-8600 | • Fax: +1 (408) 432-8609 • Email: sales@discera.com | • | www.discera.com |