# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 56858

Data Sheet Technical Data

56800E 16-bit Digital Signal Controllers

DSP56858 Rev. 6 01/2007

freescale.com

# **DSP56858 General Description**

- 120 MIPS at 120MHz

- 40K x 16-bit Program SRAM

- 24K x 16-bit Data SRAM

- 1K x 16-bit Boot ROM

- Access up to 2M words of program memory or 8M data memory

- Chip Select Logic for glue-less interface to ROM and SRAM

- Six (6) independent channels of DMA

- Two (2) Enhanced Synchronous Serial Interfaces (ESSI)

- Two (2) Serial Communication Interfaces (SCI)

- Serial Port Interface (SPI)

- 8-bit Parallel Host Interface

- General Purpose 16-bit Quad Timer

- JTAG/Enhanced On-Chip Emulation (OnCE<sup>™</sup>) for unobtrusive, real-time debugging

- Computer Operating Properly (COP)/Watchdog Timer

- Time-of -Day (TOD)

- 144 LQFP and 144 MAPBGA packages

- Up to 47 GPIO

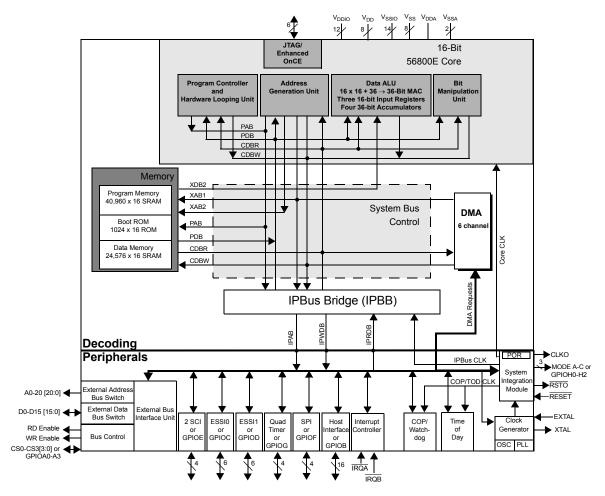

56858 Block Diagram

# Part 1 Overview

## 1.1 56858 Features

### 1.1.1 Digital Signal Processing Core

- Efficient 16-bit engine with dual Harvard architecture

- 120 Million Instructions Per Second (MIPS) at 120MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Four (4) 36-bit accumulators including extension bits

- 16-bit bidirectional shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three (3) internal address buses and one (1) external address bus

- Four (4) internal data buses and one (1) external data bus

- Instruction set supports both DSP and controller functions

- Four (4) hardware interrupt levels

- Five (5) software interrupt levels

- Controller-style addressing modes and instructions for compact code

- Efficient C-Compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/Enhanced OnCE debug programming interface

## 1.1.2 Memory

- Harvard architecture permits up to three (3) simultaneous accesses to program and data memory

- On-Chip Memory

- 40K × 16-bit Program RAM

- 24K × 16-bit Data RAM

- 1K × 16-bit Boot ROM

- Off-Chip Memory Expansion (EMI)

- Access up to 2M words of program or 8M data memory (using chip selects)

- Chip Select Logic for glue-less interface to ROM and SRAM

## 1.1.3 56858 Peripheral Circuit Features

- General Purpose 16-bit Quad Timer\*

- Two Serial Communication Interfaces (SCI)\*

- Serial Peripheral Interface (SPI) Port\*

- Two (2) Enhanced Synchronous Serial Interface (ESSI) modules\*

- Computer Operating Properly (COP)/Watchdog Timer

- JTAG/Enhanced On-Chip Emulation (EOnCE) for unobtrusive, real-time debugging

- Six (6) independent channels of DMA

- 8-bit Parallel Host Interface\*

- Time-of-Day (TOD)

- Up to 47 GPIO

- \* Each peripheral I/O can be used alternately as a GPIO if not needed

## 1.1.4 Energy Information

- Fabricated in high-density CMOS with 3.3V, TTL-compatible digital inputs

- Wait and Stop modes available

## 1.2 56858 Description

The 56858 is a member of the 56800E core-based family of controllers. This device combines the processing power of a Digital Signal Processor (DSP) and the functionality of a microcontroller with a flexible set of peripherals on a single chip to create an extremely cost-effective solution. The low cost, flexibility, and compact program code make this device well-suited for many applications. The 56858 includes peripherals that are especially useful for teledatacom devices; Internet appliances; portable devices; TAD; voice recognition; hands-free devices; and general purpose applications.

The 56800E core is based on a Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The microprocessor-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C Compilers, enabling rapid development of optimized control applications.

The 56858 supports program execution from either internal or external memories. Two data operands can be accessed from the on-chip Data RAM per instruction cycle. The 56858 also provides two external dedicated interrupt lines, and up to 47 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The 56858 controller includes 40K words of Program RAM, 24K words of Data RAM and 1K of Boot RAM. It also supports program execution from external memory.

This controller also provides a full set of standard programmable peripherals that include an 8-bit Parallel Host Interface, two Enhanced Synchronous Serial Interfaces (ESSI), one Serial Peripheral Interface (SPI), two Serial Communications Interfaces (SCI), and one Quad Timer. The Host Interface, Quad Timer, SSI, SPI, SCI I/O and four chip selects can be used as General Purpose Input/Outputs when its primary function is not required.

## **1.3 State of the Art Development Environment**

- Processor Expert<sup>TM</sup> (PE) provides a Rapid Application Design (RAD) tool that combines easy-to-use component-based software application creation with an expert knowledge system.

- The Code Warrior Integrated Development Environment is a sophisticated tool for code navigation, compiling, and debugging. A complete set of evaluation modules (EVMs) and development system cards will support concurrent engineering. Together, PE, Code Warrior and EVMs create a complete, scalable tools solution for easy, fast, and efficient development.

56858 Technical Data, Rev. 6

## **1.4 Product Documentation**

The four documents listed in **Table 1-1** are required for a complete description of and proper design with the 56858. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, Freescale Literature Distribution Centers, or online at **www.freescale.com**.

| Торіс                         | Description                                                                                      | Order Number |

|-------------------------------|--------------------------------------------------------------------------------------------------|--------------|

| 56800E<br>Reference Manual    | Detailed description of the 56800E architecture, 16-bit core processor and the instruction set   | 56800ERM     |

| DSP56858<br>User's Manual     | Detailed description of memory, peripherals, and interfaces of the 56858                         | DSP5685xUM   |

| 56858<br>Technical Data Sheet | Electrical and timing specifications, pin descriptions, and package descriptions (this document) | DSP56858     |

| DSP56858<br>Errata            | Details any chip issues that might be present                                                    | DSP56858E    |

Table 1-1 56858 Chip Documentation

## 1.5 Data Sheet Conventions

This data sheet uses the following conventions:

| OVERBAR      | This is used to indicate a signal that is active when pulled low. For example, the $\overline{\text{RESET}}$ pin is active when low. |                        |                                |                                  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|----------------------------------|--|--|--|

| "asserted"   | A high true (active high) sig                                                                                                        | nal is high or a low t | rue (active low) signal is low | Ι.                               |  |  |  |

| "deasserted" | A high true (active high) sig                                                                                                        | nal is low or a low tr | ue (active low) signal is high | ).                               |  |  |  |

| Examples:    | Signal/Symbol                                                                                                                        | Logic State            | Signal State                   | Voltage <sup>1</sup>             |  |  |  |

|              | PIN                                                                                                                                  | True                   | Asserted                       | V <sub>IL</sub> /V <sub>OL</sub> |  |  |  |

|              | PIN                                                                                                                                  | False                  | Deasserted                     | V <sub>IH</sub> /V <sub>OH</sub> |  |  |  |

|              | PIN                                                                                                                                  | True                   | Asserted                       | V <sub>IH</sub> /V <sub>OH</sub> |  |  |  |

|              | PIN                                                                                                                                  | False                  | Deasserted                     | V <sub>IL</sub> /V <sub>OL</sub> |  |  |  |

|              |                                                                                                                                      |                        |                                |                                  |  |  |  |

1. Values for VIL, VOL, VIH, and VOH are defined by individual product specifications.

# Part 2 Signal/Connection Descriptions

## 2.1 Introduction

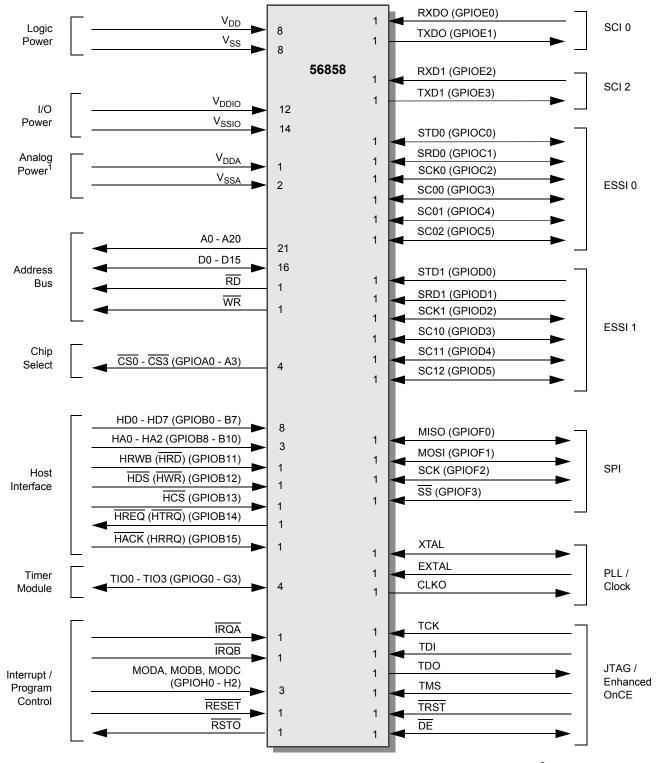

The input and output signals of the 56858 are organized into functional groups, as shown in **Table 2-1** and as illustrated in **Figure 2-1**. In **Table 3-1** each table row describes the package pin and the signal or signals present.

| Functional Group                                                   | Number of Pins          |

|--------------------------------------------------------------------|-------------------------|

| Power (V <sub>DD</sub> , V <sub>DDIO</sub> , or V <sub>DDA</sub> ) | (8, 12, 1) <sup>1</sup> |

| Ground ( $V_{SS}$ , $V_{SSIO}$ , or $V_{SSA}$ )                    | (8, 14, 2) <sup>1</sup> |

| PLL and Clock                                                      | 3                       |

| External Bus Signals                                               | 39                      |

| External Chip Select*                                              | 4                       |

| Interrupt and Program Control                                      | 7 <sup>2</sup>          |

| Host Interface (HI)*                                               | 16 <sup>3</sup>         |

| Enhanced Synchronous Serial Interface (ESSI0) Port*                | 6                       |

| Enhanced Synchronous Serial Interface (ESSI1) Port*                | 6                       |

| Serial Communications Interface (SCI0) Ports*                      | 2                       |

| Serial Communications Interface (SCI1) Ports*                      | 2                       |

| Serial Peripheral Interface (SPI) Port*                            | 4                       |

| Quad Timer Module Port*                                            | 4                       |

| JTAG/On-Chip Emulation (OnCE)                                      | 6                       |

\*Alternately, GPIO pins

1.  $V_{DD} = V_{DD \text{ CORE}}$ ,  $V_{SS} = V_{SS \text{ CORE}}$ ,  $V_{DDIO} = V_{DD \text{ IO}}$ ,  $V_{SSIO} = V_{SS \text{ IO}}$ ,  $V_{DDA} = V_{DD \text{ ANA}}$ ,  $V_{SSA} = V_{SS \text{ ANA}}$

2. MODA, MODB and MODC can be used as GPIO after the bootstrap process has completed.

3. The following Host Interface signals are multiplexed: HRWB to HRD, HDS to HWR, HREQ to HTRQ and HACK to HRRQ.

#### Figure 2-1 56858 Signals Identified by Functional Group<sup>2</sup>

1. Specifically for PLL, OSC, and POR.

2. Alternate pin functions are shown in parentheses. Pin direction/type is represented as the preferred functionality. GPIO may provide bidirectional use of any pin.

56858 Technical Data, Rev. 6

# Part 3 Signals and Package Information

All digital inputs have a weak internal pull-up circuit associated with them. These pull-up circuits are enabled by default. Exceptions:

- 1. When a pin has GPIO functionality, the pull-up may be disabled under software control.

- 2. MODE A, MODE B and MODE C pins have no pull-up.

- 3. TCK has a weak pull-down circuit always active.

- 4. Bidirectional I/O pullups automatically disable when the output is enabled.

This table is presented consistently with the Signals Identified by Functional Group figure.

- 1. **BOLD** entries in the *Type* column represents the state of the pin just out of reset.

- 2. Output(Z) means an output in a High-Z condition.

| Signal<br>Name  | BGA<br>Pin No. | LQFP<br>Pin No. | Туре            | Description                                                                |

|-----------------|----------------|-----------------|-----------------|----------------------------------------------------------------------------|

| V <sub>DD</sub> | E1             | 14              | V <sub>DD</sub> | Logic Power (V <sub>DD</sub> )—These pins provide power to the internal    |

| V <sub>DD</sub> | M6             | 36              |                 | structures of the chip, and should all be attached to $V_{DD}.$            |

| V <sub>DD</sub> | F12            | 52              |                 |                                                                            |

| V <sub>DD</sub> | A9             | 72              |                 |                                                                            |

| V <sub>DD</sub> | M2             | 87              |                 |                                                                            |

| V <sub>DD</sub> | J12            | 88              |                 |                                                                            |

| V <sub>DD</sub> | E12            | 109             |                 |                                                                            |

| V <sub>DD</sub> | A12            | 125             |                 |                                                                            |

| V <sub>SS</sub> | G1             | 15              | V <sub>SS</sub> | Logic Power–Ground (V <sub>SS</sub> )—These pins provide grounding for the |

| V <sub>SS</sub> | L6             | 16              |                 | internal structures of the chip and should all be attached to $V_{SS.}$    |

| V <sub>SS</sub> | D12            | 53              |                 |                                                                            |

| V <sub>SS</sub> | A7             | 54              |                 |                                                                            |

| V <sub>SS</sub> | F1             | 71              |                 |                                                                            |

| V <sub>SS</sub> | M7             | 89              |                 |                                                                            |

| V <sub>SS</sub> | K12            | 126             |                 |                                                                            |

| V <sub>SS</sub> | A8             | 127             |                 |                                                                            |

| Signal<br>Name    | BGA<br>Pin No. | LQFP<br>Pin No. | Туре              | Description                                                                             |

|-------------------|----------------|-----------------|-------------------|-----------------------------------------------------------------------------------------|

| V <sub>DDIO</sub> | B1             | 5               | V <sub>DDIO</sub> | I/O Power (V <sub>DDIO</sub> )—These pins provide power for all I/O and ESD             |

| V <sub>DDIO</sub> | H1             | 6               |                   | structures of the chip and should all be attached to $V_{\text{DDIO}}\left(3.3V\right)$ |

| V <sub>DDIO</sub> | M3             | 20              |                   |                                                                                         |

| V <sub>DDIO</sub> | M8             | 45              |                   |                                                                                         |

| V <sub>DDIO</sub> | M11            | 61              |                   |                                                                                         |

| V <sub>DDIO</sub> | H12            | 67              |                   |                                                                                         |

| V <sub>DDIO</sub> | C12            | 68              |                   |                                                                                         |

| V <sub>DDIO</sub> | A11            | 80              |                   |                                                                                         |

| V <sub>DDIO</sub> | A5             | 105             |                   |                                                                                         |

| V <sub>DDIO</sub> | A3             | 113             |                   |                                                                                         |

| V <sub>DDIO</sub> | C1             | 129             |                   |                                                                                         |

| V <sub>DDIO</sub> | M10            | 139             |                   |                                                                                         |

| V <sub>SSIO</sub> | D1             | 7               | V <sub>SSIO</sub> | I/O Power–Ground (V <sub>SSIO</sub> )—These pins provide grounding for all I/O          |

| V <sub>SSIO</sub> | J1             | 21              |                   | and ESD structures of the chip and should all be attached to $V_{SS.}$                  |

| V <sub>SSIO</sub> | M5             | 46              |                   |                                                                                         |

| V <sub>SSIO</sub> | M9             | 47              |                   |                                                                                         |

| V <sub>SSIO</sub> | L12            | 62              |                   |                                                                                         |

| V <sub>SSIO</sub> | G12            | 69              |                   |                                                                                         |

| V <sub>SSIO</sub> | B12            | 70              |                   |                                                                                         |

| V <sub>SSIO</sub> | A10            | 82              |                   |                                                                                         |

| V <sub>SSIO</sub> | A4             | 106             |                   |                                                                                         |

| V <sub>SSIO</sub> | A1             | 115             |                   |                                                                                         |

| V <sub>SSIO</sub> | A2             | 128             |                   |                                                                                         |

| V <sub>SSIO</sub> | M4             | 130             |                   |                                                                                         |

| V <sub>SSIO</sub> | M12            | 140             |                   |                                                                                         |

| V <sub>SSIO</sub> | A6             | 141             |                   |                                                                                         |

| V <sub>DDA</sub>  | K1             | 24              | V <sub>DDA</sub>  | Analog Power (V <sub>DDA</sub> )—These pins supply an analog power source.              |

| V <sub>SSA</sub>  | M1             | 25              | V                 | Analog Ground (V <sub>SSA</sub> )—This pin supplies an analog ground.                   |

| V <sub>SSA</sub>  | L1             | 26              | V <sub>SSA</sub>  |                                                                                         |

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре      | Description                                                   |

|----------------|----------------|-----------------|-----------|---------------------------------------------------------------|

| A0             | E5             | 10              | Output(Z) | Address Bus (A0-A20)—These signals specify a word address for |

| A1             | E4             | 11              |           | external program or data memory access.                       |

| A2             | E3             | 12              |           |                                                               |

| A3             | E2             | 13              |           |                                                               |

| A4             | J2             | 29              |           |                                                               |

| A5             | H3             | 30              |           |                                                               |

| A6             | G4             | 31              |           |                                                               |

| A7             | H4             | 32              |           |                                                               |

| A8             | G5             | 48              |           |                                                               |

| A9             | L5             | 49              |           |                                                               |

| A10            | J6             | 50              |           |                                                               |

| A11            | K6             | 51              |           |                                                               |

| A12            | J8             | 63              |           |                                                               |

| A13            | K8             | 64              |           |                                                               |

| A14            | L9             | 65              |           |                                                               |

| A15            | K9             | 66              |           |                                                               |

| A16            | K10            | 75              |           |                                                               |

| A17            | K11            | 76              |           |                                                               |

| A18            | J9             | 77              |           |                                                               |

| A19            | J10            | 78              |           |                                                               |

| A20            | J11            | 79              |           |                                                               |

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре         | Description                                                                                                   |

|----------------|----------------|-----------------|--------------|---------------------------------------------------------------------------------------------------------------|

| D0             | H7             | 81              | Input/       | Data Bus (D0-D15)—These pins provide the bidirectional data for                                               |

| D1             | G7             | 94              | Output(Z)    | external program or data memory accesses.                                                                     |

| D2             | F9             | 95              |              |                                                                                                               |

| D3             | F10            | 96              |              |                                                                                                               |

| D4             | F11            | 97              |              |                                                                                                               |

| D5             | E10            | 98              |              |                                                                                                               |

| D6             | D7             | 120             |              |                                                                                                               |

| D7             | B7             | 121             |              |                                                                                                               |

| D8             | E7             | 122             |              |                                                                                                               |

| D9             | F8             | 123             |              |                                                                                                               |

| D10            | F7             | 124             |              |                                                                                                               |

| D11            | D5             | 137             |              |                                                                                                               |

| D12            | B4             | 138             |              |                                                                                                               |

| D13            | C4             | 142             |              |                                                                                                               |

| D14            | F6             | 143             |              |                                                                                                               |

| D15            | B3             | 144             |              |                                                                                                               |

| RD             | D3             | 8               | Output       | <b>Read Enable</b> (RD) — is asserted during external memory read cycles.                                     |

|                |                |                 |              | This signal is pulled high during reset.                                                                      |

| WR             | D4             | 9               | Output       | Write Enable (WR) — is asserted during external memory write cycles.                                          |

|                |                |                 |              | This signal is pulled high during reset.                                                                      |

| CS0            | H8             | 83              | Output       | External Chip Select (CS0)—This pin is used as a dedicated GPIO.                                              |

| GPIOA0         |                |                 | Input/Output | <b>Port A GPIO (0)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| CS1            | H9             | 84              | Output       | External Chip Select (CS1)—This pin is used as a dedicated GPIO.                                              |

| GPIOA1         |                |                 | Input/Output | <b>Port A GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| CS2            | H11            | 85              | Output       | External Chip Select (CS2)—This pin is used as a dedicated GPIO.                                              |

| GPIOA2         |                |                 | Input/Output | <b>Port A GPIO (2)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| CS3            | H10            | 86              | Output       | External Chip Select (CS3)—This pin is used as a dedicated GPIO.                                              |

| GPIOA3         |                |                 | Input/Output | <b>Port A GPIO (3)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре         | Description                                                                                                   |

|----------------|----------------|-----------------|--------------|---------------------------------------------------------------------------------------------------------------|

| HD0            | J3             | 33              | Input        | Host Address (HD0)—This input provides data selection for HI registers.                                       |

|                |                |                 |              | This pin is disconnected internally during reset.                                                             |

| GPIOB0         |                |                 | Input/Output | <b>Port B GPIO (0)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| HD1            | K2             | 34              | Input        | Host Address (HD1)—This input provides data selection for HI registers.                                       |

|                |                |                 |              | This pin is disconnected internally during reset.                                                             |

| GPIOB1         |                |                 | Input/Output | <b>Port B GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| HD2            | L2             | 35              | Input        | Host Address (HD2)—This input provides data selection for HI registers.                                       |

|                |                |                 |              | This pin is disconnected internally during reset.                                                             |

| GPIOB2         |                |                 | Input/Output | <b>Port B GPIO (2)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| HD3            | J4             | 40              | Input        | Host Address (HD3)—This input provides data selection for HI registers.                                       |

|                |                |                 |              | This pin is disconnected internally during reset.                                                             |

| GPIOB3         |                |                 | Input/Output | <b>Port B GPIO (3)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| HD4            | L4             | 41              | Input        | Host Address (HD4)—This input provides data selection for HI registers.                                       |

|                |                |                 |              | This pin is disconnected internally during reset.                                                             |

| GPIOB4         |                |                 | Input/Output | <b>Port B GPIO (4)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

| HD5            | J5             | 42              | Input        | Host Address (HD5)—This input provides data selection for HI registers.                                       |

|                |                |                 |              | This pin is disconnected internally during reset.                                                             |

| GPIOB5         |                |                 | Input/Output | <b>Port B GPIO (5)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage. |

|                |                | 1.055           |              |                                                                                                                                                                                       |

|----------------|----------------|-----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре         | Description                                                                                                                                                                           |

| HD6            | K5             | 43              | Input        | Host Address (HD6)—This input provides data selection for HI registers.                                                                                                               |

|                |                |                 |              | This pin is disconnected internally during reset.                                                                                                                                     |

| GPIOB6         |                |                 | Input/Output | <b>Port B GPIO (6)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                         |

| HD7            | H5             | 44              | Input        | Host Address (HD7)—This input provides data selection for HI registers.                                                                                                               |

|                |                |                 |              | This pin is disconnected internally during reset.                                                                                                                                     |

| GPIOB7         |                |                 | Input/Output | <b>Port B GPIO (7)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                         |

| HA0            | G10            | 90              | Input        | Host Address (HA0)—These inputs provide the address selection for HI registers.                                                                                                       |

|                |                |                 |              | These pins are disconnected internally during reset.                                                                                                                                  |

| GPIOB8         |                |                 | Input/Output | <b>Port B GPIO (8)</b> —These pins are General Purpose I/O (GPIO) pins when not configured for host port usage.                                                                       |

| HA1            | G11            | 91              | Input        | Host Address (HA0)—These inputs provide the address selection for HI registers.                                                                                                       |

|                |                |                 |              | These pins are disconnected internally during reset.                                                                                                                                  |

| GPIOB9         |                |                 | Input/Output | <b>Port B GPIO (9)</b> —These pins are General Purpose I/O (GPIO) pins when not configured for host port usage.                                                                       |

| HA2            | G9             | 92              | Input        | Host Address (HA0)—These inputs provide the address selection for HI registers.                                                                                                       |

|                |                |                 |              | These pins are disconnected internally during reset.                                                                                                                                  |

| GPIOB10        |                |                 | Input/Output | <b>Port B GPIO (10)</b> —These pins are General Purpose I/O (GPIO) pins when not configured for host port usage.                                                                      |

| HRWB           | G8             | 93              | Input        | <b>Host Read/Write (HRWB)</b> —When the HI08 is programmed to interface to a single-data-strobe <u>host bus</u> and the HI function is selected, this signal is the Read/Write input. |

|                |                |                 |              | These pins are disconnected internally during reset.                                                                                                                                  |

| HRD            |                |                 | Input        | <b>Host Read Data (HRD)</b> —This signal is the Read Data input when the HI08 is programmed to interface to a double-data-strobe host bus and the HI function is selected.            |

| GPIOB11        |                |                 | Input/Output | <b>Port B GPIO (11)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                        |

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|----------------|-----------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDS            | C8             | 116             | Input                | <b>Host Data Strobe (HDS)</b> —When the HI08 is programmed to interface to a single-data-strobe host bus and the HI function is selected, this input enables a data transfer on the HI when HCS is asserted.                                                                                                                                                                     |

|                |                |                 |                      | These pins are disconnected internally during reset.                                                                                                                                                                                                                                                                                                                             |

| HWR            |                |                 | Input                | Host Write Enable (HWR)—This signal is the Write Data input when the HI08 is programmed to interface to a double-data-strobe host bus and the HI function is selected.                                                                                                                                                                                                           |

| GPIOB12        |                |                 | Input/Output         | <b>Port B GPIO (12)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                                                                                                                                                                                                                   |

| HCS            | D8             | 117             | Input                | Host Chip Select (HCS)—This input is the chip select input for the Host Interface.                                                                                                                                                                                                                                                                                               |

|                |                |                 |                      | These pins are disconnected internally during reset.                                                                                                                                                                                                                                                                                                                             |

| GPIOB13        |                |                 | Input/Output         | <b>Port B GPIO (13)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                                                                                                                                                                                                                   |

| HREQ           | B8             | 118             | Open Drain<br>Output | <b>Host Request (HREQ)</b> —When the HI08 is programmed for HRMS=0 functionality (typically used on a single-data-strobe bus), this open drain output is used by the HI to request service from the host processor. The HREQ may be connected to an interrupt request pin of a host processor, a transfer request of a DMA controller, or a control input of external circuitry. |

|                |                |                 |                      | These pins are disconnected internally during reset.                                                                                                                                                                                                                                                                                                                             |

| HTRQ           |                |                 | Open Drain<br>Output | <b>Transmit Host Request (HTRQ)</b> —This signal is the Transmit Host<br>Request output when the HI08 is programmed for HRMS=1<br>functionality and is typically used on a double-data-strobe bus.                                                                                                                                                                               |

| GPIOB14        |                |                 | Input/Output         | <b>Port B GPIO (14)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                                                                                                                                                                                                                   |

|                |                |                 |                      | 1                                                                                                                                                                                                                                                                                                                                                              |

|----------------|----------------|-----------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                    |

| HACK           | C7             | 119             | Input                | <b>Host Acknowledge (HACK)</b> —When the HI08 is programmed for<br>HRMS=0 functionality (typically used on a single-data-strobe bus), this<br>input has two functions: (1) provide a Host Acknowledge signal for<br>DMA transfers or (2) to control handshaking and provide a Host<br>Interrupt Acknowledge compatible with the MC68000 family<br>processors.  |

|                |                |                 |                      | These pins are disconnected internally during reset.                                                                                                                                                                                                                                                                                                           |

| HRRQ           |                |                 | Open Drain<br>Output | <b>Receive Host Request (HRRQ)</b> —This signal is the Receive Host<br>Request output when the HI08 is programmed for HRMS=1<br>functionality and is typically used on a double-data-strobe bus.                                                                                                                                                               |

| GPIOB15        |                |                 | Input/Output         | <b>Port B GPIO (15)</b> —This pin is a General Purpose I/O (GPIO) pin when not configured for host port usage.                                                                                                                                                                                                                                                 |

| TIO0           | B9             | 114             | Input/Output         | <b>Timer Input/Outputs (TIO0)</b> —This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                               |

| GPIOG0         |                |                 | Input/Output         | <b>Port G GPIOG0</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                              |

| TIO1           | C9             | 112             | Input/Output         | <b>Timer Input/Outputs (TIO1)</b> —This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                               |

| GPIOG1         |                |                 | Input/Output         | <b>Port G GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                            |

| TIO2           | D9             | 111             | Input/Output         | <b>Timer Input/Outputs (TIO2)</b> —This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                               |

| GPIOG2         |                |                 | Input/Output         | <b>Port G GPIO (2)</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                            |

| TIO3           | B10            | 110             | Input/Output         | <b>Timer Input/Outputs (TIO3)</b> —This pin can be independently configured to be either a timer input source or an output flag.                                                                                                                                                                                                                               |

| GPIOG3         |                |                 | Input/Output         | <b>Port G GPIO (3)</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as an input or output pin.                                                                                                                                                                                                                            |

| ĪRQA           | G2             | 22              | Input                | External Interrupt Request A and B—The IRQA and IRQB inputs                                                                                                                                                                                                                                                                                                    |

| ĪRQB           | F5             | 23              |                      | are asynchronous external interrupt requests that indicate that an<br>external device is requesting service. A Schmitt trigger input is used<br>for noise immunity. They can be programmed to be level-sensitive or<br>negative-edge-triggered. If level-sensitive triggering is selected, an<br>external pull-up resistor is required for Wired-OR operation. |

| MODE A         | F4             | 17              | Input                | <b>Mode Select (MODE A)</b> —During the bootstrap process MODE A selects one of the eight bootstrap modes.                                                                                                                                                                                                                                                     |

| GPIOH0         |                |                 | Input/Output         | <b>Port H GPIO (0)</b> —This pin is a General Purpose I/O (GPIO) pin after the bootstrap process has completed.                                                                                                                                                                                                                                                |

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре         | Description                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----------------|----------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MODE B         | F3             | 18              | Input        | <b>Mode Select (MODE B)</b> —During the bootstrap process MODE A selects one of the eight bootstrap modes.                                                                                                                                                                                                                                                        |  |  |

| GPIOH1         |                |                 | Input/Output | <b>Port H GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pin after the bootstrap process has completed.                                                                                                                                                                                                                                                   |  |  |

| MODE C         | F2             | 19              | Input        | <b>Mode Select (MODE C)</b> —During the bootstrap process MODE A selects one of the eight bootstrap modes.                                                                                                                                                                                                                                                        |  |  |

| GPIOH2         |                |                 | Input/Output | the bootstrap process has completed.                                                                                                                                                                                                                                                                                                                              |  |  |

| RESET          | K4             | 39              | Input        | <b>Reset (RESET)</b> — <u>This input is a direct hardware reset on the</u><br>processor. When RESET is asserted low, the device is initialized and<br>placed in the Reset state. A Schmitt trigger input is used for noise<br>immunity. When the RESET pin is deasserted, the initial chip operation<br>mode is latched from the MODE A, MODE B, and MODE C pins. |  |  |

|                |                |                 |              | To ensure complete hardware reset, RESET and TRST should be asserted together. The only exception occurs in a debugging environment when a hardware reset is required and it is necessary reset the JTAG/Enhanced OnCE module. In this case, assert RESET, but do not assert TRST.                                                                                |  |  |

| RSTO           | K3             | 38              | Output       | <b>Reset Output (RSTO)</b> —This output is asserted on any reset condition (external reset, low voltage, software, or COP).                                                                                                                                                                                                                                       |  |  |

| RXD0           | L10            | 73              | Input        | Serial Receive Data 0 (RXD0)—This input receives byte-oriented serial data and transfers it to the SCI 0 receive shift register.                                                                                                                                                                                                                                  |  |  |

| GPIOE0         |                |                 | Input/Output | <b>Port E GPIO (0)</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                                                                  |  |  |

| TXD0           | L11            | 74              | Output(Z)    | Serial Transmit Data 0 (TXD0)—This signal transmits data from the SCI 0 transmit data register.                                                                                                                                                                                                                                                                   |  |  |

| GPIOE1         |                |                 | Input/Output | <b>Port E GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                                                                  |  |  |

| RXD1           | B11            | 107             | Input        | Serial Receive Data 1 (RXD1)—This input receives byte-oriented serial data and transfers it to the SCI 1 receive shift register.                                                                                                                                                                                                                                  |  |  |

| GPIOE2         |                |                 | Input/Output | <b>Port E GPIO (2)</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                                                                  |  |  |

| TXD1           | C10            | 108             | Output(Z)    | Serial Transmit Data 1 (TXD1)—This signal transmits data from the SCI 1 transmit data register.                                                                                                                                                                                                                                                                   |  |  |

| GPIOE3         |                |                 | Input/Output | <b>Port E GPIO (3)</b> —This pin is a General Purpose I/O (GPIO) pin that can individually be programmed as input or output pin.                                                                                                                                                                                                                                  |  |  |

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------|----------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| STD0           | B6             | 131             | Output          | <b>ESSI Transmit Data (STD0)</b> —This output pin transmits serial data from the ESSI Transmitter Shift Register.                                                                                                                                                                                                                                                                                                                                     |  |

| GPIOC0         |                |                 | Input/Output    | <b>Port C GPIO (0)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SRD0           | C6             | 132             | Input           | <b>ESSI Receive Data (SRD0)</b> —This input pin receives serial data and transfers the data to the ESSI Receive Shift Register.                                                                                                                                                                                                                                                                                                                       |  |

| GPIOC1         |                |                 | Input/Output    | <b>Port C GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SCK0           | C5             | 133             | Input/Output    | <b>ESSI Serial Clock (SCK0)</b> —This bidirectional pin provides the seria bit rate clock for the transmit section of the ESSI. The clock signal ca be continuous or gated and can be used by both the transmitter and receiver in synchronous mode.                                                                                                                                                                                                  |  |

| GPIOC2         |                |                 | Input/Output    | <b>Port C GPIO (2)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SC00           | D6             | 134             | Input/Output    | <b>ESSI Serial Control Pin 0 (SC00)</b> —The function of this pin is determined by the selection of either synchronous or asynchronous mode. For asynchronous mode, this pin will be used for the receive clock I/O. For synchronous mode, this pin is used either for transmitter1 output or for serial I/O flag 0.                                                                                                                                  |  |

| GPIOC3         |                |                 | Input/Output    | <b>Port C GPIO (3)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SC01           | B5             | 135             | Input/Output    | <b>ESSI Serial Control Pin 1 (SC01)</b> —The function of this pin is determined by the selection of either synchronous or asynchronous mode. For asynchronous mode, this pin is the receiver frame sync I/O. For synchronous mode, this pin is used either for transmitter2 output or for serial I/O flag 1.                                                                                                                                          |  |

| GPIOC4         |                |                 | Input/Output    | <b>Port C GPIO (4)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SC02           | E6             | 136             | Input/Output    | <b>ESSI Serial Control Pin 2 (SC02)</b> —This pin is used for frame sync I/O. SC02 is the frame sync for both the transmitter and receiver in synchronous mode and for the transmitter only in asynchronous mode. When configured as an output, this pin is the internally generated frame sync signal. When configured as an input, this pin receives an external frame sync signal for the transmitter (and the receiver in synchronous operation). |  |

| GPIOC5         |                |                 | Input or Output | <b>Port C GPIO (5)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------|----------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| STD1           | E8             | 99              | Output       | <b>ESSI Transmit Data (STD1)</b> —This output pin transmits serial data from the ESSI Transmitter Shift Register.                                                                                                                                                                                                                                                                                                                                     |  |

| GPIOD0         |                |                 | Input/Output | <b>Port D GPIO (0)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SRD1           | E11            | 100             | Input        | <b>ESSI Receive Data (SRD1)</b> —This input pin receives serial data and transfers the data to the ESSI Receive Shift Register.                                                                                                                                                                                                                                                                                                                       |  |

| GPIOD1         |                |                 | Input/Output | <b>Port D GPIO (1)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SCK1           | E9             | 101             | Input/Output | ut <b>ESSI Serial Clock (SCK1)</b> —This bidirectional pin provides the serial bit rate clock for the transmit section of the ESSI. The clock signal car be continuous or gated and can be used by both the transmitter and receiver in synchronous mode.                                                                                                                                                                                             |  |

| GPIOD2         |                |                 | Input/Output | the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| SC10           | D10            | 102             | Input/Output | <b>ESSI Serial Control Pin 0 (SC10)</b> —The function of this pin is determined by the selection of either synchronous or asynchronous mode. For asynchronous mode, this pin will be used for the receive clock I/O. For synchronous mode, this pin is used either for transmitter1 output or for serial I/O flag 0.                                                                                                                                  |  |

| GPIOD3         |                |                 | Input/Output | <b>Port D GPIO (3)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SC11           | D11            | 103             | Input/Output |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| GPIOD4         |                |                 | Input/Output | <b>Port D GPIO (4)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| SC12           | C11            | 104             | Input/Output | <b>ESSI Serial Control Pin 2 (SC12)</b> —This pin is used for frame sync I/O. SC02 is the frame sync for both the transmitter and receiver in synchronous mode and for the transmitter only in asynchronous mode. When configured as an output, this pin is the internally generated frame sync signal. When configured as an input, this pin receives an external frame sync signal for the transmitter (and the receiver in synchronous operation). |  |

| GPIOC5         |                |                 | Input/Output | <b>Port D GPIO (5)</b> —This pin is a General Purpose I/O (GPIO) pin when the ESSI is not in use.                                                                                                                                                                                                                                                                                                                                                     |  |

| Signal<br>Name | BGA<br>Pin No. | LQFP<br>Pin No. | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|----------------|----------------|-----------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MISO           | B2             | 1               | Input/Output         | SPI Master In/Slave Out (MISO)—This serial data pin is an input to a master device and an output from a slave device. The MISO line of a slave device is placed in the high-impedance state if the slave device is not selected. The driver on this pin can be configured as an open-drain driver by the SPI's Wired-OR mode (WOM) bit when this pin is configured for SPI operation.                                                                                                                                                                                                                                                           |  |  |  |