Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Freescale Semiconductor

Data Sheet: Technical Data

Document Number: DSP56724EC

Rev. 2, 3/2009

# DSP56724/DSP56725

# Symphony<sup>™</sup> DSP56724/ DSP56725 Multi-Core Audio Processors

The Symphony DSP56724/DSP56725 Multi-Core Audio Processors are part of the DSP5672x family of programmable CMOS DSPs, designed using dual DSP56300 24-bit cores.

The DSP56724 is intended for consumer and professional audio applications that require high performance for audio processing. In addition, the DSP56724 is ideally suited for applications that need the capability to expand memory off-chip or to interface to external parallel peripherals. Potential applications include A/V receivers, DVD Receivers, Home Theater in a Box (HTIB), and professional audio equipment including portable recording equipment, musical instruments, guitar amplifiers and pedals. The DSP56724 offers customers flexibility in their designs by providing a more cost-effective alternative to the DSP56720 while maintaining pin compatibility.

The DSP56725 is intended for automotive and audio applications that require high performance for audio processing. Potential applications include A/V receivers, DVD Receivers, Home Theater in a Box (HTIB), and automotive amplifiers and entertainment systems. The DSP56725 offers customers flexibility in their designs by providing a more cost-effective alternative to the DSP56721 while maintaining pin compatibility.

The DSP56724/DSP56725 devices provide a wealth of on-chip audio processing functions, via a plug and play software architecture system that supports audio decoding algorithms, various equalization algorithms, compression, signal generator, tone control, fade/balance, level meter/spectrum analyzer, among others. The DSP56724/DSP56725 devices also support various matrix decoders and sound field processing algorithms.

With two DSP56300 cores, a single DSP56724/ DSP56725 device can replace dual-DSP designs, saving costs while

See Table 19.

meeting high MIPs requirements. Legacy peripherals from the previous DSP5636x/37x families are included, as are a variety of new modules available in the DSP5672x family. Modules from the DSP56720 are included, such as an Asynchronous Sample Rate Converter (ASRC), an Inter-Core Communication (ICC) module, an External Memory Controller (EMC) to support SDRAM (DSP56724 only), and a Sony/Philips Digital Interface (S/PDIF) transceiver.

The DSP56724/DSP56725 devices offer up to 250 million instructions per second (MIPs) per core using an internal 250 MHz clock. The DSP56724/DSP56725 products are high density CMOS devices with 3.3 V inputs and outputs.

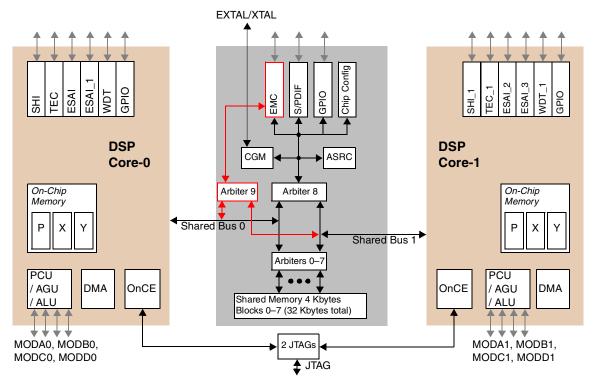

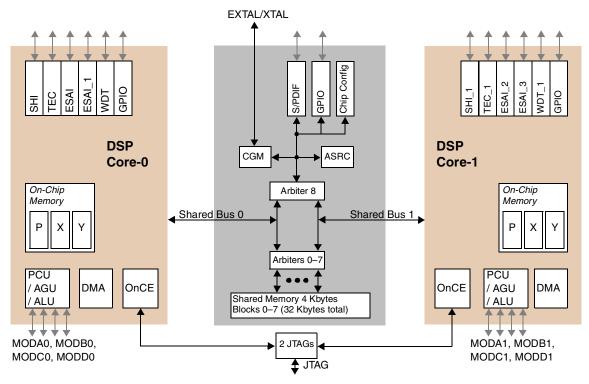

The DSP56724 block diagram is shown in Figure 1; the DSP56725 block diagram is shown in Figure 2.

#### NOTE

This document contains information on a new product. Specifications and information herein are subject to change without notice. Finalized specifications may be published after further characterization and device qualifications are completed.

This document contains information on a product under development. Freescale reserves the right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2009. All rights reserved.

# **Table of Contents**

| Elect | trical Characteristics4                                               |   | 1.2.6 JTAG Timing                                     |

|-------|-----------------------------------------------------------------------|---|-------------------------------------------------------|

| 1.1   | Chip-Level Conditions                                                 |   | 1.2.7 Watchdog Timer Timing                           |

|       | 1.1.1 Maximum Ratings                                                 |   | 1.2.8 S/PDIF Timing                                   |

|       | 1.1.2 Thermal Characteristics6                                        |   | 1.2.9 EMC Timing Specifications—DSP56724 34           |

|       | 1.1.3 Power Requirements                                              | 2 | Functional Description and Application Information 39 |

|       | 1.1.4 Power Consumption Considerations                                | 3 | Ordering Information                                  |

|       | 1.1.5 DC Electrical Characteristics8                                  | 4 | Package Information                                   |

|       | 1.1.6 AC Electrical Characteristics                                   |   | 4.1 Pinout and Package Information 40                 |

|       | 1.1.7 Internal Clocks                                                 |   | 4.1.1 Pinout for DSP56724 144-Pin Plastic LQFF        |

|       | 1.1.8 External Clock Operation10                                      |   | Package                                               |

|       | 1.1.9 Reset, Stop, Mode Select, and Interrupt Timing 11               |   | 4.1.2 Pinout for DSP56725 80-Pin Plastic LQFP Package |

| 1.2   | Module-Level Specifications                                           |   | 41                                                    |

|       | 1.2.1 Serial Host Interface SPI Protocol Timing 15                    |   | 4.1.3 Pin Multiplexing                                |

|       | 1.2.2 Serial Host Interface (SHI) I <sup>2</sup> C Protocol Timing.21 |   | 4.2 144-Pin Package Outline Drawing 42                |

|       | 1.2.3 Programming the SHI I <sup>2</sup> C Serial Clock 23            |   | 4.3 80-Pin Package Outline Drawing                    |

|       | 1.2.4 Enhanced Serial Audio Interface Timing 24                       | 5 | Product Documentation                                 |

|       | 1.2.5 GPIO Timing                                                     | 6 | Revision History                                      |

|       |                                                                       |   |                                                       |

Figure 1. DSP56724 Block Diagram

Figure 2. DSP56725 Block Diagram

## 1 Electrical Characteristics

## 1.1 Chip-Level Conditions

Table 1 provides a quick reference to the subsections in this section.

**Table 1. Chip-Level Conditions**

| For                                                             | See        |

|-----------------------------------------------------------------|------------|

| Section 1.1.1, "Maximum Ratings"                                | on page 4  |

| Section 1.1.2, "Thermal Characteristics"                        | on page 6  |

| Section 1.1.3, "Power Requirements"                             | on page 6  |

| Section 1.1.5, "DC Electrical Characteristics"                  | on page 8  |

| Section 1.1.6, "AC Electrical Characteristics"                  | on page 9  |

| Section 1.1.7, "Internal Clocks"                                | on page 9  |

| Section 1.1.8, "External Clock Operation"                       | on page 10 |

| Section 1.1.9, "Reset, Stop, Mode Select, and Interrupt Timing" | on page 11 |

## 1.1.1 Maximum Ratings

### **CAUTION**

This device contains circuitry protecting against damage due to high static voltage or electrical fields. However, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability of operation is enhanced if unused inputs are pulled to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ). The suggested value for a pull-up or pull-down resistor is 4.7 k $\Omega$ .

#### NOTE

In the calculation of timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification will never occur in the same device that has a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

Table 2 lists the maximum ratings.

**Table 2. Maximum Ratings**

| Rating <sup>1</sup>                                                                    | Symbol                                                                                          | Value <sup>1, 2</sup>  | Unit |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------|------|

| Supply Voltage                                                                         | V <sub>CORE_VDD</sub> , V <sub>PLLD_VDD</sub>                                                   | -0.3 to + 1.26         | V    |

|                                                                                        | V <sub>PLLP_VDD</sub> , V <sub>IO_VDD</sub> ,<br>V <sub>IO_VDD_25</sub> , V <sub>PLLA_VDD</sub> | -0.3 to + 4.0          | V    |

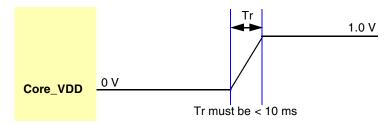

| Maximum CORE_VDD power supply ramp time                                                | Tr                                                                                              | 10                     | ms   |

| Input Voltage per pin excluding VDD and GND                                            | V <sub>IN</sub>                                                                                 | GND – 0.3 to 5.5 V     | V    |

| Current drain per pin excluding V <sub>DD</sub> and GND (Except for pads listed below) | I                                                                                               | 12                     | mA   |

| LSYNC_OUT                                                                              | I <sub>lsync_out</sub>                                                                          | 5                      | mA   |

| LCLK                                                                                   | I <sub>IcIk</sub>                                                                               | 5                      | mA   |

| LALE                                                                                   | I <sub>ale</sub>                                                                                | 5                      | mA   |

| TDO                                                                                    | I <sub>JTAG</sub>                                                                               | 12                     | mA   |

| Operating temperature range • Fsys < 200 MHz • Fsys < 250 MHz                          | T <sub>J</sub>                                                                                  | -40 to +100<br>0 to 90 | °C   |

| Storage temperature                                                                    | T <sub>STG</sub>                                                                                | -65 to +150            | °C   |

| ESD protected voltage (Human Body Model)                                               | _                                                                                               | 2000                   | V    |

| ESD protected voltage (Charged Device Model)  • All pins  • Corner pins                | _                                                                                               | 500<br>750             | V    |

<sup>1.</sup> GND = 0 V,  $T_J = -40^{\circ}$  C to  $100^{\circ}$  C, CL = 50 pF

<sup>2.</sup> Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the maximum rating may affect device reliability or cause permanent damage to the device.

### 1.1.2 Thermal Characteristics

Table 3 lists the thermal characteristics.

**Table 3. Thermal Characteristics**

| Characteristic                                                            | Symbol                  | LQFP Values                      | Unit                            |      |

|---------------------------------------------------------------------------|-------------------------|----------------------------------|---------------------------------|------|

| Natural Convection, Junction-to-ambient thermal resistance <sup>1,2</sup> | Single layer board (1s) | $R_{\theta JA}$ or $\theta_{JA}$ | 57 for 80 QFP<br>49 for 144 QFP | °C/W |

|                                                                           | Four layer board (2s2p) |                                  | 44 for 80 QFP<br>40 for 144 QFP | °C/W |

| Junction-to-case thermal resistance <sup>3</sup>                          | _                       | $R_{\theta JC}$ or $\theta_{JC}$ | 10 for 80 QFP<br>9 for 144 QFP  | °C/W |

#### Note:

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

### 1.1.3 Power Requirements

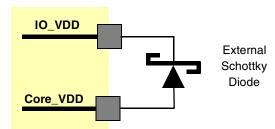

To prevent high current conditions due to possible improper sequencing of the power supplies, use an external Schottky diode as shown in Figure 3, connected between the DSP56724/DSP56725 IO\_VDD and Core\_VDD power pins.

Figure 3. Prevent High Current Conditions by Using External Schottky Diode

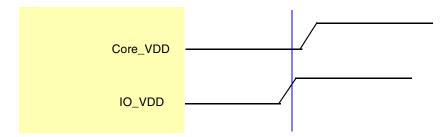

If an external Schottky diode is not used (to prevent a high current condition at power-up), then IO\_VDD must be applied ahead of Core\_VDD, as shown in Figure 4.

Figure 4. Prevent High Current Conditions by Applying IO\_VDD Before Core\_VDD

For correct operation of the internal power-on reset logic, the Core\_VDD ramp rate (Tr) to full supply must be less than 10 ms, as shown in Figure 4.

Figure 5. Ensure Correct Operation of Power-On Reset with Fast Ramp of Core\_VDD

### 1.1.4 Power Consumption Considerations

Power dissipation is a key issue in portable DSP applications. Some of the factors which affect current consumption are described in this section. Most of the current consumed by CMOS devices is alternating current (ac), which is charging and discharging the capacitances of the pins and internal nodes.

Current consumption is described by the following formula:

$$I = C \times V \times f$$

Eqn. 1

where C=node/pin capacitance

V=voltage swing

f=frequency of node/pin toggle

**Example 1. Power Consumption Example**

For a GPIO address pin loaded with 50 pF capacitance, operating at  $3.3\,V$ , and with a 150 MHz clock, toggling at its maximum possible rate (75 MHz), the current consumption is

$$I = 50x10^{-12}x3.3x75x10^6 = 12.375mA$$

**Eqn. 2**

The maximum internal current ( $I_{CCI}$ max) value reflects the typical possible switching of the internal buses on best-case operation conditions, which is not necessarily a real application case. The typical internal current ( $I_{CCItyp}$ ) value reflects the average switching of the internal buses on typical operating conditions.

For applications that require very low current consumption, do the following:

- Minimize the number of pins that are switching.

- Minimize the capacitive load on the pins.

One way to evaluate power consumption is to use a current per MIPS measurement methodology to minimize specific board effects (for example, to compensate for measured board current not caused by the DSP). Use the test algorithm, specific test current measurements, and the following equation to derive the current per MIPS value.

$$I/MIPS = I/MHz = (I_{tvpF2} - I_{tvpF1})/(F2 - F1)$$

Eqn. 3

$\begin{array}{ll} \text{where} \ : & \ I_{typF2}\text{=}\text{current at F2} \\ I_{tvDF1}\text{=}\text{current at F1} \end{array}$

F2=high frequency (any specified operating frequency)

F1=low frequency (any specified operating frequency lower than F2)

Symphony<sup>™</sup> DSP56724/ DSP56725 Multi-Core Audio Processors, Rev. 2

### **NOTE**

F1 should be significantly less than F2. For example, F2 could be 66 MHz and F1 could be 33 MHz. The degree of difference between F1 and F2 determines the amount of precision with which the current rating can be determined for an application.

## 1.1.5 DC Electrical Characteristics

**Table 4. DC Electrical Characteristics**

| Characteristics                                                                                                                           | Symbol                                                                    | Min             | Тур              | Max                      | Unit    |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------|------------------|--------------------------|---------|

| Core Supply voltages • Fsys < 200 MHz • Fsys < 250 MHz                                                                                    | V <sub>CORE_VDD</sub> ,<br>V <sub>PLLD_VDD</sub>                          | 0.95<br>1.14    | 1.0<br>1.2       | 1.05<br>1.26             | V       |

| IO Supply voltages                                                                                                                        | V <sub>IO_VDD</sub> ,<br>V <sub>PLLP_VDD</sub> ,<br>V <sub>PLLA_VDD</sub> | 3.14            | 3.3              | 3.45                     | V       |

| Input high voltage                                                                                                                        | V <sub>IH</sub>                                                           | 2.0             | _                | V <sub>IO_VDD</sub> + 2V | V       |

| Note: To avoid a high current condition and possible sy supplies rise.                                                                    | ystem damage                                                              | , all 3.3-V and | 2.5-V supplies n | nust rise before the     | e 1.0-V |

| Input low voltage                                                                                                                         | V <sub>IL</sub>                                                           | -0.3            | _                | 0.8                      | V       |

| Input leakage current                                                                                                                     | I <sub>IN</sub>                                                           | _               | _                | ± 80                     | μΑ      |

| Clock pin Input Capacitance (EXTAL)                                                                                                       | C <sub>IN</sub>                                                           | _               | 2.057            | _                        | pF      |

| High impedance (off-state) input current (@ 3.3 V or 0 V)                                                                                 | I <sub>TSI</sub>                                                          | -10             | _                | 10                       | μА      |

| Output high voltage $I_{OH} = -12 \text{ mA}$<br>LSYNC_OUT, LALE, LCLK Pins $I_{OH} = -16 \text{ mA}$ , TDO Pin $I_{OH} = -24 \text{ mA}$ | V <sub>OH</sub>                                                           | 2.4             | _                | _                        | V       |

| Output low voltage $I_{OL}$ = 12 mA LSYNC_OUT, LALE, LCLK Pins $I_{OL}$ = 16 mA, TDO Pins $I_{OL}$ = 24 mA                                | V <sub>OL</sub>                                                           | _               | _                | 0.4                      | V       |

| Internal pull-up resistor                                                                                                                 | R <sub>PU</sub>                                                           | 63              | 92               | 142                      | kΩ      |

| Internal pull-down resistor                                                                                                               | R <sub>PD</sub>                                                           | 57              | 91               | 159                      | kΩ      |

| Internal supply current <sup>1</sup> (core only) operating at Fsys < 200 MHz • In Normal mode                                             | I <sub>CCI</sub>                                                          | _               | 90               | 280                      | mA      |

| In Wait mode                                                                                                                              | I <sub>CCW</sub>                                                          | _               | 60               | 250                      | mA      |

| In Stop mode <sup>2</sup>                                                                                                                 | I <sub>ccs</sub>                                                          | _               | 30               | 220                      | mA      |

**Table 4. DC Electrical Characteristics (Continued)**

| Characteristics                                                              | Symbol           | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Internal supply current <sup>1</sup> (core only) operating at Fsys < 250 MHz |                  |     |     |     |      |

| In Normal mode                                                               | I <sub>CCI</sub> | _   | 140 | 340 | mA   |

| In Wait mode                                                                 | I <sub>CCW</sub> | _   | 90  | 290 | mA   |

| • In Stop mode <sup>2</sup>                                                  | I <sub>CCS</sub> |     | 40  | 240 | mA   |

| Input capacitance                                                            | C <sub>IN</sub>  | _   | _   | 10  | pF   |

- 1. The Current Consumption section provides a formula to compute the estimated current requirements in Normal mode. In order to obtain these results, all inputs must be terminated (for example, not allowed to float). Measurements are based on synthetic intensive DSP benchmarks. The power consumption numbers in this specification are 90% of the measured results of this benchmark. This reflects typical DSP applications. Typical internal supply current with Fsys < 200 MHz is measured with V<sub>CORE\_VDD</sub> = 1.0 V, V<sub>DD\_IO</sub> = 3.3 V at T<sub>J</sub> = 25° C. Maximum internal supply current is measured with V<sub>CORE\_VDD</sub> = 1.05 V, V<sub>IO\_VDD</sub>) = 3.6 V at T<sub>J</sub> = 100° C. Typical internal supply current with Fsys < 250 MHz is measured with V<sub>CORE\_VDD</sub> = 1.2 V, V<sub>DD\_IO</sub> = 3.3 V at T<sub>J</sub> = 25° C. Maximum internal supply current is measured with V<sub>CORE\_VDD</sub> = 1.26 V, V<sub>IO\_VDD</sub>) = 3.6 V at T<sub>J</sub> = 90° C.

- 2. In order to obtain these results, all inputs, which are not disconnected at Stop mode, must be terminated (that is, not allowed to float).

### 1.1.6 AC Electrical Characteristics

The timing waveforms shown in the AC electrical characteristics section are tested with a  $V_{IL}$  maximum of 0.8 V and a  $V_{IH}$  minimum of 2.0 V for all pins. AC timing specifications, which are referenced to a device input signal, are measured in production with respect to the 50% point of the respective input signal's transition. For all pins, output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at 0.4 V and 2.4 V, respectively.

### 1.1.7 Internal Clocks

Table 5 lists the internal clocks.

**Table 5. Internal Clocks**

| No. | Characteristics                                              | Symbol | Min | Тур | Max        | Unit | Condition     |

|-----|--------------------------------------------------------------|--------|-----|-----|------------|------|---------------|

| 1   | Comparison Frequency                                         | Fref   | 2   | _   | 8          | MHz  | Fref = Fin/NR |

| 2   | Input Clock Frequency • with PLL enabled • with PLL disabled | Fin    | 2 — | _   | 248<br>200 | MHz  | _             |

**Table 5. Internal Clocks (Continued)**

| No. | Characteristics                                                               | Symbol | Min        | Тур | Max                      | Unit | Condition                                  |

|-----|-------------------------------------------------------------------------------|--------|------------|-----|--------------------------|------|--------------------------------------------|

| 3   | PLL VCO Frequency                                                             | Fvco   | 200        | _   | 500                      | MHz  | Fvco = (Fin * NF)/NR                       |

| 4   | Output Clock Frequency [1] [2] • with PLL enabled • with PLL disabled         | Fout   | 25<br>—    | _   | 200 or 250<br>200 or 250 | MHz  | Fout = Fvco/NO<br>Fout = Fin               |

| 5   | System Clock Frequency  • with PLL enabled <sup>[2]</sup> • with PLL disabled | Fsys   | 0.195<br>0 | _   | 200 or 250<br>200        | MHz  | Fsys = Fout/2 <sup>DF</sup><br>Fsys = Fout |

1. Fin = External frequency

NF = Multiplication Factor

NR = Predivision Factor

NO = Output Divider

DF = Division Factor

2. Maximum frequency of 200 MHz supported at 0.95 V < V<sub>VDD\_CORE</sub> < 1.05 V and -40 < Tj < 100° C Maximum frequency of 250 MHz supported at 1.14 V < V<sub>VDD\_CORE</sub> < 1.26 V and 0 < Tj < 90° C

## 1.1.8 External Clock Operation

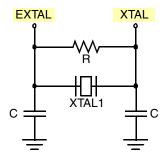

The DSP56724/DSP56725 system clock is derived from the on-chip oscillator or is externally supplied. To use the on-chip oscillator, connect a crystal and associated resistor/capacitor components to EXTAL and XTAL; see Figure 6.

Suggested component values:

$^{f}$ osc = 24.576 MHz R = 1 M ±10% C (EXTAL)= 18 pF C (XTAL) = 18 pF

Calculations are for a 5–30 MHz crystal with the following parameters:

- shunt capacitance (C<sub>0</sub>) of 10 pq–F12 pF

- series resistance 40 Ŏhm

- drive level of 10 μW

Figure 6. Using the On-Chip Oscillator

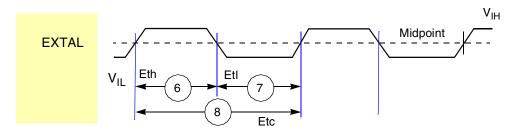

If the DSP56724/DSP56725 system clock is an externally supplied square wave voltage source, it is connected to EXTAL (Figure 7). When the external square wave source is connected to EXTAL, the XTAL pin is not used.

Note: The midpoint is 0.5 ( $V_{IH} + V_{IL}$ ).

Figure 7. External Clock Timing

Table 6 lists the clock operation.

**Table 6. Clock Operation**

| No. | Characteristics                                                                                | Symbol | Min                 | Max         | Units |

|-----|------------------------------------------------------------------------------------------------|--------|---------------------|-------------|-------|

| 6   | EXTAL input high <sup>1</sup> (40% to 60% duty cycle) • Crystal oscillator • Square wave input | Eth    | 16.67<br>2.5        | 100<br>inf  | ns    |

| 7   | EXTAL input low <sup>1</sup> (40% to 60% duty cycle) • Crystal oscillator • Square wave input  | Etl    | 16.67<br>2.5        | 100<br>inf  | ns    |

| 8   | EXTAL cycle time  With PLL disabled  With PLL enabled                                          | Etc    | 5<br>33.3           | inf<br>500  | ns    |

| 9   | Instruction cycle time  With PLL disabled  With PLL enabled                                    | Тс     | 5<br>4 <sup>4</sup> | inf<br>5120 | ns    |

#### Note:

- 1. Measured at 50% of the input transition.

- 2. The indicated duty cycle is for the specified maximum frequency for which a part is rated. The minimum clock high or low time required for correct operation, however, remains the same at lower operating frequencies; therefore, when a lower clock frequency is used, the signal symmetry may vary from the specified duty cycle as long as the minimum high time and low time requirements are met.

- 3. Maximum frequency of 200 MHz supported at 0.95 V <  $V_{VDD\_CORE}$  < 1.05 V and -40 < Tj < 100° C Maximum frequency of 250 MHz supported at 1.14 V <  $V_{VDD\_CORE}$  < 1.26 V and 0 < Tj < 90° C

- 4.  $PLL_{LOCK} = 200 \mu s$ .

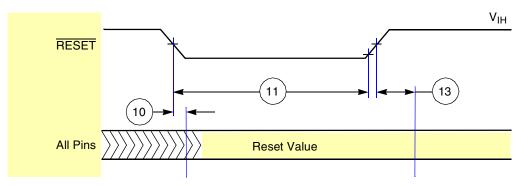

## 1.1.9 Reset, Stop, Mode Select, and Interrupt Timing

Table 7 lists the reset, stop, mode select, and interrupt timing.

Table 7. Reset, Stop, Mode Select, and Interrupt Timing

| No. | Characteristics                                                                                                                            | Expression                                                    | Min       | Max    | Unit     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------|--------|----------|

| 10  | Delay from RESET assertion to all pins at reset value <sup>3</sup>                                                                         | _                                                             | _         | 11     | ns       |

| 11  | Required RESET duration <sup>4</sup> • Power on, external clock generator, PLL disabled  • Power on, external clock generator, PLL enabled | 2×T <sub>C</sub> 2×T <sub>C</sub>                             | 10<br>10  |        | ns<br>ns |

| 13  | Syn reset deassert delay time  • Minimum  • Maximum (PLL enabled)                                                                          | 2 × T <sub>C</sub><br>(2xT <sub>C</sub> )+PLL <sub>LOCK</sub> | 10<br>200 | _<br>_ | ns<br>us |

| 14  | Mode select setup time                                                                                                                     | _                                                             | 10        | _      | ns       |

| 15  | Mode select hold time                                                                                                                      | _                                                             | 12        | _      | ns       |

| 16  | Minimum edge-triggered interrupt request assertion width                                                                                   | _                                                             | 7         | _      | ns       |

| 17  | Minimum edge-triggered interrupt request deassertion width                                                                                 | _                                                             | 4         | _      | ns       |

| 18  | Delay from interrupt trigger to interrupt code execution                                                                                   | 10 × T <sub>C + 4</sub>                                       | 54        | _      | ns       |

Symphony<sup>™</sup> DSP56724/ DSP56725 Multi-Core Audio Processors, Rev. 2

Table 7. Reset, Stop, Mode Select, and Interrupt Timing (Continued)

| No. | Characteristics                                                                                                                                              | Expression                                   | Min | Max  | Unit |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|------|------|

| 19  | Duration of level sensitive IRQA assertion to ensure interrupt service (when exiting Stop) <sup>1, 2, 3</sup>                                                |                                              |     |      |      |

|     | • PLL is active during Stop and Stop delay is enabled (OMR Bit 6 = 0)                                                                                        | (128 Kbytes × T <sub>C)</sub>                | 655 | _    | μs   |

|     | PLL is active during Stop and Stop delay is not enabled (OMR Bit 6 = 1)                                                                                      | 25 × T <sub>C</sub>                          | 125 | _    | ns   |

|     | PLL is not active during Stop and Stop delay is enabled (OMR Bit 6 = 0)                                                                                      | (128KxT <sub>C</sub> ) + PLL <sub>LOCK</sub> | 855 | _    | μs   |

|     | PLL is not active during Stop and Stop delay is not enabled (OMR Bit 6 = 1)                                                                                  | (25 × T <sub>C</sub> ) + PLL <sub>LOCK</sub> | 200 | _    | μs   |

| 20  | Delay from IRQA, IRQB, IRQC, IRQD, NMI assertion to<br>general-purpose transfer output valid caused by first interrupt<br>instruction execution <sup>1</sup> | 10 × T <sub>C</sub> + 3.8                    | _   | 53.8 | ns   |

| 21  | Interrupt Requests Rate <sup>1</sup> • ESAI, ESAI_1, ESAI_2, ESAI_3, SHI, SHI_1, Timer, Timer_1                                                              | 12×T <sub>C</sub>                            | _   | 60.0 | ns   |

|     | • DMA                                                                                                                                                        | 8 × T <sub>C</sub>                           | _   | 40.0 | ns   |

|     | ĪRQ, NMI (edge trigger)                                                                                                                                      | 8×T <sub>C</sub>                             | _   | 40.0 | ns   |

|     | ĪRQ (level trigger)                                                                                                                                          | 12×T <sub>C</sub>                            | _   | 60.0 | ns   |

| 22  | DMA Requests Rate  • Data read from ESAI, ESAI_1, ESAI_2, ESAI_3, SHI, SHI_1                                                                                 | 6×T <sub>C</sub>                             | _   | 30.0 | ns   |

|     | Data write to ESAI, ESAI_1, ESAI_2, ESAI_3, SHI, SHI_1                                                                                                       | 7×T <sub>C</sub>                             | _   | 35.0 | ns   |

|     | Timer, Timer_1                                                                                                                                               | $2 \times T_{\mathbb{C}}$                    | _   | 10.0 | ns   |

|     | ĪRQ, NMI (edge trigger)                                                                                                                                      | $3 \times T_C$                               | _   | 15.0 | ns   |

- 1. When using fast interrupts and when IRQA, IRQB, IRQC, and IRQD are defined as level-sensitive, timings 19 through 21 apply to prevent multiple interrupt service. To avoid these timing restrictions, the Edge-triggered mode is recommended when using fast interrupts. Long interrupts are recommended when using Level-sensitive mode.

- 2. For PLL disable, if using an external clock (PCTL Bit 13 = 1), no stabilization delay is required and recovery time will be defined by the OMR Bit 6 settings.

- For PLL enable, (if bit 12 of the PCTL register is 0), the PLL is shut down during Stop. Recovering from Stop requires the PLL to get locked. The PLL lock procedure duration, PLL Lock Cycles (PLC), may be in the range of 200 us.

- 3. Periodically sampled and not 100% tested.

- 4. RESET duration is measured during the time in which RESET is asserted, V<sub>DD</sub> is valid, and the EXTAL input is active and valid. When V<sub>DD</sub> is valid, but the other "required RESET duration" conditions (as specified above) have not been yet met, the device circuitry will be in an uninitialized state that can result in significant power consumption and heat-up. Designs should minimize this state to the shortest possible duration.

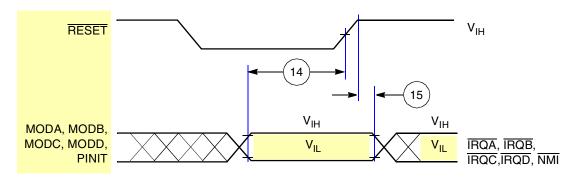

Figure 8 shows the reset timing diagram.

Figure 8. Reset Timing

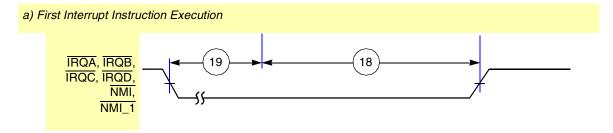

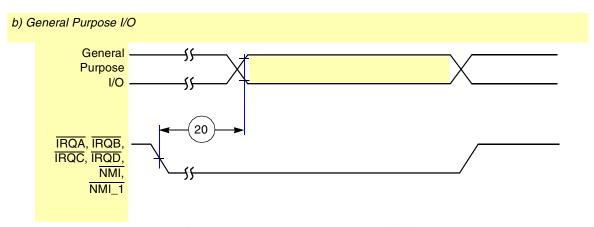

Figure 9 shows external fast interrupt timing diagram.

Figure 9. External Fast Interrupt Timing

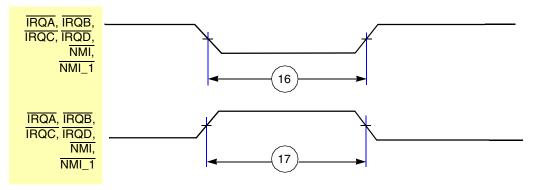

Figure 10 shows external interrupt timing (negative edge-triggered).

Figure 10. External Interrupt Timing (Negative Edge-Triggered)

Figure 11 shows MODE select set-up and hold time diagram.

Figure 11. MODE Select Set-Up and Hold Time

# 1.2 Module-Level Specifications

Table 8 provides a quick reference to the subsections of this section.

**Table 8. Module-Level Specifications**

| For                                                                           | See        |

|-------------------------------------------------------------------------------|------------|

| Section 1.2.1, "Serial Host Interface SPI Protocol Timing"                    | on page 4  |

| Section 1.2.2, "Serial Host Interface (SHI) I <sup>2</sup> C Protocol Timing" | on page 6  |

| Section 1.2.3, "Programming the SHI I <sup>2</sup> C Serial Clock"            | on page 6  |

| Section 1.2.4, "Enhanced Serial Audio Interface Timing"                       | on page 8  |

| Section 1.2.5, "GPIO Timing"                                                  | on page 29 |

| Section 1.2.6, "JTAG Timing"                                                  | on page 30 |

| Section 1.2.7, "Watchdog Timer Timing"                                        | on page 32 |

| Section 1.2.8, "S/PDIF Timing"                                                | on page 33 |

| Section 1.2.9, "EMC Timing Specifications—DSP56724"                           | on page 34 |

# 1.2.1 Serial Host Interface SPI Protocol Timing

Table 9 lists the serial host interface SPI protocol timing.

Table 9. Serial Host Interface SPI Protocol Timing

| No. | Characteristics <sup>1,3,4</sup>                      | Mode            | Filter Mode | Expression                   | Min   | Max            | Unit     |

|-----|-------------------------------------------------------|-----------------|-------------|------------------------------|-------|----------------|----------|

| 23  | Minimum serial clock cycle = t <sub>SPICC</sub> (min) | Master/Slave    | Bypassed    | 10 × T <sub>C</sub> + 9      | 59.0  | _              | ns       |

|     |                                                       |                 | Very Narrow | 10 × T <sub>C</sub> + 9      | 59.0  | _              | ns       |

|     |                                                       |                 | Narrow      | 10 × T <sub>C</sub> + 133    | 183.0 | _              | ns       |

|     |                                                       |                 | Wide        | 10 × T <sub>C</sub> + 333    | 383.0 | _              | ns       |

| XX  | Tolerable Spike width on data or clock in.            | _               | Bypassed    | _                            | _     | 0              | ns       |

|     |                                                       |                 | Very Narrow | _                            | _     | 10             | ns       |

|     |                                                       |                 | Narrow      | _                            | _     | 50             | ns       |

|     |                                                       |                 | Wide        | _                            | _     | 100            | ns       |

| 24  | Serial clock high period                              | Master          | Bypassed    | $0.5 \times (t_{SPICC})$     | 29.5  | _              | ns       |

|     |                                                       |                 | Very Narrow | $0.5 \times (t_{SPICC})$     | 29.5  | _              | ns       |

|     |                                                       |                 | Narrow      | $0.5 \times (t_{SPICC})$     | 91.5  | _              | ns       |

|     |                                                       |                 | Wide        | $0.5 \times (t_{SPICC})$     | 191.5 | _              | ns       |

|     |                                                       | Slave           | Bypassed    | $2.0 \times T_{C} + 19.6$    | 29.6  | _              | ns       |

|     |                                                       |                 | Very Narrow | 2.0 × T <sub>C</sub> + 19.6  | 29.6  | _              | ns       |

|     |                                                       |                 | Narrow      | 2.0 × T <sub>C</sub> + 86.6  | 96.6  | _              | ns       |

|     |                                                       |                 | Wide        | 2.0 × T <sub>C</sub> + 186.6 | 196.6 | _              | ns       |

| 25  | Serial clock low period                               | Master          | Bypassed    | 0.5 × (t <sub>SPICC</sub> )  | 29.5  | _              | ns       |

|     |                                                       |                 | Very Narrow | $0.5 \times (t_{SPICC})$     | 29.5  | _              | ns       |

|     |                                                       |                 | Narrow      | $0.5 \times (t_{SPICC})$     | 91.5  | _              | ns       |

|     |                                                       |                 | Wide        | 0.5 × t <sub>SPICC</sub> )   | 191.5 | _              | ns       |

|     |                                                       | Slave           | Bypassed    | $2.0 \times T_{C} + 19.6$    | 29.6  | _              | ns       |

|     |                                                       |                 | Very Narrow | 2.0 × T <sub>C</sub> + 19.6  | 29.6  | _              | ns       |

|     |                                                       |                 | Narrow      | 2.0 × T <sub>C</sub> + 86.6  | 96.6  | _              | ns       |

|     |                                                       |                 | Wide        | 2.0 × T <sub>C</sub> + 186.6 | 196.6 | _              | ns       |

| 26  | Serial clock rise/fall time                           | Master<br>Slave | _<br>_      | _<br>_                       | _     | <del>_</del> 5 | ns<br>ns |

**Table 9. Serial Host Interface SPI Protocol Timing (Continued)**

| No. | Characteristics <sup>1,3,4</sup>                   | Mode   | Filter Mode | Expression               | Min   | Max  | Unit |

|-----|----------------------------------------------------|--------|-------------|--------------------------|-------|------|------|

| 27  | SS assertion to first SCK edge                     | Slave  | Bypassed    | 2.0 × T <sub>C</sub> + 2 | 35    | _    | ns   |

|     | CPHA = 0                                           |        | Very Narrow | 2.0 × T <sub>C</sub> + 1 | 25    | _    | ns   |

|     |                                                    |        | Narrow      | _                        | 0     | _    | ns   |

|     |                                                    |        | Wide        | _                        | 0     | _    | ns   |

|     | CPHA = 1                                           | Slave  | Bypassed    | _                        | 10    | _    | ns   |

|     |                                                    |        | Very Narrow | _                        | 0     | _    | ns   |

|     |                                                    |        | Narrow      | _                        | 0     | _    | ns   |

|     |                                                    |        | Wide        | _                        | 0     | _    | ns   |

| 28  | Last SCK edge to SS not asserted                   | Slave  | Bypassed    | _                        | 12    | _    | ns   |

|     |                                                    |        | Very Narrow | _                        | 22    | _    | ns   |

|     |                                                    |        | Narrow      | _                        | 100   | _    | ns   |

|     |                                                    |        | Wide        | _                        | 200   |      | ns   |

| 29  | Data input valid to SCK edge (data input           | Master | Bypassed    | _                        | 0     | _    | ns   |

|     | set-up time)                                       | /Slave | Very Narrow | _                        | 0     | _    | ns   |

|     |                                                    |        | Narrow      | _                        | 0     | _    | ns   |

|     |                                                    |        | Wide        | _                        | 0     | _    | ns   |

| 30  | SCK last sampling edge to data input not           | Master | Bypassed    | 2 × T <sub>C</sub> + 10  | 20    | _    | ns   |

|     | valid                                              | /Slave | Very Narrow | 2 × T <sub>C</sub> + 30  | 40    | _    | ns   |

|     |                                                    |        | Narrow      | 2×T <sub>C</sub> +60     | 70    |      | ns   |

|     |                                                    |        | Wide        | _                        | 100.0 | _    | ns   |

| 31  | SS assertion to data out active                    | Slave  | _           | _                        | 5     | _    | ns   |

| 32  | SS deassertion to data high impedance <sup>2</sup> | Slave  | _           | _                        | _     | 9    | ns   |

| 33  | SCK edge to data out valid                         | Master | Bypassed    | _                        | _     | 45   | ns   |

|     | (data out delay time)                              | /Slave | Very Narrow | _                        | _     | 110  | ns   |

|     |                                                    |        | Narrow      | _                        | _     | 135  | ns   |

|     |                                                    |        | Wide        | _                        | _     | 225  | ns   |

| 34  | SCK edge to data out not valid                     | Master | Bypassed    | _                        | 10    | _    | ns   |

|     | (data out hold time)                               | /Slave | Very Narrow | _                        | 15    | _    | ns   |

|     |                                                    |        | Narrow      | _                        | 55    | _    | ns   |

|     |                                                    |        | Wide        | _                        | 105   | _    | ns   |

| 35  | SS assertion to data out valid<br>(CPHA = 0)       | Slave  | _           | _                        | _     | 14.0 | ns   |

**Table 9. Serial Host Interface SPI Protocol Timing (Continued)**

| No. | Characteristics <sup>1,3,4</sup>                                                                                        | Mode   | Filter Mode | Expression           | Min   | Max | Unit |

|-----|-------------------------------------------------------------------------------------------------------------------------|--------|-------------|----------------------|-------|-----|------|

| 36  | First SCK sampling edge to HREQ output                                                                                  | Slave  | Bypassed    | _                    | 45    | _   | ns   |

|     | deassertion                                                                                                             |        | Very Narrow | _                    | 55    | _   | ns   |

|     |                                                                                                                         |        | Narrow      | _                    | 95    | _   | ns   |

|     |                                                                                                                         |        | Wide        | _                    | 145   | _   | ns   |

| 37  | Last SCK sampling edge to HREQ output                                                                                   | Slave  | Bypassed    | _                    | 50.0  | _   | ns   |

|     | not deasserted (CPHA = 1)                                                                                               |        | Very Narrow | _                    | 60.0  | _   | ns   |

|     |                                                                                                                         |        | Narrow      | _                    | 100.0 | _   | ns   |

|     |                                                                                                                         |        | Wide        | _                    | 150.0 | _   | ns   |

| 38  | SS deassertion to HREQ output not deasserted (CPHA = 0)                                                                 | Slave  | _           | _                    | 45.0  | _   | ns   |

| 39  | SS deassertion pulse width (CPHA = 0)                                                                                   | Slave  | _           | $2 \times T_C$       | 0     | _   | ns   |

| 40  | $\overline{\text{HREQ}}$ in deassertion to last SCK sampling edge ( $\overline{\text{HREQ}}$ in set-up time) (CPHA = 1) | Master | _           | _                    | 0     | _   | ns   |

| 41  | First SCK edge to HREQ in not asserted (HREQ in hold time)                                                              | Master | _           | _                    | 0     | _   | ns   |

| 42  | HREQ assertion width                                                                                                    | Master | _           | 3.0 × T <sub>C</sub> | 15    | _   | ns   |

- 1. 0.95 V <  $V_{VDD\_CORE}$  < 1.05 V and  $T_{J}$  < 100° C,  $C_{L}$  = 50 pF

- 2. Periodically sampled, not 100% tested

- 3. All times assume noise free inputs.

- 4. All times assume internal clock frequency of 200 MHz.

- 5. SHI\_1 specs match those of SHI

- 6. Slave timings should equal the serial clock high period + the serial clock low period.

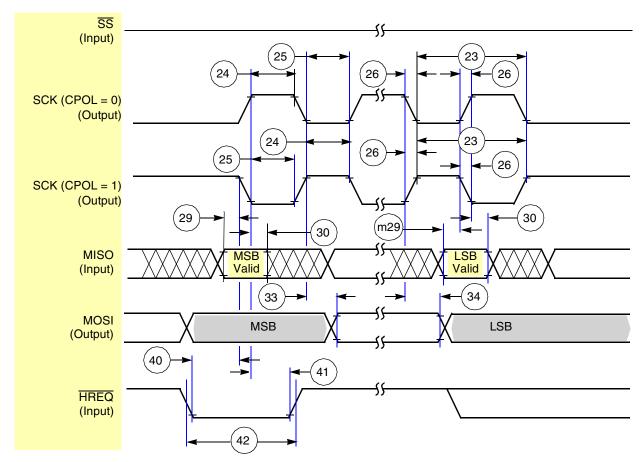

Figure 12 shows the SPI master timing (CPHA = 0).

Figure 12. SPI Master Timing (CPHA = 0)

Figure 13 shows the SPI master timing (CPHA = 1).

Figure 13. SPI Master Timing (CPHA = 1)

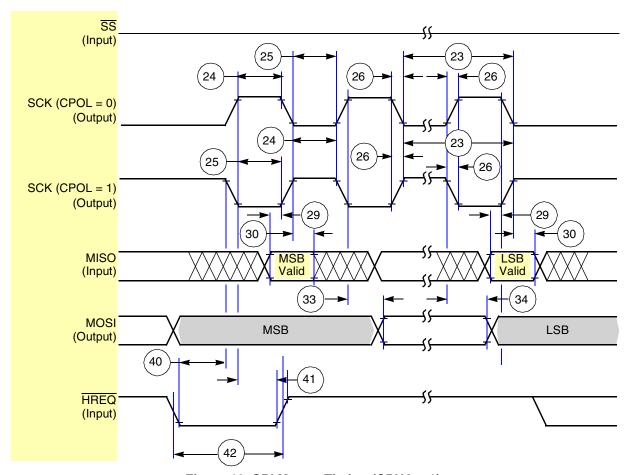

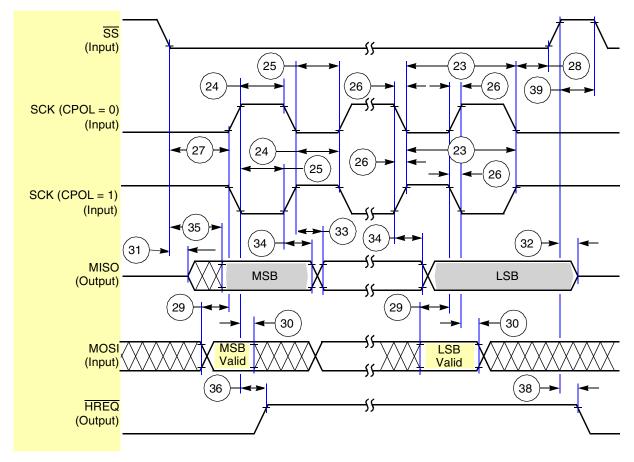

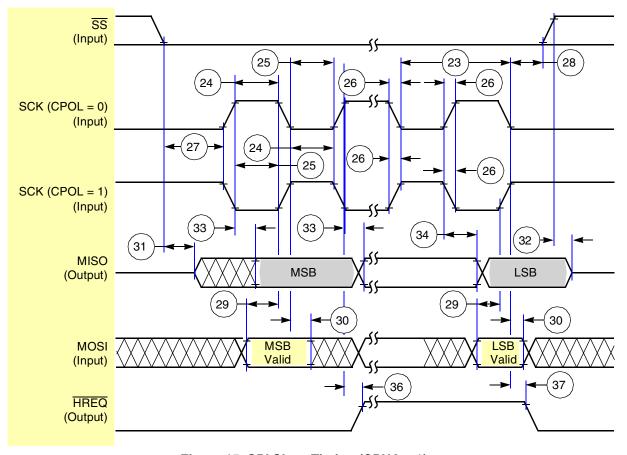

Figure 14 shows the SPI slave timing (CPHA = 0).

Figure 14. SPI Slave Timing (CPHA = 0)

Figure 15 shows the SPI slave timing (CPHA = 1).

Figure 15. SPI Slave Timing (CPHA = 1)

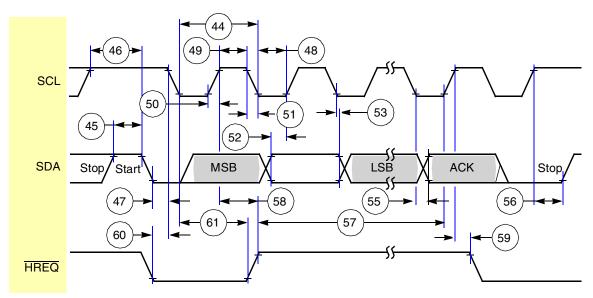

# 1.2.2 Serial Host Interface (SHI) I<sup>2</sup>C Protocol Timing

Table 10 lists the SHI I<sup>2</sup>C protocol timing diagram.

Table 10. SHI I<sup>2</sup>C Protocol Timing

|     | Standard I <sup>2</sup> C                                                                                                     |                    |                  |                      |                  |                      |                      |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|----------------------|------------------|----------------------|----------------------|--|--|

| No. | Characteristics <sup>1,2,3,4,5</sup>                                                                                          | Symbol/            | Stan             | dard                 | Fast-M           | Unit                 |                      |  |  |

| NO. | Cital acteristics                                                                                                             | Expression         | Min              | Max                  | Min              | Max                  | Unit                 |  |  |

| XX  | Tolerable Spike Width on SCL or SDA Filters Bypassed Very Narrow Filters enabled Narrow Filters enabled Wide Filters enabled. | _                  | _<br>_<br>_<br>_ | 0<br>10<br>50<br>100 | _<br>_<br>_<br>_ | 0<br>10<br>50<br>100 | ns<br>ns<br>ns<br>ns |  |  |

| 44  | SCL clock frequency                                                                                                           | F <sub>SCL</sub>   | _                | 100                  | _                | 400                  | kHz                  |  |  |

| 44  | SCL clock cycle                                                                                                               | T <sub>SCL</sub>   | 10               | _                    | 2.5              | _                    | μs                   |  |  |

| 45  | Bus free time                                                                                                                 | T <sub>BUF</sub>   | 4.7              | _                    | 1.3              | _                    | μs                   |  |  |

| 46  | Start condition set-up time                                                                                                   | T <sub>SUSTA</sub> | 4.7              | _                    | 0.6              | _                    | μs                   |  |  |

Symphony<sup>™</sup> DSP56724/ DSP56725 Multi-Core Audio Processors, Rev. 2

Table 10. SHI I<sup>2</sup>C Protocol Timing (Continued)

|     | Standard I <sup>2</sup> C                                                                                                                                           |                                                                                                        |                              |                                |                              |                                |                          |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------|------------------------------|--------------------------------|--------------------------|--|--|

| N   | Characteristics <sup>1,2,3,4,5</sup>                                                                                                                                | Symbol/                                                                                                | Star                         | ıdard                          | Fast-N                       | lode                           | 11                       |  |  |

| No. |                                                                                                                                                                     | Expression                                                                                             | Min                          | Max                            | Min                          | Max                            | Unit                     |  |  |

| 47  | Start condition hold time                                                                                                                                           | T <sub>HD;STA</sub>                                                                                    | 4.0                          | _                              | 0.6                          | _                              | μs                       |  |  |

| 48  | SCL low period                                                                                                                                                      | T <sub>LOW</sub>                                                                                       | 4.7                          | _                              | 1.3                          | _                              | μs                       |  |  |

| 49  | SCL high period                                                                                                                                                     | T <sub>HIGH</sub>                                                                                      | 4.0                          | _                              | 1.3                          | _                              | μs                       |  |  |

| 50  | SCL and SDA rise time <sup>7</sup>                                                                                                                                  | T <sub>R</sub>                                                                                         | _                            | 1000                           | _                            | 300                            | ns                       |  |  |

| 51  | SCL and SDA fall time <sup>7</sup>                                                                                                                                  | T <sub>F</sub>                                                                                         | _                            | 5.0                            | _                            | 5.0                            | ns                       |  |  |

| 52  | Data set-up time                                                                                                                                                    | T <sub>SU;DAT</sub>                                                                                    | 250                          | _                              | 100                          | _                              | ns                       |  |  |

| 53  | Data hold time                                                                                                                                                      | T <sub>HD;DAT</sub>                                                                                    | 0.0                          | _                              | 0.0                          | 0.9                            | μs                       |  |  |

| 54  | DSP clock frequency     Filters bypassed     Very Narrow filters enabled     Narrow filters enabled     Wide filters enabled                                        | F <sub>osc</sub>                                                                                       | 10.6<br>10.6<br>11.8<br>13.1 | _<br>_<br>_<br>_               | 28.5<br>28.5<br>39.7<br>61.0 | _<br>_<br>_                    | MHz<br>MHz<br>MHz<br>MHz |  |  |

| 55  | SCL low to data out valid                                                                                                                                           | T <sub>VD;DAT</sub>                                                                                    | _                            | 3.4                            | _                            | 0.9                            | μs                       |  |  |

| 56  | Stop condition setup time                                                                                                                                           | T <sub>SU;STO</sub>                                                                                    | 4.0                          | _                              | 0.6                          | _                              | μs                       |  |  |

| 57  | HREQ in deassertion to last SCL edge (HREQ in set-up time)                                                                                                          | t <sub>SU;RQI</sub>                                                                                    | 0.0                          | _                              | 0.0                          | _                              | ns                       |  |  |

| 58  | First SCL sampling edge to HREQ output deassertion <sup>2</sup> • Filters bypassed  • Very Narrow filters enabled  • Narrow filters enabled  • Wide filters enabled | $T_{NG;RQO}$ $4 \times T_{C} + 30$ $4 \times T_{C} + 50$ $4 \times T_{C} + 130$ $4 \times T_{C} + 230$ |                              | 50.0<br>70.0<br>250.0<br>150.0 |                              | 50.0<br>70.0<br>150.0<br>250.0 | ns<br>ns<br>ns<br>ns     |  |  |

| 59  | Last SCL edge to HREQ output not deasserted <sup>2</sup> • Filters bypassed • Very Narrow filters enabled • Narrow filters enabled • Wide filters enabled           | $T_{AS;RQO}$ $2 \times T_{C} + 30$ $2 \times T_{C} + 40$ $2 \times T_{C} + 80$ $2 \times T_{C} + 130$  | 40<br>50<br>90<br>140        | _<br>_<br>_<br>_               | 40<br>50<br>90<br>140        | _<br>_<br>_<br>_               | ns<br>ns<br>ns           |  |  |

Table 10. SHI I<sup>2</sup>C Protocol Timing (Continued)

|     | Standard I <sup>2</sup> C                                                                                                    |                     |                              |                  |                          |                  |                |  |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------|------------------|--------------------------|------------------|----------------|--|--|--|

| No. | Characteristics <sup>1,2,3,4,5</sup>                                                                                         | Symbol/             | Standard                     |                  | Fast-N                   | Unit             |                |  |  |  |

|     |                                                                                                                              | Expression          | Min                          | Max              | Min                      | Max              |                |  |  |  |

| 60  | HREQ in assertion to first SCL edge Filters bypassed Very Narrow filters enabled Narrow filters enabled Wide filters enabled | T <sub>AS;RQI</sub> | 4327<br>4317<br>4282<br>4227 | _<br>_<br>_<br>_ | 927<br>917<br>877<br>827 | _<br>_<br>_<br>_ | ns<br>ns<br>ns |  |  |  |

| 61  | First SCL edge to HREQ is not asserted (HREQ in hold time.)                                                                  | t <sub>HO;RQI</sub> | 0.0                          | _                | 0.0                      |                  | ns             |  |  |  |

- 1.  $V_{CORE\ VDD}$  = 1.00± 0.05 V;  $T_{J}$  = -40° C to 100° C,  $C_{L}$  = 50 pF

- 2. Pull-up resistor: R  $_P$  (min) = 1.5  $k\Omega$

- 3. Capacitive load: C b (max) = 50 pF

- 5. All times assume noise free inputs

- 5. All times assume internal clock frequency of 200 MHz

- 6. SHI\_1 specs match those of SHI

- 7. The numbers listed are based on the module/pad design and its characteristics during output. The module is compliant with I<sup>2</sup>C standard, so the module should receive I<sup>2</sup>C bus compliant signal without any issue.

# 1.2.3 Programming the SHI I<sup>2</sup>C Serial Clock

The programmed serial clock cycle,  $T_{1^{2}CCP}$ , is specified by the value of the HDM[7:0] and HRS bits of the HCKR (SHI clock control register).

The expression for T<sub>I<sup>2</sup>CCP</sub> is

$$T_{1^{2}CCP} = [T_{C} \times 2 \times (HDM[7:0] + 1) \times (7 \times (1 - HRS) + 1)]$$

Eqn. 4

where

- HRS is the prescaler rate select bit. When HRS is cleared, the fixed divide-by-eight prescaler is operational. When HRS is set, the prescaler is bypassed.

- HDM[7:0] are the divider modulus select bits. A divide ratio from 1 to 256 (HDM[7:0] = \$00 to \$FF) may be selected.

In I<sup>2</sup>C mode, the user may select a value for the programmed serial clock cycle from

$$6 \times T_{C}$$

(if HDM[7:0] = \$02 and HRS = 1)

to

$$4096 \times T_{C}$$

(if HDM[7:0] = \$FF and HRS = 0) Eqn. 6

The programmed serial clock cycle  $(T_{I^2CCP})$  should be chosen in order to achieve the desired SCL serial clock cycle  $(T_{SCL})$ , as shown in next.

$$T_{1}^{2}CCP + 3 \times T_{C} + 45ns + T_{R}$$

(Nominal, SCL Serial Clock Cycle (TSCL) generated as master) Eqn. 7

Symphony<sup>™</sup> DSP56724/ DSP56725 Multi-Core Audio Processors, Rev. 2

Figure 16 shows the I<sup>2</sup>C timing diagram.

Figure 16. I<sup>2</sup>C Timing

# 1.2.4 Enhanced Serial Audio Interface Timing

Table 11 lists the enhanced serial audio interface timing.

**Table 11. Enhanced Serial Audio Interface Timing**

| No. | Characteristics <sup>1, 2, 3</sup>                 | Symbol | Expression <sup>3</sup>                                                         | Min          | Max         | Condition <sup>4</sup> | Unit |

|-----|----------------------------------------------------|--------|---------------------------------------------------------------------------------|--------------|-------------|------------------------|------|

| 62  | Clock cycle <sup>5</sup>                           | tssicc | $\begin{array}{c} 4\times T_{\mathbf{C}} \\ 4\times T_{\mathbf{C}} \end{array}$ | 20.0<br>20.0 |             | i ck<br>i ck           | ns   |

| 63  | Clock high period • For internal clock             |        | 2×T <sub>C</sub>                                                                | 10           | -           | _                      | ns   |

|     | For external clock                                 | _      | $2 \times T_{c}$                                                                | 10           | _           | _                      |      |

| 64  | Clock low period  • For internal clock             | _      | 2×T <sub>C</sub>                                                                | 10           | _           | _                      | ns   |

|     | For external clock                                 | _      | $2 \times T_{c}$                                                                | 10           | _           | _                      |      |

| 65  | SCKR rising edge to FSR out (bl) high              | _      | _                                                                               | _            | 17.0<br>7.0 | x ck<br>i ck a         | ns   |

| 66  | SCKR rising edge to FSR out (bl) low               | _      | _                                                                               | _            | 17.0<br>7.0 | x ck<br>i ck a         | ns   |

| 67  | SCKR rising edge to FSR out (wr) high <sup>6</sup> | _      | _                                                                               | _            | 19.0<br>9.0 | x ck<br>i ck a         | ns   |

| 68  | SCKR rising edge to FSR out (wr) low <sup>6</sup>  | _      | _                                                                               | _            | 19.0<br>9.0 | x ck<br>i ck a         | ns   |

| 69  | SCKR rising edge to FSR out (wl) high              | _      | _                                                                               | _            | 16.0<br>6.0 | x ck<br>i ck a         | ns   |

| 70  | SCKR rising edge to FSR out (wl) low               | _      | _                                                                               | _            | 17.0<br>7.0 | x ck<br>i ck a         | ns   |

**Table 11. Enhanced Serial Audio Interface Timing (Continued)**

| No. | Characteristics <sup>1, 2, 3</sup>                                       | Symbol | Expression <sup>3</sup> | Min         | Max          | Condition <sup>4</sup> | Unit |

|-----|--------------------------------------------------------------------------|--------|-------------------------|-------------|--------------|------------------------|------|

| 71  | Data in setup time before SCKR (SCK in synchronous mode) falling edge    | _      | _                       | 0.0<br>19.0 | _            | x ck<br>i ck           | ns   |

| 72  | Data in hold time after SCKR falling edge                                | _      | _                       | 3.5<br>9.0  | _            | x ck<br>i ck           | ns   |

| 73  | FSR input (bl, wr) high before SCKR falling edge <sup>6</sup>            | _      | _                       | 2.0<br>12.0 | _            | x ck<br>i ck a         | ns   |

| 74  | FSR input (wl) high before SCKR falling edge                             | _      | _                       | 2.0<br>12.0 | _            | x ck<br>i ck a         | ns   |

| 75  | FSR input hold time after SCKR falling edge                              | _      | _                       | 2.5<br>8.5  | _            | x ck<br>i ck a         | ns   |

| 76  | Flags input setup before SCKR falling edge                               | _      | _                       | 0.0<br>19.0 | _            | x ck<br>i ck s         | ns   |

| 77  | Flags input hold time after SCKR falling edge                            | _      | _                       | 6.0<br>0.0  | _            | x ck<br>i ck s         | ns   |

| 78  | SCKT rising edge to FST out (bl) high                                    | _      | _                       | _           | 18.0<br>8.0  | x ck<br>i ck           | ns   |

| 79  | SCKT rising edge to FST out (bl) low                                     | _      | _                       | _           | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 80  | SCKT rising edge to FST out (wr) high <sup>6</sup>                       | _      | _                       | _           | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 81  | SCKT rising edge to FST out (wr) low <sup>6</sup>                        | _      | _                       | _           | 22.0<br>12.0 | x ck<br>i ck           | ns   |

| 82  | SCKT rising edge to FST out (wl) high                                    | _      | _                       | _           | 15.0<br>9.0  | x ck<br>i ck           | ns   |

| 83  | SCKT rising edge to FST out (wl) low                                     | _      | _                       | _           | 15.0<br>10.0 | x ck<br>i ck           | ns   |

| 84  | SCKT rising edge to data out enable from high impedance                  | _      | _                       | _           | 22.0<br>17.0 | x ck<br>i ck           | ns   |

| 85  | SCKT rising edge to transmitter #0 drive enable assertion                | _      | _                       | _           | 17.0<br>11.0 | x ck<br>i ck           | ns   |

| 86  | SCKT rising edge to data out valid                                       | _      | _                       | _           | 25.0<br>13.0 | x ck<br>i ck           | ns   |

| 87  | SCKT rising edge to data out high impedance <sup>7</sup>                 | _      | _                       | _           | 25.0<br>16.0 | x ck<br>i ck           | ns   |

| 88  | SCKT rising edge to transmitter #0 drive enable deassertion <sup>7</sup> | _      | _                       | _           | 14.0<br>9.0  | x ck<br>i ck           | ns   |

| 89  | FST input (bl, wr) setup time before SCKT falling edge <sup>6</sup>      | _      | _                       | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |

| 90  | FST input (wl) setup time before SCKT falling edge                       | _      | _                       | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |

| 91  | FST input hold time after SCKT falling edge                              | _      | _                       | 4.0<br>5.0  | _<br>_       | x ck<br>i ck           | ns   |