# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# dsPIC33FJXXXMCX06/X08/X10 Data Sheet

## High-Performance,

16-Bit Digital Signal Controllers

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, nanoWatt XLP, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## High-Performance, 16-Bit Digital Signal Controllers

### **Operating Range:**

- Up to 40 MIPS operation (at 3.0-3.6V):

- Industrial temperature range (-40°C to +85°C)

#### **High-Performance DSC CPU:**

- · Modified Harvard architecture

- C compiler optimized instruction set

- · 16-bit wide data path

- 24-bit wide instructions

- Linear program memory addressing up to 4M instruction words

- · Linear data memory addressing up to 64 Kbytes

- 83 base instructions: mostly 1 word/1 cycle

- Two 40-bit accumulators:

- With rounding and saturation options

- · Flexible and powerful addressing modes:

- Indirect, Modulo and Bit-Reversed

- Software stack

- 16 x 16 fractional/integer multiply operations

- · 32/16 and 16/16 divide operations

- · Single-cycle multiply and accumulate:

- Accumulator write back for DSP operations

- Dual data fetch

- Up to ±16-bit shifts for up to 40-bit data

### **Direct Memory Access (DMA):**

- 8-channel hardware DMA

- 2 Kbytes dual ported DMA buffer area (DMA RAM) to store data transferred via DMA:

- Allows data transfer between RAM and a peripheral while CPU is executing code (no cycle stealing)

- Most peripherals support DMA

#### **Interrupt Controller:**

- 5-cycle latency

- · Up to 67 available interrupt sources

- · Up to five external interrupts

- · Seven programmable priority levels

- · Five processor exceptions

### **Digital I/O:**

- · Up to 85 programmable digital I/O pins

- · Wake-up/Interrupt-on-Change on up to 24 pins

- · Output pins can drive from 3.0V to 3.6V

- All digital input pins are 5V tolerant

- 4 mA sink on all I/O pins

### **On-Chip Flash and SRAM:**

- · Flash program memory, up to 256 Kbytes

- Data SRAM, up to 30 Kbytes (includes 2 Kbytes of DMA RAM)

### System Management:

- Flexible clock options:

- External, crystal, resonator, internal RC

- Fully integrated PLL

- Extremely low jitter PLL

- Power-up Timer

- Oscillator Start-up Timer/Stabilizer

- · Watchdog Timer with its own RC oscillator

- · Fail-Safe Clock Monitor

- · Reset by multiple sources

#### **Power Management:**

- · On-chip 2.5V voltage regulator

- · Switch between clock sources in real time

- · Idle, Sleep and Doze modes with fast wake-up

#### Timers/Capture/Compare/PWM:

- Timer/Counters, up to nine 16-bit timers:

- Can pair up to make four 32-bit timers

- 1 timer runs as Real-Time Clock with external 32.768 kHz oscillator

- Programmable prescaler

- Input Capture (up to eight channels):

- Capture on up, down or both edges

- 16-bit capture input functions

- 4-deep FIFO on each capture

- Output Compare (up to eight channels):

- Single or Dual 16-Bit Compare mode

- 16-bit Glitchless PWM mode

## **Communication Modules:**

- 3-wire SPI (up to two modules):

- Framing supports I/O interface to simple codecs

- Supports 8-bit and 16-bit data

- Supports all serial clock formats and sampling modes

- I<sup>2</sup>C<sup>™</sup> (up to two modules):

- Full Multi-Master Slave mode support

- 7-bit and 10-bit addressing

- Bus collision detection and arbitration

- Integrated signal conditioning

- Slave address masking

- UART (up to two modules):

- Interrupt on address bit detect

- Interrupt on UART error

- Wake-up on Start bit from Sleep mode

- 4-character TX and RX FIFO buffers

- LIN bus support

- IrDA® encoding and decoding in hardware

- High-Speed Baud mode

- Hardware Flow Control with CTS and RTS

- Enhanced CAN™ (ECAN™ module) 2.0B active (up to 2 modules):

- Up to eight transmit and up to 32 receive buffers

- 16 receive filters and three masks

- Loopback, Listen Only and Listen All Messages modes for diagnostics and bus monitoring

- Wake-up on CAN message

- Automatic processing of Remote Transmission Requests

- FIFO mode using DMA

- DeviceNet<sup>™</sup> addressing support

### **Motor Control Peripherals:**

- Motor Control PWM (up to eight channels):

- Four duty cycle generators

- Independent or Complementary mode

- Programmable dead time and output polarity

- Edge or center-aligned

- Manual output override control

- Up to two Fault inputs

- Trigger for ADC conversions

- PWM frequency for 16-bit resolution

(@ 40 MIPS) = 1220 Hz for Edge-Aligned mode, 610 Hz for Center-Aligned mode

- PWM frequency for 11-bit resolution

(@ 40 MIPS) = 39.1 kHz for Edge-Aligned mode, 19.55 kHz for Center-Aligned mode

- Quadrature Encoder Interface module:

- Phase A, Phase B and index pulse input

- 16-bit up/down position counter

- Count direction status

- Position Measurement (x2 and x4) mode

- Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- Interrupt on position counter rollover/underflow

## Analog-to-Digital Converters (ADCs):

- · Up to two ADC modules in a device

- 10-bit, 1.1 Msps or 12-bit, 500 ksps conversion:

- Two, four or eight simultaneous samples

- Up to 32 input channels with auto-scanning

- Conversion start can be manual or synchronized with one of four trigger sources

- Conversion possible in Sleep mode

- ±1 LSb max integral nonlinearity

- ±1 LSb max differential nonlinearity

### **CMOS Flash Technology:**

- · Low-power, high-speed Flash technology

- Fully static design

- 3.3V (±10%) operating voltage

- Industrial temperature

- Low-power consumption

### Packaging:

- 100-pin TQFP (14x14x1 mm and 12x12x1 mm)

- 80-pin TQFP (12x12x1 mm)

- 64-pin TQFP (10x10x1 mm)

**Note:** See the device variant tables for exact peripheral features per device.

## dsPIC33F PRODUCT FAMILIES

The dsPIC33FJXXXMCX06/X08/X10 family of devices supports a variety of motor control applications, such as brushless DC motors, single and 3-phase induction motors and switched reluctance motors. The dsPIC33F Motor Control products are also well-suited for Uninterrupted Power Supply (UPS), inverters, switched mode power supplies, power factor correction and also for controlling the power management module in servers, telecommunication equipment and other industrial equipment.

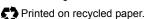

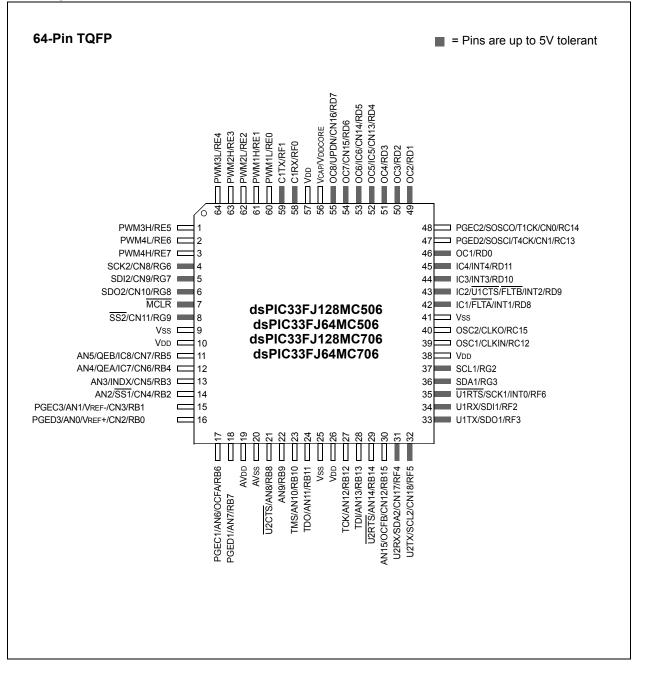

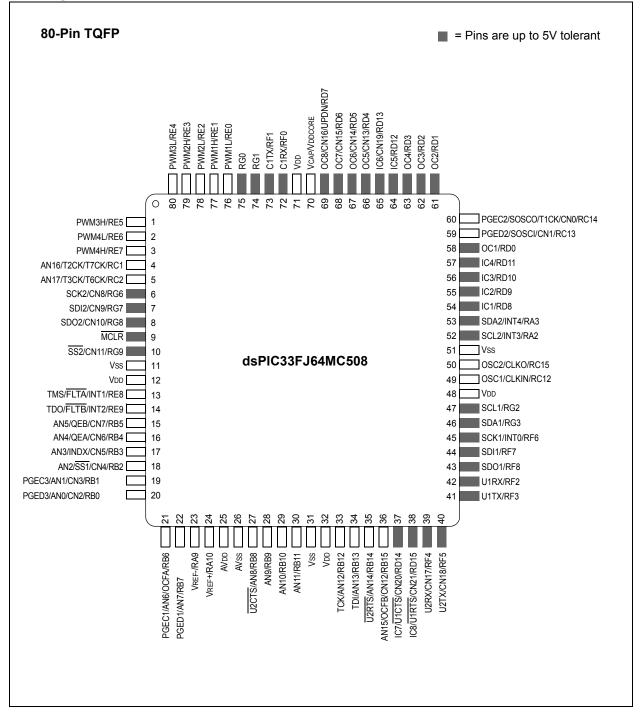

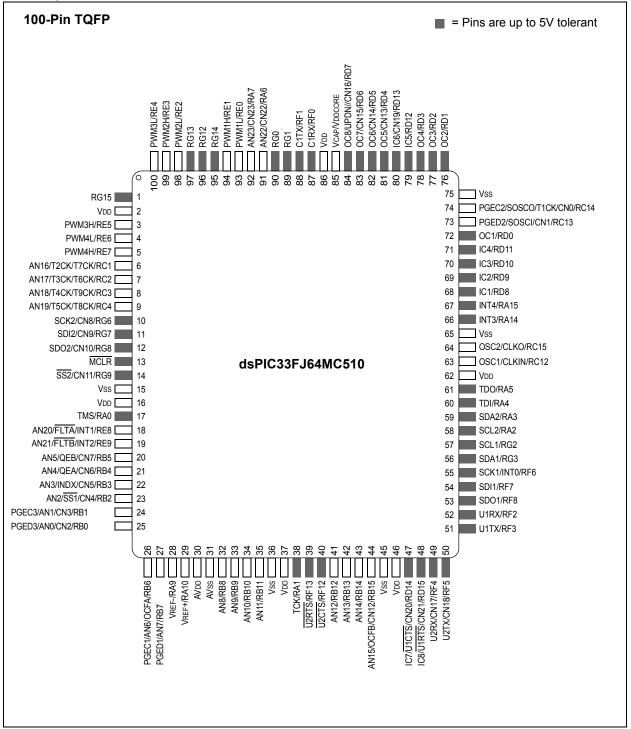

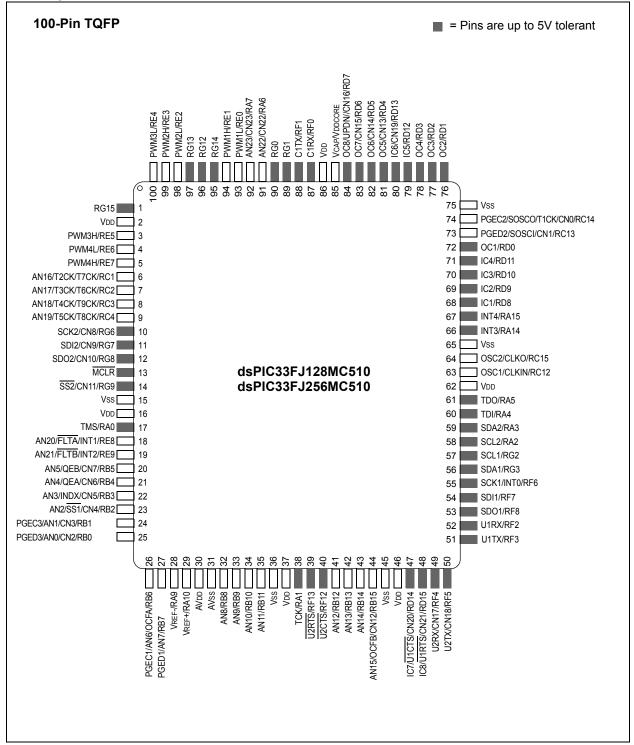

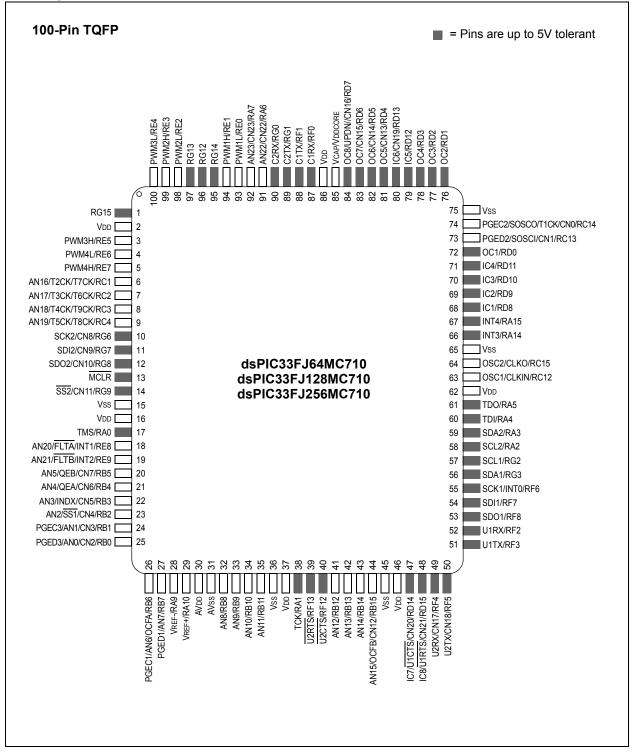

The device names, pin counts, memory sizes and peripheral availability of each device are listed below. The following pages show their pinout diagrams.

## dsPIC33FJXXXMCX06/X08/X10 Controller Families

| Device            | Pins | Program<br>Flash<br>Memory<br>(Kbyte) | RAM<br>(Kbyte) <sup>(1)</sup> | Timer 16-bit | Input Capture | Output Compare<br>Std. PWM | Motor Control PWM | Quadrature Encoder<br>Interface | Codec Interface | ADC             | UART | SPI | I²C™ | Enhanced CAN <sup>TM</sup> | I/O Pins (Max) <sup>(2)</sup> | Packages |

|-------------------|------|---------------------------------------|-------------------------------|--------------|---------------|----------------------------|-------------------|---------------------------------|-----------------|-----------------|------|-----|------|----------------------------|-------------------------------|----------|

| dsPIC33FJ64MC506  | 64   | 64                                    | 8                             | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 1 ADC,<br>16 ch | 2    | 2   | 2    | 1                          | 53                            | PT       |

| dsPIC33FJ64MC508  | 80   | 64                                    | 8                             | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 1 ADC,<br>18 ch | 2    | 2   | 2    | 1                          | 69                            | PT       |

| dsPIC33FJ64MC510  | 100  | 64                                    | 8                             | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 1 ADC,<br>24 ch | 2    | 2   | 2    | 1                          | 85                            | PF, PT   |

| dsPIC33FJ64MC706  | 64   | 64                                    | 16                            | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 2 ADC,<br>16 ch | 2    | 2   | 2    | 1                          | 53                            | PT       |

| dsPIC33FJ64MC710  | 100  | 64                                    | 16                            | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 2 ADC,<br>24 ch | 2    | 2   | 2    | 2                          | 85                            | PF, PT   |

| dsPIC33FJ128MC506 | 64   | 128                                   | 8                             | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 1 ADC,<br>16 ch | 2    | 2   | 2    | 1                          | 53                            | PT       |

| dsPIC33FJ128MC510 | 100  | 128                                   | 8                             | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 1 ADC,<br>24 ch | 2    | 2   | 2    | 1                          | 85                            | PF, PT   |

| dsPIC33FJ128MC706 | 64   | 128                                   | 16                            | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 2 ADC,<br>16 ch | 2    | 2   | 2    | 1                          | 53                            | PT       |

| dsPIC33FJ128MC708 | 80   | 128                                   | 16                            | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 2 ADC,<br>18 ch | 2    | 2   | 2    | 2                          | 69                            | PT       |

| dsPIC33FJ128MC710 | 100  | 128                                   | 16                            | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 2 ADC,<br>24 ch | 2    | 2   | 2    | 2                          | 85                            | PF, PT   |

| dsPIC33FJ256MC510 | 100  | 256                                   | 16                            | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 1 ADC,<br>24 ch | 2    | 2   | 2    | 1                          | 85                            | PF, PT   |

| dsPIC33FJ256MC710 | 100  | 256                                   | 30                            | 9            | 8             | 8                          | 8 ch              | 1                               | 0               | 2 ADC,<br>24 ch | 2    | 2   | 2    | 2                          | 85                            | PF, PT   |

Note 1: RAM size is inclusive of 2 Kbytes DMA RAM.

2: Maximum I/O pin count includes pins shared by the peripheral functions.

### **Pin Diagrams**

## **Table of Contents**

| dsPIC | C33F Product Families                                                 |     |

|-------|-----------------------------------------------------------------------|-----|

| 1.0   | Device Overview                                                       |     |

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers |     |

|       | CPU                                                                   |     |

|       | Memory Organization                                                   |     |

|       | Flash Program Memory                                                  |     |

|       | Reset                                                                 |     |

| 7.0   | Interrupt Controller                                                  | 85  |

| 8.0   | Direct Memory Access (DMA)                                            | 133 |

| 9.0   | Oscillator Configuration                                              | 143 |

| 10.0  | Power-Saving Features                                                 | 153 |

|       | I/O Ports                                                             |     |

| 12.0  | Timer1                                                                | 163 |

| 13.0  | Timer2/3, Timer4/5, Timer6/7 and Timer8/9                             | 165 |

| 14.0  | Input Capture                                                         | 171 |

| 15.0  | Output Compare                                                        | 173 |

| 16.0  | Motor Control PWM Module                                              | 177 |

| 17.0  | Quadrature Encoder Interface (QEI) Module                             | 191 |

|       | Serial Peripheral Interface (SPI)                                     |     |

|       | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                         |     |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                    | 209 |

| 21.0  | Enhanced CAN (ECAN™) Module                                           | 215 |

|       | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                       |     |

| 23.0  | Special Features                                                      | 253 |

| 24.0  | Instruction Set Summary                                               |     |

| 25.0  | Development Support                                                   |     |

| 26.0  | Electrical Characteristics                                            | 273 |

| 27.0  | Packaging Information                                                 | 315 |

| Apper | ndix A: Revision History                                              | 325 |

| Index | · · · · · · · · · · · · · · · · · · ·                                 | 331 |

| The N | /icrochip Web Site                                                    | 335 |

| Custo | omer Change Notification Service                                      | 335 |

| Custo | omer Support                                                          | 335 |

| Read  | er Response                                                           | 336 |

| Produ | uct Identification System                                             | 337 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

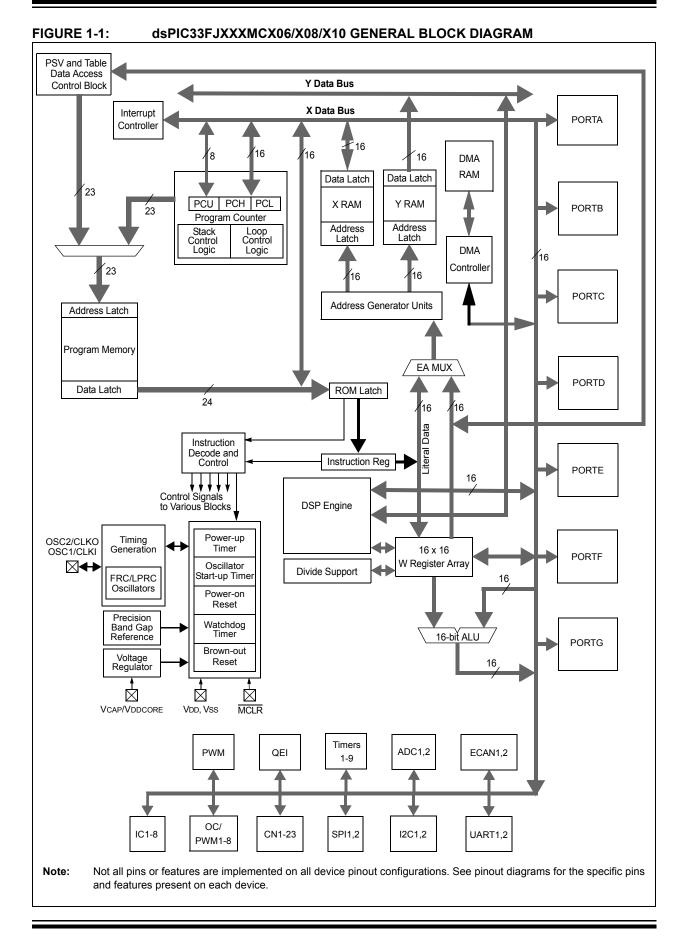

## 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJXXXMCX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

This document contains device specific information for the following devices:

- dsPIC33FJ64MC506

- dsPIC33FJ64MC508

- dsPIC33FJ64MC510

- dsPIC33FJ64MC706

- dsPIC33FJ64MC710

- dsPIC33FJ128MC506

- dsPIC33FJ128MC510

- dsPIC33FJ128MC706

- dsPIC33FJ128MC708

- dsPIC33FJ128MC710

- dsPIC33FJ256MC510

- dsPIC33FJ256MC710

The dsPIC33FJXXXMCX06/X08/X10 includes devices with a wide range of pin counts (64, 80 and 100), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes, 16 Kbytes and 30 Kbytes).

These features make this family suitable for a wide variety of high-performance digital signal control applications. The devices are pin compatible with the PIC24H family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

The dsPIC33FJXXXMCX06/X08/X10 family of devices employ a powerful 16-bit architecture that seamlessly integrates the control features of a Microcontroller (MCU) with the computational capabilities of a Digital Signal Processor (DSP). The resulting functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

The DSP engine, dual 40-bit accumulators, hardware support for division operations, barrel shifter, 17 x 17 multiplier, a large array of 16-bit working registers and a wide variety of data addressing modes, together, provide the dsPIC33FJXXXMCX06/X08/X10 Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the dsPIC33FJXXXMCX06/X08/X10 devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use dsPIC33FJXXXMCX06/X08/X10 devices.

| Pin Name Pin Buff<br>Type Typ |          |              | Description                                                                                                                                                                                                                                                       |  |  |  |  |

|-------------------------------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AN0-AN31                      | I        | Analog       | Analog input channels.                                                                                                                                                                                                                                            |  |  |  |  |

| AVDD                          | Р        | Р            | Positive supply for analog modules. This pin must be connected at all times.                                                                                                                                                                                      |  |  |  |  |

| AVss                          | Р        | Р            | Ground reference for analog modules.                                                                                                                                                                                                                              |  |  |  |  |

| CLKI                          |          |              |                                                                                                                                                                                                                                                                   |  |  |  |  |

| CLKO                          | 1<br>0   |              | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associate<br>with OSC2 pin function. |  |  |  |  |

| CN0-CN23                      | I        | ST           | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                         |  |  |  |  |

| C1RX                          | 1        | ST           | ECAN1 bus receive pin.                                                                                                                                                                                                                                            |  |  |  |  |

| C1TX                          | 0        |              | ECAN1 bus transmit pin.                                                                                                                                                                                                                                           |  |  |  |  |

| C2RX                          | 1        | ST           | ECAN2 bus receive pin.                                                                                                                                                                                                                                            |  |  |  |  |

| C2TX                          | 0        |              | ECAN2 bus transmit pin.                                                                                                                                                                                                                                           |  |  |  |  |

| PGED1                         | I/O      | ST           | Data I/O pin for programming/debugging communication channel 1.                                                                                                                                                                                                   |  |  |  |  |

| PGEC1                         | 1        | ST           | Clock input pin for programming/debugging communication channel 1.                                                                                                                                                                                                |  |  |  |  |

| PGED2                         | I/O      | ST           | Data I/O pin for programming/debugging communication channel 2.                                                                                                                                                                                                   |  |  |  |  |

| PGEC2                         | 1        | ST           | Clock input pin for programming/debugging communication channel 2.                                                                                                                                                                                                |  |  |  |  |

| PGED3                         | I/O      | ST           | Data I/O pin for programming/debugging communication channel 3.                                                                                                                                                                                                   |  |  |  |  |

| PGEC3                         | 1        | ST           | Clock input pin for programming/debugging communication channel 3.                                                                                                                                                                                                |  |  |  |  |

| IC1-IC8                       |          | ST           | Capture inputs 1 through 8.                                                                                                                                                                                                                                       |  |  |  |  |

| INDX                          |          | ST           | Quadrature Encoder Index Pulse input.                                                                                                                                                                                                                             |  |  |  |  |

| QEA                           |          | ST           |                                                                                                                                                                                                                                                                   |  |  |  |  |

| QEA                           | I        | 51           | Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External                                                                                                                                                                                            |  |  |  |  |

|                               |          | OT           | Clock/Gate input in Timer mode.                                                                                                                                                                                                                                   |  |  |  |  |

| QEB                           |          | ST           | Quadrature Encoder Phase A input in QEI mode. Auxiliary Timer External                                                                                                                                                                                            |  |  |  |  |

| UPDN                          | 0        | CMOS         | Clock/Gate input in Timer mode.<br>Position Up/Down Counter Direction State.                                                                                                                                                                                      |  |  |  |  |

|                               |          |              |                                                                                                                                                                                                                                                                   |  |  |  |  |

| INT0                          |          | ST           | External interrupt 0.                                                                                                                                                                                                                                             |  |  |  |  |

| INT1                          |          | ST           | External interrupt 1.                                                                                                                                                                                                                                             |  |  |  |  |

| INT2                          |          | ST           | External interrupt 2.                                                                                                                                                                                                                                             |  |  |  |  |

| INT3                          |          | ST           | External interrupt 3.                                                                                                                                                                                                                                             |  |  |  |  |

| INT4                          | 1        | ST           | External interrupt 4.                                                                                                                                                                                                                                             |  |  |  |  |

| FLTA                          |          | ST           | PWM Fault A input.                                                                                                                                                                                                                                                |  |  |  |  |

| FLTB                          |          | ST           | PWM Fault B input.                                                                                                                                                                                                                                                |  |  |  |  |

| PWM1L                         | 0        | —            | PWM 1 low output.                                                                                                                                                                                                                                                 |  |  |  |  |

| PWM1H                         | 0        | —            | PWM 1 high output.                                                                                                                                                                                                                                                |  |  |  |  |

| PWM2L                         | 0        | -            | PWM 2 low output.                                                                                                                                                                                                                                                 |  |  |  |  |

| PWM2H                         | 0        | -            | PWM 2 high output.                                                                                                                                                                                                                                                |  |  |  |  |

| PWM3L                         | 0        | -            | PWM 3 low output.                                                                                                                                                                                                                                                 |  |  |  |  |

| PWM3H                         | 0        | -            | PWM 3 high output.                                                                                                                                                                                                                                                |  |  |  |  |

| PWM4L                         | 0        | -            | PWM 4 low output.                                                                                                                                                                                                                                                 |  |  |  |  |

| PWM4H                         | 0        | -            | PWM 4 high output.                                                                                                                                                                                                                                                |  |  |  |  |

| MCLR                          | I/P      | ST           | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                        |  |  |  |  |

| OCFA                          | I        | ST           | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).                                                                                                                                                                                                       |  |  |  |  |

| OCFB                          | I        | ST           | Compare Fault B input (for Compare Channels 5, 6, 7 and 8).                                                                                                                                                                                                       |  |  |  |  |

| 0C1-0C8                       | 0        | <u> </u>     | Compare outputs 1 through 8.                                                                                                                                                                                                                                      |  |  |  |  |

| OSC1                          | I        | ST/CMOS      | Oscillator crystal input. ST buffer when configured in RC mode;<br>CMOS otherwise.                                                                                                                                                                                |  |  |  |  |

| OSC2                          | I/O      | _            | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                          |  |  |  |  |

|                               |          |              |                                                                                                                                                                                                                                                                   |  |  |  |  |

| Legend: CMC                   | DS = CMO | S compatible | e input or output Analog = Analog input P = Power                                                                                                                                                                                                                 |  |  |  |  |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

© 2009 Microchip Technology Inc.

|                                                                                                                                                                                            |                                                                                           |                                                                                            | CRIPTIONS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name Pin Buffer<br>Type Type                                                                                                                                                           |                                                                                           |                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| RA0-RA7                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                         | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RA9-RA10                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| RA12-RA15                                                                                                                                                                                  | I/O                                                                                       | ST                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| RB0-RB15                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                         | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RC1-RC4                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                         | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RC12-RC15                                                                                                                                                                                  | I/O                                                                                       | ST                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| RD0-RD15                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                         | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RE0-RE9                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                         | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RF0-RF8                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                         | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RF12-RF13                                                                                                                                                                                  |                                                                                           |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| RG0-RG3                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                         | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| RG6-RG9                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| RG12-RG15                                                                                                                                                                                  | I/O                                                                                       | ST                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| SCK1                                                                                                                                                                                       | I/O                                                                                       | ST                                                                                         | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| SDI1                                                                                                                                                                                       | 1                                                                                         | ST                                                                                         | SPI1 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| SDO1                                                                                                                                                                                       | Ō                                                                                         | _                                                                                          | SPI1 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SS1                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                         | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SCK2                                                                                                                                                                                       | I/O                                                                                       | ST                                                                                         | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| SDI2                                                                                                                                                                                       | I                                                                                         | ST                                                                                         | SPI2 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| SDO2                                                                                                                                                                                       | 0                                                                                         | —                                                                                          | SPI2 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SS2                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                         | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SCL1                                                                                                                                                                                       | I/O                                                                                       | ST                                                                                         | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| SDA1                                                                                                                                                                                       | I/O                                                                                       | ST                                                                                         | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SCL2                                                                                                                                                                                       | I/O                                                                                       | ST                                                                                         | Synchronous serial clock input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| SDA2                                                                                                                                                                                       | I/O                                                                                       | ST                                                                                         | Synchronous serial data input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SOSCI                                                                                                                                                                                      | I                                                                                         | ST/CMOS                                                                                    | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                                                                                                                                                                            |                                                                                           |                                                                                            | 22 769 kHz low nower excilletor enveted output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| SOSCO                                                                                                                                                                                      | 0                                                                                         | -                                                                                          | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                                                                                                                                                                                            | 0<br>                                                                                     | ST                                                                                         | JTAG Test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| TMS                                                                                                                                                                                        |                                                                                           | ST<br>ST                                                                                   | JTAG Test mode select pin.<br>JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| TMS<br>TCK<br>TDI                                                                                                                                                                          | <br> <br>                                                                                 |                                                                                            | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| SOSCO<br>TMS<br>TCK<br>TDI<br>TDO                                                                                                                                                          |                                                                                           | ST                                                                                         | JTAG Test mode select pin.<br>JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| TMS<br>TCK<br>TDI<br>TDO<br>T1CK                                                                                                                                                           | <br> <br>                                                                                 | ST<br>ST<br>                                                                               | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.<br>Timer1 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| TMS<br>TCK<br>TDI<br>TDO<br>T1CK<br>T2CK                                                                                                                                                   | <br> <br> <br>0                                                                           | ST<br>ST<br>—<br>ST<br>ST                                                                  | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| TMS<br>TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK                                                                                                                                           | <br> <br> <br>0                                                                           | ST<br>ST<br>—<br>ST<br>ST<br>ST                                                            | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| TMS<br>TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK                                                                                                                                   | <br> <br> <br>0                                                                           | ST<br>ST<br>ST<br>ST<br>ST<br>ST                                                           | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.<br>JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

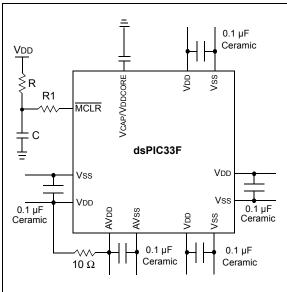

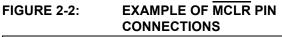

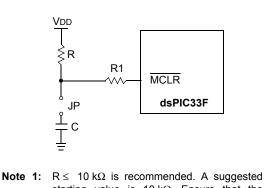

| TMS<br>TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK                                                                                                                           | <br> <br> <br>0                                                                           | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                                     | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                                                                                                                                                                                             |  |  |  |  |  |