Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### GS2989 Dual-Slew-Rate, Dual-Output Cable Driver with 3Gb/s Capability

### **Features**

- SMPTE 424M, SMPTE 292M and SMPTE 259M compliant

- Supports DVB-ASI at 270Mb/s

- Supports data rates from 270Mb/s to 2.97Gb/s

- Wide common-mode range input buffer

- 100mV sensitivity

- supports DC-coupling to industry-standard differential logic

- on-chip  $100\Omega$  differential data input termination

- Input signal trace equalization

- Dual differential coaxial-cable-driving outputs

- selectable slew rates

- adjustable output swing from 500mVpp to 1800mVpp

- independent DISABLE controls for each output

- Robust output signal presence function

- Excellent output eye quality

- Power supply operation at 3.3V or 2.5V

- 110mW power consumption (2.5V supply)

- Operating temperature range: -40°C to +85°C

- Small footprint QFN package (4mm x 4mm)

- new dual-output pin out

- use the GS2988 for a single-output variant that is drop-in compatible to the GS2978

- Pb-free and RoHS compliant

### **Applications**

SMPTE 424M, SMPTE 292M and SMPTE 259M coaxial cable serial digital interfaces

### **Description**

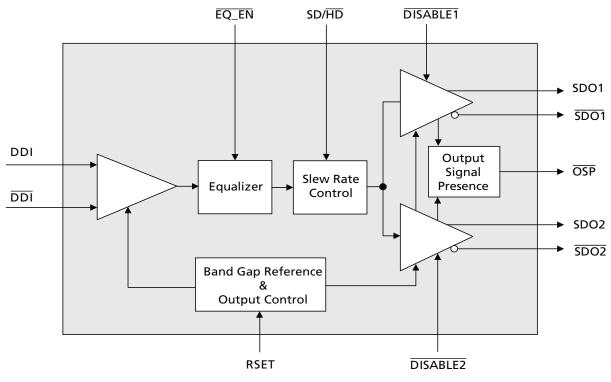

The GS2989 is a high-speed BiCMOS integrated circuit designed to drive one to four 75 $\Omega$  coaxial cables.

The GS2989 may drive data rates up to 2.97Gb/s and provides two selectable slew rates in order to achieve compliance to SMPTE 424M, SMPTE 292M and SMPTE 259M.

The GS2989 accepts industry-standard differential input levels including LVPECL and CML.

Input trace equalization compensates for up to 10 inches of FR4 trace loss while in HD and 3G modes. This feature can be disabled using the  $\overline{EQ}$ \_EN pin.

The DISABLE1 and DISABLE2 pins power-down the first and second output drivers respectively, leaving the serial data outputs in a high-impedance state. When applied simultaneously, the entire device is powered-down.

The GS2989 features adjustable output swing using an external bias resistor. The single-ended output swing is adjustable from 500mVpp to 1800mVpp.

An output signal presence function, the  $\overline{\text{OSP}}$  pin, indicates whether an active signal is present at the output of the GS2989.

The GS2989 can be powered from either a 3.3V or a 2.5V supply. Power consumption is typically 110mW using a 2.5V power supply with one output enabled.

The GS2989 is Pb-free, and the encapsulation compound does not contain halogenated flame retardant.

This component and all homogeneous subcomponents are RoHS compliant.

**Functional Block Diagram**

## **Revision History**

| Version | ECR    | PCN | Date          | Changes and/or Modifications                                                                             |

|---------|--------|-----|---------------|----------------------------------------------------------------------------------------------------------|

| 4       | 155552 | -   | December 2010 | Correction to Marking Diagram.                                                                           |

| 3       | 155359 | -   | November 2010 | Clarified the functionality of the EQ_EN pin in Table 1-1: Pin Descriptions and throughout the document. |

| 2       | 155070 | -   | October 2010  | Updated Typical Application Circuit.                                                                     |

| 1       | 153602 | -   | February 2010 | Converted to Data Sheet.                                                                                 |

| 0       | 152844 | -   | October 2009  | Converted to Preliminary Data Sheet. Updates throughout.                                                 |

| В       | 152691 | -   | October 2009  | Updates to Section 2. Electrical Characteristics. Corrections to Section 3. Input/Output Circuits.       |

| А       | 151623 | _   | April 2009    | New document.                                                                                            |

## Contents

| Features                                               | 1  |

|--------------------------------------------------------|----|

| Applications                                           | 1  |

| Description                                            | 1  |

| Revision History                                       | 2  |

| 1. Pin Out                                             | 4  |

| 1.1 Pin Assignment                                     | 4  |

| 1.2 Pin Descriptions                                   | 4  |

| 2. Electrical Characteristics                          | 6  |

| 2.1 Absolute Maximum Ratings                           | 6  |

| 2.2 DC Electrical Characteristics                      | 6  |

| 2.3 AC Electrical Characteristics                      | 7  |

| 3. Input/Output Circuits                               | 9  |

| 4. Detailed Description                                | 10 |

| 4.1 Serial Data Input                                  | 10 |

| 4.2 Input Trace-equalization                           | 10 |

| 4.3 Serial Data Output                                 | 10 |

| 4.3.1 Slew Rate Selection (Rise/Fall Time Requirement) | 10 |

| 4.4 Output Disable                                     | 11 |

| 4.5 Output Signal Presence Indicator (OSP)             |    |

| 4.6 Output Amplitude (RSET)                            | 12 |

| 4.7 Output Return Loss Measurement                     | 13 |

| 5. Application Information                             | 14 |

| 5.1 PCB Layout                                         | 14 |

| 5.2 Typical Application Circuit                        | 15 |

| 6. Package & Ordering Information                      | 16 |

| 6.1 Package Dimensions                                 | 16 |

| 6.2 Recommended PCB Footprint                          | 17 |

| 6.3 Packaging Data                                     | 17 |

| 6.4 Solder Reflow Profiles                             | 18 |

| 6.5 Marking Diagram                                    | 18 |

| 6.6 Ordering Information                               | 19 |

## 1. Pin Out

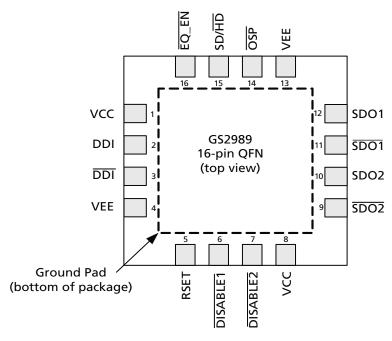

## 1.1 Pin Assignment

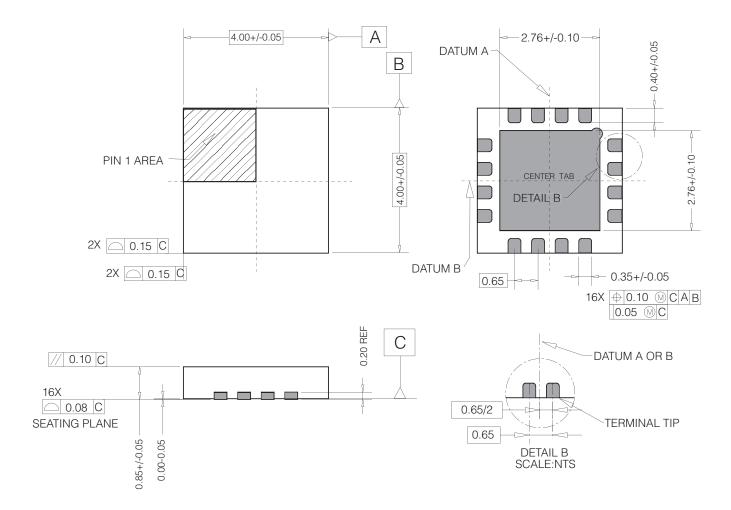

Figure 1-1: 16-Pin QFN

## **1.2 Pin Descriptions**

**Table 1-1: Pin Descriptions**

| Pin Number | Name     | Туре  | Description                                                                                                                                                                                                                                                                                           |

|------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 8       | VCC      | Power | Most positive power supply connection for the input buffer and core. Connect to 3.3V or 2.5V.                                                                                                                                                                                                         |

| 2, 3       | DDI, DDI | Input | Serial data differential input.                                                                                                                                                                                                                                                                       |

| 4, 13      | VEE      | Power | Most negative power supply connection for the input buffer and core.  Connect to GND.                                                                                                                                                                                                                 |

| 5          | RSET     | Input | External output amplitude control resistor connection.                                                                                                                                                                                                                                                |

| 6*         | DISABLE1 | Input | Control signal input.  When set LOW, the first serial data output is disabled (powered-down) and the SDO1/SDO1 pins are set to high-impedance. When set HIGH, the SDO1/SDO1 pins will output a serial data signal.  NOTE: if this pin is left floating, the first serial data output will be enabled. |

**Table 1-1: Pin Descriptions**

| Pin Number | Name          | Туре   | Description                                                                                                               |

|------------|---------------|--------|---------------------------------------------------------------------------------------------------------------------------|

| 7*         | DISABLE2      | Input  | Control signal input.                                                                                                     |

|            |               |        | When set LOW, the second serial data output is disabled (powered-down) and the SDO2/SDO2 pins are set to high-impedance.  |

|            |               |        | When set HIGH, the SDO2/SDO2 pins will output a serial data signal.                                                       |

|            |               |        | <b>NOTE:</b> if this pin is left floating, the second serial data output will be <b>disabled</b> .                        |

| 9,10       | SDO2/<br>SDO2 | Output | Serial data differential output of second output buffer.                                                                  |

| 11,12      | SDO1/<br>SDO1 | Output | Serial data differential output of first output buffer.                                                                   |

| 14         | OSP           | Output | Output signal presence status signal output.                                                                              |

|            |               |        | Signal levels are LVCMOS/LVTTL compatible.                                                                                |

|            |               |        | Indicates presence of a valid output signal.                                                                              |

|            |               |        | When the OSP pin is LOW, a good input signal has been detected within the output stage pre-driver.                        |

|            |               |        | When this pin is HIGH, the output signal is invalid at the output of the pre-driver.                                      |

| 15         | SD/HD         | Input  | Control signal input.                                                                                                     |

|            |               |        | When set HIGH, the serial data outputs will meet the SMPTE 259M rise/fall time specification.                             |

|            |               |        | When set LOW, the serial outputs will meet the SMPTE 292M and SMPTE 424M rise/fall time specification.                    |

|            |               |        | <b>NOTE:</b> if this pin is left floating, the serial data outputs will meet the SMPTE 259M rise/fall time specification. |

| 16         | EQ_EN         | Input  | Control signal input.                                                                                                     |

|            |               |        | When set LOW, trace-equalization is turned ON.                                                                            |

|            |               |        | When set HIGH, trace-equalization is turned OFF.                                                                          |

|            |               |        | NOTE 1: if this pin is left floating, trace-equalization is turned OFF.                                                   |

|            |               |        | NOTE 2: this pin must be pulled HIGH or left floating for operation in SD mode.                                           |

| -          | Center Pad    | Power  | Connect to most negative power supply plane following the recommendations in Recommended PCB Footprint on page 17.        |

<sup>\*</sup>NOTE: When pins 6 and 7 are driven LOW together (or similarly when pin 6 is driven LOW while pin 7 is left floating), the entire device is powered-down. In this state, minimum power consumption occurs.

## 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

| Parameter                       | Value                           |

|---------------------------------|---------------------------------|

| Supply Voltage                  | -0.5V to 3.6 V <sub>DC</sub>    |

| Input ESD Voltage               | 2.5kV                           |

| Storage Temperature Range       | -50°C < T <sub>s</sub> < 125°C  |

| Input Voltage Range (any input) | -0.3 to (V <sub>CC</sub> +0.3)V |

| Operating Temperature Range     | -40°C to +85°C                  |

| Solder Reflow Temperature       | 260°C                           |

**NOTE:** Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions or at any other condition beyond those indicated in the AC/DC Electrical Characteristic sections is not implied.

### 2.2 DC Electrical Characteristics

**Table 2-1: DC Electrical Characteristics**

$V_{CC}$  = 3.3V ±5% or 2.5V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                | Symbol          | Conditions                               | Min   | Тур | Max   | Units | Notes |

|--------------------------|-----------------|------------------------------------------|-------|-----|-------|-------|-------|

| Supply Voltage           | V <sub>CC</sub> | 3.3V Typical                             | 3.135 | 3.3 | 3.465 | V     | -     |

|                          |                 | 2.5V Typical                             | 2.375 | 2.5 | 2.625 | V     | -     |

| Power Consumption (2.5V) | $P_{D}$         | SDO1/SDO1 enabled,<br>SDO2/SDO2 disabled | -     | 110 | 130   | mW    | 1     |

|                          |                 | SDO1/SDO1 and<br>SDO2/SDO2 enabled       | -     | 180 | 215   | mW    | 1     |

|                          |                 | SDO1/SDO1 and<br>SDO2/SDO2 disabled      | -     | 3   | 5     | mW    | 1     |

| Power Consumption (3.3V) | _               | SDO1/SDO1 enabled,<br>SDO2/SDO2 disabled | -     | 155 | 183   | mW    | 1     |

|                          |                 | SDO1/SDO1 and<br>SDO2/SDO2 enabled       | -     | 250 | 300   | mW    | 1     |

|                          |                 | SDO1/SDO1 and<br>SDO2/SDO2 disabled      | -     | 4   | 6     | mW    | 1     |

**Table 2-1: DC Electrical Characteristics**

$V_{CC}$  = 3.3V ±5% or 2.5V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                      | Symbol             | Conditions               | Min                        | Тур                                  | Max                                    | Units | Notes |

|--------------------------------|--------------------|--------------------------|----------------------------|--------------------------------------|----------------------------------------|-------|-------|

| Supply Current                 | I <sub>S</sub>     | 1 channel, VCC = 3.3V    | -                          | 47                                   | 53                                     | mA    | 1     |

|                                |                    | 1 channel, VCC = 2.5V    | _                          | 44                                   | 50                                     | mA    | 1     |

|                                |                    | 2 channels, VCC = 3.3V   | _                          | 76                                   | 87                                     | mA    | 1     |

|                                |                    | 2 channels, VCC = 2.5V   | _                          | 72                                   | 82                                     | mA    | 1     |

|                                |                    | Power-down               | _                          | 1                                    | 1.8                                    | mA    | 1     |

| Output Voltage                 | V <sub>CMOUT</sub> | Common mode              | -                          | V <sub>TERM</sub> - V <sub>OUT</sub> | -                                      | V     | -     |

| Input Voltage                  | V <sub>CMIN</sub>  | Common mode              | 1.4 + ΔV <sub>DDI</sub> /2 | -                                    | V <sub>CC</sub> - ΔV <sub>DDI</sub> /2 | V     | -     |

| SD/HD, DISABLE,<br>EQ_EN Input | V <sub>IH</sub>    | I <sub>IH</sub> <= 150μA | 1.7                        | -                                    | -                                      | V     | -     |

| EQ_EN IIIput                   | V <sub>IL</sub>    | I <sub>IL</sub> <= 150μΑ | _                          | _                                    | 0.8                                    | V     | _     |

| OSP Drive Strength             | _                  | -                        | 2                          | _                                    | _                                      | mA    | -     |

### NOTES:

### 2.3 AC Electrical Characteristics

**Table 2-2: AC Electrical Characteristics**

$V_{CC}$  = 3.3V ±5% or 2.5V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                  | Symbol                            | Conditions         | Min | Тур | Max  | Units             | Notes |

|----------------------------|-----------------------------------|--------------------|-----|-----|------|-------------------|-------|

| Serial input data rate     | DR <sub>SDO</sub>                 | -                  | .27 | _   | 2.97 | Gb/s              | 1     |

| Additive jitter            | -                                 | 2.97Gb/s           | -   | 10  | _    | ps <sub>p-p</sub> | 2     |

|                            | _                                 | 1.485Gb/s          | -   | 10  | _    | ps <sub>p-p</sub> | 2     |

|                            | _                                 | 270Mb/s            | _   | 30  | _    | ps <sub>p-p</sub> | 2     |

| Rise/Fall time             | t <sub>n</sub> t <sub>f</sub>     | SD/HD=0            | -   | _   | 135  | ps                | 3     |

|                            | t <sub>r</sub> , t <sub>f</sub>   | SD/HD=1            | 400 | _   | 800  | ps                | 3     |

| Mismatch in rise/fall time | $\triangle t_{r} \triangle t_{f}$ | HD/3G modes only   | _   | _   | 35   | ps                | _     |

| Duty cycle distortion      | -                                 | SD/HD=0, 2.97Gb/s  | _   | _   | 14   | ps                | 4, 5  |

|                            | _                                 | SD/HD=0, 1.485Gb/s | -   | -   | 20   | ps                | 4, 5  |

|                            | -                                 | SD/HD=1            | _   | -   | 50   | ps                | 4, 5  |

| Overshoot                  | _                                 | SD/HD=0,           | _   | _   | 10   | %                 | 4     |

<sup>1.</sup> Power consumed in GS2989 only. Termination resistors draw extra current with output swing = 800mV.

### **Table 2-2: AC Electrical Characteristics**

$V_{CC}$  = 3.3V ±5% or 2.5V ±5%;  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter            | Symbol              | Conditions                                       | Min | Тур | Max  | Units              | Notes |

|----------------------|---------------------|--------------------------------------------------|-----|-----|------|--------------------|-------|

| Output Return Loss   | ORL                 | 5 MHz – 1.485GHz                                 | 17  | 19  | _    | dB                 | 6     |

|                      |                     | 1.485GHz – 2.97GHz                               | 13  | 15  | _    | dB                 | 6     |

| Output Voltage Swing | V <sub>OUT</sub>    | $R_{SET} = 750\Omega$                            | 750 | 800 | 850  | mV <sub>p-p</sub>  | 4     |

| Input Voltage Swing  | $\triangle V_{DDI}$ | Guaranteed functional.                           | 100 | _   | 250  | mV <sub>p-pd</sub> | -     |

|                      |                     | Guaranteed to meet all published specifications. | 250 |     | 2200 | mV <sub>p-pd</sub> | -     |

| Output Enable Delay  | -                   | -                                                | _   | _   | 100  | ns                 | -     |

| Output Disable Delay | -                   | -                                                | _   | _   | 80   | ns                 | -     |

### NOTES:

- 1. The input coupling capacitor must be set accordingly for lower data rates.

- 2. Turning on input trace equalization will reduce jitter in most applications.

- 3. Rise/Fall time measured between 20% and 80% applies to 800mV output swing only.

- 4. Single-ended into a  $75\Omega$  external load.

- 5. Calculated as the actual positive bit-width compared to the expected positive bit-width using a 1010 pattern.

- 6. ORL depends on board design. The GS2989 achieves this specification on Gennum's evaluation boards.

# 3. Input/Output Circuits

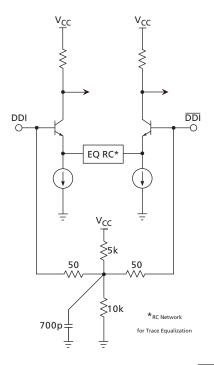

Figure 3-1: Differential Input Stage (DDI/DDI)

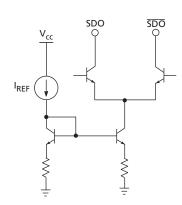

Figure 3-2: Differential Output Stage (SDO1/SDO1, SDO2/SDO2)

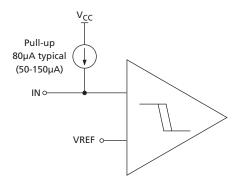

Figure 3-3: Control Input (DISABLE1, SD/HD, EQ\_EN) Figure 3-4: Control Input (DISABLE2)

## 4. Detailed Description

### 4.1 Serial Data Input

The GS2989 features a differential input buffer with on-chip  $100\Omega$  differential termination.

The serial data input signal is connected to the DDI and DDI input pins of the device.

Input signals can be single-ended or differential, DC or AC-coupled.

The serial data input buffer is capable of operation with any binary coded signal that meets the input signal level requirements, in the range of 270Mb/s to at least 2.97Gb/s.

The input circuit is self-biasing to allow for simple AC or DC-coupling of input signals to the device.

### 4.2 Input Trace-equalization

The GS2989 features fixed trace-equalization to compensate for PCB trace dielectric losses.

NOTE: This feature is not available in SD mode, and therefore trace-equalization must be disabled when operating in this mode.

The trace-equalization has two settings, OFF and ON. ON invokes a typical 3dB gain value at 1.5GHz. This value is optimized for compensating the high-frequency losses associated with approximately 10 inches of 5-mil stripline in FR4 material.

Table 4-1: Input Trace-Equalization

| <u>EQ_EN</u> | Function                       |

|--------------|--------------------------------|

| 0            | Typical 3dB Trace Equalization |

| 1            | Trace Equalization OFF         |

| Floating     | Trace Equalization OFF         |

## 4.3 Serial Data Output

The GS2989 features dual current-mode differential output drivers capable of driving up to 1800 mVpp single-ended into a 1 m length of  $75 \Omega$  cable terminated at both ends.

The output signal amplitude or swing is user configurable using an external RSET resistor.

The SDO1/SDO1 and SDO2/SDO2 pins of the device provide the serial data outputs.

## 4.3.1 Slew Rate Selection (Rise/Fall Time Requirement)

The GS2989 supports two user-selectable output slew rates.

Control of the slew rate is determined by the setting of the SD/HD input pin.

Table 4-2: Slew Rate Selection

| SD/ <del>HD</del> | Rise/Fall Time              |

|-------------------|-----------------------------|

| 0                 | SMPTE 424M & 292M compliant |

| 1                 | SMPTE 259M compliant        |

| Floating          | SMPTE 259M compliant        |

## **4.4 Output Disable**

The GS2989 supports an output disable function for each serial data differential output.

Control of this function is determined by the setting of the  $\overline{DISABLE1}$  and  $\overline{DISABLE2}$  control pins.

The serial output disables ( $\overline{DISABLE1}$  and  $\overline{DISABLE2}$ ), disable power to the current mode serial data output drivers. When asserted LOW, the SDO/ $\overline{SDO}$  output drivers are powered-down.

**Table 4-3: Output Disable**

| DISABLE1      | DISABLE2      | SDO1/SDO1           | SDO2/SDO2      |

|---------------|---------------|---------------------|----------------|

| 0             | 0 or Floating | All Chip Power Down |                |

| 0             | 1             | High-Impedance      | Operational    |

| 1 or Floating | 0 or Floating | Operational         | High-Impedance |

| 1 or Floating | 1             | Operational         | Operational    |

| Floating      | Floating      | Operational         | High-Impedance |

When  $\overline{\text{DISABLE1}}$  and  $\overline{\text{DISABLE2}}$  are driven LOW simultaneously, the entire device is powered down, and the power consumption is minimized.

## 4.5 Output Signal Presence Indicator (OSP)

The GS2989 supports an output signal presence indicator function.

The output signal presence pin ( $\overline{\text{OSP}}$ ) is an active-low output that indicates when a valid output signal has been detected at the pre-driver output.

The output signal presence function measures signal-edge energy to indicate that the pre-driver to the serial data outputs is toggling.

**Table 4-4: Output Signal Presence Indicator**

| Pre-Driver Output       | OSP Pin |

|-------------------------|---------|

| Valid signal present    | 0       |

| No valid signal present | 1       |

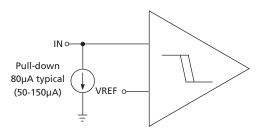

## 4.6 Output Amplitude (RSET)

The output amplitude of the GS2989 can be adjusted by changing the value of the RSET resistor as shown in Figure 4-1. For an  $800 mV_{p-p}$  output with a nominal  $\pm 7\%$  tolerance, a value of 750  $\!\Omega$  is required. A ±1% SMT resistor should be used.

The RSET resistor is part of an internal DC feedback loop in the GS2989. The resistor should be placed as close as possible to the R<sub>SET</sub> pin, and connected directly to the VCC plane (traces/wires may cause instability). In addition, the PCB capacitance should be minimized at this node by removing the PCB groundplane beneath the RSET resistor and the RSET pin.

NOTE: Care should be taken when considering layout of the RSET resistor. Please refer to Section 5.1 for more details.

Figure 4-1: V<sub>OUT</sub> vs. RSET

In order to determine the best starting value for Rset, the following formula should be used:

### Rset = 8\*(Rtrm/VoutppSE)

Where **VoutppSE** is in Volts, and both resistances are in  $\Omega$ .

**Rtrm** is the value of the termination resistors, which should be equal to the characteristic impedance of the cable, and is typically  $75\Omega$ .

The cable must be short ( $\leq 1$ m), and terminated at both ends for the formula to be valid.

Example: For a  $75\Omega$  cable, Rtrm =  $75\Omega$  (at both ends), VoutppSE = 800 mV

### $Rset = 8*(75/0.8) = 750\Omega$

This formula is not valid for long, unterminated, or improperly terminated cables.

This formula should be considered as a starting point, and actual swing values may vary based on layout. Also, for large output swings (>1040mV), smaller Rset values may be required in order to achieve the desired output swing level at HD and 3G data rates.

**Table 4-5: Typical RSET Values**

| Output Swing (mV) | RSET ( $\Omega$ ) |

|-------------------|-------------------|

| 1800*             | 332               |

| 800               | 750               |

| 500               | 1210              |

<sup>\*</sup>NOTE: In order to generate output swings greater than 1040mV, VCC\_TERM must be connected to a 5V supply.

## **4.7 Output Return Loss Measurement**

The GS2989 has a feature which allows users to measure ORL reliably while the device is still powered. The device can be put into a BALANCE mode which prevents the outputs from toggling while the device is powered on, allowing the ORL to be measured while the device is still powered.

When EQ\_EN is LOW while SD/HD is HIGH, the device goes into BALANCE mode. This mode is used during ORL measurement, disabling the AC signal path of the device without powering it down. When in BALANCE mode, the device produces equal pull-down currents in both differential shoulders of both serial data differential outputs, effectively stopping all outputs at the output common mode voltage level. Gennum recommends using BALANCE mode when measuring ORL with 2.5V termination voltage.

## 5. Application Information

## **5.1 PCB Layout**

Special attention must be paid to component layout when designing serial digital interfaces for HDTV.

An FR-4 dielectric can be used, however, controlled impedance transmission lines are required for PCB traces longer than approximately 1cm. Note the following PCB artwork features used to optimize performance:

- The PCB trace width for HD rate signals is closely matched to SMT component width to minimize reflections due to changes in trace impedance

- The PCB ground plane is removed under the GS2989 output components to minimize parasitic capacitance (NOTE: care should be taken, as removing too much of the plane will make the system susceptible to EMI)

- The PCB ground plane is removed under the GS2989 RSET pin and resistor to minimize parasitic capacitance. The RSET resistor should be directly connected to the VCC plane

- Input and output BNC connectors are surface mounted in-line to eliminate a transmission line stub caused by a BNC mounting via high-speed traces

- High-speed traces are round-curved (rather than 45° or 90° angles) to minimize impedance variations due to change of PCB trace width

**NOTE:** For more recommendations on Trace Lengths, ORL Inductor Values and other PCB Layout Considerations, please refer to Gennum's GS2989 Design Guide (Doc ID 52070).

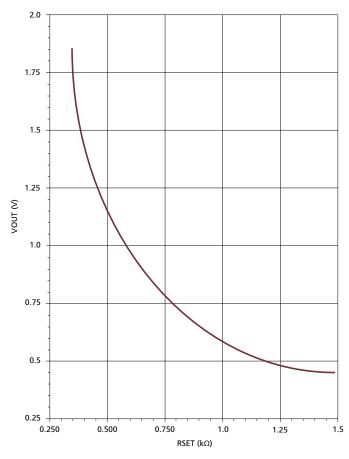

## **5.2 Typical Application Circuit**

NOTE: All resistors in Ohms, capacitors in Farads, and inductors in Henrys, unless otherwise stated.

\* Typical value: varies with layout, and represents a trade-off Typical Value, values with layout, and represents a used-between good eye shape and output return loss. 5n6 is the optimum value for an 800mV output swing and 3.3V operation. 4n7 is the optimum value for an 800mV output swing and

2.5V operation.

6n8 is the optimum value for an 1800mV output swing.

Figure 5-1: Typical Application Circuit

# 6. Package & Ordering Information

## **6.1 Package Dimensions**

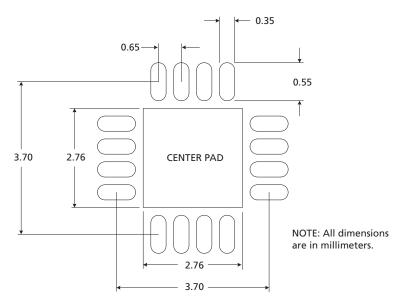

## **6.2 Recommended PCB Footprint**

The Center Pad should be connected to the most negative power supply plane (VEE) by a minimum of 5 vias.

**NOTE**: Suggested dimensions only. Final dimensions should conform to customer design rules and process optimizations.

## **6.3 Packaging Data**

| Parameter                                                                                | Value                              |

|------------------------------------------------------------------------------------------|------------------------------------|

| Package type / dimensions / pad pitch                                                    | 16-pin QFN / 4mm x 4mm /<br>0.65mm |

| Package Drawing Reference                                                                | JEDEC M0220                        |

| Moisture Sensitivity Level                                                               | 3                                  |

| Junction to Case Thermal Resistance, $\boldsymbol{\theta}_{j\text{-}c}$                  | 31.0°C/W                           |

| Junction to Air Thermal Resistance, $\boldsymbol{\theta}_{j\text{-}a}$ (at zero airflow) | 43.8°C/W                           |

| Psi, Ψ                                                                                   | 11.0°C/W                           |

| Pb-free and RoHS compliant, Halogen-free                                                 | Yes                                |

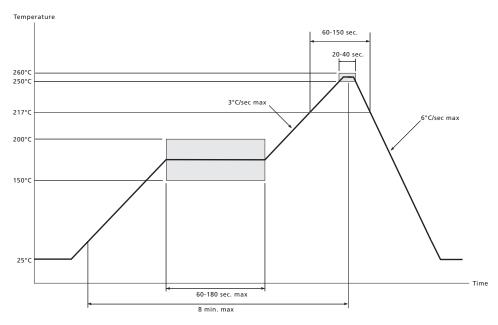

### **6.4 Solder Reflow Profiles**

The device is manufactured with Matte-Sn terminations and is compatible with both standard eutectic and Pb-free solder reflow profiles. MSL qualification was performed using the maximum Pb-free reflow profile shown in Figure 6-1.

Figure 6-1: Maximum Pb-free Solder Reflow Profile (Preferred)

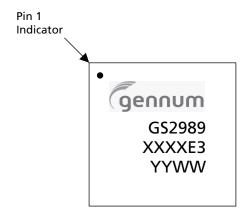

## 6.5 Marking Diagram

| Instructions: |                                      |

|---------------|--------------------------------------|

| GS2989        | Package Mark                         |

| XXXX          | Last 4 digits (excluding decimal) of |

|               | SAP Batch Assembly (FIN) as listed   |

|               | on Packing Slip                      |

| E3            | Pb-free & Green indicator            |

| YYWW          | Date Code                            |

## **6.6 Ordering Information**

|        | Part Number   | Package                    | Temperature Range |

|--------|---------------|----------------------------|-------------------|

| GS2989 | GS2989-INE3   | 16-pin QFN                 | -40°C to 85°C     |

| GS2989 | GS2989-INTE3  | 16-pin QFN<br>250pc Reel   | -40°C to 85°C     |

| GS2989 | GS2989-INTE3Z | 16-pin QFN<br>2,500pc Reel | -40°C to 85°C     |

#### **DOCUMENT IDENTIFICATION DATA SHEET**

The product is in production. Gennum reserves the right to make changes to the product at any time without notice to improve reliability, function or design, in order to provide the best product possible.

#### **CAUTION**

Phone: +1 (905) 632-2996

E-mail: corporate@gennum.com

**ELECTROSTATIC SENSITIVE DEVICES** DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

#### **GENNUM CORPORATE HEADQUARTERS**

4281 Harvester Road, Burlington, Ontario L7L 5M4 Canada

**OTTAWA** 232 Herzberg Road, Suite 101 Kanata, Ontario K2K 2A1

Phone: +1 (613) 270-0458 Fax: +1 (613) 270-0429

#### **CALGARY**

3553 - 31st St. N.W., Suite 320 Calgary, Alberta T2L 2K7

Phone: +1 (403) 284-2672

### **UNITED KINGDOM**

South Building, Walden Court Parsonage Lane, Bishop's Stortford Hertfordshire, CM23 5DB United Kingdom

Phone: +44 1279 714170 Fax: +44 1279 714171

### INDIA

#208(A), Nirmala Plaza, Airport Road, Forest Park Square Bhubaneswar 751009

Phone: +91 (674) 653-4815 Fax: +91 (674) 259-5733

#### **SNOWBUSH IP - A DIVISION OF GENNUM**

439 University Ave. Suite 1700 Toronto, Ontario M5G 1Y8

Phone: +1 (416) 925-5643 Fax: +1 (416) 925-0581 F-mail: sales@snowbush.com Web Site: http://www.snowbush.com

#### MEXICO

288-A Paseo de Maravillas Jesus Ma., Aquascalientes

Mexico 20900

Phone: +1 (416) 848-0328

#### JAPAN KK

Shinjuku Green Tower Building 27F 6-14-1, Nishi Shinjuku Shinjuku-ku, Tokyo, 160-0023

Japan

Phone: +81 (03) 3349-5501 Fax: +81 (03) 3349-5505

E-mail: gennum-japan@gennum.com Web Site: http://www.gennum.co.jp

6F-4, No.51, Sec.2, Keelung Rd. Sinyi District, Taipei City 11502

Taiwan R.O.C.

Phone: (886) 2-8732-8879 Fax: (886) 2-8732-8870

E-mail: gennum-taiwan@gennum.com

### **GERMANY**

Hainbuchenstraße 2 80935 Muenchen (Munich), Germany

Fax: +1 (905) 632-2055

www.gennum.com

Phone: +49-89-35831696 Fax: +49-89-35804653

E-mail: gennum-germany@gennum.com

#### **NORTH AMERICA WESTERN REGION**

691 South Milpitas Blvd., Suite #200 Milpitas, CA 95035

**United States**

Phone: +1 (408) 934-1301 Fax: +1 (408) 934-1029

E-mail: naw\_sales@gennum.com

### **NORTH AMERICA EASTERN REGION**

4281 Harvester Road Burlington, Ontario L7L 5M4 Canada

Phone: +1 (905) 632-2996 Fax: +1 (905) 632-2055

E-mail: nae\_sales@gennum.com

Gennum Corporation assumes no liability for any errors or omissions in this document, or for the use of the circuits or devices described herein. The sale of the circuit or device described herein does not imply any patent license, and Gennum makes no representation that the circuit or device is free from patent

All other trademarks mentioned are the properties of their respective owners.

GENNUM and the Gennum logo are registered trademarks of Gennum Corporation.

© Copyright 2009 Gennum Corporation. All rights reserved.

www.gennum.com