## mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Embedded LPDDR3 SDRAM**

## EDF8164A3PK, EDFA164A2PK

## Features

- Ultra-low-voltage core and I/O power supplies

- Frequency range

- 800/933 MHz (data rate: 1600/1866 Mb/s/pin)

- 8*n* prefetch DDR architecture

- 8 internal banks for concurrent operation

- Multiplexed, double data rate, command/address inputs; commands entered on each CK\_t/CK\_c edge

- Bidirectional/differential data strobe per byte of data (DQS\_t/DQS\_c)

- Programmable READ and WRITE latencies (RL/WL)

- Burst length: 8

- Per-bank refresh for concurrent operation

- Auto temperature-compensated self refresh (ATCSR) by built-in temperature sensor

- Partial-array self refresh (PASR)

- Deep power-down mode (DPD)

- Selectable output drive strength (DS)

**Table 1: Configuration Addressing**

- Clock-stop capability

- Lead-free (RoHS-compliant) and halogen-free packaging

## Options

- V<sub>DD1</sub>/V<sub>DD2</sub>/V<sub>DDCA</sub>/V<sub>DDO</sub>: 1.8V/1.2V/1.2V/1.2V

- Array configuration

- 128 Meg x 64 (DDP)

- 256 Meg x 64 (QDP)

- Packaging

- 12mm x 12mm, 216-ball PoP FBGA package

- Operating temperature range

- From –30°C to +85°C

| Architecture                          | 128 Meg x 64                      | 256 Meg x 64                               |

|---------------------------------------|-----------------------------------|--------------------------------------------|

| Density per package                   | 8Gb                               | 16Gb                                       |

| Die per package                       | 2                                 | 4                                          |

| Ranks (CS_n) per channel              | 1                                 | 2                                          |

| Die per channel                       | 1                                 | 2                                          |

| Configuration                         | 16 Meg x 32 x 8 banks x 2 channel | 16 Meg x 32 x 8 banks x 2 rank x 2 channel |

| Row addressing                        | 16K A[13:0]                       | 16K A[13:0]                                |

| Column addressing (same for each die) | 1K A[9:0]                         | 1K A[9:0]                                  |

PDF: embedded\_lpddr3\_2e0f\_20151022 216b\_12x12\_2ch\_8-16gb\_2e0f\_embedded-lpddr3.pdf - Rev. A 10/15 EN

\*Products and specifications discussed herein are for evaluation and reference purposes only and are subject to change by Micron without notice. Products are only warranted by Micron to meet Micron's production data sheet specifications.

1

#### **Table 2: Key Timing Parameters**

| Speed<br>Grade | Clock Rate<br>(MHz) | Data Rate<br>(Mb/s/pin) | WRITE Latency<br>(Set A/B) | READ<br>Latency |

|----------------|---------------------|-------------------------|----------------------------|-----------------|

| GD             | 800                 | 1600                    | 6/9                        | 12              |

| JD             | 933                 | 1866                    | 8/11                       | 14              |

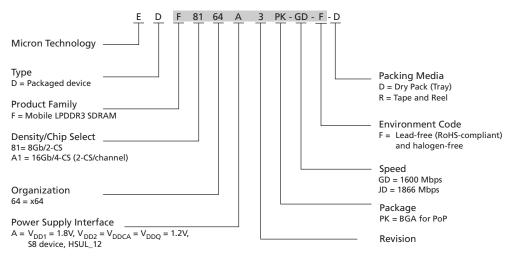

#### **Table 3: Part Number Description**

| Part<br>Number                                                                       | Total<br>Density | Configuration | Ranks | Channels | Package<br>Size                    | Ball<br>Pitch |

|--------------------------------------------------------------------------------------|------------------|---------------|-------|----------|------------------------------------|---------------|

| EDF8164A3PK-GD-F-D<br>EDF8164A3PK-GD-F-R<br>EDF8164A3PK-JD-F-D<br>EDF8164A3PK-JD-F-R | 8Gb              | 128 Meg x 64  | 1     | 2        | 12mm x 12mm<br>(0.70mm MAX height) | 0.40mm        |

| EDFA164A2PK-GD-F-D<br>EDFA164A2PK-GD-F-R<br>EDFA164A2PK-JD-F-D<br>EDFA164A2PK-JD-F-R | 16Gb             | 256 Meg x 64  | 2     | 2        | 12mm x 12mm<br>(0.80mm MAX height) | 0.40mm        |

#### **Figure 1: Marketing Part Number Chart**

## 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3\_SDRAM **Features**

## **Contents**

| Ball Assignments                                              |      |

|---------------------------------------------------------------|------|

| Ball Descriptions                                             | 12   |

| Package Block Diagrams                                        | 14   |

| Package Dimensions                                            | 16   |

| MR0, MR5–MR8 Readout                                          | 18   |

| I <sub>DD</sub> Specifications – Dual Die, Dual Channel       | 19   |

| I <sub>DD</sub> Specifications – Quad Die, Dual Channel       | 22   |

| Pin Capacitance                                               | 26   |

| LPDDR3 Array Configuration                                    | 27   |

| General Notes                                                 | . 27 |

| Functional Description                                        | 28   |

| Simplified Bus Interface State Diagram                        | 30   |

| Power-Up and Initialization                                   | . 32 |

| Voltage Ramp and Device Initialization                        |      |

| Initialization After Reset (Without Voltage Ramp)             | 34   |

| Power-Off Sequence                                            | 35   |

| Uncontrolled Power-Off Sequence                               | . 35 |

| Standard Mode Register Definition                             |      |

| Mode Register Assignments and Definitions                     | . 36 |

| Commands and Timing                                           | 46   |

| ACTIVATE Command                                              | 47   |

| 8-Bank Device Operation                                       | 47   |

| Read and Write Access Modes                                   | 48   |

| Burst READ Command                                            | 49   |

| <sup>t</sup> DQSCK Delta Timing                               | 51   |

| Burst WRITE Command                                           | 55   |

| Write Data Mask                                               | . 59 |

| PRECHARGE Command                                             | 60   |

| Burst READ Operation Followed by PRECHARGE                    | 61   |

| Burst WRITE Followed by PRECHARGE                             | 62   |

| Auto Precharge                                                | 63   |

| Burst READ with Auto Precharge                                | 63   |

| Burst WRITE with Auto Precharge                               |      |

| REFRESH Command                                               | 66   |

| REFRESH Requirements                                          | 69   |

| SELF REFRESH Operation                                        | 71   |

| Partial-Array Self Refresh (PASR) – Bank Masking              | 72   |

| Partial-Array Self Refresh – Segment Masking                  | 72   |

| MODE REGISTER READ                                            |      |

| MRR Following Idle Power-Down State                           |      |

| Temperature Sensor                                            | 76   |

| DQ Calibration                                                |      |

| MODE REGISTER WRITE                                           | . 79 |

| MRW RESET Command                                             | . 79 |

| MRW ZQ Calibration Commands                                   | . 80 |

| ZQ External Resistor Value, Tolerance, and Capacitive Loading |      |

| MRW – CA Training Mode                                        |      |

| MRW - Write Leveling Mode                                     |      |

| On-Die Termination (ODT)                                      |      |

| ODT Mode Register                                             | 87   |

#### **Solution** 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3 SDRAM **Features**

| Agreebron oue ODT                                                       | 07    |

|-------------------------------------------------------------------------|-------|

| Asychronous ODT<br>ODT During READ Operations (READ or MRR)             |       |

|                                                                         |       |

| ODT During Power-Down                                                   |       |

| ODT During Self Refresh                                                 |       |

| ODT During Deep Power-Down                                              |       |

| ODT During CA Training and Write Leveling                               |       |

| Power-Down                                                              |       |

| Deep Power-Down                                                         |       |

| Input Clock Frequency Changes and Stop Events                           |       |

| Input Clock Frequency Changes and Clock Stop with CKE LOW               | . 98  |

| Input Clock Frequency Changes and Clock Stop with CKE HIGH              | . 99  |

| NO OPERATION Command                                                    |       |

| Truth Tables                                                            |       |

| Absolute Maximum Ratings                                                |       |

| Electrical Specifications – I <sub>DD</sub> Measurements and Conditions |       |

| I <sub>DD</sub> Specifications                                          |       |

| AC and DC Operating Conditions                                          |       |

| AC and DC Logic Input Measurement Levels for Single-Ended Signals       |       |

| V <sub>REF</sub> Tolerances                                             | . 114 |

| Input Signal                                                            |       |

| AC and DC Logic Input Measurement Levels for Differential Signals       |       |

| Single-Ended Requirements for Differential Signals                      | 118   |

| Differential Input Crosspoint Voltage                                   | . 119 |

| Input Slew Rate                                                         | . 120 |

| Output Characteristics and Operating Conditions                         | . 122 |

| Single-Ended Output Slew Rate                                           | . 122 |

| Differential Output Slew Rate                                           | . 124 |

| HSUL_12 Driver Output Timing Reference Load                             | . 126 |

| Output Driver Impedance                                                 |       |

| Output Driver Impedance Characteristics with ZQ Calibration             | . 128 |

| Output Driver Temperature and Voltage Sensitivity                       | . 128 |

| Output Impedance Characteristics Without ZQ Calibration                 |       |

| ODT Levels and I-V Characteristics                                      | . 133 |

| Clock Specification                                                     |       |

| <sup>t</sup> CK(abs), <sup>t</sup> CH(abs), and <sup>t</sup> CL(abs)    | . 135 |

| Clock Period Jitter                                                     |       |

| Clock Period Jitter Effects on Core Timing Parameters                   |       |

| Cycle Time Derating for Core Timing Parameters                          |       |

| Clock Cycle Derating for Core Timing Parameters                         |       |

| Clock Jitter Effects on Command/Address Timing Parameters               |       |

| Clock Jitter Effects on Read Timing Parameters                          |       |

| Clock Jitter Effects on Write Timing Parameters                         |       |

| Refresh Requirements                                                    |       |

| AC Timing                                                               |       |

| CA and CS_n Setup, Hold, and Derating                                   |       |

| Data Setup, Hold, and Slew Rate Derating                                |       |

| Revision History                                                        |       |

| Rev. A – 10/15                                                          |       |

|                                                                         |       |

## **List of Figures**

| Figure 1:   | Marketing Part Number Chart                                              | . 2 |

|-------------|--------------------------------------------------------------------------|-----|

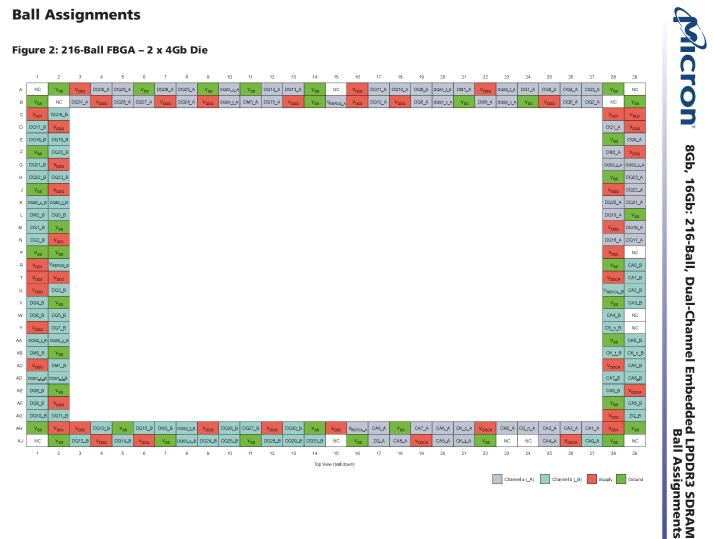

| Figure 2:   | 216-Ball FBGA – 2 x 4Gb Die                                              | 10  |

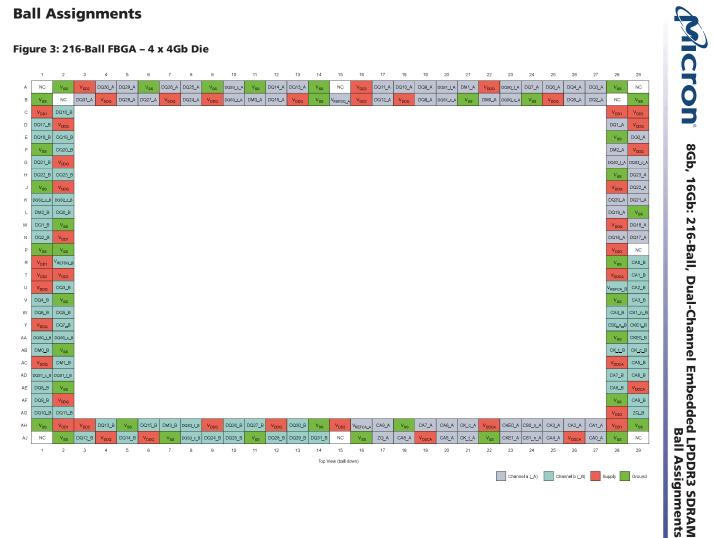

| Figure 3:   | 216-Ball FBGA – 4 x 4Gb Die                                              | 11  |

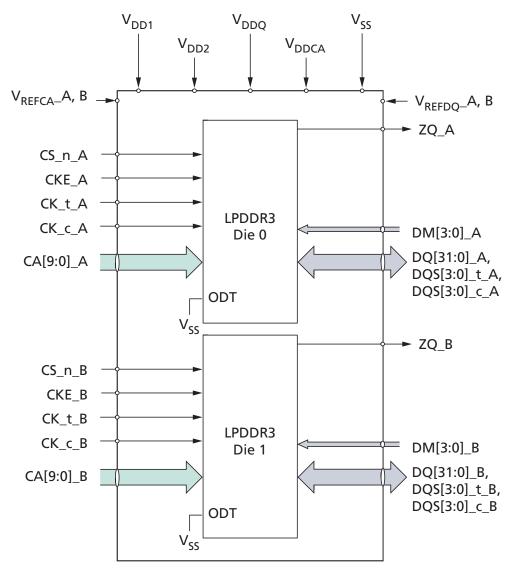

| Figure 4:   | Dual-Die, Dual-Channel Package Block Diagram                             | 14  |

| Figure 5:   | Quad-Die, Dual-Channel Package Block Diagram                             | 15  |

|             | 216-Ball FBGA (12mm x 12mm) – EDF8164A3PK                                |     |

| Figure 7: 2 | 216-Ball FBGA (12mm x 12mm) – EDFA164A2PK                                | 17  |

|             | Functional Block Diagram                                                 |     |

|             | Simplified State Diagram                                                 |     |

|             | Voltage Ramp and Initialization Sequence                                 |     |

|             | Command and Input Setup and Hold                                         |     |

|             | CKE Input Setup and Hold                                                 |     |

|             | ACTIVATE Command                                                         |     |

|             | <sup>t</sup> FAW Timing                                                  |     |

|             | READ Output Timing                                                       |     |

|             | Burst READ – $RL = 12$ , $BL = 8$ , <sup>t</sup> DQSCK > <sup>t</sup> CK |     |

| Figure 17:  | Burst READ - RL = 12, BL = 8, tDQSCK < tCK                               | 50  |

|             | Burst READ Followed by Burst WRITE – $RL = 12$ , $WL = 6$ , $BL = 8$     |     |

|             | Seamless Burst READ – RL = 6, BL = 8, $^{t}CCD = 4$                      |     |

|             | <sup>t</sup> DQSCKDL Timing                                              |     |

| 0           | <sup>t</sup> DQSCKDM Timing                                              |     |

|             | <sup>t</sup> DQSCKDS Timing                                              |     |

|             | Data Input (WRITE) Timing                                                |     |

| Figure 24:  | Burst WRITE                                                              | 56  |

|             | Method for Calculating <sup>t</sup> WPRE Transitions and Endpoints       |     |

|             | Method for Calculating <sup>t</sup> WPST Transitions and Endpoints       |     |

|             | Burst WRITE Followed by Burst READ                                       |     |

|             | Seamless Burst WRITE – $WL = 4$ , $BL = 8$ , <sup>t</sup> CCD = 4        |     |

|             | Data Mask Timing                                                         |     |

|             | Write Data Mask – Second Data Bit Masked                                 |     |

|             | Burst READ Followed by PRECHARGE – BL = 8, $RU(^{t}RTP(MIN)/^{t}CK) = 2$ |     |

|             | Burst WRITE Followed by PRECHARGE – $BL = 8$                             |     |

|             | LPDDR3 – Burst READ with Auto Precharge                                  |     |

|             | Burst WRITE with Auto Precharge – $BL = 8$                               |     |

|             | REFRESH Command Timing                                                   |     |

|             | Postponing REFRESH Commands                                              |     |

|             | Pulling In REFRESH Commands                                              |     |

|             |                                                                          |     |

|             | All-Bank REFRESH Operation                                               |     |

|             | Per-Bank REFRESH Operation                                               |     |

| -           | SELF REFRESH Operation                                                   |     |

|             | MRR Timing                                                               |     |

| Figure 42:  | READ to MRR Timing                                                       | 75  |

|             | Burst WRITE Followed by MRR                                              |     |

|             | MRR After Idle Power-Down Exit                                           |     |

|             | Temperature Sensor Timing                                                |     |

|             | MR32 and MR40 DQ Calibration Timing                                      |     |

| Figure 47:  | MODE REGISTER WRITE Timing                                               | 79  |

| 0           | MODE REGISTER WRITE Timing for MRW RESET                                 |     |

|             | ZQ Timings                                                               |     |

| Figure 50:  | CA Training Timing                                                       | 83  |

#### **Solution** 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3 SDRAM **Features**

| <ul> <li>Figure 51: Write-Leveling Timing</li> <li>Figure 52: Functional Representation of On-Die Termination</li> <li>Figure 53: Asynchronous ODT Timing – RL = 12</li> <li>Figure 54: Automatic ODT Timing During READ Operation – RL = m</li> <li>Figure 55: ODT Timing During Power-Down, Self Refresh, Deep Power-Down Entry/Exit</li> <li>Figure 56: Power-Down Entry and Exit Timing</li> <li>Figure 57: CKE Intensive Environment</li> <li>Figure 58: REFRESH to REFRESH Timing in CKE Intensive Environments</li> </ul> | 87           89           90           90           90           90 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| <ul> <li>Figure 53: Asynchronous ODT Timing – RL = 12</li> <li>Figure 54: Automatic ODT Timing During READ Operation – RL = m</li> <li>Figure 55: ODT Timing During Power-Down, Self Refresh, Deep Power-Down Entry/Exit</li> <li>Figure 56: Power-Down Entry and Exit Timing</li> <li>Figure 57: CKE Intensive Environment</li> </ul>                                                                                                                                                                                           | 89<br>90<br>90<br>92                                                |

| <ul> <li>Figure 54: Automatic ODT Timing During READ Operation – RL = m</li> <li>Figure 55: ODT Timing During Power-Down, Self Refresh, Deep Power-Down Entry/Exit</li> <li>Figure 56: Power-Down Entry and Exit Timing</li> <li>Figure 57: CKE Intensive Environment</li> </ul>                                                                                                                                                                                                                                                 | 90<br>90<br>92                                                      |

| Figure 55:ODT Timing During Power-Down, Self Refresh, Deep Power-Down Entry/ExitFigure 56:Power-Down Entry and Exit TimingFigure 57:CKE Intensive Environment                                                                                                                                                                                                                                                                                                                                                                    | 90<br>92                                                            |

| Figure 56: Power-Down Entry and Exit Timing<br>Figure 57: CKE Intensive Environment                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92                                                                  |

| Figure 57: CKE Intensive Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92                                                                  |

| Figure 58: REFRESH to REFRESH Timing in CKE Intensive Environments                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 93                                                                  |

| Figure 59: READ to Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |

| Figure 60: READ with Auto Precharge to Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

| Figure 61: WRITE to Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                     |

| Figure 62: WRITE with Auto Precharge to Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |

| Figure 63: REFRESH Command to Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |

| Figure 64: ACTIVATE Command to Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |

| Figure 65: PRECHARGE Command to Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                     |

| Figure 66: MRR Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |

| Figure 67: MRW Command to Power-Down Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |

| Figure 68: Deep Power-Down Entry and Exit Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                     |

| Figure 69: $V_{\text{REF}}$ DC Tolerance and $V_{\text{REF}}$ AC Noise Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 114                                                                 |

| Figure 70: LPDDR3-1600 to LPDDR3-1333 Input Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                     |

| Figure 71: LPDDR3-2133 to LPDDR3-1866 Input Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 116                                                                 |

| Figure 72: Differential AC Swing Time and <sup>t</sup> DVAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 117                                                                 |

| Figure 73: Single-Ended Requirements for Differential Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                     |

| Figure 74: V <sub>IX</sub> Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 120                                                                 |

| Figure 75: Differential Input Slew Rate Definition for CK and DQS                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |

| Figure 76: Single-Ended Output Slew Rate Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 123                                                                 |

| Figure 77: Differential Output Slew Rate Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 124                                                                 |

| Figure 78: Overshoot and Undershoot Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |

| Figure 79: HSUL_12 Driver Output Reference Load for Timing and Slew Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |

| Figure 80: Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |

| Figure 81: Output Impedance = 240Ω, I-V Curves After ZQRESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 131                                                                 |

| Figure 82: Output Impedance = 240Ω, I-V Curves After Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132                                                                 |

| Figure 83: ODT Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

| Figure 84: Typical Slew Rate and <sup>t</sup> VAC – <sup>t</sup> IS for CA and CS_n Relative to Clock                                                                                                                                                                                                                                                                                                                                                                                                                            | 149                                                                 |

| Figure 85: Typical Slew Rate – <sup>t</sup> IH for CA and CS_n Relative to Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 150                                                                 |

| Figure 86: Tangent Line – <sup>t</sup> IS for CA and CS_n Relative to Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 151                                                                 |

| Figure 87: Tangent Line – <sup>t</sup> IH for CA and CS_n Relative to Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                     |

| Figure 88: Typical Slew Rate and <sup>t</sup> VAC – <sup>t</sup> DS for DQ Relative to Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                     |

| Figure 89: Typical Slew Rate – <sup>t</sup> DH for DQ Relative to Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |

| Figure 90: Tangent Line – <sup>t</sup> DS for DQ with Respect to Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

| Figure 91: Tangent Line – <sup>t</sup> DH for DQ with Respect to Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

## 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3\_SDRAM **Features**

## **List of Tables**

|                          | nfiguration Addressing                                                 |     |

|--------------------------|------------------------------------------------------------------------|-----|

| Table 2: Key             | Timing Parameters                                                      | . 2 |

|                          | t Number Description                                                   |     |

| Table 4: Ball            | /Pad Descriptions                                                      | 12  |

| Table 5: Mod             | de Register Contents                                                   | 18  |

| Table 6: I <sub>DD</sub> | Specifications                                                         | 19  |

| Table 7: IDD6            | <sup>6</sup> Partial-Array Self Refresh Current at 45°C                | 21  |

|                          | 6 Partial-Array Self Refresh Current at 85°C                           |     |

| Table 9: I <sub>DD</sub> | Specifications                                                         | 22  |

| Table 10: IDT            | D6 Partial-Array Self Refresh Current at 45°C                          | 24  |

| Table 11: IDT            | D6 Partial-Array Self Refresh Current at 85°C                          | 25  |

| Table 12: Int            | put/Output Capacitance                                                 | 26  |

|                          | Itage Ramp Conditions                                                  |     |

|                          | itialization Timing Parameters                                         |     |

|                          | wer Supply Conditions                                                  |     |

|                          | wer-Off Timing                                                         |     |

|                          | ode Register Assignments                                               |     |

|                          | R0 Device Feature 0 ( $MA[7:0] = 00h$ )                                |     |

|                          | R0 Op-Code BIt Definitions                                             |     |

|                          | R1 Device Feature 1 (MA[7:0] = $01h$ )                                 |     |

|                          | R1 Op-Code Bit Definitions                                             |     |

|                          | Irst Sequence                                                          |     |

|                          | R2 Device Feature 2 (MA[7:0] = $02h$ )                                 |     |

| Table 24: MI             | R2 Op-Code Bit Definitions                                             | 30  |

|                          | DDR3 READ and WRITE Latency                                            |     |

|                          | R3 I/O Configuration 1 (MA[7:0] = $03h$ )                              |     |

| Table 27: MI             | R3 Op-Code Bit Definitions                                             | 40  |

|                          | R4 Device Temperature (MA[7:0] = 04h)                                  |     |

| Table 20. MI             | R4 Op-Code Bit Definitions                                             | 40  |

|                          | R5 Basic Configuration 1 (MA[7:0] = 05h)                               |     |

| Table 21. MI             | R5 Op-Code Bit Definitions                                             | 41  |

|                          |                                                                        |     |

| Table 32: MI             | R6 Basic Configuration 2 (MA[7:0] = 06h)<br>R6 Op-Code Bit Definitions | 41  |

|                          |                                                                        |     |

| Table 34: MI             | R7 Basic Configuration 3 (MA[7:0] = 07h)<br>R7 Op-Code Bit Definitions | 41  |

|                          |                                                                        |     |

|                          | R8 Basic Configuration 4 (MA[7:0] = 08h)                               |     |

|                          | R8 Op-Code Bit Definitions                                             |     |

|                          | R9 Test Mode ( $MA[7:0] = 09h$ )                                       |     |

|                          | R10 Calibration (MA[7:0] = 0Ah)                                        |     |

|                          | R10 Op-Code Bit Definitions                                            |     |

|                          | R11 ODT Control (MA[7:0] = 0Bh)                                        |     |

|                          | R11 Op-Code Bit Definitions                                            |     |

|                          | R16 PASR Bank Mask (MA[7:0] = 010h)                                    |     |

|                          | R16 Op-Code Bit Definitions                                            |     |

|                          | R17 PASR Segment Mask (MA[7:0] = 011h)                                 |     |

|                          | R17 PASR Segment Mask Definitions                                      |     |

|                          | R17 PASR Row Address Ranges in Masked Segments                         |     |

|                          | $R63 \text{ RESET } (MA[7:0] = 3Fh) - MRW \text{ Only } \dots$         |     |

|                          | served Mode Registers                                                  |     |

| Table 50: Bar            | nk Selection for PRECHARGE by Address Bits                             | 60  |

#### **Solution** 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3 SDRAM **Features**

|           | PRECHARGE and Auto Precharge Clarification                                            |                |

|-----------|---------------------------------------------------------------------------------------|----------------|

| Table 52: | REFRESH Command Scheduling Separation Requirements                                    |                |

| Table 53: | Bank- and Segment-Masking Example                                                     |                |

|           | Temperature Sensor Definitions and Operating Conditions                               |                |

| Table 55: | Data Calibration Pattern Description                                                  |                |

|           | Truth Table for MRR and MRW                                                           |                |

| Table 57: | CA Training Mode Enable (MR41 (29H, 0010 1001b), OP = A4H (1010 0100b))               |                |

| Table 58: | CA Training Mode Disable (MR42 (2AH, 0010 1010b), OP = A8H(1010 1000b))               |                |

|           | CA to DQ Mapping (CA Training Mode Enabled with MR41)                                 |                |

| Table 60: | CA Training Mode Enable (MR48 (30H, 0011 0000b), OP = C0H (1100 0000b))               |                |

|           | CA to DQ Mapping (CA Training Mode Enabled with MR48)                                 |                |

|           | DRAM Termination Function in Write-Leveling Mode                                      |                |

| Table 63: | ODT States Truth Table                                                                |                |

|           | Command Truth Table                                                                   |                |

|           | CKE Truth Table                                                                       |                |

|           | Current State Bank <i>n</i> to Command to Bank <i>n</i> Truth Table                   |                |

|           | Current State Bank <i>n</i> to Command to Bank <i>m</i> Truth Table                   |                |

|           | DM Truth Table                                                                        |                |

|           | Absolute Maximum DC Ratings                                                           |                |

|           | Switching for CA Input Signals                                                        |                |

| Table 71. | Switching for $I_{DD4R}$                                                              | 100<br>108     |

| Table 71. | Switching for $I_{DD4W}$                                                              | 100 100<br>100 |

|           | $I_{DD}$ Specification Parameters and Operating Conditions                            |                |

|           | Recommended DC Operating Conditions                                                   |                |

| Table 74. | Input Leakage Current                                                                 |                |

| Table 75: | Input Leakage Current                                                                 |                |

|           | Operating Temperature Range                                                           |                |

|           | Single-Ended AC and DC Input Levels for CA and CS_n Inputs                            |                |

| Table 78: | Single-Ended AC and DC Input Levels for CKE                                           |                |

| Table 79: | Single-Ended AC and DC Input Levels for DQ and DM                                     |                |

|           | Differential AC and DC Input Levels                                                   |                |

| Table 81: | CK and DQS Time Requirements Before Ringback ( <sup>t</sup> DVAC)                     |                |

|           | Single-Ended Levels for CK and DQS                                                    |                |

| Table 83: | Crosspoint Voltage for Differential Input Signals (CK, CK_c, DQS_t, DQS_c)            |                |

|           | Differential Input Slew Rate Definition                                               |                |

|           | Single-Ended AC and DC Output Levels                                                  |                |

|           | Differential AC and DC Output Levels                                                  |                |

|           | Single-Ended Output Slew Rate Definition                                              |                |

|           | Single-Ended Output Slew Rate                                                         |                |

| Table 89: | Differential Output Slew Rate Definition                                              |                |

| Table 90: | Differential Output Slew Rate                                                         |                |

|           | AC Overshoot/Undershoot Specification                                                 |                |

|           | Output Driver DC Electrical Characteristics with ZQ Calibration                       |                |

|           | Output Driver Sensitivity Definition                                                  |                |

| Table 94: | Output Driver Temperature and Voltage Sensitivity                                     |                |

| Table 95: | Output Driver DC Electrical Characteristics Without ZQ Calibration                    |                |

|           | I-V Curves                                                                            |                |

| Table 97: | ODT DC Electrical Characteristics ( $R_{ZQ} = 240\Omega$ After Proper ZQ Calibration) |                |

| Table 98: | Definitions and Calculations                                                          |                |

|           | <sup>t</sup> CK(abs), <sup>t</sup> CH(abs), and <sup>t</sup> CL(abs) Definitions      |                |

|           | Refresh Requirement Parameters (Per Density)                                          |                |

|           | AC Timing                                                                             |                |

|           | CA Setup and Hold Base Values                                                         |                |

### **Solution** 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3 SDRAM **Features**

| Table 103: | CS_n Setup and Hold Base Values                                                | . 147 |

|------------|--------------------------------------------------------------------------------|-------|

|            | Derating Values for AC/DC-Based <sup>t</sup> IS/ <sup>t</sup> IH (AC150)       |       |

| Table 105: | Derating Values for AC/DC-Based <sup>t</sup> IS/ <sup>t</sup> IH (AC135)       | . 147 |

| Table 106: | Required Time for Valid Transition – $^{t}VAC > V_{IH(AC)}$ and $< V_{IL(AC)}$ | . 148 |

|            | Data Setup and Hold Base Values                                                |       |

| Table 108: | Derating Values for AC/DC-Based <sup>t</sup> DS/ <sup>t</sup> DH (AC150)       | . 154 |

| Table 109: | Derating Values for AC/DC-Based <sup>t</sup> DS/ <sup>t</sup> DH (AC135)       | . 154 |

| Table 110: | Required Time for Valid Transition – $^{t}VAC > V_{IH(AC)}$ or $< V_{IL(AC)}$  | . 155 |

10

Preliminary

PDF: embedded\_lpddr3\_2e0f\_20151022 216b\_12x12\_2ch\_8-16gb\_2e0f\_embedded-lpddr3.pdf – Rev. A 10/15 EN

Micron Technology, Inc. reserves the right to change products or specifications without notice. © 2015 Micron Technology, Inc. All rights reserved.

1

Preliminary

## **Ball Descriptions**

The ball/pad description table below is a comprehensive list of signals for the device family. All signals listed may not be supported on this device. See ball assignments for information specific to this device.

#### Table 4: Ball/Pad Descriptions

| Symbol                                                                                   | Туре      | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CA[9:0]_A,<br>CA[9:0]_B                                                                  | Input     | <b>Command/address inputs:</b> Provide the command and address inputs according to the command truth table. A separate CA[9:0] is provided for each channel (A and B).                                                                                                                                                                      |

| CK_t_B, CK_t_A                                                                           | Input     | <b>Clock:</b> Differential clock inputs. All CA inputs are sampled on both rising and falling                                                                                                                                                                                                                                               |

| CK_t_B, CK_t_A<br>CK_c_B, CK_c_A                                                         | mput      | edges of CK. CS and CKE inputs are sampled at the rising edge of CK. AC timings are referenced to clock. A separate CK_t/CK_c is provided for each channel (A and B).                                                                                                                                                                       |

| CKE[1:0]_A,<br>CKE[1:0]_B                                                                | Input     | <b>Clock enable:</b> CKE HIGH activates and CKE LOW deactivates the internal clock signals, input buffers, and output drivers. Power-saving modes are entered and exited via CKE transitions. CKE is considered part of the command code. CKE is sampled on the rising edge of CK. A separate CKE is provided for each channel (A and B).   |

| CS[1:0]_n_A,<br>CS[1:0]_n_B                                                              | Input     | <b>Chip select:</b> Considered part of the command code and is sampled on the rising edge of CK. A separate CS_n is provided for each channel (A and B).                                                                                                                                                                                    |

| DM[3:0]_B,<br>DM[3:0]_A                                                                  | Input     | <b>Input data mask:</b> Input mask signal for write data. Although DM balls are input-only, the DM loading is designed to match that of DQ and DQS balls. DM[3:0] is DM for each of the four data bytes, respectively. A separate DM[3:0] is provided for each channel (A and B).                                                           |

| ODT_B, ODT_A                                                                             | Input     | <b>On-die termination:</b> Enables and disables termination on the DRAM DQ bus according to the specified mode register settings. For packages that do not support ODT, the ODT signal may be grounded internally. A separate ODT provided for each channel (A and B).                                                                      |

| DQ[31:0]_B,<br>DQ[31:0]_A                                                                | I/O       | <b>Data input/output:</b> Bidirectional data bus. A separate DQ[11:0] is provided for each channel (A and B).                                                                                                                                                                                                                               |

| DQS[3:0]_t_B,<br>DQS[3:0]_t_A,<br>DQS[3:0]_c_B,<br>DQS[3:0]_c_A                          | I/O       | <b>Data strobe:</b> Bidirectional (used for read and write data) and complementary (DQS_t and DQS_c). It is edge-aligned output with read data and centered input with write data. DQS[3:0]_t/DQS[3:0]_c is DQS for each of the four data bytes, respectively. A separate DQS[3:0]_t and DQS[3:0]_c is provided for each channel (A and B). |

| V <sub>DDQ</sub>                                                                         | Supply    | DQ power supply: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                           |

| V <sub>SSQ</sub>                                                                         | Supply    | DQ ground: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                                 |

| V <sub>DDCA</sub>                                                                        | Supply    | Command/address power supply: Command/address power supply.                                                                                                                                                                                                                                                                                 |

| V <sub>SSCA</sub>                                                                        | Supply    | Command/address ground: Isolated on the die for improved noise immunity.                                                                                                                                                                                                                                                                    |

| V <sub>DD1</sub>                                                                         | Supply    | Core power: Supply 1.                                                                                                                                                                                                                                                                                                                       |

| V <sub>DD2</sub>                                                                         | Supply    | Core power: Supply 2.                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub>                                                                          | Supply    | Common ground.                                                                                                                                                                                                                                                                                                                              |

| V <sub>REFCA</sub> B, V <sub>REFCA</sub> A<br>V <sub>REFDQ</sub> B, V <sub>REFDQ</sub> A | Supply    | <b>Reference voltage:</b> $V_{REFCA}$ is reference for command/address input buffers, $V_{REFDQ}$ is reference for DQ input buffers. A separate $V_{REFCA}$ and $V_{REFDQ}$ provided for each channel (A and B).                                                                                                                            |

| ZQ_B, ZQ_A                                                                               | Reference | <b>External reference ball for output drive calibration:</b> This ball is tied to an external 240 $\Omega$ resistor (RZQ), which is tied to V <sub>SSQ</sub> . A separate ZQ is provided for each channel (A and B).                                                                                                                        |

## 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3 SDRAM Ball Descriptions

| Symbol | Туре | escription                                                                                                        |  |

|--------|------|-------------------------------------------------------------------------------------------------------------------|--|

| DNU    | -    | o not use: Must be grounded or left floating.                                                                     |  |

| NC     | -    | No connect: Not internally connected.                                                                             |  |

| (NC)   |      | <b>No connect:</b> Balls indicated as (NC) are no connects; however, they could be connected together internally. |  |

#### Table 4: Ball/Pad Descriptions (Continued)

#### 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3 SDRAM Package Block Diagrams

## Package Block Diagrams

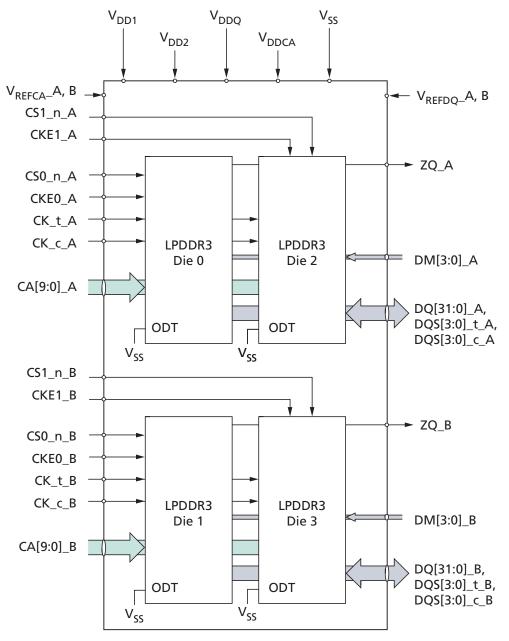

#### Figure 4: Dual-Die, Dual-Channel Package Block Diagram

### 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3 SDRAM Package Block Diagrams

#### Figure 5: Quad-Die, Dual-Channel Package Block Diagram

Note: 1. The ODT input is connected to rank 0. The ODT input to rank 1 is connected to V<sub>SS</sub> in the package.

## **Package Dimensions**

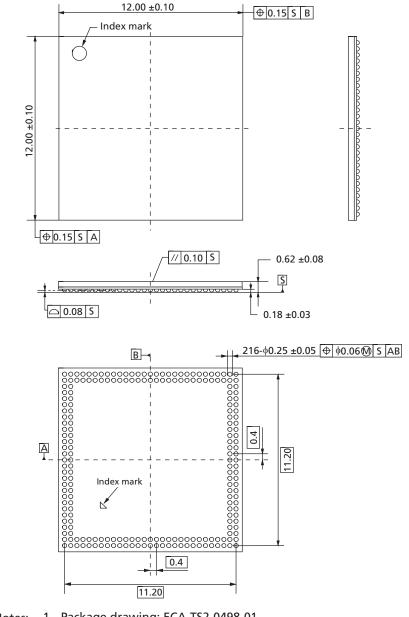

#### Figure 6: 216-Ball FBGA (12mm x 12mm) – EDF8164A3PK

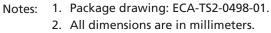

#### Figure 7: 216-Ball FBGA (12mm x 12mm) – EDFA164A2PK

Notes:1. Package drawing: ECA-TS2-0499-01.2. All dimensions are in millimeters.

## MR0, MR5-MR8 Readout

#### **Table 5: Mode Register Contents**

| Mode Register | OP7                         | OP6                                                                                                | OP5 | OP4 | OP3 | OP2 | OP1 | OP0   |  |  |

|---------------|-----------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-------|--|--|

| MR0           |                             | OP6 = 1b indicates support for WL set B<br>OP7 = 1b indicates that the option for RL3 is supported |     |     |     |     |     |       |  |  |

|               |                             | OP6 and OP7 =1b for this package                                                                   |     |     |     |     |     |       |  |  |

| MR5           |                             | Manufacturer ID = 0000 0011b                                                                       |     |     |     |     |     |       |  |  |

| MR6           |                             | Revision ID1 = 0000 0010b: Revision C                                                              |     |     |     |     |     |       |  |  |

| MR7           |                             | Revision ID2 = (RFU)                                                                               |     |     |     |     |     |       |  |  |

| MR8           | I/O Width Density Type      |                                                                                                    |     |     |     |     | ре  |       |  |  |

|               | 00b: x32 0110b: 4Gb 11b: 58 |                                                                                                    |     |     |     |     |     | : \$8 |  |  |

Note: 1. The contents of MR0 and MR5–MR8 will reflect the manufacturer ID, die revision, and interface configurations for each die for each package.

## I<sub>DD</sub> Specifications – Dual Die, Dual Channel

#### Table 6: I<sub>DD</sub> Specifications

$V_{DD2}$ ,  $V_{DDQ}$ ,  $V_{DDCA}$  = 1.14–1.30V;  $V_{DD1}$  = 1.70–1.95V;  $T_{C}$  = -30°C to +85°C

|                        |                                      | Speed |      |      |                                                                                                                                      |  |  |

|------------------------|--------------------------------------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                 | Supply                               | 1600  | 1333 | Unit | Parameter/Condition                                                                                                                  |  |  |

| I <sub>DD01</sub>      | V <sub>DD1</sub>                     | 12    | 12   | mA   | All devices in operating one bank active-precharge                                                                                   |  |  |

| I <sub>DD02</sub>      | V <sub>DD2</sub>                     | 60    | 60   | 1    | <sup>t</sup> CK = <sup>t</sup> CK(avg) MIN; <sup>t</sup> RC = <sup>t</sup> RC (MIN); CKE is HIGH; CS_                                |  |  |

| I <sub>DD0,in</sub>    | V <sub>DDCA</sub> + V <sub>DDQ</sub> | 12    | 12   |      | is HIGH between valid commands;<br>CA bus inputs are SWITCHING;                                                                      |  |  |

|                        |                                      |       |      |      | Data bus inputs are STABLE                                                                                                           |  |  |

| I <sub>DD2P1</sub>     | V <sub>DD1</sub>                     | 0.8   | 0.8  | mA   | All devices in idle power-down standby current                                                                                       |  |  |

| I <sub>DD2P2</sub>     | V <sub>DD2</sub>                     | 1.8   | 1.8  | ]    | <sup>t</sup> CK = <sup>t</sup> CK(avg) MIN; CKE is LOW; CS_n is HIGH;                                                                |  |  |

| I <sub>DD2P,in</sub>   | $V_{DDCA} + V_{DDQ}$                 | 0.2   | 0.2  |      | All banks are idle; CA bus inputs are SWITCHING;<br>Data bus inputs are STABLE                                                       |  |  |

| I <sub>DD2PS1</sub>    | V <sub>DD1</sub>                     | 0.8   | 0.8  | mA   | All devices in idle power-down standby current with                                                                                  |  |  |

| I <sub>DD2PS2</sub>    | V <sub>DD2</sub>                     | 1.8   | 1.8  | 1    | clock stop                                                                                                                           |  |  |

| I <sub>DD2PS,in</sub>  | V <sub>DDCA</sub> + V <sub>DDQ</sub> | 0.2   | 0.2  |      | CK_t = LOW, CK_c = HIGH; CKE is LOW;<br>CS_n is HIGH; All banks are idle;<br>CA bus inputs are STABLE;<br>Data bus inputs are STABLE |  |  |

| I <sub>DD2N1</sub>     | V <sub>DD1</sub>                     | 0.8   | 0.8  | mA   | All devices in idle non power-down standby current                                                                                   |  |  |

| I <sub>DD2N2</sub>     | V <sub>DD2</sub>                     | 23    | 22   | 1    | <sup>t</sup> CK = <sup>t</sup> CK(avg) MIN; CKE is HIGH;                                                                             |  |  |

| I <sub>DD2N,in</sub>   | V <sub>DDCA</sub> + V <sub>DDQ</sub> | 12    | 12   |      | CS_n is HIGH; All banks are idle;<br>CA bus inputs are SWITCHING;<br>Data bus inputs are STABLE                                      |  |  |

| I <sub>DD2NS1</sub>    | V <sub>DD1</sub>                     | 0.8   | 0.8  | mA   | All devices in idle non power-down standby current                                                                                   |  |  |

| I <sub>DD2NS2</sub>    | V <sub>DD2</sub>                     | 19    | 19   | 1    | with clock stop                                                                                                                      |  |  |

| I <sub>DD2NS,in</sub>  | V <sub>DDCA</sub> + V <sub>DDQ</sub> | 12    | 12   | 1    | CK_t = LOW, CK_c = HIGH; CKE is HIGH;<br>CS_n is HIGH; All banks are idle;                                                           |  |  |

|                        |                                      |       |      |      | CA bus inputs are STABLE;<br>Data bus inputs are STABLE                                                                              |  |  |

| I <sub>DD3P1</sub>     | V <sub>DD1</sub>                     | 1.4   | 1.4  | mA   | All devices in active power-down standby current                                                                                     |  |  |

| I <sub>DD3P2</sub>     | V <sub>DD2</sub>                     | 10    | 10   | 1    | <sup>t</sup> CK = <sup>t</sup> CK(avg) MIN; CKE is LOW;                                                                              |  |  |

| I <sub>DD3P,in</sub>   | V <sub>DDCA</sub> + V <sub>DDQ</sub> | 0.2   | 0.2  |      | CS_n is HIGH; One bank is active;<br>CA bus inputs are SWITCHING;<br>Data bus inputs are STABLE                                      |  |  |

| I <sub>DD3PS1</sub>    | V <sub>DD1</sub>                     | 1.4   | 1.4  | mA   | All devices in active power-down standby current with                                                                                |  |  |

| I <sub>DD3PS2</sub>    | V <sub>DD2</sub>                     | 10    | 10   | ]    | clock stop                                                                                                                           |  |  |

| I <sub>DD3PS</sub> ,in | V <sub>DDCA</sub> + V <sub>DDQ</sub> | 0.2   | 0.2  |      | CK_t = LOW, CK_c = HIGH; CKE is LOW;<br>CS_n is HIGH; One bank is active;<br>CA bus inputs are STABLE;<br>Data bus inputs are STABLE |  |  |

| I <sub>DD3N1</sub>     | V <sub>DD1</sub>                     | 2.0   | 2.0  | mA   | All devices in active non power-down standby current                                                                                 |  |  |

| I <sub>DD3N2</sub>     | V <sub>DD2</sub>                     | 25    | 24   | 1    | <sup>t</sup> CK = <sup>t</sup> CK(avg) MIN; CKE is HIGH;                                                                             |  |  |

| I <sub>DD3N,in</sub>   | V <sub>DDCA</sub> + V <sub>DDQ</sub> | 12    | 12   | 1    | CS_n is HIGH; One bank is active;<br>CA bus inputs are SWITCHING;                                                                    |  |  |

|                        |                                      |       |      |      | Data bus inputs are STABLE                                                                                                           |  |  |

## 8Gb, 16Gb: 216-Ball, Dual-Channel Embedded LPDDR3 SDRAM I<sub>DD</sub> Specifications – Dual Die, Dual Channel

#### Table 6: I<sub>DD</sub> Specifications (Continued)

|                        |                                      | Speed |      |      | +85°C                                                                                                                                 |  |

|------------------------|--------------------------------------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                 | Supply                               | 1600  | 1333 | Unit | Parameter/Condition                                                                                                                   |  |