Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **Product Description**

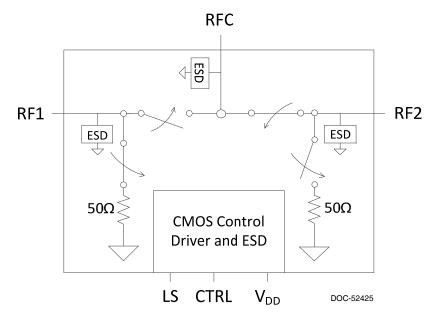

The PE42423 is a HaRP™ technology-enhanced absorptive 50Ω SPDT RF switch designed for use in high power and high performance WLAN 802.11 a/b/g/n/ac applications such as carrier and enterprise Wi-Fi Products, supporting bandwidths up to 6 GHz.

This switch features high linearity which remains invariant across the full supply range. PE42423 also features exceptional isolation, high power handling and is offered in a 16-lead 3x3 mm QFN package. In addition, no external blocking capacitors are required if 0V DC is present on the RF ports.

The PE42423 is manufactured on Peregrine's UltraCMOS® process, a patented variation of silicon-on-insulator (SOI) technology on a sapphire substrate.

Peregrine's HaRP™ technology enhancements deliver high linearity and excellent harmonics performance. It is an innovative feature of the UltraCMOS® process, offering the performance of GaAs with the economy and integration of conventional CMOS.

Figure 1. Functional Diagram

# **Product Specification**

## PE42423

# UltraCMOS® SPDT RF Switch 100 MHz - 6 GHz

#### **Features**

- 802.11 a/b/g/n/ac support

- Wide supply range of 2.3V to 5.5V

- +1.8V control logic compatible

- Exceptional isolation

- 47 dB @ 2.4 GHz

- 43 dB @ 6.0 GHz

- High linearity across supply range

- IIP3 of 65 dBm

- IIP2 of 120 dBm

- High power handling

- 38.5 dBm @ 2.4 GHz

- 37.0 dBm @ 6.0 GHz

- Fast switching time of 500 ns

- ESD performance

- 3kV HBM on RF pins to GND

- 1.5kV HBM on all pins

- 1kV CDM on all pins

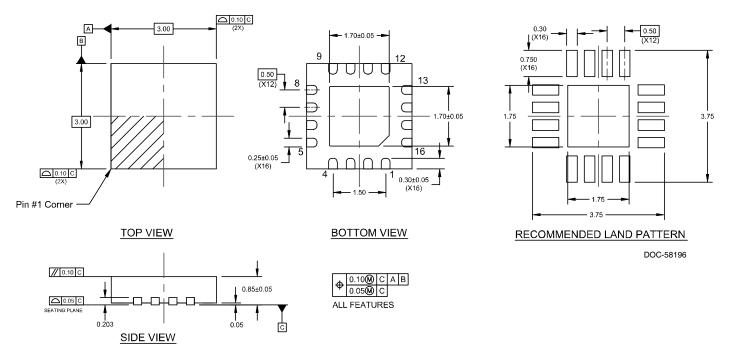

Figure 2. Package Type

16-lead 3x3 mm QFN

Table 1. Electrical Specifications Temp = 25°C, V<sub>DD</sub> = 3.3V

| Parameter                                   | Path    | Condition                                 | Min            | Тур                  | Max               | Unit           |

|---------------------------------------------|---------|-------------------------------------------|----------------|----------------------|-------------------|----------------|

| Operational frequency                       |         |                                           | 0.1            |                      | 6                 | GHz            |

| Insertion loss                              | RFC-RFX | 0.1–2.4 GHz<br>2.4–5.8 GHz<br>5.8–6.0 GHz |                | 0.80<br>0.95<br>0.95 | 1.0<br>1.1<br>1.1 | dB<br>dB<br>dB |

| Isolation                                   | RFX-RFX | 0.1–2.4 GHz<br>2.4–5.8 GHz<br>5.8–6.0 GHz | 49<br>39<br>39 | 51<br>41<br>41       |                   | dB<br>dB<br>dB |

| Isolation                                   | RFC-RFX | 0.1–2.4 GHz<br>2.4–5.8 GHz<br>5.8–6.0 GHz | 44<br>39<br>40 | 47<br>41<br>43       |                   | dB<br>dB<br>dB |

| Return loss<br>(common and active port)     | RFX     | 0.1–2.4 GHz<br>2.4–5.8 GHz<br>5.8–6.0 GHz |                | 19<br>16<br>16       |                   | dB<br>dB<br>dB |

| Return loss (terminated port)               | RFX     | 0.1–2.4 GHz<br>2.4–5.8 GHz<br>5.8–6.0 GHz |                | 23<br>23<br>24       |                   | dB<br>dB<br>dB |

| Input 0.1 dB compression point <sup>1</sup> | RFC-RFX | 0.6–4.0 GHz                               |                | 39.5                 |                   | dBm            |

| Input IP3 <sup>2</sup>                      | RFC-RFX | 0.8–2.7 GHz                               |                | 65                   |                   | dBm            |

| Input IP2 <sup>2</sup>                      | RFC-RFX | 0.8–2.7 GHz                               |                | 120                  |                   | dBm            |

| Switching time                              |         | 50% CTRL to 90% or 10% of final value     |                | 500                  | 700               | ns             |

1. The input 0.1dB compression point is a linearity figure of merit. Refer to *Table 3* for the operating RF input power (50 $\Omega$ ) 2. The input intercept point remains invariant over the full supply range as defined in *Table 3*

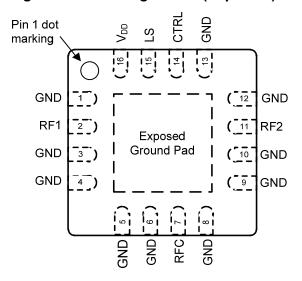

Figure 3. Pin Configuration (Top View)

**Table 2. Pin Descriptions**

| Pin #                                 | Pin Name         | Description                                                                            |

|---------------------------------------|------------------|----------------------------------------------------------------------------------------|

| 1, 3, 4, 5,<br>6, 8, 9, 10,<br>12, 13 | GND              | Ground                                                                                 |

| 2                                     | RF1 <sup>1</sup> | RF port 1                                                                              |

| 7                                     | RFC <sup>1</sup> | RF common                                                                              |

| 11                                    | RF2 <sup>1</sup> | RF port 2                                                                              |

| 14                                    | CTRL             | Digital control logic input                                                            |

| 15                                    | LS               | Logic Select - used to determine the definition for the CTRL pin (see <i>Table 5</i> ) |

| 16                                    | $V_{DD}$         | Supply voltage (nominal 3.3V)                                                          |

| Pad                                   | GND              | Exposed pad: ground for proper operation                                               |

Note 1: RF pins 2, 7 and 11 must be at 0V DC. The RF pins do not require DC blocking capacitors for proper operation if the 0V DC requirement is

**Table 3. Operating Ranges**

| Parameter                                                                        | Symbol                  | Min  | Тур | Max                    | Unit              |

|----------------------------------------------------------------------------------|-------------------------|------|-----|------------------------|-------------------|

| Supply voltage                                                                   | $V_{DD}$                | 2.3  |     | 5.5                    | V                 |

| Supply current                                                                   | I <sub>DD</sub>         |      | 120 | 200                    | μΑ                |

| Digital input high (CTRL)                                                        | V <sub>IH</sub>         | 1.17 |     | 3.6                    | ٧                 |

| Digital input low (CTRL)                                                         | V <sub>IL</sub>         | -0.3 |     | 0.6                    | ٧                 |

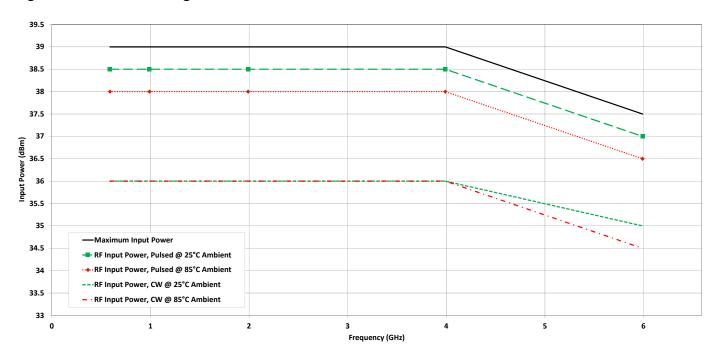

| RF input power, CW<br>0.1–0.6 GHz<br>0.6–4.0 GHz<br>4.0–6.0 GHz                  | P <sub>MAX,CW</sub>     |      |     | 32<br>36<br>Fig. 4     | dBm<br>dBm<br>dBm |

| RF input power, pulsed <sup>1</sup><br>0.1–0.6 GHz<br>0.6–4.0 GHz<br>4.0–6.0 GHz | P <sub>MAX,PULSED</sub> |      |     | 32<br>Fig. 4<br>Fig. 4 | dBm<br>dBm<br>dBm |

| RF input power into terminated ports, CW                                         | P <sub>MAX,TERM</sub>   |      |     | 26                     | dBm               |

| Operating temperature range                                                      | T <sub>OP</sub>         | -40  | +25 | +85                    | °C                |

Note 1: Pulsed, 5% duty cycle of 4620  $\mu s$  period,  $50\Omega$

**Table 4. Absolute Maximum Ratings**

| Parameter/Condition                                              | Symbol               | Min  | Max                | Unit              |

|------------------------------------------------------------------|----------------------|------|--------------------|-------------------|

| Supply voltage                                                   | $V_{DD}$             | -0.3 | 5.5                | V                 |

| Digital input voltage (CTRL)                                     | V <sub>CTRL</sub>    | -0.3 | 3.6                | V                 |

| LS input voltage                                                 | V <sub>LS</sub>      | -0.3 | 3.6                | V                 |

| Maximum input power<br>0.1–0.6 GHz<br>0.6–4.0 GHz<br>4.0–6.0 GHz | P <sub>MAX,ABS</sub> |      | 32<br>39<br>Fig. 4 | dBm<br>dBm<br>dBm |

| Storage temperature range                                        | T <sub>ST</sub>      | -65  | +150               | Ô                 |

| ESD voltage HBM <sup>1</sup> RF pins to GND All pins             | V <sub>ESD,HBM</sub> |      | 3000<br>1500       | V<br>V            |

| ESD voltage MM <sup>2</sup> , all pins                           | $V_{ESD,MM}$         |      | 200                | V                 |

| ESD voltage CDM <sup>3</sup> , all pins                          | V <sub>ESD,CDM</sub> |      | 1000               | V                 |

s: 1. Human Body Model (MIL-STD 883 Method 3015)

2. Machine Model (JEDEC JESD22-A115)

3. Charged Device Model (JEDEC JESD22-C101)

Exceeding absolute maximum ratings may cause permanent damage. Operation should be restricted to the limits in the Operating Ranges table. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS® device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rating specified.

#### Latch-Up Avoidance

Unlike conventional CMOS devices, UltraCMOS<sup>®</sup> devices are immune to latch-up.

#### **Switching Frequency**

The PE42423 has a maximum 25 kHz switching rate. Switching frequency describes the time duration between switching events. Switching time is the time duration between the point the control signal reaches 50% of the final value and the point the output signal reaches within 10% or 90% of its target value.

**Table 5. Control Logic Truth Table**

| LS | CTRL | RFC-RF1 | RFC-RF2 |

|----|------|---------|---------|

| 0  | 0    | off     | on      |

| 0  | 1    | on      | off     |

| 1  | 0    | on      | off     |

| 1  | 1    | off     | on      |

#### **Moisture Sensitivity Level**

The Moisture Sensitivity Level rating for the PE42423 in the 16-lead 3x3 mm QFN package is MSL3.

#### Logic Select (LS)

The Logic Select feature is used to determine the definition for the CTRL pin.

Figure 4. Power De-rating Curve for 600 MHz - 6 GHz

## Typical Performance Data @ $25^{\circ}$ C and $V_{DD} = 3.3V$ unless otherwise specified

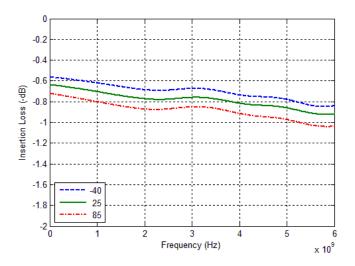

Figure 5. Insertion Loss vs. Temp (RFC-RFX)

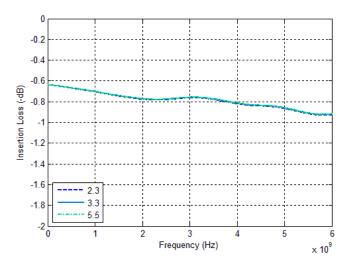

Figure 6. Insertion Loss vs. V<sub>DD</sub> (RFC–RFX)

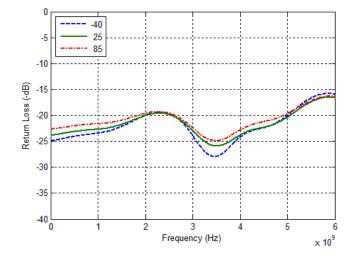

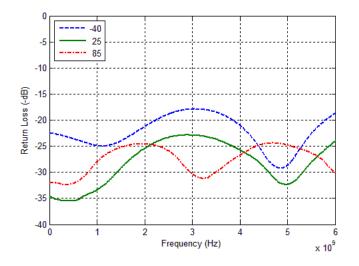

Figure 7. RFX Port Return Loss vs. Temp (RFX Active)

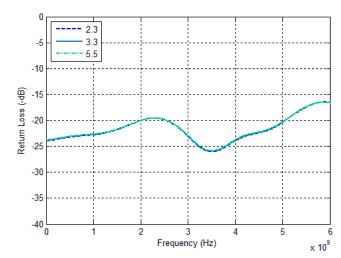

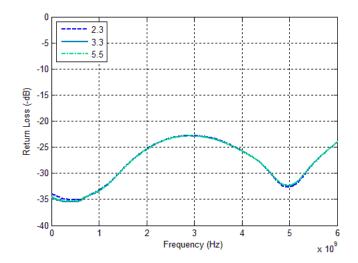

Figure 8. RFX Port Return Loss vs.  $V_{DD}$  (RFX Active)

## Typical Performance Data @ $25^{\circ}$ C and $V_{DD} = 3.3V$ unless otherwise specified

Figure 9. Terminated Port Return Loss vs. Temp (RFX Active)

Figure 10. Terminated Port Return Loss vs. V<sub>DD</sub> (RFX Active)

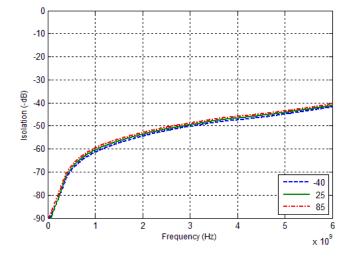

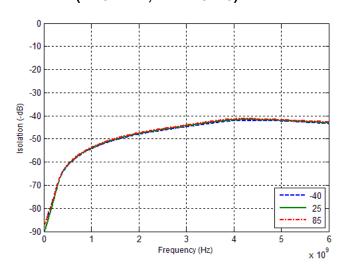

Figure 11. Isolation vs. Temp (RFX-RFX, RFX Active)

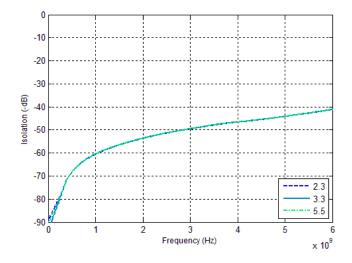

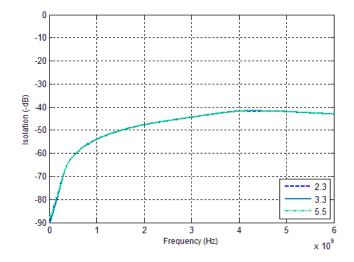

Figure 12. Isolation vs. V<sub>DD</sub> (RFX–RFX, RFX Active)

## Typical Performance Data @ $25^{\circ}$ C and $V_{DD} = 3.3V$ unless otherwise specified

Figure 13. Isolation vs. Temp (RFC-RFX, RFX Active)

Figure 14. Isolation vs. V<sub>DD</sub> (RFC–RFX, RFX Active)

#### **Evaluation Kit**

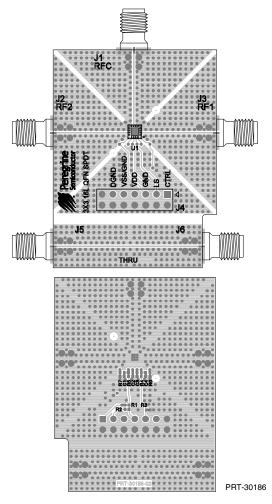

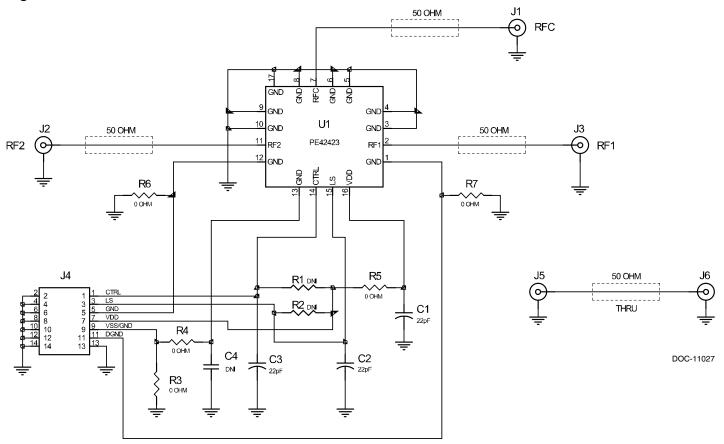

The SPDT switch evaluation board was designed to ease customer evaluation of Peregrine's PE42423. The RF common port is connected through a  $50\Omega$  transmission line via the SMA connector, J1. RF1 and RF2 ports are connected through  $50\Omega$  transmission lines via SMA connectors J2 and J3, respectively. A  $50\Omega$  through transmission line is available via SMA connectors J5 and J6, which can be used to de-embed the loss of the PCB. J4 provides DC and digital inputs to the device.

For the true performance of the PE42423 to be realized, the PCB should be designed in such a way that RF transmission lines and sensitive DC I/O traces are heavily isolated from one another.

Figure 15. Evaluation Kit Layout

Figure 16. Evaluation Board Schematic

Notes: 1. Use PRT-30186-2 PCB

2. CAUTION: Contains parts and assemblies susceptible to damage by electrostatic discharge (ESD)

## Figure 17. Package Drawing

16-lead 3x3 mm QFN

Figure 18. Top Marking Specifications

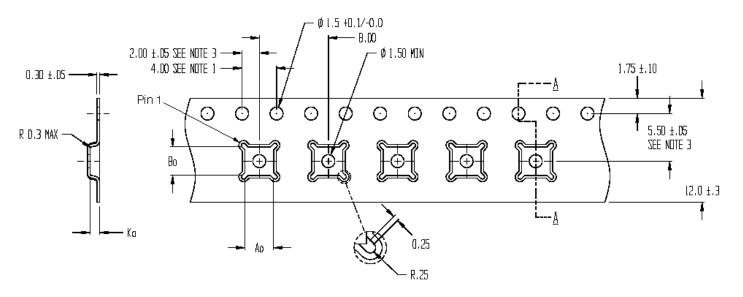

#### Figure 19. Tape and Reel Specifications

SECTION A - A

Notes: 1. 10 sprocket hole pitch cumulative tolerance ±0.2

2. Camber in compliance with EIA 481

3. Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole

Ao = 3.30 Bo = 3.30Ko = 1.10

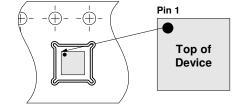

Device Orientation in Tape

**Table 6. Ordering Information**

| Order Code    | Description Package    |                          | Shipping Method |  |

|---------------|------------------------|--------------------------|-----------------|--|

| PE42423MLBA-Z | PE42423 SPDT RF switch | Green 16-lead 3x3 mm QFN | 3000 units/T&R  |  |

| EK42423-02    | PE42423 Evaluation kit | Evaluation kit           | 1/Box           |  |

#### **Sales Contact and Information**

For sales and contact information please visit www.psemi.com.

Advance Information: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. Preliminary Specification: The datasheet contains preliminary data. Additional data may be added at a later data. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product. Product Specification: The datasheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by Issuing a CNF (Customer Notification Form).

The information in this datasheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this datasheet are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo, UltraCMOS and UTSi are registered trademarks and HaRP, MultiSwitch and DuNE

The Peregrine name, logo, UltraCMOS and UTSi are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp. Peregrine products are protected under one or more of the following U.S. Patents: <a href="http://patents.psemi.com">http://patents.psemi.com</a>.