Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PE46120 Evaluation Kit (EVK) User's Manual

Monolithic Phase & Amplitude Controller, 1.7–2.2 GHz

## Copyright and Trademarks

©2015, Peregrine Semiconductor Corporation. All rights reserved. The Peregrine name, logo, UTSi and UltraCMOS are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp.

### **Disclaimers**

The information in this document is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

### **Patent Statement**

Peregrine products are protected under one or more of the following U.S. patents: patents.psemi.com

### **Sales Contact**

For additional information, contact Sales at sales@psemi.com.

# **Corporate Headquarters**

9369 Carroll Park Drive, San Diego, CA, 92121 858-731-9400

# **Table of Contents**

| Introduction                             | 1  |

|------------------------------------------|----|

| Introduction                             | 1  |

| Application Support                      |    |

| Evaluation Kit Contents and Requirements |    |

| Software Requirements                    |    |

| Evaluation Board Assembly                | 3  |

| Evaluation Board Assembly Overview       | 3  |

| Quick Start Guide                        | 5  |

| Quick Start Overview                     |    |

| Software Installation                    |    |

| USB Driver                               |    |

| EVK Software                             |    |

| Hardware Configuration                   |    |

| USB Interface Board Overview             |    |

| Hardware Operation                       |    |

| Using the Graphical User Interface       | 15 |

| Continuous Pattern Loop                  |    |

| Send Signal                              |    |

| Technical Resources                      | 19 |

| Technical Resources                      |    |

|                                          |    |

| Document Categories                      |    |

This page intentionally left blank.

# Introduction

1

#### Introduction

The PE46120 is a HaRP™ technology-enhanced monolithic phase and amplitude controller (MPAC) designed for precise phase and amplitude control of two independent RF paths. It optimizes system performance while reducing manufacturing costs of transmitters that use symmetric or asymmetric power amplifier designs to efficiently process signals with large peak-to-average ratios.

This monolithic RFIC integrates a 90° RF splitter, digital phase shifters and a digital step attenuator along with a low voltage CMOS serial interface. It can cover a phase range of 87.2° in 2.8° steps and an attenuation range of 7.5 dB in 0.5 dB steps, while providing excellent phase and amplitude accuracy from 1.8–2.2 GHz.

The PE46120 also features exceptional linearity, high output port-to-port isolation and extremely low power consumption relative to competing module solutions. It is offered in a 32-lead 6 × 6 mm QFN package.

The PE46120 evaluation kit (EVK) includes hardware required to control and evaluate the functionality of the MPAC. The MPAC evaluation software can be downloaded at www.psemi.com and requires a PC running Windows® operating system to control the USB interface board.

## **Application Support**

For any technical inquiries regarding the evaluation kit or software, please visit applications support at www.psemi.com (fastest response) or call (858) 731-9400.

## **Evaluation Kit Contents and Requirements**

#### **Kit Contents**

The PE46120 EVK includes the following hardware required to evaluate the MPAC.

Table 1 • PE46120 Evaluation Kit Contents

| Quality | Description                                        |

|---------|----------------------------------------------------|

| 1       | PE46120 MPAC evaluation board assembly (PRT-55151) |

| 1       | Peregrine USB interface board assembly (PRT-50866) |

| 1       | USB 2.0 Type A to Type B mini cable                |

### Software Requirements

The MPAC evaluation software will need to be installed on a computer with the following minimum requirements:

- PC compatible with Windows™ XP, Vista, 7 or 8

- · Mouse or other pointing device

- · USB port

- · HTML browser with internet access

- · Administrative privileges

#### Hardware Requirements

In order to evaluate the performance of the evaluation board, a Vector network analyzer is required.

**Caution:** The PE46120 MPAC EVK contains components that might be damaged by exposure to voltages in excess of the specified voltage, including voltages produced by electrostatic discharges. Handle the board in accordance with procedures for handling static-sensitive components. Avoid applying excessive voltages to the power supply terminals or signal inputs or outputs.

# **Evaluation Board Assembly**

2

# **Evaluation Board Assembly Overview**

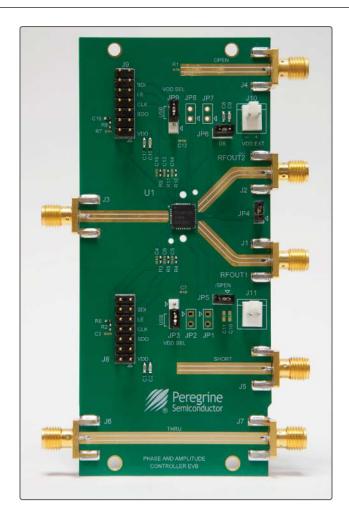

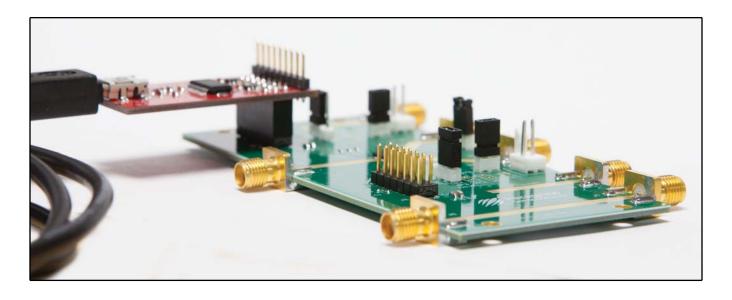

The evaluation board (EVB) is assembled with a PE46120, several headers and SMA connectors, as shown in **Figure 1**.

Figure 1 • PE46120 Evaluation Board Assembly

This page intentionally left blank.

# **Quick Start Guide**

3

### **Quick Start Overview**

The EVB was designed to ease customer evaluation of the PE46120 MPAC. This chapter will guide the user through the software installation, hardware configuration and using the graphical user interface (GUI).

### **Software Installation**

#### **USB Driver**

The latest USB interface board drivers are available via Microsoft Windows update. Internet connectivity is required to download the drivers. Connect the USB interface board to the PC and select the Windows Update option to obtain and install the drivers (Figure 2).

If the USB board drivers are not installed, it will not be possible to complete the installation of the MPAC EVK software. A USB interface board (Figure 11) is included in the evaluation kit.

Figure 2 • USB Driver Installation (Detecting)

#### **EVK Software**

In order to evaluate the PE46120 performance, the application software has to be installed on your

computer. The USB interface and MPAC application software is compatible with computers running Windows<sup>®</sup>, XP, Vista, 7, 8, in 32- or 64-bit configurations. This software is available directly from Peregrine's website at www.psemi.com.

To install the MPAC evaluation software, unzip the archive and execute the "setup.exe" (Figure 3).

Figure 3 • MPAC Evaluation Software Installer

After the setup.exe file has been executed, a welcome screen will appear. It is strongly recommended that all programs be closed prior to running the install program. Click the "Next>" button to proceed.

Figure 4 • MPAC Evaluation Software Setup

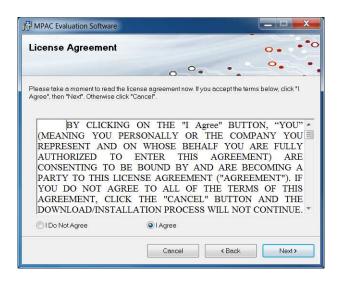

Take a moment to read the license agreement, then click "I Agree" and "Next>"

Figure 5 • License Agreement

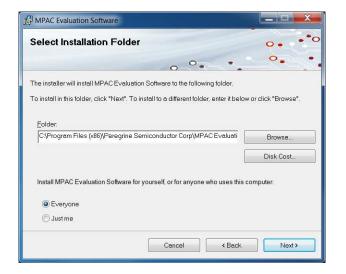

For most users the default install location for the program files is sufficient. If a different location is desired, the install program can be directed to place the program files in an alternate location. The software is installed for "Everyone" by default. Once the desired location is selected click "Next>."

Figure 6 • Select Installer Folder

Page 6

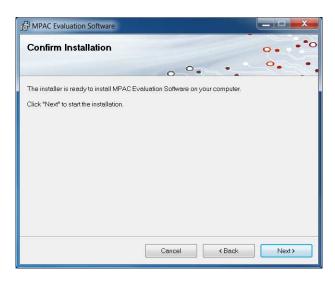

In the window of Confirm Installation, click "Next>" to proceed with the software installation.

Figure 7 • Confirm Installation

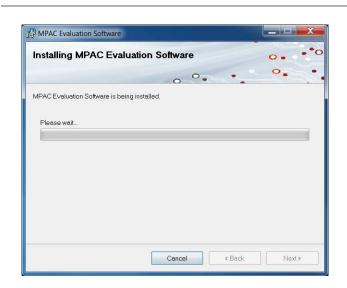

As the software files are installed, a progress indicator will be displayed. On slower computers, installation of the software may proceed for a few moments.

Figure 8 • Progress Indicator

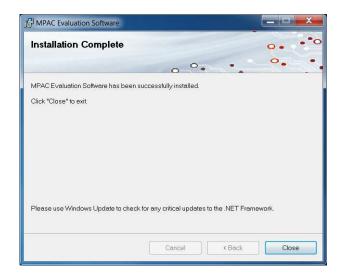

Once the evaluation software is installed, click "Close" to exit.

Figure 9 • Installation Complete

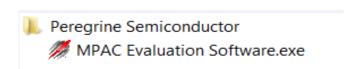

A new Start Menu item under Peregrine Semiconductor will appear in the start menu of your computer. Select "MPAC Evaluation Software" to launch the GUI.

Figure 10 • MPAC Evaluation Software Launch

# **Hardware Configuration**

#### **USB Interface Board Overview**

The USB interface board (**Figure 11**) is included in the evaluation kit. This board allows the user to send serial peripheral interface (SPI) commands to the device under test by using a PC running the Windows<sup>®</sup> operating system. To install the software, extract the zip file to a temporary directory and follow the installation procedure included.

Figure 11 • USB Interface Board

#### Connection of the USB Interface Board to the Evaluation Board

The EVB and the USB interface board contain a 14 pin header. This feature allows the USB interface board (socket) to connect directly to the EVB (pin) on the front side as show in **Figure 12**. Use caution when making the connection to insure the USB interface board is aligned and connected to both rows of pins properly.

Figure 12 • USB Interface Board Connected to the Evaluation Board

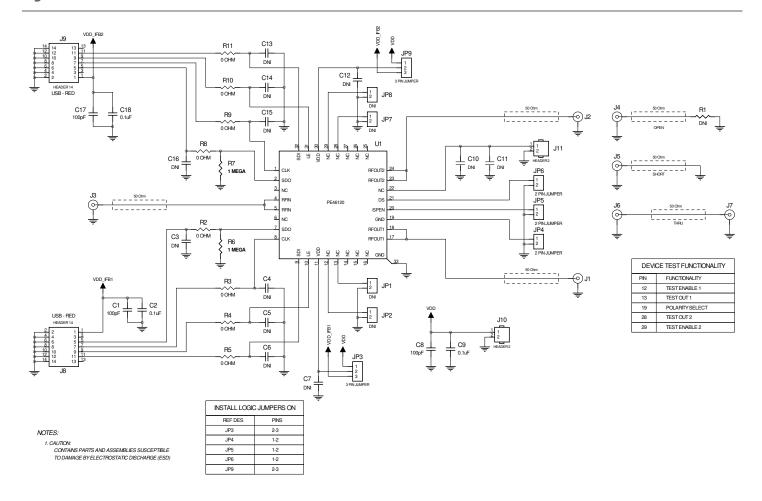

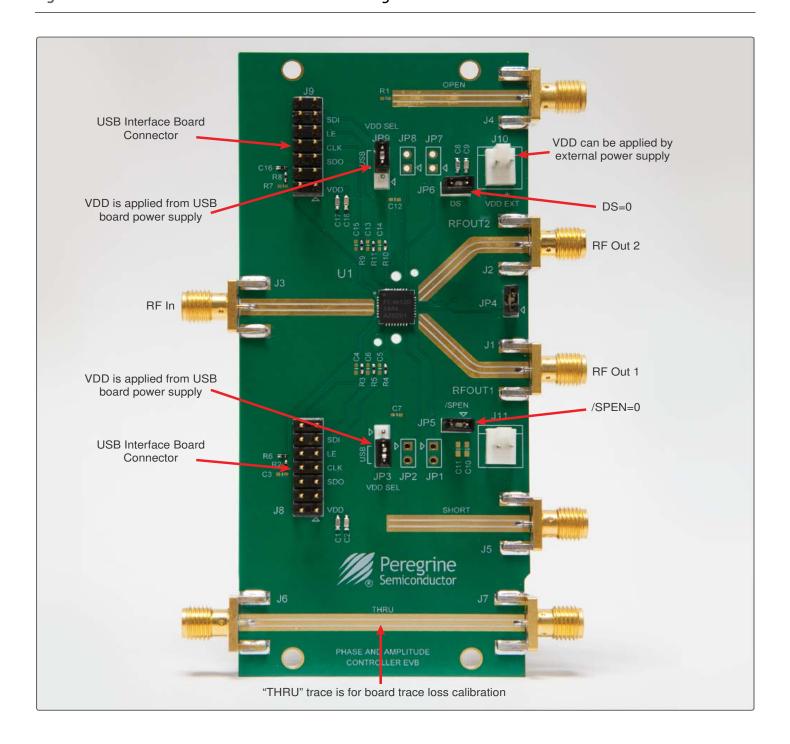

#### **Evaluation Board Overview**

The evaluation board is designed to ease customer evaluation of Peregrine's products. The board contains:

- 1) Digital signal connectors are provided for power supply, digital control signals and USB interface board.

- 2) SMA connectors are provided for RF performance verification and THRU trace to calibrate board trace loss.

The schematic and evaluation board outline are provided in this user manual.

Figure 13 • PE46120 Evaluation Board Schematic

Figure 14 • PE46120 Evaluation Board Outline Showing Functional Overview

### **Hardware Operation**

The general guidelines for operating the hardware evaluation board are listed in this section. Follow the steps below to configure the hardware properly for the performance.

- 1) Connect the jumper on JP4, JP5 and JP6.

- a) JP4 is connected to PE46120 pin-19 (GND) to ground.

- b) JP5 is connected to PE46120 pin-20 (/SPEN) to ground for normal SPI operation. Refer to datasheet Table 11.

- c) JP6 is connected to PE46120 pin-21 (DS) to ground as DS = 0 setting. Refer to Table 6 and Table 7.

- 2) There are two options to provide PE46120 a power supply. They are:

- a) Option 1: Power up through USB interface board. Evaluation board is using this option by connecting jumper on JP3 pin 2–3 and jumper on JP9 pin 2–3; refer to Figure 14.

- b) Option 2: Power via external power supply. The evaluation board is configured for this option by installing a jumper on JP3 pins 1–2 and JP9 pins 1–2 (refer to **Figure 14**). Connect the external power supply to VDD EXT J10 or J11 (pin 1+, pin 2–).

- 3) Plug in USB interface board (Figure 11) on J8 or J9, as shown in Figure 12. J8 and J9 provide identical control to the device.

- 4) Calibrate board trace loss and phase with THRU trace between J6 and J7. THRU calibration is sufficient for initial measurements. If more accurate results are desired, the full set of SLOT standards can be used.

Table 2 • Recommended Operating Condition for PE46120

| Parameter                                      | Min  | Тур | Max  | Unit |

|------------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>DD</sub> <sup>(1)</sup> | 2.3  |     | 5.5  | V    |

| Supply current                                 |      | 350 | 500  | μΑ   |

| Digital input high                             | 1.17 |     | 3.6  | V    |

| Digital input low                              | 0    |     | 0.6  | V    |

| Digital input leakage                          |      | 10  | 20   | μΑ   |

| RF input power, CW                             |      |     | 29   | dBm  |

| RF input power, pulsed <sup>(2)</sup>          |      |     | 32   | dBm  |

| Operating temperature range                    | -40  | +25 | +105 | °C   |

|                                                |      |     |      |      |

#### Notes

- 1) Product performance does not vary over V<sub>DD</sub>.

- 2) Pulsed, 5% duty cycle of 4620 µs period.

### Table 3 • Bit Descriptions

| C0    | Channel register select                            |

|-------|----------------------------------------------------|

|       | C0 = L, channel RF <sub>OUT1</sub> register select |

|       | C0 = H, channel RF <sub>OUT2</sub> register select |

| M0-M3 | Attenuation setting per channel                    |

| P0-P4 | Phase shift setting per channel                    |

| S0-S3 | Spare bits                                         |

#### Table 4 • 14-bit Word

| Q13 | Q12 | Q11 | Q10 | <b>Q</b> 9 | Q8 | Q7  | Q6 | <b>Q</b> 5 | Q4   | Q3  | Q2  | Q1 | Q0 |

|-----|-----|-----|-----|------------|----|-----|----|------------|------|-----|-----|----|----|

| C0  | S3  | S2  | МЗ  | M2         | M1 | M0  | P4 | P3         | P2   | P1  | P0  | S1 | S0 |

| 1   | _   | _   | _   | _          | _  | _   | 45 | 22.5       | 11.2 | 5.6 | 2.8 | _  | _  |

| 2   | _   | _   | 4   | 2          | 1  | 0.5 | 45 | 22.5       | 11.2 | 5.6 | 2.8 | _  | _  |

# Table 5 • Serial Truth Table—Phase Setting

| Q13 | Q12 | Q11 | Q10 | Q9 | Q8 | Q7  | Q6 | Q5   | Q4   | Q3  | Q2  | Q1 | Q0 |                        |

|-----|-----|-----|-----|----|----|-----|----|------|------|-----|-----|----|----|------------------------|

| C0  | S3  | S2  | М3  | M2 | M1 | МО  | P4 | P3   | P2   | P1  | P0  | S1 | S0 | Phase Shift<br>Setting |

| 1/2 |     |     | 4   | 2  | 1  | 0.5 | 45 | 22.5 | 11.2 | 5.6 | 2.8 |    |    |                        |

| Х   | Х   | Х   | Х   | Х  | Х  | Х   | L  | L    | L    | L   | L   | Х  | Х  | Ref phase              |

| Х   | Х   | Х   | Х   | Х  | Х  | Х   | L  | L    | L    | L   | Н   | Х  | Х  | 2.8 deg                |

| Х   | Х   | Х   | Х   | Х  | Х  | Х   | L  | L    | L    | Н   | L   | Х  | Х  | 5.6 deg                |

| Х   | Х   | Х   | Х   | Х  | Х  | Х   | L  | L    | Н    | L   | L   | Х  | Х  | 11.25 deg              |

| Х   | Х   | Х   | Х   | Х  | Х  | Х   | L  | Н    | L    | L   | L   | Х  | Х  | 22.5 deg               |

| Х   | Х   | Х   | Х   | Х  | Х  | Х   | Н  | L    | L    | L   | L   | Х  | Х  | 45 deg                 |

| Х   | Х   | Х   | Х   | Х  | Х  | Х   | Н  | Н    | Н    | Н   | Н   | Х  | Х  | 87.2 deg               |

# Table 6 • Serial Truth Table—Attenuation Setting (RF<sub>OUT2</sub>)

| Q13 | Q12 | Q11 | Q10 | Q9 | Q8 | Q7  | Q6 | Q5         | Q4   | Q3  | Q2  | Q1 | Q0 |                    |

|-----|-----|-----|-----|----|----|-----|----|------------|------|-----|-----|----|----|--------------------|

| C0  | S3  | S2  | M3  | M2 | M1 | МО  | P4 | <b>P</b> 3 | P2   | P1  | P0  | S1 | S0 | Amplitude Setting  |

| 1   | _   | _   | _   | _  |    | _   | 45 | 22.5       | 11.2 | 5.6 | 2.8 | _  | _  | Ampilitude Setting |

| 2   | _   | _   | 4   | 2  | 1  | 0.5 | 45 | 22.5       | 11.2 | 5.6 | 2.8 | _  | _  |                    |

| Н   | Х   | Х   | L   | L  | L  | L   | Х  | Х          | Х    | Х   | Х   | Х  | Х  | Ref insertion loss |

| Н   | Х   | Х   | L   | L  | L  | Н   | Х  | Х          | Х    | Х   | Х   | Х  | Х  | 0.5 dB             |

| Н   | Х   | Х   | L   | L  | Н  | L   | Х  | Х          | Х    | Х   | Х   | Х  | Х  | 1 dB               |

| Н   | Х   | Х   | L   | Н  | L  | L   | Х  | Х          | Х    | Х   | Х   | Х  | Х  | 2 dB               |

| Н   | Х   | Х   | Н   | L  | L  | L   | Х  | Х          | Х    | Х   | Х   | Х  | Х  | 4 dB               |

| Н   | Х   | Х   | Н   | Н  | Н  | Н   | Х  | Х          | Х    | Х   | Х   | Х  | Х  | 7.5 dB             |

## Table 7 • Default State Settings at Power Up (RF<sub>OUT1</sub>)

|               | Q13 | Q12 | Q11 | Q10 | Q9 | Q8 | Q7  | Q6 | Q5   | Q4   | Q3  | Q2  | Q1 | Q0 | Default        |  |

|---------------|-----|-----|-----|-----|----|----|-----|----|------|------|-----|-----|----|----|----------------|--|

| DS<br>Setting | CO  | S3  | S2  | M3  | M2 | M1 | МО  | P4 | P3   | P2   | P1  | P0  | S1 | S0 | Setting at     |  |

|               | 1/2 |     |     | 4   | 2  | 1  | 0.5 | 45 | 22.5 | 11.2 | 5.6 | 2.8 |    |    | Power Up       |  |

| DS = 0        | _   | _   | _   | _   | _  | _  | _   | L  | L    | L    | L   | L   | _  | _  | 0 dB<br>0 deg  |  |

| DS = 1        | _   | _   | _   | _   | _  | _  | _   | Н  | L    | L    | L   | L   | _  | _  | 0 dB<br>45 deg |  |

# Table 8 • Default State Setting at Power Up ( $RF_{OUT2}$ )

|               | Q13 | Q12 | Q11 | Q10 | Q9 | Q8 | Q7  | Q6 | Q5   | Q4   | Q4  | Q3  | Q2 | Q1 | Default          |  |

|---------------|-----|-----|-----|-----|----|----|-----|----|------|------|-----|-----|----|----|------------------|--|

| DS<br>Setting | C0  | S3  | S2  | M3  | M2 | M1 | МО  | P4 | P3   | P2   | P1  | P0  | S1 | S0 | Setting at       |  |

|               | 1/2 | _   |     | 4   | 2  | 1  | 0.5 | 45 | 22.5 | 11.2 | 5.6 | 2.8 | _  | _  | Power Up         |  |

| DS = 0        | _   | _   | _   | L   | L  | L  | L   | L  | L    | L    | L   | L   | _  | _  | 0 dB<br>0 deg    |  |

| DS = 1        | _   | _   | _   | Н   | Н  | Н  | Н   | Н  | L    | L    | L   | L   | _  | _  | 7.5 dB<br>45 deg |  |

### Table 9 • Serial Interface Timing Characteristics(1)

| Parameter/Condition                                                                 | Min   | Max | Unit |

|-------------------------------------------------------------------------------------|-------|-----|------|

| Serial clock frequency, F <sub>CLK</sub> <sup>(2)</sup>                             | 0.032 | 26  | MHz  |

| Serial clock period, T <sub>SCLK</sub>                                              | 40    |     | ns   |

| Serial clock HIGH time, T <sub>SCLKH</sub>                                          | 20    |     | ns   |

| Serial clock LOW time, T <sub>SCLKL</sub>                                           | 20    |     | ns   |

| Serial data output propagation delay from CLK falling edge, T <sub>OV</sub> (10 pF) |       | 9   | ns   |

| Latch clock pulse width high, T <sub>LCLKH</sub>                                    | 10    |     | ns   |

| Serial data input setup time from CLK rising edge, T <sub>SU</sub>                  |       | 5   | ns   |

| Serial data input hold time from CLK rising edge, T <sub>H</sub>                    |       | 2   | ns   |

| Serial data output hold time from CLK rising edge, T <sub>OH</sub>                  | 1.6   |     | ns   |

| Serial clock rising edge setup time to latch clock rising edge, T <sub>SETTLE</sub> |       | 27  | ns   |

| SDO drive strength <sup>(3)</sup>                                                   |       | 15  | pF   |

#### Notes:

- 1)  $V_{DD}$  = 2.3V–5.5V, –40 °C <  $T_A$  < +1-5 °C, unless otherwise specified.

- 2) Limited by test duration not static logic design. Synchronous to clock. Minimum clock frequency tested = 32 kHz.

- 3) SDO maximum capacitive load drive strength for  $F_{CLK}$  = MHz with a 1.8V swing.

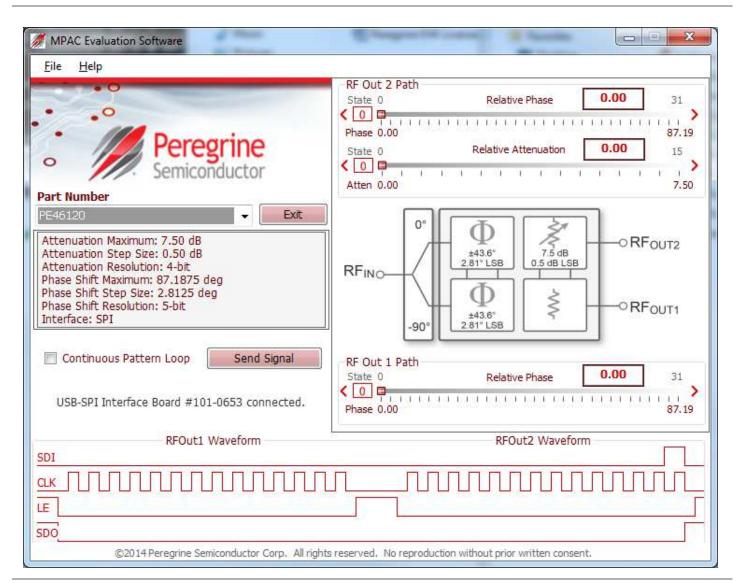

# Using the Graphical User Interface

**Figure 15** displays the MPAC application software graphical user interface (GUI), which has the USB interface board plugged into the computer. The message "USB-SPI Interface Board #101-0653 connected" will indicate that the USB interface board is connected and recognized. "Hardware Operation" as shown on page 11 is for the EVK hardware configuration to use with the GUI control software. If the USB interface board is not connected when the application software is launched, the message "No interface board connected! Please connect USB-SPI Interface #101-0653" will appear at the bottom of the screen.

In the upper left corner, under the Peregrine logo, there is a drop-down menu item to select the part number for evaluation and the part description is below the part number box.

The MPAC application software graphical user interface (GUI) is displayed in **Figure 15** and illustrates the available controls and messages available to the user.

Figure 15 • MPAC Application Software Graphical User Interface<sup>(\*)</sup>

Note: \* SDO in the serial interface waveform is read back from the MPAC to verify SDO toggling to indicate proper communication with the MPAC.

#### **Continuous Pattern Loop**

The continuous pattern loop checkbox (see **Figure 16**) allows the user to observe the evaluation board automatically step through each of the phase and attenuation states. Once the GUI reaches the maximum state value the cycle begins again at the minimum state value. This function can be started and stopped at any time by selecting/deselecting the checkbox.

Figure 16 • Continuous Pattern Loop

### Send Signal

The "Send Signal" box can be used to resend the same data.

Figure 17 • Send Signal

Send Signal

#### Attenuation and Phase Slide Bar

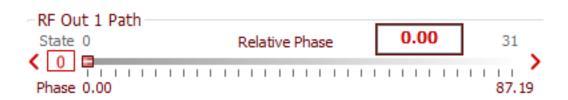

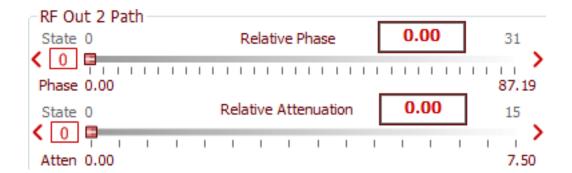

The RF Out Path slide bar allows the user to quickly select the desired attenuation and phase. The arrows at the left and right can be clicked to increase or decrease phase or attenuation state at the minimum step size. The attenuation and phase value text box is updated with each change of the phase slider. This control is two-way; the user can also enter a valid attenuation and phase value into this text box followed by the ENTER key to program the hardware with the updated value.

Figure 18 • RF<sub>OUT1</sub> Path Slide Bar

Figure 19 • RF<sub>OUT2</sub> Path Slide Bar

This page intentionally left blank.

# **Technical Resources**

4

### **Technical Resources**

Additional technical resources are available for download in the Products section at www.psemi.com. These include the Product Specification datasheet, S-parameters, zip file, evaluation kit schematic and bill of materials, material declaration form and PC-compatible software file.

Trademarks are subject to trademark claims.

This page intentionally left blank.

# **Document Categories**

### **Advance Information**

The product is in a formative or design stage. The document contains design target specifications for product development. Specifications and features may change in any manner without notice.

# **Preliminary Specification**

The document contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product.

# **Product Specification**

The document contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

# Not Recommended for New Designs (NRND)

This product is in production but is not recommended for new designs.

## End of Life (EOL)

This product is currently going through the EOL process. It has a specific last-time buy date.

### **Obsolete**

This product is discontinued. Orders are no longer accepted for this product.