# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **Product Description**

PE64907 is a DuNE<sup>™</sup> technology-enhanced Digitally Tunable Capacitor (DTC) based on Peregrine's UltraCMOS<sup>®</sup> technology. This highly versatile product supports a wide variety of tuning circuit topologies with emphasis on impedance matching and aperture tuning applications.

PE64907 offers high RF power handling and ruggedness while meeting challenging harmonic and linearity requirements enabled by Peregrine's HaRP<sup>™</sup> technology. The device is controlled through the widely supported 3-wire (SPI compatible) interface. All decoding and biasing is integrated on-chip and no external bypassing or filtering components are required.

DuNE<sup>™</sup> devices feature ease of use while delivering superior RF performance in the form of tuning accuracy, monotonicity, tuning ratio, power handling, size, and quality factor. With built-in bias voltage generation and ESD protection, DTC products provide a monolithically integrated tuning solution for demanding RF applications.

## Product Specification PE64907

UltraCMOS<sup>®</sup> Digitally Tunable Capacitor (DTC) 100-3000 MHz

#### Features

- 3-wire (SPI) compatible serial interface with built-in bias voltage generation and ESD protection

- DuNE<sup>™</sup> technology enhanced

- 5-bit 32-state Digitally Tunable Capacitor

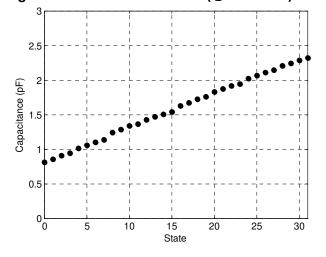

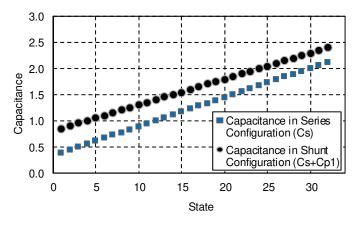

- Shunt configuration C = 0.85 pF to 2.4 pF (2.82:1 tuning ratio) in discrete 50 fF steps

- High RF power handling (30 V<sub>pk</sub> RF) and linearity

- Wide power supply range (2.3V to 4.8V) and low current consumption (typ. 140 μA at 2.75V)

- High ESD tolerance of 2kV HBM on all pins

- Applications include:

- Tunable antennas

- Tunable matching networks

- Tunable filter networks

- Phase shifters

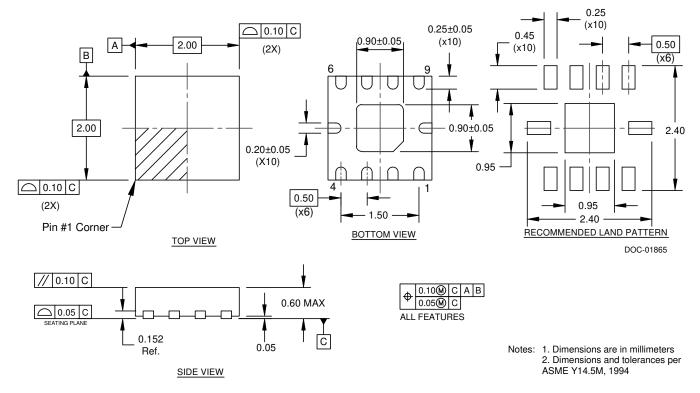

#### Figure 2. Package Type

10-lead 2 x 2 x 0.55 mm QFN

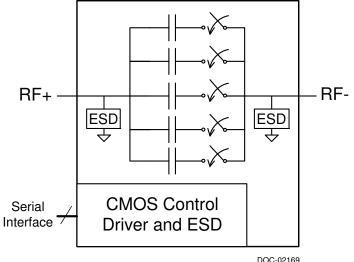

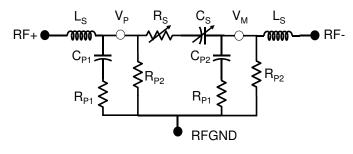

### Figure 1. Functional Diagram

DOC-0216

Document No. DOC-30214-2 | www.psemi.com

©2013 Peregrine Semiconductor Corp. All rights reserved.

#### Table 1. Electrical Specifications @ 25°C, V<sub>DD</sub> = 2.75V (In shunt configuration, RF- connected to GND)

| Parameter                                       | Condition                                                                                                        | Min  | Тур        | Max        | Unit       |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------------|------------|------------|

| Operating frequency                             |                                                                                                                  | 100  |            | 3000       | MHz        |

| Minimum capacitance<br>(C <sub>min</sub> )      | State 00000, 100 MHz                                                                                             | 0.77 | 0.85       | 0.94       | pF         |

| Maximum capacitance<br>(C <sub>max</sub> )      | State 11111, 100 MHz                                                                                             | 2.16 | 2.40       | 2.64       | pF         |

| Tuning ratio                                    | C <sub>max</sub> /C <sub>min</sub> , 100 MHz                                                                     |      | 2.82:1     |            |            |

| Step size                                       | 5 bits (32 states), 100 MHz                                                                                      |      | 0.050      |            | pF         |

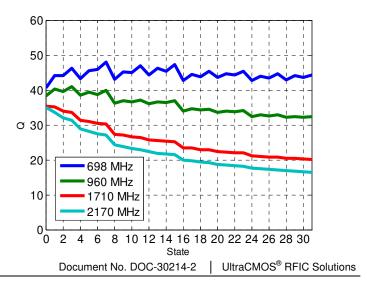

| Quality factor at C <sub>min</sub> <sup>1</sup> | 698 - 960 MHz, with L <sub>S</sub> removed<br>1710 - 2170 MHz, with L <sub>S</sub> removed                       |      | 41<br>37   |            |            |

| Quality Factor at C <sub>max</sub> <sup>1</sup> | 698 - 960 MHz, with L <sub>S</sub> removed<br>1710 - 2170 MHz, with L <sub>S</sub> removed                       |      | 34<br>16   |            |            |

| Self resonant frequency                         | State 00000<br>State 11111                                                                                       |      | 8.3<br>3.5 |            | GHz        |

| Harmonics <sup>2</sup>                          | 2fo, 3fo: 698 - 915 MHz; P <sub>IN</sub> +34 dBm, 50Ω<br>2fo, 3fo: 1710 - 1910 MHz; P <sub>IN</sub> +32 dBm, 50Ω |      |            | -36<br>-36 | dBm<br>dBm |

| IMD3                                            | Bands I,II,V/VIII, +20 dBm CW @ TX freq,<br>-15 dBm CW @ 2Tx-Rx freq, 50Ω                                        |      |            | -105       | dBm        |

| Third order intercept point (IP3)               | Shunt configuration derived from IMD3 spec IP3 = $(2P_{TX} + P_{block} - IMD3) / 2$                              |      | 65         |            | dBm        |

| Switching time <sup>3,4</sup>                   | State change to 10/90% delta capacitance between any two states                                                  |      |            | 12         | μs         |

| Start-up time <sup>3</sup>                      | Time from $V_{DD}$ within specification to all performances within specification                                 |      |            | 70         | μs         |

| Wake-up time <sup>3,4</sup>                     | State change from Standby mode to RF state to all performances within specification                              |      |            | 70         | μs         |

Notes: 1. Q for a shunt DTC based on a series RLC equivalent circuit

Q = X<sub>C</sub> / R = (X - X<sub>L</sub>) / R, where X = X<sub>L</sub> + X<sub>C</sub>, X<sub>L</sub> = 2\*pi\*f\*L, X<sub>C</sub> = -1 / (2\*pi\*f\*C), which is equal to removing the effect of parasitic inductance L<sub>S</sub>

2. In shunt between 50Ω ports. Pulsed RF input with 4620 µS period, 50% duty cycle, measured per 3GPP TS 45.005

3. DC path to ground at RF– must be provided to achieve specified performance

4. State change activated on falling edge of SEN following data word

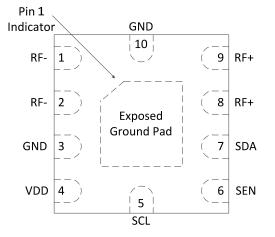

#### Figure 3. Pin Configuration (Top View)

#### **Table 2. Pin Descriptions**

| Pin # | Pin Name        | Description                                           |

|-------|-----------------|-------------------------------------------------------|

| 1     | RF-             | Negative RF port <sup>1</sup>                         |

| 2     | RF-             | Negative RF port <sup>1</sup>                         |

| 3     | GND             | Ground <sup>2</sup>                                   |

| 4     | V <sub>DD</sub> | Power supply pin                                      |

| 5     | SCL             | Serial interface clock input                          |

| 6     | SEN             | Serial interface latch enable input                   |

| 7     | SDA             | Serial interface data input                           |

| 8     | RF+             | Positive RF port <sup>1</sup>                         |

| 9     | RF+             | Positive RF port <sup>1</sup>                         |

| 10    | GND             | Ground <sup>2</sup>                                   |

| Pad   | GND             | Exposed pad: ground for proper operation <sup>2</sup> |

Notes: 1. For optimal performance, recommend typing Pins 1-2 and Pins 8-9 together on PCB

2. For optimal performance, recommend tying Pins 3, 10, and exposed ground pad together on PCB

#### **Moisture Sensitivity Level**

The Moisture Sensitivity Level rating for the PE64907 in the 10-lead 2 x 2 x 0.55 mm QFN package is MSL1.

#### **Table 3. Operating Ranges**

| Parameter                                                                                                                                   | Symbol          | Min  | Тур  | Max        | Unit       |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|------|------------|------------|

| Supply voltage                                                                                                                              | $V_{\text{DD}}$ | 2.30 | 2.75 | 4.80       | V          |

| Supply current ( $V_{DD} = 2.75V$ )                                                                                                         | I <sub>DD</sub> |      | 140  | 200        | μA         |

| Standby current ( $V_{DD} = 2.75V$ )                                                                                                        | I <sub>DD</sub> |      | 25   |            | μA         |

| Control voltage high                                                                                                                        | V <sub>IH</sub> | 1.2  | 1.8  | 3.1        | V          |

| Control voltage low                                                                                                                         | V <sub>IL</sub> | 0    | 0    | 0.57       | V          |

| RF input power (50Ω) <sup>1</sup><br>698 - 915 MHz<br>1710 - 1910 MHz                                                                       |                 |      |      | +34<br>+32 | dBm<br>dBm |

| $\begin{array}{c} \text{Peak operating RF voltage}^2 \\ V_{\text{P}} \text{ to } V_{\text{M}} \\ V_{\text{P}} \text{ to RFGND} \end{array}$ |                 |      |      | 30<br>30   | Vpk<br>Vpk |

| Operating temperature range                                                                                                                 | T <sub>OP</sub> | -40  | +25  | +85        | °C         |

| Storage temperature range                                                                                                                   | T <sub>ST</sub> | -65  | +25  | +150       | °C         |

Notes: 1. Maximum power available from  $50\Omega$  source. Pulsed RF input with 4620 µS period, 50% duty cycle, measured per 3GPP TS 45.005 measured in shunt between  $50\Omega$  ports, RF- connected to GND

2. Node voltages defined per Equivalent Circuit Model Schematic (*Figure 13*). When DTC is used as a part of reactive network, impedance transformation may cause the internal RF voltages (V<sub>P</sub>, V<sub>M</sub>) to exceed peak operating RF voltage even with specified RF input power levels. For operation above about +20 dBm (100 mW), the complete RF circuit must be simulated using actual input power and load conditions, and internal node voltages (V<sub>P</sub>, V<sub>M</sub> in *Figure 13*) monitored to not exceed 30 V<sub>pk</sub>

#### **Table 4. Absolute Maximum Ratings**

| Parameter/Condition          | Symbol           | Min | Max  | Unit |

|------------------------------|------------------|-----|------|------|

| ESD Voltage HBM <sup>1</sup> | $V_{\text{ESD}}$ |     | 2000 | V    |

Note 1: Human Body Model (MIL-STD-883 Method 3015.7)

Exceeding absolute maximum ratings may cause permanent damage. Operation should be restricted to the limits in the Operating Ranges table. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS<sup>®</sup> device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the specified rating.

#### Latch-Up Avoidance

Unlike conventional CMOS devices, UltraCMOS<sup>®</sup> devices are immune to latch-up.

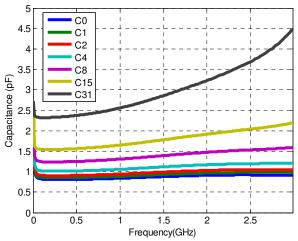

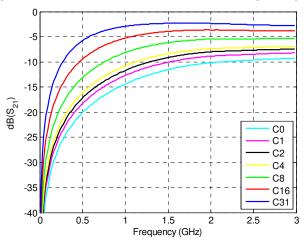

#### Performance Plots @ 25°C and 2.75V unless otherwise specified

Figure 4. Measured Shunt C (@ 100 MHz) vs State

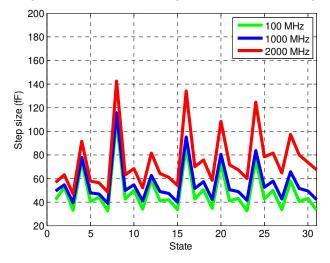

Figure 6. Measured Step Size vs State (frequency)

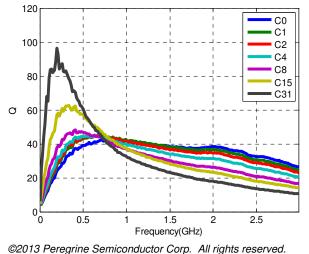

Figure 8. Measured Shunt Q vs Frequency (major states)

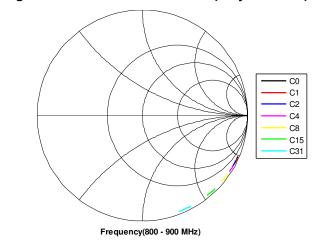

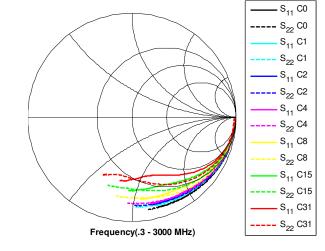

Figure 5. Measured Shunt S<sub>11</sub> (major states)

Figure 9. Measured Shunt Q vs State

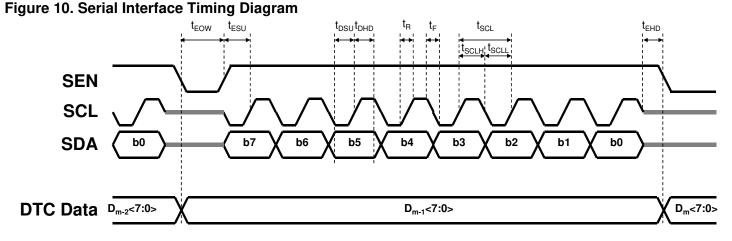

#### Serial Interface Operation and Sharing

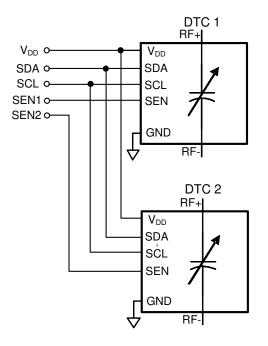

The PE64907 is controlled by a three wire SPIcompatible interface with enable active high. As shown in *Figure 10*, the serial master initiates the start of a telegram by driving the SEN (Serial Enable) line high. Each bit of the 8-bit telegram (MSB first in) is clocked in on the rising edge of SCL (Serial Clock), as shown in *Table 5* and *Figure 10*. Transitions on SDA (Serial Data) are allowed on the falling edge of SCL. The DTC activates the data on the falling edge of SEN. The DTC does not count how many bits are clocked and only maintains the last 8 bits it received. More than 1 DTC can be controlled by one interface by utilizing a dedicated enable (SEN) line for each DTC. SDA, SCL, and  $V_{DD}$  lines may be shared as shown in *Figure 11*. Dedicated SEN lines act as a chip select such that each DTC will only respond to serial transactions intended for them. This makes each DTC change states sequentially as they are programmed.

Alternatively, a dedicated SDA line with common SEN can be used. This allows all DTCs to change states simultaneously, but requires all DTCs to be programmed even if the state is not changed.

LSB (last in)

|                |                |                  |    | •  | U  | U  | •  |

|----------------|----------------|------------------|----|----|----|----|----|

| b7             | b6             | b5               | b4 | b3 | b2 | b1 | b0 |

| 0 <sup>1</sup> | 0 <sup>1</sup> | STB <sup>2</sup> | d4 | d3 | d2 | d1 | d0 |

| <b>A</b>       |                |                  |    |    |    |    |    |

Table 5. 8-Bit Serial Programming Register Map

MSB (first in)

Notes: 1. These bits are reserved and must be written to 0 for proper operation 2. The DTC is active when low (set to 0) and in low-current stand-by mode when high (set to 1)

#### Table 6. Serial Interface Timing Characteristics

$V_{DD} = 2.75V$ , -40 °C <  $T_A$  < +85 °C, unless otherwise specified

| Symbol            | Parameter                           | Min  | Max | Unit |

|-------------------|-------------------------------------|------|-----|------|

| t <sub>SCL</sub>  | Serial Clock Period                 | 38.4 |     | ns   |

| t <sub>SCLL</sub> | SCL Low Time                        | 13.2 |     | ns   |

| t <sub>SCLH</sub> | SCL High Time                       | 13.2 |     | ns   |

| t <sub>R</sub>    | SCL, SDA, SEN Rise Time             |      | 6.5 | ns   |

| t <sub>F</sub>    | SCL, SDA, SEN Fall Time             |      | 6.5 | ns   |

| t <sub>ESU</sub>  | SEN rising edge to SCL rising edge  | 19.2 |     | ns   |

| t <sub>EHD</sub>  | SCL rising edge to SEN falling edge | 19.2 |     | ns   |

| t <sub>DSU</sub>  | SDA valid to SCL rising edge        |      |     | ns   |

| t <sub>DHD</sub>  | SDA valid after SCL rising edge     |      |     | ns   |

| t <sub>EOW</sub>  | SEN falling edge to SEN rising edge | 38.4 |     | ns   |

Figure 11. Recommended Bus Sharing

©2013 Peregrine Semiconductor Corp. All rights reserved.

Document No. DOC-30214-2 | www.psemi.com

#### Equivalent Circuit Model Description

The DTC Equivalent Circuit Model includes all parasitic elements and is accurate in both series and shunt configurations, reflecting physical circuit behavior accurately and providing very close correlation to measured data. It can easily be used in circuit simulation programs.

For  $V_P$  and  $V_M$  max operating limits, refer to *Table 3*.

#### Figure 12. Equivalent Circuit Model Schematic

#### **Table 7. Equivalent Circuit Model Parameters**

| Variable        | <b>Equation</b> (state = 0, 1, 231) | Unit |

|-----------------|-------------------------------------|------|

| Cs              | 0.056*state + 0.38                  | pF   |

| Rs              | 20/(state+20/(state+0.7)) + 0.7     | Ω    |

| R <sub>P1</sub> | 8+state                             | Ω    |

| R <sub>P2</sub> | 25000+3*state^3                     |      |

| C <sub>P1</sub> | -0.0061*state + 0.47                | pF   |

| C <sub>P2</sub> | 0.0096*state + 0.61                 | pF   |

| Ls              | 0.35                                |      |

#### Table 8. Equivalent Circuit Data

|      | State |     | DTC     | Core               | Parasitic       | Elements        |

|------|-------|-----|---------|--------------------|-----------------|-----------------|

| Hex  | Bin   | Dec | C₅ [pF] | R <sub>s</sub> [Ω] | C <sub>P1</sub> | C <sub>P2</sub> |

| 0x00 | 00000 | 0   | 0.38    | 1.40               | 0.47            | 0.61            |

| 0x01 | 00001 | 1   | 0.44    | 2.27               | 0.46            | 0.62            |

| 0x02 | 00010 | 2   | 0.49    | 2.83               | 0.46            | 0.63            |

| 0x03 | 00011 | 3   | 0.55    | 3.08               | 0.45            | 0.64            |

| 0x04 | 00100 | 4   | 0.60    | 3.12               | 0.45            | 0.65            |

| 0x05 | 00101 | 5   | 0.66    | 3.05               | 0.44            | 0.66            |

| 0x06 | 00110 | 6   | 0.72    | 2.93               | 0.43            | 0.67            |

| 0x07 | 00111 | 7   | 0.77    | 2.78               | 0.43            | 0.68            |

| 0x08 | 01000 | 8   | 0.83    | 2.64               | 0.42            | 0.69            |

| 0x09 | 01001 | 9   | 0.88    | 2.51               | 0.42            | 0.70            |

| 0x0A | 01010 | 10  | 0.94    | 2.39               | 0.41            | 0.71            |

| 0x0B | 01011 | 11  | 1.00    | 2.27               | 0.40            | 0.72            |

| 0x0C | 01100 | 12  | 1.05    | 2.17               | 0.40            | 0.73            |

| 0x0D | 01101 | 13  | 1.11    | 2.08               | 0.39            | 0.73            |

| 0x0E | 01110 | 14  | 1.16    | 2.00               | 0.38            | 0.74            |

| 0x0F | 01111 | 15  | 1.22    | 1.93               | 0.38            | 0.75            |

| 0x10 | 10000 | 16  | 1.28    | 1.86               | 0.37            | 0.76            |

| 0x11 | 10001 | 17  | 1.33    | 1.80               | 0.37            | 0.77            |

| 0x12 | 10010 | 18  | 1.39    | 1.75               | 0.36            | 0.78            |

| 0x13 | 10011 | 19  | 1.44    | 1.70               | 0.35            | 0.79            |

| 0x14 | 10100 | 20  | 1.50    | 1.65               | 0.35            | 0.80            |

| 0x15 | 10101 | 21  | 1.56    | 1.61               | 0.34            | 0.81            |

| 0x16 | 10110 | 22  | 1.61    | 1.57               | 0.34            | 0.82            |

| 0x17 | 10111 | 23  | 1.67    | 1.54               | 0.33            | 0.83            |

| 0x18 | 11000 | 24  | 1.72    | 1.51               | 0.32            | 0.84            |

| 0x19 | 11001 | 25  | 1.78    | 1.48               | 0.32            | 0.85            |

| 0x1A | 11010 | 26  | 1.84    | 1.45               | 0.31            | 0.86            |

| 0x1B | 11011 | 27  | 1.89    | 1.42               | 0.31            | 0.87            |

| 0x1C | 11100 | 28  | 1.95    | 1.40               | 0.30            | 0.88            |

| 0x1D | 11101 | 29  | 2.00    | 1.37               | 0.29            | 0.89            |

| 0x1E | 11110 | 30  | 2.06    | 1.35               | 0.29            | 0.90            |

| 0x1F | 11111 | 31  | 2.12    | 1.33               | 0.28            | 0.91            |

©2013 Peregrine Semiconductor Corp. All rights reserved.

#### **Series Operation**

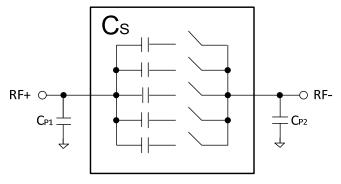

In Series configuration, the effective capacitance between RF+ and RF- ports is represented by  $C_s$  and tuning ratio as  $C_{Smax}/C_{Smin}$ .

#### Figure 13. Effective Capacitance Diagram

Shunt Configuration (looking into RF+ when RF- is grounded) will have higher total capacitance at RF+ due to parallel combination of Cs with parasitic capacitance  $C_{P1}$  ( $C_S + C_{P1}$ ), as demonstrated in *Figure 14* and *Table 9.*

| Configuration       | Effective<br>Capacitance | C <sub>min</sub><br>(state 0) | C <sub>max</sub><br>(state 31) | Tuning<br>Ratio |

|---------------------|--------------------------|-------------------------------|--------------------------------|-----------------|

| Series (RF+ to RF-) | Cs                       | 0.38                          | 2.12                           | 5.58:1          |

| Shunt (RF+ to GND)  | $C_{S} + C_{P1}$         | 0.85                          | 2.4                            | 2.82:1          |

$S_{11}$  and  $S_{21}$  for series configuration is illustrated in *Figures 15* and *16*.  $S_{21}$  includes mismatch and dissipative losses and is not indicative of tuning network loss. Equivalent Circuit Model can be used for simulation of tuning network loss.

#### Figure 16. Measured Series S<sub>21</sub> vs. Frequency

When the DTC is used as a part of a reactive network, impedance transformation may cause the internal RF voltages ( $V_P$  and  $V_M$  in *Figure 12*) to exceed peak operating RF voltage. The complete RF circuit must be simulated using actual input power and load conditions to ensure neither  $V_P$  nor  $V_M$  exceeds 30 Vpk.

Document No. DOC-30214-2 | www.psemi.com

#### Layout Recommendations

For optimal results, place a ground fill directly under the DTC package on the PCB. Layout isolation is desired between all control and RF lines. When using the DTC in a shunt configuration, it is important to make sure the RF-pin is solidly grounded to a filled ground plane. Ground traces should be as short as possible to minimize inductance. A continuous ground plane is preferred on the top layer of the PCB. When multiple DTCs are used together, the physical distance between them should be minimized and the connection should be as wide as possible to minimize series parasitic inductance.

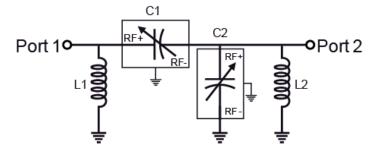

#### Figure 17. Recommended Schematic of Multiple DTCs

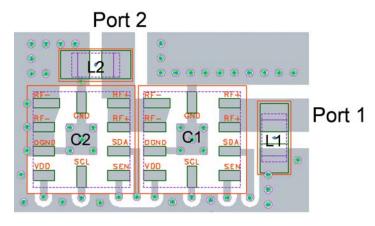

#### Figure 18. Recommended Layout of Multiple DTCs

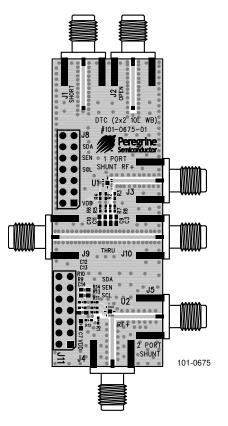

#### **Evaluation Board**

The 101-0675 Evaluation Board (EVB) was designed for accurate measurement of the DTC impedance and loss. Two configurations are available: 1 Port Shunt (J3) and 2 Port Shunt (J4, J5). Three calibration standards are provided. The open (J2) and short (J1) standards (104 ps delay) are used for performing port extensions and accounting for electrical length and transmission line loss. The Thru (J9, J10) standard can be used to estimate PCB transmission line losses for scalar de-embedding of the 2 Port Series configuration (J4, J5).

The board consists of a 4 layer stack with 2 outer layers made of Rogers 4350B ( $\varepsilon_r = 3.48$ ) and 2 inner layers of FR4 ( $\varepsilon_r = 4.80$ ). The total thickness of this board is 62 mils (1.57 mm). The inner layers provide a ground plane for the transmission lines. Each transmission line is designed using a coplanar waveguide with ground plane (CPWG) model using a trace width of 32 mils (0.813 mm), gap of 15 mils (0.381 mm), and a metal thickness of 1.4 mils (0.051 mm).

#### Figure 19. Evaluation Board Layout

©2013 Peregrine Semiconductor Corp. All rights reserved.

#### Figure 20. Package Drawing

10-lead 2 x 2 x 0.55 mm QFN

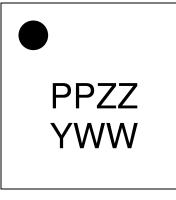

Figure 21. Top Marking Specifications

| Marking Spec<br>Symbol | Package<br>Marking | Definition                                                              |

|------------------------|--------------------|-------------------------------------------------------------------------|

| PP                     | DH*                | Part number marking for PE64907                                         |

| ZZ                     | 00-99              | Last two digits of lot code                                             |

| Y                      | 0-9                | Last digit of year, starting from 2009<br>(0 for 2010, 1 for 2011, etc) |

| ww                     | 01-53              | Work week                                                               |

17-0112

\* Note: (PP), the package marking specific to the PE64906, is shown in the figure instead of the standard Peregrine package marking symbol (P)

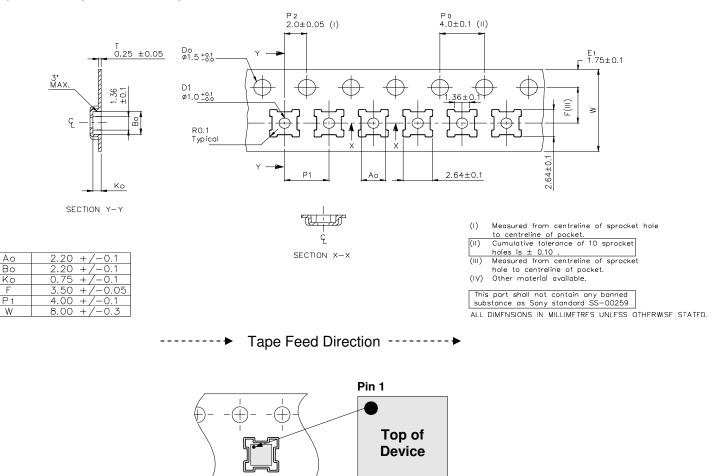

#### Figure 22. Tape and Reel Specifications

Device Orientation in Tape

#### Table 10. Ordering Information

| Order Code    | Description            | Package         | Shipping Method |

|---------------|------------------------|-----------------|-----------------|

| PE64907MLAA-Z | PE64907 DTC            | 10-lead 2x2 QFN | 3,000 units/T&R |

| EK64907-11    | PE64907 Evaluation kit | Evaluation kit  | 1 set/box       |

#### **Sales Contact and Information**

For sales and contact information please visit www.psemi.com.

<u>Advance Information</u>: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. <u>Preliminary Specification</u>: The datasheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product. <u>Product Specification</u>: The datasheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

The information in this datasheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this datasheet are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo, UltraCMOS and UTSi are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp. Peregrine products are protected under one or more of the following U.S. Patents: <u>http://patents.psemi.com</u>.

#### ©2013 Peregrine Semiconductor Corp. All rights reserved.

Document No. DOC-30214-2 | UltraCMOS® RFIC Solutions

Page 10 of 10