Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **EMC2105**

# RPM-Based High Side Fan Controller with Hardware Thermal Shutdown

#### PRODUCT FEATURES

**Datasheet**

#### **General Description**

The EMC2105 is an SMBus compliant fan controller with up to five (up to 4 external and 1 internal) temperature channels. The fan driver can be operated using two methods each with two modes. The methods include an RPM based Fan Speed Control Algorithm and a direct drive setting. The modes include manually programming the desired settings or using the internal programmable temperature look-up table to select the desired setting based on measured temperature.

The temperature monitors offer 1°C accuracy (for external diodes) with sophisticated features to reduce errors introduced by series resistance and beta variation of substrate thermal diode transistors commonly found in processors.

The EMC2105 also includes a hardware programmable temperature limit and dedicated system shutdown output for thermal protection of critical circuitry.

#### **Applications**

- Notebook Computers

- Embedded Applications

- Projectors

- Industrial and Networking Equipment

#### **Features**

- Programmable Fan Control circuit

- 600mA, 5V, High Side Fan Driver

- Optional detection of aging fans

- RPM based fan control algorithm

- 2% accuracy from 500RPM to 16k RPM

- Temperature Look-Up Table

- Allows programmed fan response to temperature

- 1 to 4 thermal zones to control fan driver

- Controls fan speed or drive setting

- Allows externally generated temperature data to control fan drivers including two DTS channels

- Up to Four External Temperature Channels

- Designed to support 45nm, 60nm, and 90nm CPUs

- Automatically detects and supports CPUs requiring the BJT or Transistor models

- Resistance error correction

- 1°C accurate (60°C to 100°C)

- 0.125°C resolution

- Detects fan aging and variation

- Up to three thermistor compatible voltage inputs

- Hardware Programmable Thermal Shutdown Temperature

- Cannot be altered by software

- 60°C to 122°C Range or 92°C to 154°C Range

- Programmable High and Low Limits for all channels

- 3.3V Supply Voltage

- SMBus 2.0 Compliant

- SMBus Alert compatible

- Available in 20-pin QFN Package Lead Free RoHS compliant (4mm x 4mm)

#### **ORDER NUMBER:**

| ORDERING NUMBER | PACKAGE                                | FEATURES                                                                                                       |

|-----------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------|

| EMC2105-BP      | 20 pin QFN Lead-Free<br>RoHS compliant | Single High Side Fan driver, up to 4external diode measurement channels, one Critical / Thermal Shutdown input |

#### **REEL SIZE IS 4,000 PIECES**

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2009 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| Chap | oter 1 Block Diagram                                        | 9        |

|------|-------------------------------------------------------------|----------|

| Chap | oter 2 Pin Description                                      | 0        |

| Chap | oter 3 Electrical Specifications                            | 4        |

| 3.1  | Electrical Specifications                                   |          |

| 3.2  | SMBus Electrical Specifications (client mode)               |          |

| Char | oter 4 Communications                                       | <b>-</b> |

| 4.1  | System Management Bus Interface Protocol                    |          |

| 4.2  | Write Byte                                                  |          |

| 4.3  | Read Byte                                                   |          |

| 4.4  | Send Byte                                                   |          |

| 4.5  | Receive Byte                                                |          |

| 4.6  | Alert Response Address                                      |          |

| 4.7  | SMBus Address                                               |          |

| 4.8  | SMBus Time-out.                                             |          |

|      | ONE DATE OF THE OUT.                                        | _        |

| Chap | 1                                                           |          |

| 5.1  | Critical/Thermal Shutdown                                   |          |

|      | 5.1.1 SHDN_SEL Pin                                          | 23       |

|      | 5.1.2 TRIP_SET / VIN4 Pin                                   | 23       |

| 5.2  | Fan Control Modes of Operation                              | 25       |

| 5.3  | High Side Fan Driver                                        | 26       |

|      | 5.3.1 Over Current Limit                                    | 26       |

| 5.4  | Fan Control Look-Up Table                                   | 27       |

|      | 5.4.1 Programming the Look Up Table                         | 28       |

|      | 5.4.2 DTS Support                                           |          |

| 5.5  | RPM based Fan Speed Control Algorithm (FSC)                 |          |

|      | 5.5.1 Programming the RPM Based Fan Speed Control Algorithm | 31       |

| 5.6  | Tachometer Measurement                                      | 31       |

|      | 5.6.1 Stalled Fan 3                                         | 31       |

|      | 5.6.2 32kHz Clock Source                                    |          |

|      | 5.6.3 Aging Fan or Invalid Drive Detection                  | 32       |

| 5.7  | Spin Up Routine                                             | 32       |

| 5.8  | Ramp Rate Control                                           | 33       |

| 5.9  | Watchdog Timer                                              |          |

| 5.10 | Internal Thermal Shutdown (TSD)                             | 35       |

| 5.11 | Fault Queue 3                                               |          |

| 5.12 | Temperature Monitoring                                      | 35       |

|      | 5.12.1 Dynamic Averaging                                    | 35       |

|      | 5.12.2 Resistance Error Correction                          | 36       |

|      | 5.12.3 Beta Compensation                                    | 36       |

|      | 5.12.4 Digital Averaging                                    |          |

| 5.13 | Thermistor Support                                          | 36       |

| 5.14 | Diode Connections                                           |          |

|      | 5.14.1 Diode Faults                                         | 37       |

| 5.15 | GPIOs                                                       | 37       |

| 5.16 | Interrupts                                                  | 37       |

| Char | ston 6 Dogiston Cot                                         | -        |

| Chap | oter 6 Register Set                                         | ø        |

| 6.1                  | Register Map                                    |      |

|----------------------|-------------------------------------------------|------|

| 6.2                  | Temperature Data Registers                      |      |

| 6.3                  | Critical/Thermal Shutdown Temperature Registers |      |

| 6.4                  | Pushed Temperature Registers                    |      |

| 6.5                  | Voltage Registers                               |      |

| 6.6                  | Beta Configuration Registers                    |      |

| 6.7                  | REC Configuration Register                      |      |

| 6.8                  | Critical Temperature Limit Registers            |      |

| 6.9                  | Configuration Register                          |      |

| 6.10                 | Configuration 2 Register                        |      |

| 6.11                 | Configuration 3 Register                        |      |

| 6.12                 | Interrupt Status Register                       |      |

| 6.13                 | Error Status Registers                          |      |

|                      | 6.13.1 Tcrit Status Register                    |      |

| 6.14                 | Fan Status Register                             |      |

| 6.15                 | Interrupt Enable Register                       |      |

| 6.16                 | Fan Interrupt Enable Register                   |      |

| 6.17                 | Limit Registers                                 | . 57 |

| 6.18                 | Fan Setting Register                            |      |

| 6.19                 | Fan Configuration 1 Register                    |      |

| 6.20                 | Fan Configuration 2 Register                    |      |

| 6.21                 | Gain Register                                   |      |

| 6.22                 | Fan Spin Up Configuration Register              |      |

| 6.23                 | Fan Step Register                               |      |

| 6.24                 | Fan Minimum Drive Register                      |      |

| 6.25                 | Valid TACH Count Register                       |      |

| 6.26                 | Fan Drive Fail Band Registers                   |      |

| 6.27                 | TACH Target Registers                           |      |

| 6.28                 | TACH Reading Registers                          |      |

| 6.29                 | Look Up Table Configuration Register            |      |

| 6.30                 | Look Up Table Registers                         |      |

| 6.31                 | Muxed Pin Configuration Register                |      |

| 6.32                 | GPIO Direction Register                         |      |

| 6.33                 | GPIO Pin Output Configuration Register          |      |

| 6.34                 | GPIO Input Register                             |      |

| 6.35                 | GPIO Output Register                            |      |

| 6.36                 | GPIO Interrupt Enable Register                  |      |

| 6.37                 | GPIO Status Register                            |      |

| 6.38                 | Software Lock Register                          |      |

| 6.39                 | Product Features Register                       |      |

| 6.40                 | Product ID Register                             |      |

| 6.41                 | Manufacturer ID Register                        |      |

| 6.42                 | Revision Register                               | . /: |

| <b>C</b> 1           | And To Dealess Durantes                         | 7    |

|                      | oter 7 Package Drawing                          |      |

| 7.1                  | QFN 20-Pin 4mm x 4mm                            |      |

| 7.2                  | Package Markings                                | . /5 |

| Anna                 | endix A Thermistors                             | 74   |

| љррс<br>А.1          | Thermistor Look Up Tables                       |      |

| <u>л. і</u>          | THEITHISTOLEOUR OF LANGS                        | . // |

| Anne                 | endix B Look Up Table Operation                 | . 81 |

| љ <b>рр</b> с<br>В.1 | Example #1                                      |      |

|                      |                                                 |      |

#### RPM-Based High Side Fan Controller with Hardware Thermal Shutdown

| Chan | ter 8   | Revision History                          | . 89 |

|------|---------|-------------------------------------------|------|

|      | B.3.3   | LUT Configuration - Bit Description       | . 87 |

|      | B.3.2   | Fan Spin Up Configuration Bit Description |      |

|      | B.3.1   | Fan Configuration 1 Bit Description       | . 86 |

| B.3  | Example | e #3                                      | . 86 |

|      | B.2.4   | LUT Configuration - Bit Description       | . 84 |

|      | B.2.3   | Fan Spin Up Configuration Bit Description | . 84 |

|      | B.2.2   | Fan Configuration 1 Bit Description       | . 84 |

|      | B.2.1   | Configuration 3 Bit Description           | . 84 |

| B.2  | Example | e #2                                      | . 83 |

|      | B.1.1   | LUT Configuration Bit Description         | . 82 |

|      |         |                                           |      |

# **List of Figures**

| Figure 1.1 | EMC2105 Block Diagram                                   | . 9 |

|------------|---------------------------------------------------------|-----|

| Figure 2.1 | EMC2105 Pin Diagram (20 Pin QFN)                        | 10  |

| Figure 4.1 | SMBus Timing Diagram                                    | 18  |

| Figure 5.1 | System Diagram of EMC2105                               | 21  |

| Figure 5.2 | EMC2105 Critical/Thermal Shutdown Block Diagram         | 22  |

| Figure 5.3 | Fan Control Look-Up Table Example                       | 28  |

| Figure 5.4 | RPM based Fan Speed Control Algorithm                   | 30  |

| Figure 5.5 | Spin Up Routine                                         | 33  |

| Figure 5.6 | Ramp Rate Control                                       | 34  |

| Figure 5.7 | Diode Connections                                       | 37  |

| Figure 7.1 | EMC2105 20-Pin 4x4mm QFN Package Outline and Parameters | 74  |

| Figure 7.2 | EMC2105 Package Markings                                | 75  |

| Figure A.1 | "Low Side" Thermistor Connection                        | 76  |

# **List of Tables**

|            | Pin Description for EMC2105                     |    |

|------------|-------------------------------------------------|----|

| Table 2.2  | Pin Types                                       | 12 |

| Table 3.1  | Absolute Maximum Ratings                        | 14 |

| Table 3.2  | Electrical Specifications                       | 14 |

| Table 3.3  | SMBus Electrical Specifications                 | 17 |

| Table 4.1  | Protocol Format                                 | 18 |

| Table 4.2  | Write Byte Protocol                             | 18 |

| Table 4.3  | Read Byte Protocol                              | 19 |

|            |                                                 |    |

|            | Receive Byte Protocol                           |    |

|            | Alert Response Address Protocol                 |    |

| Table 5.1  | SHDN_SEL Pin Configuration                      |    |

|            | TRIP_SET Resistor Setting                       |    |

|            | Fan Controls Active for Operating Mode          |    |

| Table 5.4  | Dynamic Averaging Behavior                      |    |

| Table 6.1  | EMC2105 Register Set                            |    |

|            | Temperature Data Registers                      |    |

|            | Temperature Data Format                         |    |

|            | Critical/Thermal Shutdown Temperature Registers |    |

|            | Critical / Thermal Shutdown Data Format         |    |

|            | Pushed Temperature Register                     |    |

|            | TripSet Voltage Register                        |    |

|            | Beta Configuration Registers                    |    |

|            | Beta Compensation Look Up Table.                |    |

|            | REC Configuration Register                      |    |

|            | Limit Registers                                 |    |

|            |                                                 |    |

|            | Configuration Register                          |    |

|            | Configuration 2 Register                        |    |

|            | Fault Queue                                     |    |

|            | Conversion Rate                                 |    |

|            | Configuration 3 Register                        |    |

|            | Interrupt Status Register                       |    |

|            | Error Status Register                           |    |

|            | Fan Status Register                             |    |

|            | Interrupt Enable Register                       |    |

|            | Fan Interrupt Enable Register                   |    |

|            | Limit Registers                                 |    |

|            | Fan Driver Setting Register                     |    |

|            | Fan Configuration 1 Register                    |    |

| Table 6.25 | Range Decode                                    | 59 |

|            | Minimum Edges for Fan Rotation                  |    |

| Table 6.27 | Update Time                                     | 59 |

|            | Fan Configuration 1 Register                    |    |

|            | Derivative Options                              |    |

| Table 6.30 | Error Range Options                             | 61 |

|            | Gain Register                                   |    |

|            | Gain Decode                                     |    |

| Table 6.33 | Fan Spin Up Configuration Register              | 62 |

|            | DRIVE_FAIL_CNT[1:0] Bit Decode                  |    |

|            | Spin Level                                      |    |

|            | Spin Time                                       |    |

|            | Fan Step Register                               |    |

|            | Minimum Fan Drive Register                      |    |

| Table 6.39 Valid TACH Count Register                                            | . 64 |

|---------------------------------------------------------------------------------|------|

| Table 6.40 Fan Drive Fail Band Registers                                        | . 65 |

| Table 6.41 TACH Target Registers                                                | . 65 |

| Table 6.42 TACH Reading Registers                                               | . 66 |

| Table 6.43 Look Up Table Configuration Register                                 | . 66 |

| Table 6.44 TEMP3_CFG Decode                                                     |      |

| Table 6.45 TEMP4_CFG Decode                                                     |      |

| Table 6.46 Look Up Table Registers                                              |      |

| Table 6.47 Muxed Pin Configuration Register                                     |      |

| Table 6.48 GPIO Direction Register                                              |      |

| Table 6.49 GPIO Pin Output Configuration Register                               |      |

| Table 6.50 GPIO Input Register                                                  |      |

| Table 6.51 GPIO Output Register                                                 |      |

| Table 6.52 GPIO Interrupt Enable Register                                       |      |

| Table 6.53 GPIO Status Register                                                 |      |

| Table 6.54 Software Lock Register                                               |      |

| Table 6.55 Product Features Register                                            |      |

| Table 6.56 SHDN_SEL Bit Decode                                                  |      |

| Table 6.57 Product ID Register                                                  |      |

| Table 6.58 Manufacturer ID Register                                             |      |

| Table 6.59 Revision Register                                                    |      |

| Table A.1 "Low Side" Thermistor Look Up Table                                   |      |

| Table A.2 Inverted Thermistor Look Up Table                                     |      |

| Table B.1 Look Up Table Format                                                  |      |

| Table B.2 Look Up Table Example #1 Configuration                                |      |

| Table B.3 Fan Speed Control Table Example #1                                    |      |

| Table B.4 Fan Speed Determination for Example #1 (using settings in Table B.3)  |      |

| Table B.5 Look Up Table Example #2 Configuration                                |      |

| Table B.6 Fan Speed Control Table Example #2                                    |      |

| Table B.7 Fan Speed Determination for Example #2 (using settings in Table B.6)  |      |

| Table B.8 Look Up Table Example #3 Configuration                                |      |

| Table B.9 Fan Speed Control Table Example #3                                    |      |

| Table B.10 Fan Speed Determination for Example #3 (using settings in Table B.9) |      |

| Table 8.1. Customer Revision History                                            | 89   |

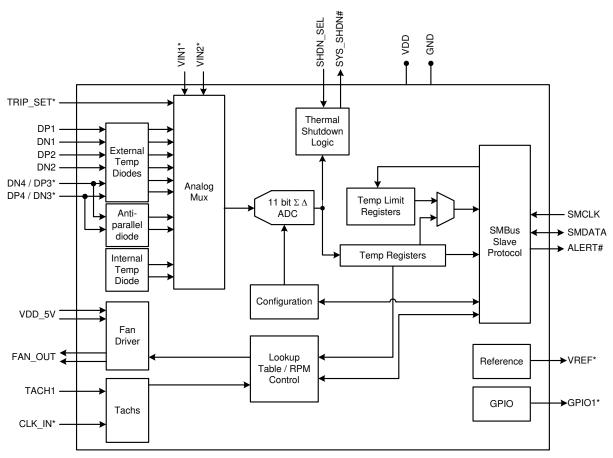

# **Chapter 1 Block Diagram**

\* denotes multiple pin functions

Figure 1.1 EMC2105 Block Diagram

# **Chapter 2 Pin Description**

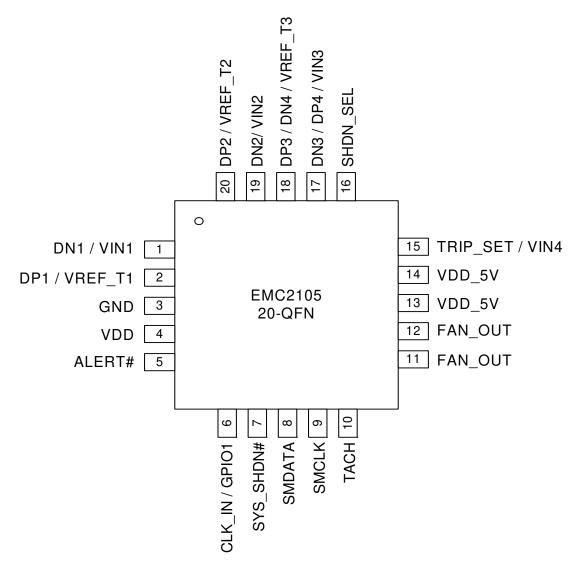

Figure 2.1 EMC2105 Pin Diagram (20 Pin QFN)

Table 2.1 Pin Description for EMC2105

| PIN NUMBER<br>EMC2105 | PIN NAME        | PIN FUNCTION                                                                             | PIN TYPE  |

|-----------------------|-----------------|------------------------------------------------------------------------------------------|-----------|

| 1                     | DN1 / VIN1      | DN1 - Negative (cathode) analog input for External Diode 1 (default)                     | AIO (2V)  |

|                       | DINT / VIINT    | VIN1 - General voltage input for use with a thermistor                                   | AI (2V)   |

| 2                     | DP1 / VREF T1   | DP1 - Positive (anode) analog input for External Diode 1 (default)                       | AIO (2V)  |

|                       | DITTY VILLI_IT  | VREF_T1 - Reference output for use with a thermistor and to drive VIN3                   | AO (2V)   |

| 3                     | GND             | Ground connection                                                                        | Power     |

| 4                     | VDD             | Power Supply                                                                             | Power     |

| 5                     | ALERT#          | Active low interrupt - requires external pull-up resistor.                               | OD (5V)   |

|                       |                 | CLK_IN - 32.768KHz clock input.                                                          | DI (5V)   |

|                       |                 | GPI1 - General Purpose Input (default)                                                   | DI (5V)   |

| 6                     | CLK_IN / GPIO1  | GPO1 - General Purpose push/ pull<br>Output                                              | DI (5V)   |

|                       |                 | GPO1 - General Purpose open drain<br>Output.                                             | DI (5V)   |

| 7                     | SYS_SHDN#       | Active low Critical System Shutdown output                                               | OD (5V)   |

| 8                     | SMDATA          | SMBus data input/output - requires external pull-up resistor                             | DIOD (5V) |

| 9                     | SMCLK           | SMBus clock input - requires external pull-up resistor                                   | DIOD (5V) |

| 10                    | TACH1           | Tachometer input for Fan 1                                                               | DI (5V)   |

| 11                    | FAN_OUT         | High Side Fan Driver Output                                                              | Power     |

| 12                    | FAN_OUT         | High Side Fan Driver Output                                                              | Power     |

| 13                    | VDD_5V          | Supply for High Side Fan Driver                                                          | Power     |

| 14                    | VDD_5V          | Supply for High Side Fan Driver                                                          | Power     |

| 15                    | TRIP_SET / VIN4 | TRIP_SET - Determines HW Shutdown temperature features for the hardware shutdown channel | AI (2V)   |

|                       |                 | VIN4 - General voltage input when<br>Thermal / Critical shutdown disabled                | AI (2V)   |

| 16                    | SHDN_SEL        | Determines HW Shutdown temperature features and measurement channel                      | AIO       |

Table 2.1 Pin Description for EMC2105

| PIN NUMBER<br>EMC2105 | PIN NAME            | PIN FUNCTION                                                                                                                                  | PIN TYPE |

|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 17                    | DN3 / DP4 / VIN3    | DN3 / DP4 - Negative (cathode) analog<br>input for External Diode 3 and positive<br>(anode) Analog Input for External Diode 4<br>(default)    | AIO (2V) |

|                       |                     | VIN3 - General voltage input for use with a thermistor                                                                                        | AI (2V)  |

| 18                    | DP3 / DN4 / VREF_T3 | DP3 / DN4 - Positive (anode) analog input<br>for External Diode 3 and negative<br>(cathode) analog input for External Diode<br>4<br>(default) | AIO (2V) |

|                       |                     | VREF_T3 - Reference output for use with a thermistor and to drive VIN3                                                                        | AIO (2V) |

| 19                    | DN2 / VIN2          | DN2 - Negative (cathode) analog input for External Diode 2. (default)                                                                         | AIO (2V) |

|                       |                     | VIN2 - General voltage input for use with a thermistor                                                                                        | AIO (2V) |

| 20                    | DP2 / VREF_T2       | DP2 - Positive (anode) analog input for External Diode 2. (default)                                                                           | AIO (2V) |

|                       |                     | VREF_T2 - Reference output for use with a thermistor and to drive VIN2                                                                        | AIO (2V) |

The pin type are described in detail below. All pins labelled with (5V) are 5V tolerant.

All pin labelled with (2V) should not be exposed to any voltage level greater than 2V.

Table 2.2 Pin Types

| PIN TYPE | DESCRIPTION                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------|

| Power    | This pin is used to supply power or ground to the device.                                               |

| DI       | Digital Input - this pin is used as a digital input. This pin is 5V tolerant.                           |

| Al       | Analog Input - this pin is used as an input for analog signals.                                         |

| AO       | Analog Output - this pin is used as an output for analog signals.                                       |

| AIO      | Analog Input / Output - this pin is used as an I/O for analog signals.                                  |

| DO       | Push / Pull Digital Output - this pin is used as a digital output. It can both source and sink current. |

## Table 2.2 Pin Types (continued)

| PIN TYPE | DESCRIPTION                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIOD     | Digital Input / Open Drain Output this pin is used as an digital I/O. When it is used as an output, It is open drain and requires a pull-up resistor. This pin is 5V tolerant. |

| OD       | Open Drain Digital Output - this pin is used as a digital output. It is open drain and requires a pull-up resistor. This pin is 5V tolerant.                                   |

# **Chapter 3 Electrical Specifications**

**Table 3.1 Absolute Maximum Ratings**

| Voltage on 5V tolerant pins including VDD_5V        | -0.3 to 6.5                   | V    |

|-----------------------------------------------------|-------------------------------|------|

| Voltage on VDD pin                                  | -0.3 to 4                     | V    |

| Voltage on 2V tolerant pins                         | -0.3 to 2.5                   | V    |

| Voltage on any other pin to GND                     | -0.3 to VDD + 0.3             | V    |

| Package Power Dissipation See Note 3.1              | 1 up to T <sub>A</sub> = 85°C | W    |

| Junction to Ambient (θ <sub>JA</sub> ) See Note 3.2 | 40                            | °C/W |

| Operating Ambient Temperature Range                 | -40 to 85°C                   | °C   |

| Storage Temperature Range                           | -55 to 150                    | °C   |

| ESD Rating, All Pins, HBM                           | 2000                          | V    |

Note: Stresses above those listed could cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other condition above those indicated in the operation sections of this specification is not implied. When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes on their outputs when the AC power is switched on or off. In addition, voltage transients on the AC power line may appear on the DC output. If this possibility exists, it is suggested that a clamp circuit be used.

- Note 3.1 All voltages are relative to ground.

- **Note 3.2** The Package Power Dissipation specification assumes a recommended thermal via design consisting of four 12mil vias connected to the ground plane with a 2x2mm thermal landing.

- Note 3.3 Junction to Ambient  $(\theta_{JA})$  is dependent on the design of the thermal vias. Without thermal vias and a thermal landing, the  $\theta_{JA}$  is approximately 52°C/W including localized PCB temperature increase.

## 3.1 Electrical Specifications

**Table 3.2 Electrical Specifications**

| VDD = 3V to 3.6V, VDD_5V = 4.5V to 5.5V, $T_A$ = -40°C to 85°C, all Typical values at $T_A$ = 27°C unless otherwise noted. |          |     |     |     |      |            |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|----------|-----|-----|-----|------|------------|--|--|--|

| CHARACTERISTIC                                                                                                             | SYMBOL   | MIN | TYP | MAX | UNIT | CONDITIONS |  |  |  |

|                                                                                                                            | DC Power |     |     |     |      |            |  |  |  |

| Supply Voltage                                                                                                             | $V_{DD}$ | 3   | 3.3 | 3.6 | V    |            |  |  |  |

| Supply Current (active)  2 3 mA 4 Conversions / second - Dynamic Averaging Enabled Fan Driver enabled                      |          |     |     |     |      |            |  |  |  |

#### Table 3.2 Electrical Specifications (continued)

VDD = 3V to 3.6V, VDD\_5V = 4.5V to 5.5V, T<sub>A</sub> = -40°C to 85°C, all Typical values at T<sub>A</sub> = 27°C unless otherwise

| CHARACTERISTIC                     | SYMBOL                | MIN              | TYP              | MAX         | UNIT | CONDITIONS                                                                     |

|------------------------------------|-----------------------|------------------|------------------|-------------|------|--------------------------------------------------------------------------------|

| Supply Current                     | I <sub>DD</sub>       |                  | 500              | 750         | uA   | 1 Conversions / second-<br>Dynamic Averaging disabled,<br>Fan Driver disabled. |

| Supply Current from VDD_5V         | I <sub>DD_5</sub>     |                  | 100              |             | uA   | Fan Driver enabled, No load current                                            |

| SMBus Delay                        | t <sub>SMB</sub>      |                  |                  | 15          | ms   | Delay from power to first SMBus communication                                  |

| Time to First Round<br>Robin       |                       |                  |                  | 300         | ms   |                                                                                |

|                                    |                       | Externa          | al Tempera       | ture Monito | ors  |                                                                                |

| Temperature<br>Accuracy            |                       |                  | ±0.25            | ±1          | °C   | 60°C < T <sub>DIODE</sub> < 110°C<br>30°C < T <sub>DIE</sub> < 85°C            |

|                                    |                       |                  | ±0.5             | ±2          | °C   | 0°C < T <sub>DIODE</sub> < 125°C,<br>0°C < T <sub>DIE</sub> < 115°C            |

| Temperature<br>Resolution          |                       |                  | 0.125            |             | °C   |                                                                                |

| Diode decoupling capacitor         | C <sub>FILTER</sub>   |                  | 2200             | 2700        | pF   | Connected across external diode, CPU, GPU, or AMD diode                        |

| Resistance Error<br>Corrected      | R <sub>SERIES</sub>   |                  |                  | 100         | Ohm  | Sum of series resistance in both DP and DN lines                               |

|                                    |                       | Intern           | al Tempera       | ture Monito | or   |                                                                                |

| Temperature<br>Accuracy            | T <sub>DIE</sub>      |                  | ±1               | ±2          | °C   | Note 3.4                                                                       |

| Temperature<br>Resolution          |                       |                  | 0.125            |             | °C   |                                                                                |

|                                    |                       | Vo               | ltage Meas       | surement    |      |                                                                                |

| Total Unadjusted<br>Error          | TUE                   |                  |                  | 1           | %    | Measured at 3/4 full scale                                                     |

| Reference Voltage                  | V <sub>REF</sub>      |                  | 800              |             | mV   |                                                                                |

| Reference Accuracy                 | $\Delta V_REF$        |                  | 1                |             | %    |                                                                                |

|                                    |                       | Hi               | gh Side Fa       | an Driver   |      |                                                                                |

| Output High Voltage from 5V supply | V <sub>OH_5V</sub>    | VDD_5V<br>- 0.35 | VDD_5<br>V - 0.3 |             | V    | I <sub>SOURCE</sub> = 600mA, VDD_5V = 5V                                       |

| Voltage Accuracy                   | $\Delta V_{FAN\_OUT}$ |                  | 1                | 2           | %    | Measured at 3/4 full scale -<br>Direct Setting Mode                            |

| Fan Drive Current                  | I <sub>SOURCE</sub>   |                  |                  | 600         | mA   |                                                                                |

| Overcurrent Limit                  | I <sub>OVER</sub>     |                  |                  | 2800        | mA   | Momentary Current drive at startup for < 2 seconds 1.5V < FAN_OUT < 3.5V       |

#### **Table 3.2 Electrical Specifications (continued)**

VDD = 3V to 3.6V, VDD\_5V = 4.5V to 5.5V,  $T_A$  = -40°C to 85°C, all Typical values at  $T_A$  = 27°C unless otherwise noted. **SYMBOL CHARACTERISTIC** MIN **TYP** MAX UNIT **CONDITIONS** DC Short Circuit 700 mA Sourcing current, Thermal I<sub>SHORT</sub> shutdown not triggered, FAN\_OUT = 0V **Current Limit** Short circuit delay 2 t<sub>DFS</sub> s  $Z_{\text{ESR}} < 100 \text{m}\Omega$  at 10 kHz**Output Capacitive** CLOAD 100 uF Load RPM Based Fan Controller **RPM** TACH 480 16000 Tachometer Range **Tachometer Setting** ±2 % External oscillator 32.768kHz  $\Delta_{\mathsf{TACH}}$ ±1 Accuracy Internal Oscillator 40°C < T<sub>DIE</sub> < 100°C %  $\Delta_{\mathsf{TACH}}$ ±2.5 ±5 Thermal Shutdown Thermal Shutdown TSD<sub>TH</sub> 150 °C Threshold Thermal Shutdown 50 °C TSD<sub>HYST</sub> Hysteresis Digital I/O pins Input High Voltage  $V_{IH}$ 2.0 ٧ Input Low Voltage  $V_{\mathsf{IL}}$ 8.0 ٧ Output High Voltage VDD -4 mA current drive ٧  $V_{OH}$ 0.4 Output Low Voltage  $V_{OL}$ 0.4 ٧ 4 mA current sink ALERT and SYS\_SHDN pins Leakage current ±5 uΑ  $I_{LEAK}$ Powered and unpowered

Note 3.4  $T_{DIE}$  refers to the internal die temperature and may not match  $T_A$  due to self heating of the device. The internal temperature sensor will return  $T_{DIE}$ .

# 3.2 SMBus Electrical Specifications (client mode)

**Table 3.3 SMBus Electrical Specifications**

| VDD= 3V to 3.6V                | /, T <sub>A</sub> = -40°C         | to 85°C      | Typical | values a | re at T <sub>A</sub> = | 27°C unless otherwise noted.      |  |  |  |

|--------------------------------|-----------------------------------|--------------|---------|----------|------------------------|-----------------------------------|--|--|--|

| CHARACTERISTIC                 | SYMBOL                            | MIN          | TYP     | MAX      | UNITS                  | CONDITIONS                        |  |  |  |

| SMBus Interface                |                                   |              |         |          |                        |                                   |  |  |  |

| Input High Voltage             | V <sub>IH</sub>                   | 2.0          |         |          | V                      |                                   |  |  |  |

| Input Low Voltage              | V <sub>IL</sub>                   |              |         | 0.8      | V                      |                                   |  |  |  |

| Output High Voltage            | V <sub>OH</sub>                   | VDD<br>- 0.4 |         |          | ٧                      |                                   |  |  |  |

| Output Low Voltage             | V <sub>OL</sub>                   |              |         | 0.4      | V                      | 4 mA current sink                 |  |  |  |

| Input High/Low Current         | I <sub>IH /</sub> I <sub>IL</sub> |              |         | ±5       | uA                     | Powered and unpowered             |  |  |  |

| Input Capacitance              | C <sub>IN</sub>                   |              | 5       |          | pF                     |                                   |  |  |  |

|                                |                                   |              | SMBu    | s Timing |                        |                                   |  |  |  |

| Clock Frequency                | f <sub>SMB</sub>                  | 10           |         | 400      | kHz                    |                                   |  |  |  |

| Spike Suppression              | t <sub>SP</sub>                   |              |         | 50       | ns                     |                                   |  |  |  |

| Bus free time Start to<br>Stop | t <sub>BUF</sub>                  | 1.3          |         |          | us                     |                                   |  |  |  |

| Setup Time: Start              | t <sub>SU:STA</sub>               | 0.6          |         |          | us                     |                                   |  |  |  |

| Setup Time: Stop               | t <sub>SU:STP</sub>               | 0.6          |         |          | us                     |                                   |  |  |  |

| Data Hold Time                 | t <sub>HD:DAT</sub>               | 0.6          |         | 6        | us                     |                                   |  |  |  |

| Data Setup Time                | t <sub>SU:DAT</sub>               | 0.6          |         | 72       | us                     |                                   |  |  |  |

| Clock Low Period               | t <sub>LOW</sub>                  | 1.3          |         |          | us                     |                                   |  |  |  |

| Clock High Period              | t <sub>HIGH</sub>                 | 0.6          |         |          | us                     |                                   |  |  |  |

| Clock/Data Fall time           | t <sub>FALL</sub>                 |              |         | 300      | ns                     | $Min = 20+0.1C_{LOAD} \text{ ns}$ |  |  |  |

| Clock/Data Rise time           | t <sub>RISE</sub>                 |              |         | 300      | ns                     | $Min = 20+0.1C_{LOAD} ns$         |  |  |  |

| Capacitive Load                | C <sub>LOAD</sub>                 |              |         | 400      | pF                     | per bus line                      |  |  |  |

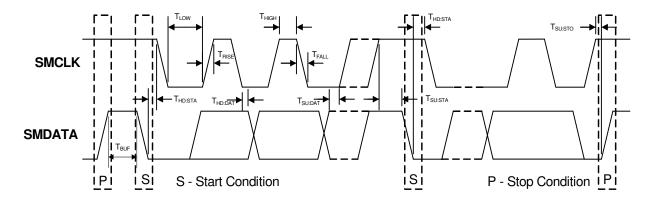

# **Chapter 4 Communications**

### 4.1 System Management Bus Interface Protocol

The EMC2105 communicates with a host controller, such as an SMSC SIO, through the SMBus. The SMBus is a two-wire serial communication protocol between a computer host and its peripheral devices. A detailed timing diagram is shown in Figure 4.1. Stretching of the SMCLK signal is supported, however the EMC2105 will not stretch the clock signal.

The EMC2105 powers up as an SMBus client.

Figure 4.1 SMBus Timing Diagram

The EMC2105 contains a single SMBus interface. . The EMC2105 client interfaces are SMBus 2.0 compatible and support Send Byte, Read Byte, Receive Byte and the Alert Response Address as valid protocols. These protocols are used as shown below.

All of the below protocols use the convention in Table 4.1.

**Table 4.1 Protocol Format**

| DATA SENT      | DATA SENT TO   |

|----------------|----------------|

| TO DEVICE      | THE HOST       |

| # of bits sent | # of bits sent |

## 4.2 Write Byte

The Write Byte is used to write one byte of data to the registers as shown below Table 4.2:

**Table 4.2 Write Byte Protocol**

| START  | SLAVE<br>ADDRESS | WR | ACK | REGISTER<br>ADDRESS | ACK | REGISTER<br>DATA | ACK | STOP   |

|--------|------------------|----|-----|---------------------|-----|------------------|-----|--------|

| 0 -> 1 | 0101_111         | 0  | 0   | XXh                 | 0   | XXh              | 0   | 1 -> 0 |

## 4.3 Read Byte

The Read Byte protocol is used to read one byte of data from the registers as shown in Table 4.3.

**Table 4.3 Read Byte Protocol**

| START  | SLAVE<br>ADDRESS | WR | ACK | Register<br>Address | ACK | START  | Slave<br>Address | RD | ACK | Register<br>Data | NACK | STOP   |

|--------|------------------|----|-----|---------------------|-----|--------|------------------|----|-----|------------------|------|--------|

| 0 -> 1 | 0101_111         | 0  | 0   | XXh                 | 0   | 0 -> 1 | 0101_111         | 1  | 0   | XXh              | 1    | 1 -> 0 |

## 4.4 Send Byte

The Send Byte protocol is used to set the internal address register pointer to the correct address location. No data is transferred during the Send Byte protocol as shown in Table 4.4.

Table 4.4 Send Byte Protocol

| START  | SLAVE<br>ADDRESS | WR | ACK | REGISTER<br>ADDRESS | ACK | STOP   |

|--------|------------------|----|-----|---------------------|-----|--------|

| 0 -> 1 | 0101_111         | 0  | 0   | XXh                 | 0   | 1 -> 0 |

## 4.5 Receive Byte

The Receive Byte protocol is used to read data from a register when the internal register address pointer is known to be at the right location (e.g. set via Send Byte). This is used for consecutive reads of the same register as shown in Table 4.5.

Table 4.5 Receive Byte Protocol

| START  | SLAVE<br>ADDRESS | RD | ACK | REGISTER DATA | NACK | STOP   |

|--------|------------------|----|-----|---------------|------|--------|

| 0 -> 1 | 0101_111         | 1  | 0   | XXh           | 1    | 1 -> 0 |

## 4.6 Alert Response Address

The ALERT# output can be used as a processor interrupt or as an SMBus Alert when configured to operate as an interrupt.

When it detects that the ALERT# pin is asserted, the host will send the Alert Response Address (ARA) to the general address of 0001\_100xb. All devices with active interrupts will respond with their client address as shown in Table 4.6.

**Table 4.6 Alert Response Address Protocol**

| START  | ALERT<br>RESPONSE<br>ADDRESS | RD | ACK | DEVICE<br>ADDRESS | NACK | STOP   |

|--------|------------------------------|----|-----|-------------------|------|--------|

| 0 -> 1 | 0001_100                     | 1  | 0   | 0101_111          | 1    | 1 -> 0 |

The EMC2105 will respond to the ARA in the following way if the ALERT# pin is asserted.

- 1. Send Slave Address and verify that full slave address was sent (i.e. the SMBus communication from the device was not prematurely stopped due to a bus contention event).

- 2. Set the MASK bit to clear the ALERT# pin.

#### 4.7 SMBus Address

The EMC2105 SMBus Address is fixed at 0101\_111xb.

Attempting to communicate with the EMC2105 SMBus interface with an invalid slave address or invalid protocol will result in no response from the device and will not affect its register contents.

#### 4.8 SMBus Time-out

The EMC2105 includes an SMBus time-out feature. Following a 30ms period of inactivity on the SMBus, the device will time-out and reset the SMBus interface. The SMBus Timeout defaults to enabled and can be disabled by setting the DIS\_TO bit in the Configuration 2 register.

# **Chapter 5 Product Description**

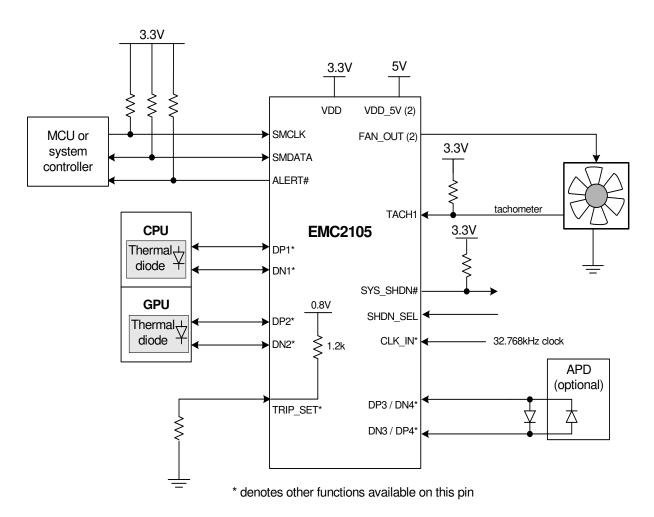

The EMC2105 is an SMBus compliant fan controller with up to four (up to 4 external) temperature channels. It contains a single High Side fan driver capable of sourcing up to 600mA from a 5V supply. The fan driver can be operated using two methods each with two modes. The methods include an RPM based Fan Speed Control Algorithm and a direct fan drive setting. The modes include manually programming the desired settings or using the internal programmable temperature look-up table to select the desired setting based on measured temperature.

The temperature monitors offer 1°C accuracy (for external diodes) with sophisticated features to reduce errors introduced by series resistance and beta variation of substrate thermal diode transistors commonly found in processors (including support for BJT or transistor model for CPU diodes).

The EMC2105 also includes a hardware programmable temperature limit and dedicated system shutdown output for thermal protection of critical circuitry. Any of the three temperature channels can be configured to measure a thermistor or voltage channel using a precision reference voltage for reduced system complexity.

Figure 5.1 shows a system diagram of the EMC2105.

Figure 5.1 System Diagram of EMC2105

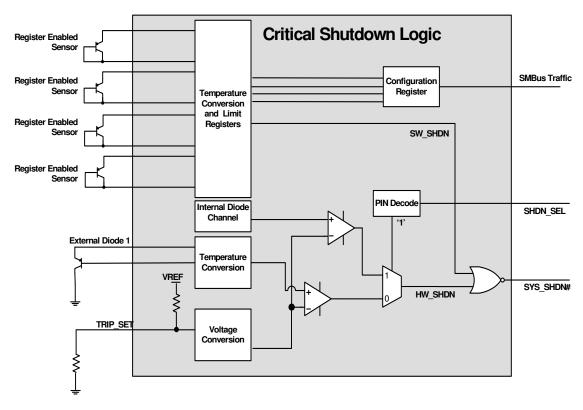

#### 5.1 Critical/Thermal Shutdown

The EMC2105 provides a hardware Critical/Thermal Shutdown function for systems. Figure 5.2 is a block diagram of this Critical/Thermal Shutdown function. The Critical/Thermal Shutdown function in the EMC2105 accepts configuration information from the fixed states of the SHDN\_SEL pin as described in Section 5.1.1.

Each of the software programmed temperature limits can be optionally configured to act as inputs to the Critical / Thermal Shutdown independent of the hardware shutdown operation. When configured to operate this way, the SYS\_SHDN# pin will be asserted when the temperature meets or exceeds the limit. The pin will be released when the temperature drops below the limit however the individual status bits will not be cleared if set (see Section 6.13).

The analog portion of the Critical/Thermal Shutdown function monitors the hardware determined temperature channel (see Section 5.1.1). This measured temperature is then compared with TRIP\_SET point. This TRIP\_SET point is set by the system designer with a single external resistor divider as described in Section 5.1.2.

The SYS\_SHDN# is asserted when the indicated temperature exceeds the temperature threshold established by the TRIP\_SET input pin for a number of consecutive measurements defined by the fault queue. If the HW\_SHDN output is asserted and the temperature drops below the Thermal / Critical Shutdown threshold then it will be set to a logic '0' state.

Figure 5.2 EMC2105 Critical/Thermal Shutdown Block Diagram

#### 5.1.1 SHDN SEL Pin

The EMC2105 has a 'strappable' input (SHDN\_SEL) allowing for configuration of the hardware Critical/Thermal Shutdown input channels. This pin has 3 possible states and is monitored and decoded by the EMC2105 at power-up. The three possible states are 0 (tied to GND), 1 (tied to 3.3V) or High-Z (open). The state of this pin determines which external diode configuration is used for the Critical / Thermal shutdown function.

The different configurations of the SHDN\_SELpin are described in Table 5.1. SHDN\_SEL applies only to the selected temperature channel.

| SHDN_SEL      | FUNCTION<br>NAME                            | TEMPERATURE MONITORING FEATURES                                                                                                                                                                                 | CRITICAL / THERMAL<br>SHUTDOWN RANGE |

|---------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 0             | Intel Transistor<br>Mode (substrate<br>PNP) | The external diode 1 channel is configured with Beta Compensation enabled and Resistance Error Correction enabled. This mode is ideal for monitoring a substrate transistor such as an Intel CPU thermal diode. | High - 92°C to 154°C                 |

| High-Z (open) | AMD CPU /<br>Diode Mode                     | The external diode 1channel is configured with Beta Compensation disabled and Resistance Error Correction disabled. This mode is ideal for monitoring an AMD processor diode or a 2N3904 diode.                 | Low - 60°C to 122°C                  |

| 1             | Internal                                    | The internal diode is linked to the Hardware set Thermal / Critical shutdown circuitry and the SYS_SHDN# pin.                                                                                                   | Low - 60°C to 122°C                  |

Table 5.1 SHDN SEL Pin Configuration

#### 5.1.2 TRIP\_SET / VIN4 Pin

The EMC2105's TRIP\_SET / VIN4 pin is an analog input to the Critical/Thermal Shutdown block which sets the Thermal Shutdown temperature. The system designer creates a voltage level at the input through a simple resistor connected to GND as shown in Figure 5.1. The value of this resistor is used to create an input voltage on the TRIP\_SET / VIN4 pin which is translated into a temperature ranging from 60°C to 122°C or 90°C to 152°C as enumerated in Table 5.2.

When the SHDN\_SEL pin is pulled to '1' at power up, then the TRIP\_SET / VIN4 pin is configured to measure VIN4 as its primary function. The circuitry will still calculate the thermal / critical shutdown threshold based on the voltage and compare this temperature against the Internal Diode temperature. This will cause the SYS\_SHDN# pin to assert if the measured temperature exceeds this threshold. The device will also compare the measured voltage against the VIN4 High and Low limits. This function is not available if SHDN SEL is set to '0' or 'High-Z' at power up.

**APPLICATION NOTE:** If the SHDN\_SEL pin is pulled to '1' at power up and the TRIP\_SET / VIN4 pin is intended for use as a voltage input then the SYS SHDN# pin should be ignored.

**APPLICATION NOTE:** If the SHDN\_SEL pin is pulled to '1' at power up and the TRIP\_SET / VIN4 pin is intended to be used to set a threshold level then the VIN4 channel should be masked. Furthermore, the voltage on the pin must be externally generated based on Equation [1]. Do not use Table 5.2.

**APPLICATION NOTE:** When used in its TRIP\_SET mode (i.e. the SHDN\_SEL pin is not set to a logic '1'), current only flows when the TRIP\_SET / VIN4 pin is being monitored. At all other times, the internal reference voltage is removed and the TRIP\_SET / VIN4 pin will be pulled down to ground.

**APPLICATION NOTE:** The TRIP\_SET / VIN4 pin circuitry is designed to use a 1% resistor externally. Using a 1% resistor will result in the Thermal / Critical Shutdown temperature being decoded correctly. If a 5% resistor is used, then the Thermal / Critical Shutdown temperature may be decoded with as much as  $\pm 1^{\circ}$ C error.

$$V_{TRIP} = \frac{T_{TRIP} - T_{MIN}}{80}$$

V<sub>TRIP</sub> is the TRIP\_SET voltage

T<sub>MIN</sub> is the minimum temperature based on the range

[1]

Table 5.2 TRIP\_SET Resistor Setting

| T <sub>TRIP</sub> (°C)<br>LOW RANGE | T <sub>TRIP</sub> (°C)<br>HIGH RANGE | RSET (1%) | T <sub>TRIP</sub> (°C)<br>LOW RANGE | T <sub>TRIP</sub> (°C)<br>HIGH RANGE | RSET (1%) |

|-------------------------------------|--------------------------------------|-----------|-------------------------------------|--------------------------------------|-----------|

| 60                                  | 92                                   | 0.0       | 92                                  | 124                                  | 1240      |

| 61                                  | 93                                   | 28.7      | 93                                  | 125                                  | 1330      |

| 62                                  | 94                                   | 48.7      | 94                                  | 126                                  | 1400      |

| 63                                  | 95                                   | 69.8      | 95                                  | 127                                  | 1500      |

| 64                                  | 96                                   | 90.9      | 96                                  | 128                                  | 1580      |

| 65                                  | 97                                   | 113       | 97                                  | 129                                  | 1690      |

| 66                                  | 98                                   | 137       | 98                                  | 130                                  | 1820      |

| 67                                  | 99                                   | 158       | 99                                  | 131                                  | 1960      |

| 68                                  | 100                                  | 182       | 100                                 | 132                                  | 2050      |

| 69                                  | 101                                  | 210       | 101                                 | 133                                  | 2210      |

| 70                                  | 102                                  | 237       | 102                                 | 134                                  | 2370      |

| 71                                  | 103                                  | 261       | 103                                 | 135                                  | 2550      |

| 72                                  | 104                                  | 294       | 104                                 | 136                                  | 2740      |

| 73                                  | 105                                  | 324       | 105                                 | 137                                  | 2940      |

| 74                                  | 106                                  | 348       | 106                                 | 138                                  | 3160      |

| 75                                  | 107                                  | 383       | 107                                 | 139                                  | 3480      |

| 76                                  | 108                                  | 412       | 108                                 | 140                                  | 3740      |

| 77                                  | 109                                  | 453       | 109                                 | 141                                  | 4120      |

| 78                                  | 110                                  | 487       | 110                                 | 142                                  | 4530      |

| 79                                  | 111                                  | 523       | 111                                 | 143                                  | 4990      |

| 80                                  | 112                                  | 562       | 112                                 | 144                                  | 5490      |

| 81                                  | 113                                  | 604       | 113                                 | 145                                  | 6040      |

| 82                                  | 114                                  | 649       | 114                                 | 146                                  | 6810      |

Table 5.2 TRIP SET Resistor Setting (continued)

| T <sub>TRIP</sub> (°C)<br>LOW RANGE | T <sub>TRIP</sub> (°C)<br>HIGH RANGE | RSET (1%) | T <sub>TRIP</sub> (°C)<br>LOW RANGE | T <sub>TRIP</sub> (°C)<br>HIGH RANGE | RSET (1%) |

|-------------------------------------|--------------------------------------|-----------|-------------------------------------|--------------------------------------|-----------|

| 83                                  | 115                                  | 698       | 115                                 | 147                                  | 7870      |

| 84                                  | 116                                  | 750       | 116                                 | 148                                  | 9090      |

| 85                                  | 117                                  | 787       | 117                                 | 149                                  | 10700     |

| 86                                  | 118                                  | 845       | 118                                 | 150                                  | 12700     |

| 87                                  | 119                                  | 909       | 119                                 | 151                                  | 15800     |

| 88                                  | 120                                  | 953       | 120                                 | 152                                  | 20500     |

| 89                                  | 121                                  | 1020      | 121                                 | 153                                  | 29400     |

| 90                                  | 122                                  | 1100      | 122                                 | 154                                  | 49900     |

| 91                                  | 123                                  | 1150      | 60                                  | 92                                   | Open      |

## 5.2 Fan Control Modes of Operation

The EMC2105 has four modes of operation for the fan driver. Each mode of operation uses the Ramp Rate control and Spin Up Routine.

- 1. Direct Setting Mode- in this mode of operation, the user directly controls the fan drive setting. Updating the Fan Driver Setting Register (see Section 6.18) will instantly update the fan drive. Ramp Rate control is optional and enabled via the EN RRC bits.

- This is the default mode. The Direct Setting Mode is enabled by clearing the LUT\_LOCK bit in the Look Up Table Configuration Register (see Section 6.29) while the TACH / DRIVE bit is set to '0'.

- Whenever the Direct Setting Mode is enabled the current drive will be changed to what was last written into the Fan Driver Setting Register.

- 2. Fan Speed Control Mode (FSC) in this mode of operation, the user determines a target tachometer count and the drive setting is automatically updated to achieve this target speed. The algorithm uses the Spin Up Routine and has user definable ramp rate controls.

- This mode is enabled by clearing the LUT\_LOCK bit in the Look Up Table (LUT) Configuration Register and setting the EN ALGO bit in the Fan Configuration Register.

- 3. Using the Look Up Table with Fan Drive Settings (Direct Setting w/ LUT Mode) In this mode of operation, the user programs the Look Up Table with fan drive settings and corresponding temperature thresholds. The fan drive is set based on the measured temperatures and the corresponding drive settings. Ramp Rate control is optional and enabled via the EN\_RRC bits.

- This mode is enabled by programming the Look Up Table then setting the LUT\_LOCK bit while the TACH / DRIVE bit is set to '1'.

- The TACH / DRIVE bit in the Look Up Table Configuration Register MUST be set to '1' or the fan drive settings will be incorrectly set. Setting this bit to '1' ensures the settings will be PWM settings.

- 4. Using the Look Up Table with RPM Target Settings (FSC w/ LUT Mode) In this mode of operation, the user programs the Look Up Table with TACH Target values and corresponding temperature thresholds. The TACH Target will be set based on the measured temperatures and the corresponding target settings. The fan drive settings will be determined automatically based on the RPM based Fan Speed Control Algorithm.

- This mode is enabled by programming the Look Up Table then setting the LUT\_LOCK bit while the TACH / DRIVE bit is set to '0'.