# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **APEX 20KC**

#### Programmable Logic Device

#### February 2004 ver. 2.2

Data Sheet

#### Features...

Programmable logic device (PLD) manufactured using a 0.15-µm alllayer copper-metal fabrication process

- − 25 to 35% faster design performance than APEX<sup>TM</sup> 20KE devices

- Pin-compatible with APEX 20KE devices

- High-performance, low-power copper interconnect

- MultiCore<sup>™</sup> architecture integrating look-up table (LUT) logic and embedded memory

- LUT logic used for register-intensive functions

- Embedded system blocks (ESBs) used to implement memory functions, including first-in first-out (FIFO) buffers, dual-port RAM, and content-addressable memory (CAM)

- High-density architecture

- 200,000 to 1 million typical gates (see Table 1)

- Up to 38,400 logic elements (LEs)

- Up to 327,680 RAM bits that can be used without reducing available logic

| Table 1. APEX 20KC Device FeaturesNote (1) |            |            |            |            |  |  |

|--------------------------------------------|------------|------------|------------|------------|--|--|

| Feature                                    | EP20K200C  | EP20K400C  | EP20K600C  | EP20K1000C |  |  |

| Maximum system gates                       | 526,000    | 1,052,000  | 1,537,000  | 1,772,000  |  |  |

| Typical gates                              | 200,000    | 400,000    | 600,000    | 1,000,000  |  |  |

| LEs                                        | 8,320      | 16,640     | 24,320     | 38,400     |  |  |

| ESBs                                       | 52         | 104        | 152        | 160        |  |  |

| Maximum RAM bits                           | 106,496    | 212,992    | 311,296    | 327,680    |  |  |

| PLLs (2)                                   | 2          | 4          | 4          | 4          |  |  |

| Speed grades (3)                           | -7, -8, -9 | -7, -8, -9 | -7, -8, -9 | -7, -8, -9 |  |  |

| Maximum macrocells                         | 832        | 1,664      | 2,432      | 2,560      |  |  |

| Maximum user I/O pins                      | 376        | 488        | 588        | 708        |  |  |

#### Notes to Table 1:

The embedded IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan circuitry contributes up to 57,000 additional gates.

- (2) PLL: phase-locked loop.

- (3) The -7 speed grade provides the fastest performance.

| and More<br>Features | <ul> <li>Low-power operation design</li> <li>1.8-V supply voltage (see Table</li> <li>Copper interconnect reduces point</li> </ul> |                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|                      | <ul> <li>MultiVolt™ I/O support for 1.3</li> </ul>                                                                                 |                                   |

|                      | <ul> <li>ESBs offering programmable p</li> </ul>                                                                                   |                                   |

|                      | <ul> <li>Flexible clock management circuitry</li> </ul>                                                                            |                                   |

|                      | loops (PLLs)                                                                                                                       | 1 1                               |

|                      | <ul> <li>Built-in low-skew clock tree</li> </ul>                                                                                   |                                   |

|                      | <ul> <li>Up to eight global clock signals</li> </ul>                                                                               |                                   |

|                      | <ul> <li>ClockLock<sup>TM</sup> feature reducing of</li> </ul>                                                                     | clock delay and skew              |

|                      | <ul> <li>ClockBoost<sup>™</sup> feature providing<br/>division</li> </ul>                                                          | g clock multiplication and        |

|                      |                                                                                                                                    | programmable clock phase and      |

|                      | delay shifting                                                                                                                     | 1 0 1                             |

|                      | <ul> <li>Powerful I/O features</li> </ul>                                                                                          |                                   |

|                      | - Compliant with peripheral con                                                                                                    |                                   |

|                      | Interest Group (PCI SIG) PCI L<br>Regulation 2.2 for 3.3-V operation                                                               | at 33 or 66 MHz and 32 or 64 bits |

|                      | <ul> <li>Support for high-speed externa</li> </ul>                                                                                 |                                   |

|                      | synchronous dynamic RAM (S                                                                                                         |                                   |

|                      | (SRAM)                                                                                                                             |                                   |

|                      | – 16 input and 16 output LVDS c                                                                                                    | hannels at 840 megabits per       |

|                      | second (Mbps)                                                                                                                      |                                   |

|                      | - Direct connection from 1/O pir<br>fast $t_{CO}$ and $t_{SU}$ times for comp                                                      | s to local interconnect providing |

|                      | <ul> <li>MultiVolt I/O support for 1.8-Y</li> </ul>                                                                                |                                   |

|                      | <ul> <li>Programmable clamp to V<sub>CCIO</sub></li> </ul>                                                                         |                                   |

|                      | <ul> <li>Individual tri-state output enal</li> </ul>                                                                               |                                   |

|                      | <ul> <li>Programmable output slew-rat<br/>noise</li> </ul>                                                                         |                                   |

|                      | <ul> <li>Support for advanced I/O stan</li> </ul>                                                                                  | dards, including low-voltage      |

|                      | differential signaling (LVDS), I                                                                                                   |                                   |

|                      | SSTL-3 and SSTL-2, GTL+, and                                                                                                       | HSTL Class I                      |

|                      | <ul> <li>Supports hot-socketing operati</li> </ul>                                                                                 |                                   |

|                      | <ul> <li>Pull-up on I/O pins before and</li> </ul>                                                                                 | during configuration              |

|                      | Table 2. APEX 20KC Supply Voltages                                                                                                 |                                   |

|                      | Feature                                                                                                                            | Voltage                           |

|                      | Internal supply voltage (V <sub>CCINT</sub> )                                                                                      | 1.8 V                             |

|                      | MultiVolt I/O interface voltage levels (V <sub>CCIO</sub> )                                                                        | 1.8 V, 2.5 V, 3.3 V, 5.0 V (1)    |

|                      | Note to Table 2:<br>(1) APEX 20KC devices can be 5.0-V tolerant b                                                                  | y using an external resistor.     |

- Advanced interconnect structure

- Copper interconnect for high performance

- Four-level hierarchical FastTrack<sup>®</sup> interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

- Advanced software support

- Software design support and automatic place-and-route provided by the Altera<sup>®</sup> Quartus<sup>™</sup> II development system for Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations

- Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions optimized for APEX 20KC architecture available

- NativeLink<sup>™</sup> integration with popular synthesis, simulation, and timing analysis tools

- Quartus II SignalTap<sup>®</sup> embedded logic analyzer simplifies in-system design evaluation by giving access to internal nodes during device operation

- Supports popular revision-control software packages including PVCS, RCS, and SCCS

| Table 3. APE | Notes (1), (2) |             |     |     |

|--------------|----------------|-------------|-----|-----|

| Device       | 208-Pin PQFP   | 652-Pin BGA |     |     |

| EP20K200C    | 136            | 168         | 271 |     |

| EP20K400C    |                |             |     | 488 |

| EP20K600C    |                |             |     | 488 |

| EP20K1000C   |                |             |     | 488 |

| Table 4. APEX 20KC FineLine BGA Package Options & I/O Count Notes (1), (2) |     |                |     |  |  |  |

|----------------------------------------------------------------------------|-----|----------------|-----|--|--|--|

| Device         484 Pin         672 Pin         1,020 Pin                   |     |                |     |  |  |  |

| EP20K200C                                                                  | 376 |                |     |  |  |  |

| EP20K400C                                                                  |     | 488 (3)        |     |  |  |  |

| EP20K600C                                                                  |     | 508 (3)        | 588 |  |  |  |

| EP20K1000C                                                                 |     | 508 <i>(3)</i> | 708 |  |  |  |

#### Notes to Tables 3 and 4:

- (1) I/O counts include dedicated input and clock pins.

- (2) APEX 20KC device package types include plastic quad flat pack (PQFP), 1.27-mm pitch ball-grid array (BGA), and 1.00-mm pitch FineLine BGA<sup>™</sup> packages.

- (3) This device uses a thermally enhanced package, which is taller than the regular package. Consult the *Altera Device Package Information Data Sheet* for detailed package size information.

| Table 5. APEX 20KC QFP & BGA Package Sizes                                              |                                      |                                      |             |                 |  |  |  |

|-----------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|-------------|-----------------|--|--|--|

| Feature         208-Pin PQFP         240-Pin PQFP         356-Pin BGA         652-Pin B |                                      |                                      |             |                 |  |  |  |

| Pitch (mm)                                                                              | 0.50                                 | 0.50                                 | 1.27        | 1.27            |  |  |  |

| Area (mm <sup>2</sup> )                                                                 | 924                                  | 1,218                                | 1,225       | 2,025           |  |  |  |

| Length $\times$ Width (mm $\times$ mm)                                                  | $\textbf{30.4} \times \textbf{30.4}$ | $\textbf{34.9} \times \textbf{34.9}$ | 35.0 × 35.0 | 45.0 	imes 45.0 |  |  |  |

| Table 6. APEX 20KC FineLine BGA Package Sizes |         |         |         |  |  |  |

|-----------------------------------------------|---------|---------|---------|--|--|--|

| Feature 484 Pin 672 Pin 1,020 Pin             |         |         |         |  |  |  |

| Pitch (mm)                                    | 1.00    | 1.00    | 1.00    |  |  |  |

| Area (mm <sup>2</sup> )                       | 529     | 729     | 1,089   |  |  |  |

| Length $\times$ Width (mm $\times$ mm)        | 23 × 23 | 27 × 27 | 33 × 33 |  |  |  |

### General Description

Similar to APEX 20K and APEX 20KE devices, APEX 20KC devices offer the MultiCore architecture, which combines the strengths of LUT-based and product-term-based devices with an enhanced memory structure. LUT-based logic provides optimized performance and efficiency for datapath, register-intensive, mathematical, or digital signal processing (DSP) designs. Product-term-based logic is optimized for complex combinatorial paths, such as complex state machines. LUT- and productterm-based logic combined with memory functions and a wide variety of MegaCore and AMPP functions make the APEX 20KC architecture uniquely suited for SOPC designs. Applications historically requiring a combination of LUT-, product-term-, and memory-based devices can now be integrated into one APEX 20KC device. APEX 20KC devices include additional features such as enhanced I/O standard support, CAM, additional global clocks, and enhanced ClockLock clock circuitry. Table 7 shows the features included in APEX 20KC devices.

| Table 7. APEX 20KC Device Features (Part 1 of 2) |                                                                                                                                                                                                                              |  |  |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Feature                                          | APEX 20KC Devices                                                                                                                                                                                                            |  |  |  |  |

| MultiCore system integration                     | Full support                                                                                                                                                                                                                 |  |  |  |  |

| Hot-socketing support                            | Full support                                                                                                                                                                                                                 |  |  |  |  |

| SignalTap logic analysis                         | Full support                                                                                                                                                                                                                 |  |  |  |  |

| 32-/64-bit, 33-MHz PCI                           | Full compliance                                                                                                                                                                                                              |  |  |  |  |

| 32-/64-bit, 66-MHz PCI                           | Full compliance in -7 and -8 speed grades in selected devices                                                                                                                                                                |  |  |  |  |

| MultiVolt I/O                                    | 1.8-V, 2.5-V, or 3.3-V $V_{CCIO}$<br>V <sub>CCIO</sub> selected bank by bank<br>5.0-V tolerant with use of external resistor                                                                                                 |  |  |  |  |

| ClockLock support                                | Clock delay reduction<br>$m/(n \times v)$ clock multiplication<br>Drive ClockLock output off-chip<br>External clock feedback<br>ClockShift circuitry<br>LVDS support<br>Up to four PLLs<br>ClockShift clock phase adjustment |  |  |  |  |

| Dedicated clock and input pins Eight             |                                                                                                                                                                                                                              |  |  |  |  |

| Feature              | APEX 20KC Devices                               |

|----------------------|-------------------------------------------------|

| I/O standard support | 1.8-V, 2.5-V, 3.3-V, 5.0-V I/O                  |

|                      | 3.3-V PCI and PCI-X                             |

|                      | 3.3-V AGP                                       |

|                      | CTT                                             |

|                      | GTL+                                            |

|                      | LVCMOS                                          |

|                      | LVTTL                                           |

|                      | True-LVDS <sup>™</sup> and LVPECL data pins (in |

|                      | EP20K400C and larger devices)                   |

|                      | LVDS and LVPECL clock pins (in all devices      |

|                      | LVDS and LVPECL data pins up to 156 Mbp         |

|                      | (in EP20K200C devices)                          |

|                      | HSTL Class I                                    |

|                      | PCI-X                                           |

|                      | SSTL-2 Class I and II                           |

|                      | SSTL-3 Class I and II                           |

| Memory support       | CAM                                             |

|                      | Dual-port RAM                                   |

|                      | FIFO                                            |

|                      | RAM                                             |

|                      | ROM                                             |

All APEX 20KC devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault-coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different application-specific integrated circuit (ASIC) designs; APEX 20KC devices can be configured on the board for the specific functionality required.

APEX 20KC devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable EPC16, EPC8, EPC4, EPC2, and EPC1 configuration devices and one-time programmable (OTP) EPC1 configuration devices, which configure APEX 20KC devices via a serial data stream. Moreover, APEX 20KC devices contain an optimized interface that permits microprocessors to configure APEX 20KC devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat APEX 20KC devices as memory and configure the device by writing to a virtual memory location, making reconfiguration easy. After an APEX 20KC device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

APEX 20KC devices are supported by the Altera Quartus II development system, a single, integrated package that offers HDL and schematic design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, SignalTap logic analysis, and device configuration. The Quartus II software runs on Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations.

The Quartus II software provides NativeLink interfaces to other industrystandard PC- and UNIX workstation-based EDA tools. For example, designers can invoke the Quartus II software from within third-party design tools. Further, the Quartus II software contains built-in optimized synthesis libraries; synthesis tools can use these libraries to optimize designs for APEX 20KC devices. For example, the Synopsys Design Compiler library, supplied with the Quartus II development system, includes DesignWare functions optimized for the APEX 20KC architecture.

## Functional Description

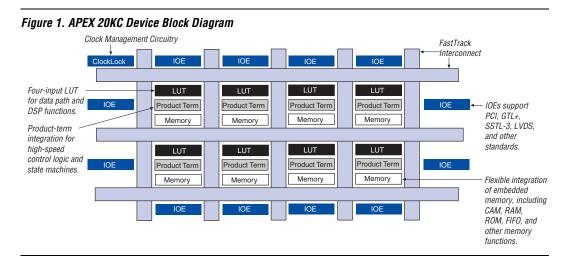

APEX 20KC devices incorporate LUT-based logic, product-term-based logic, and memory into one device on an all-copper technology process. Signal interconnections within APEX 20KC devices (as well as to and from device pins) are provided by the FastTrack interconnect—a series of fast, continuous row and column channels that run the entire length and width of the device.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack interconnect. Each IOE contains a bidirectional I/O buffer and a register that can be used as either an input or output register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. IOEs provide a variety of features, such as 3.3-V, 64-bit, 66-MHz PCI compliance; JTAG BST support; slew-rate control; and tri-state buffers. APEX 20KC devices offer enhanced I/O support, including support for 1.8-V I/O, 2.5-V I/O, LVCMOS, LVTTL, LVPECL, 3.3-V PCI, PCI-X, LVDS, GTL+, SSTL-2, SSTL-3, HSTL, CTT, and 3.3-V AGP I/O standards. The ESB can implement a variety of memory functions, including CAM, RAM, dual-port RAM, ROM, and FIFO functions. Embedding the memory directly into the die improves performance and reduces die area compared to distributed-RAM implementations. Moreover, the abundance of cascadable ESBs allows APEX 20KC devices to implement multiple wide memory blocks for high-density designs. The ESB's high speed ensures it can implement small memory blocks without any speed penalty. Additionally, designers can use the ESBs to create as many different-sized memory blocks as the system requires. Figure 1 shows an overview of the APEX 20KC device.

APEX 20KC devices provide four dedicated clock pins and four dedicated input pins that drive register control inputs. These signals ensure efficient distribution of high-speed, low-skew control signals, which use dedicated routing channels to provide short delays and low skews. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or internally generated asynchronous clear signals with high fan-out. The dedicated clock pins featured on the APEX 20KC devices can also feed logic. The devices also feature ClockLock and ClockBoost clock management circuitry.

#### **Altera Corporation**

#### **MegaLAB Structure**

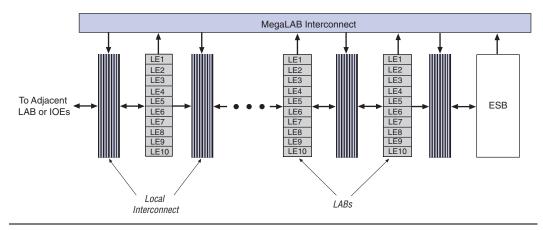

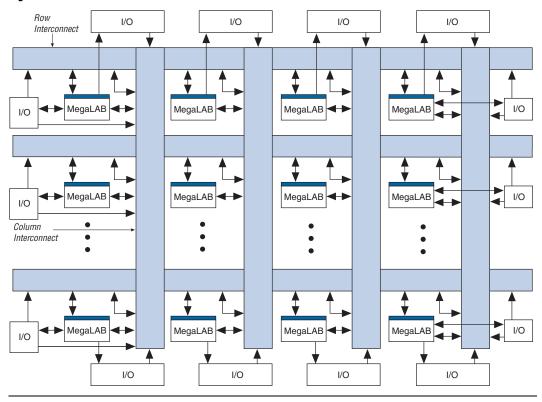

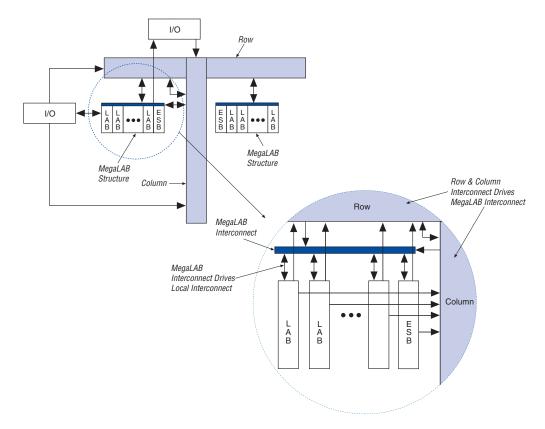

APEX 20KC devices are constructed from a series of MegaLAB<sup>™</sup> structures. Each MegaLAB structure contains 16 logic array blocks (LABs), one ESB, and a MegaLAB interconnect, which routes signals within the MegaLAB structure. In EP20K1000C devices, MegaLAB structures contain 24 LABs. Signals are routed between MegaLAB structures and I/O pins via the FastTrack interconnect. In addition, edge LABs can be driven by I/O pins through the local interconnect. Figure 2 shows the MegaLAB structure.

Figure 2. MegaLAB Structure

#### **Logic Array Block**

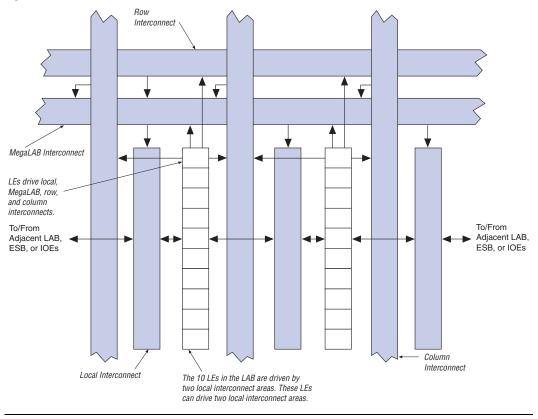

Each LAB consists of 10 LEs, the LEs' associated carry and cascade chains, LAB control signals, and the local interconnect. The local interconnect transfers signals between LEs in the same or adjacent LABs, IOEs, or ESBs. The Quartus II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of a fast local interconnect for high performance. Figure 3 shows the APEX 20KC LAB.

APEX 20KC devices use an interleaved LAB structure. This structure allows each LE to drive two local interconnect areas, minimizing the use of the MegaLAB and FastTrack interconnect and providing higher performance and flexibility. Each LE can drive 29 other LEs through the fast local interconnect.

#### Figure 3. LAB Structure

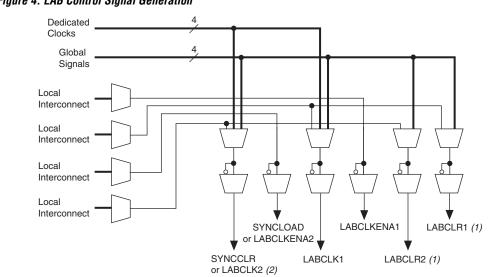

Each LAB contains dedicated logic for driving control signals to its LEs and ESBs. The control signals include clock, clock enable, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, and synchronous load signals. A maximum of six control signals can be used at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked (e.g., any LE in a particular LAB using CLK1 will also use CLKENA1). LEs with the same clock but different clock enable signals either use both clock signals in one LAB or are placed into separate LABs.

If both the rising and falling edges of a clock are used in a LAB, both LABwide clock signals are used. The LAB-wide control signals can be generated from the LAB local interconnect, global signals, and dedicated clock pins. The inherent low skew of the FastTrack interconnect enables it to be used for clock distribution. Figure 4 shows the LAB control signal generation circuit.

#### Figure 4. LAB Control Signal Generation

#### Notes to Figure 4:

- The LABCLR1 and LABCLR2 signals also control asynchronous load and asynchronous preset for LEs within the LAB.

- (2) The SYNCCLR signal can be generated by the local interconnect or global signals.

#### Logic Element

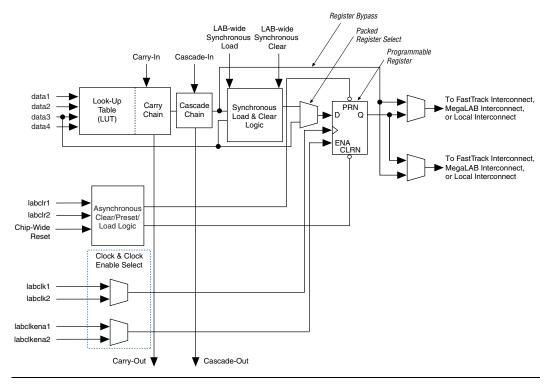

The LE, the smallest unit of logic in the APEX 20KC architecture, is compact and provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. In addition, each LE contains a programmable register and carry and cascade chains. Each LE drives the local interconnect, MegaLAB interconnect, and FastTrack interconnect routing structures. See Figure 5.

#### Figure 5. APEX 20KC Logic Element

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives the outputs of the LE.

Each LE has two outputs that drive the local, MegaLAB, or FastTrack interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

The APEX 20KC architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equality comparators with minimum delay. Carry and cascade chains connect LEs 1 through 10 in an LAB and all LABs in the same MegaLAB structure.

#### Carry Chain

The carry chain provides a very fast carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higherorder bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the APEX 20KC architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Quartus II Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as DesignWare functions from Synopsys and library of parameterized modules (LPM) functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than ten LEs by automatically linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a MegaLAB structure. A carry chain longer than one LAB skips either from an even-numbered LAB to the next evennumbered LAB, or from an odd-numbered LAB to the next oddnumbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure.

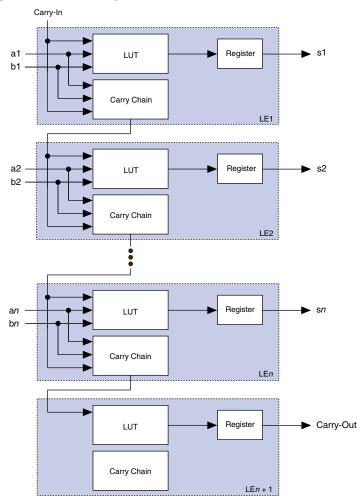

Figure 6 shows how an *n*-bit full adder can be implemented in n + 1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the local, MegaLAB, or FastTrack interconnect routing structures.

Figure 6. APEX 20KC Carry Chain

#### Cascade Chain

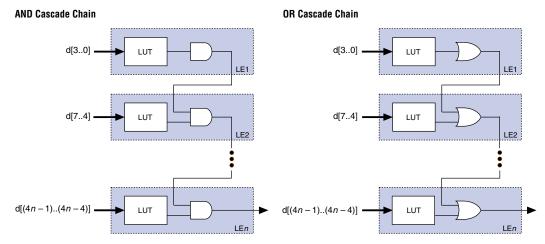

With the cascade chain, the APEX 20KC architecture can implement functions with a very wide fan-in. Adjacent LUTs can compute portions of a function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a short cascade delay. Cascade chain logic can be created automatically by the Quartus II Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than ten LEs are implemented automatically by linking LABs together. For enhanced fitting, a long cascade chain skips alternate LABs in a MegaLAB structure. A cascade chain longer than one LAB skips either from an even-numbered LAB to the next even-numbered LAB, or from an odd-numbered LAB to the next odd-numbered LAB. For example, the last LE of the first LAB in the upper-left MegaLAB structure carries to the first LE of the third LAB in the MegaLAB structure. Figure 7 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in.

Figure 7. APEX 20KC Cascade Chain

#### LE Operating Modes

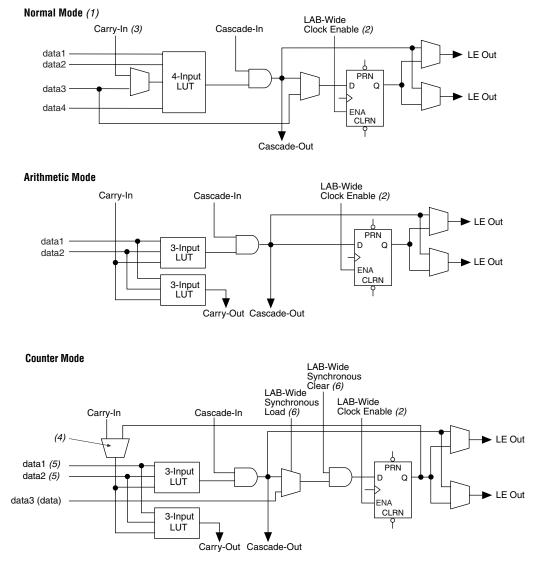

The APEX 20KC LE can operate in one of the following three modes:

- Normal mode

- Arithmetic mode

- Counter mode

Each mode uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes.

The Quartus II software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions that specify which LE operating mode to use for optimal performance. Figure 8 shows the LE operating modes.

#### Figure 8. APEX 20KC LE Operating Modes

#### Notes to Figure 8:

- (1) LEs in normal mode support register packing.

- (2) There are two LAB-wide clock enables per LAB.

- (3) When using the carry-in in normal mode, the packed register feature is unavailable.

- (4) A register feedback multiplexer is available on LE1 of each LAB.

- (5) The DATA1 and DATA2 input signals can supply counter enable, up or down control, or register feedback signals for LEs other than the second LE in an LAB.

- (6) The LAB-wide synchronous clear and LAB wide synchronous load affect all registers in an LAB.

#### Altera Corporation

#### Normal Mode

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Quartus II Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. LEs in normal mode support packed registers.

#### Arithmetic Mode

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a three-input function; the other generates a carry output. As shown in Figure 8, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The Quartus II software implements parameterized functions that use the arithmetic mode automatically where appropriate; the designer does not need to specify how the carry chain will be used.

#### **Counter Mode**

The counter mode offers clock enable, counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in an LAB use the counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The counter mode uses two 3-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading, and another AND gate provides synchronous clearing. If the cascade function is used by an LE in counter mode, the synchronous clear or load overrides any signal carried on the cascade chain. The synchronous clear overrides the synchronous load. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

#### Clear & Preset Logic Control

Logic for the register's clear and preset signals is controlled by LAB-wide signals. The LE directly supports an asynchronous clear function. The Quartus II Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset or to emulate simultaneous preset and clear or asynchronous load. However, this technique uses three additional LEs per register. All emulation is performed automatically when the design is compiled. Registers that emulate simultaneous preset and load will enter an unknown state upon power-up or when the chip-wide reset is asserted.

In addition to the two clear and preset modes, APEX 20KC devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. Use of this pin is controlled through an option in the Quartus II software that is set before compilation. The chip-wide reset overrides all other control signals. Registers using an asynchronous preset are preset when the chip-wide reset is asserted; this effect results from the inversion technique used to implement the asynchronous preset.

#### FastTrack Interconnect

In the APEX 20KC architecture, connections between LEs, ESBs, and I/O pins are provided by the FastTrack interconnect. The FastTrack interconnect is a series of continuous horizontal and vertical routing channels that traverse the device. This global routing structure provides predictable performance, even in complex designs. In contrast, the segmented routing in FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance.

The FastTrack interconnect consists of row and column interconnect channels that span the entire device. The row interconnect routes signals throughout a row of MegaLAB structures; the column interconnect routes signals throughout a column of MegaLAB structures. When using the row and column interconnect, an LE, IOE, or ESB can drive any other LE, IOE, or ESB in a device. See Figure 9.

Figure 9. APEX 20KC Interconnect Structure

A row line can be driven directly by LEs, IOEs, or ESBs in that row. Further, a column line can drive a row line, allowing an LE, IOE, or ESB to drive elements in a different row via the column and row interconnect. The row interconnect drives the MegaLAB interconnect to drive LEs, IOEs, or ESBs in a particular MegaLAB structure.

A column line can be directly driven by LEs, IOEs, or ESBs in that column. A column line on a device's left or right edge can also be driven by row IOEs. The column line is used to route signals from one row to another. A column line can drive a row line; it can also drive the MegaLAB interconnect directly, allowing faster connections between rows.

Figure 10 shows how the FastTrack interconnect uses the local interconnect to drive LEs within MegaLAB structures.

Figure 10. FastTrack Connection to Local Interconnect

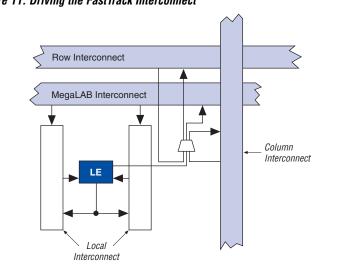

Figure 11 shows the intersection of a row and column interconnect, and how these forms of interconnects and LEs drive each other.

Figure 11. Driving the FastTrack Interconnect

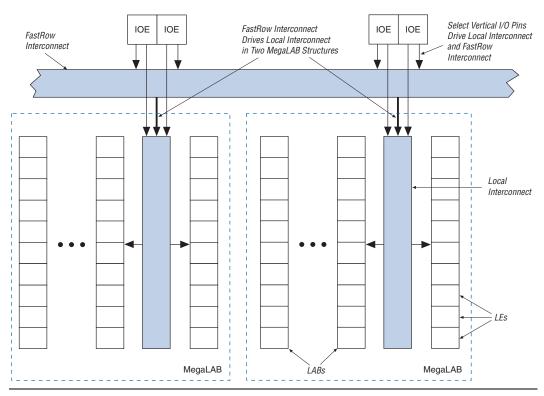

APEX 20KC devices include an enhanced interconnect structure for faster routing of input signals with high fan-out. Column I/O pins can drive the FastRow<sup>TM</sup> interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. The FastRow lines traverse two MegaLAB structures. Also, these pins can drive the local interconnect directly for fast setup times. On EP20K400C and larger devices, the FastRow interconnect drives the two MegaLAB structures in the top left corner, the two MegaLAB structures in the two right corner, the two MegaLAB structures in the bottom left corner, and the two MegaLAB structures in the bottom right corner. On EP20K200C and smaller devices, FastRow interconnect drives the two MegaLAB structures on the top and the two MegaLAB structures on the bottom of the device. On all devices, the FastRow interconnect drives all local interconnect in the appropriate MegaLAB structures except the end local interconnect on the side of the MegaLAB opposite the ESB. Pins using the FastRow interconnect achieve a faster set-up time, as the signal does not need to use a MegaLAB interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

Figure 12. APEX 20KC FastRow Interconnect

Table 8 summarizes how various elements of the APEX 20KC architecture drive each other.

| Source                              | EX 20KC Routing Scheme Destination |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                  |                                     |                         |

|-------------------------------------|------------------------------------|-------------------|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------|-------------------------------------|-------------------------|

| -                                   | Row<br>I/O Pin                     | Column<br>I/O Pin | LE | ESB | Local<br>Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MegaLAB<br>Interconnect | Row<br>FastTrack<br>Interconnect | Column<br>FastTrack<br>Interconnect | FastRow<br>Interconnect |

| Row I/O pin                         |                                    |                   |    |     | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\checkmark$            | ~                                | $\checkmark$                        |                         |

| Column I/O<br>pin                   |                                    |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                  | ~                                   | ~                       |

| LE                                  |                                    |                   |    |     | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\checkmark$            | ~                                | $\checkmark$                        |                         |

| ESB                                 |                                    |                   |    |     | <ul> <li>Image: A set of the set of the</li></ul> | $\checkmark$            | ~                                | $\checkmark$                        |                         |

| Local interconnect                  | ~                                  | ~                 | ~  | ~   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                  |                                     |                         |

| MegaLAB<br>interconnect             |                                    |                   |    |     | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                                  |                                     |                         |

| Row<br>FastTrack<br>interconnect    |                                    |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~                       |                                  | ~                                   |                         |

| Column<br>FastTrack<br>interconnect |                                    |                   |    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ~                       | ~                                |                                     |                         |

| FastRow interconnect                |                                    |                   |    |     | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                                  |                                     |                         |

#### **Product-Term Logic**

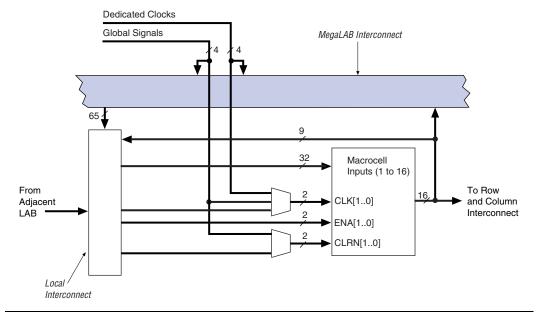

The product-term portion of the MultiCore architecture is implemented with the ESB. The ESB can be configured to act as a block of macrocells on an ESB-by-ESB basis. Each ESB is fed by 32 inputs from the adjacent local interconnect; therefore, it can be driven by the MegaLAB interconnect or the adjacent LAB. Also, nine ESB macrocells feed back into the ESB through the local interconnect for higher performance. Dedicated clock pins, global signals, and additional inputs from the local interconnect drive the ESB control signals.

In product-term mode, each ESB contains 16 macrocells. Each macrocell consists of two product terms and a programmable register. Figure 13 shows the ESB in product-term mode.

Figure 13. Product-Term Logic in ESB

#### Macrocells

APEX 20KC macrocells can be configured individually for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register.

Combinatorial logic is implemented in the product terms. The productterm select matrix allocates these product terms for use as either primary logic inputs (to the OR and XOR gates) to implement combinatorial functions, or as parallel expanders to be used to increase the logic available to another macrocell. One product term can be inverted; the Quartus II software uses this feature to perform De Morgan's inversion for more efficient implementation of wide OR functions. The Quartus II Compiler can use a NOT-gate push-back technique to emulate an asynchronous preset. Figure 14 shows the APEX 20KC macrocell.