Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **FEATURES**

- 200-MHz ARM920T Processor

- 16-kbyte Instruction Cache

- 16-kbyte Data Cache

- Linux<sup>®</sup>, Microsoft<sup>®</sup> Windows<sup>®</sup> CE-enabled MMU

- 100-MHz System Bus

- MaverickCrunch<sup>™</sup> Math Engine

- Floating Point, Integer and Signal Processing Instructions

- Optimized for digital music compression and decompression algorithms.

- · Hardware interlocks allow in-line coding.

- MaverickKey<sup>™</sup> IDs

- 32-bit unique ID can be used for DRM-compliant, 128-bit random ID.

- · Integrated Peripheral Interfaces

- 32-bit SDRAM Interface (up to 4 banks)

- 32/16-bit SRAM/FLASH/ROM

- Serial EEPROM Interface

- 1/10/100 Mbps Ethernet MAC

- Three UARTs

- Three-port USB 2.0 Full-speed Host (OHCI) (12 Mbits per second)

- · IrDA Interface

- LCD and Raster Interface with Graphics Accelerator

# ARM9 SOC with Ethernet, USB, Display, and Touchscreen

- · Touchscreen Interface with ADC

- 8 x 8 Keypad Scanner

- One Serial Peripheral Interface (SPI) Port

- 6-channel or 2-channel Serial Audio Interface (I<sup>2</sup>S)

- 2-channel, Low-cost Serial Audio Interface (AC'97)

- Internal Peripherals

- 12 Direct Memory Access (DMA) Channels

- · Real-time Clock with Software Trim

- Dual PLL controls all clock domains.

- · Watchdog Timer

- Two General-purpose 16-bit Timers

- · One General-purpose 32-bit Timer

- · One 40-bit Debug Timer

- Interrupt Controller

- · Boot ROM

- Package

- 272 pin TFBGA

**USER INTERFACE**

**COMMUNICATIONS PORTS**

**MEMORY AND STORAGE**

#### **OVERVIEW**

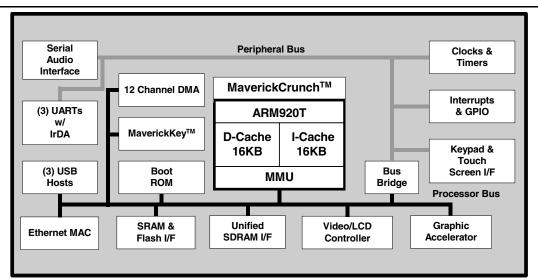

The EP9307 is an ARM920T-based system-on-a-chip (SOC) design with a large peripheral set targeted to a variety of applications:

- · Thin client computers for business and home

- Internet radio

- Internet access devices

- Industrial computers

- · Specialized terminals

- · Point of sale terminals

- Test and measurement equipment

The ARM920T microprocessor core with separate 16-kbyte, 64-way set-associative instruction and data caches is augmented by the MaverickCrunch™ coprocessor, enabling high-speed floating point calculations.

MaverickKey<sup>™</sup> unique hardware programmed IDs are a solution to the growing concern over secure web content and commerce. With Internet security playing an

important role in the delivery of digital media such as books or music, traditional software methods are quickly becoming unreliable. The MaverickKey unique IDs provide OEMs with a method of utilizing specific hardware IDs such as those assigned for SDMI (Secure Digital Music Initiative) or any other authentication mechanism.

A high-performance 1/10/100 Mbps Ethernet media access controller (MAC) is included along with external interfaces to SPI, I<sup>2</sup>S audio, Raster/LCD, keypad and touchscreen. A three-port USB 2.0 Full-speed Host (OHCI) (12 Mbits per second) and three UARTs are included as well.

The EP9307 is a high-performance, low-power, RISC-based, single-chip computer built around an ARM920T microprocessor core with a maximum operating clock rate of 200 MHz (184 MHz for industrial conditions). The ARM core operates from a 1.8 V supply, while the I/O operates at 3.3 V with power usage between 100 mW and 750 mW (dependent on speed).

**Table A. Change History**

| Revision | Date          | Changes                                                                                                                                                                                                                                                            |

|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PP1      | July 2004     | Initial Release.                                                                                                                                                                                                                                                   |

| PP2      | August 2004   | Correct error in pin out table, pages 42 & 43.                                                                                                                                                                                                                     |

| PP3      | August 2004   | Minor correction.                                                                                                                                                                                                                                                  |

| PP4      | March 2005    | Update electrical characteristics with most-current characterization data.                                                                                                                                                                                         |

| F1       | February 2010 | Removed "Preliminary Data" statement from legal disclaimer. Removed lead-containing device part numbers. Increased minimum CVDD & VDD_PLL voltages from 1.65 V min. to 1.71 V min. Changed operating temperatures to 0 to 60°C commercial, -40 to 70°C industrial. |

| F2       | March 2010    | Increased commercial/industrial temperatures to 70/85 deg. C max.                                                                                                                                                                                                  |

## **Table of Contents**

| FEATURES                                                             | 1    |

|----------------------------------------------------------------------|------|

| OVERVIEW                                                             | 2    |

| Processor Core - ARM920T                                             | 6    |

| MaverickCrunch™ Math Engine                                          | 6    |

| MaverickKey™ Unique ID                                               | 6    |

| General Purpose Memory Interface (SDRAM, SRAM, ROM, FLASH)           | 6    |

| Ethernet Media Access Controller (MAC)                               | 7    |

| Serial Interfaces (SPI, I2S and AC '97)                              | 7    |

| Raster/LCD Interface                                                 | 7    |

| Graphics Accelerator                                                 |      |

| Touch Screen Interface with 12-bit Analog-to-digital Converter (ADC) | 8    |

| 64-key Keypad Interface                                              |      |

| Universal Asynchronous Receiver/Transmitters (UARTs)                 |      |

| Internal Boot ROM                                                    |      |

| Triple-port USB Host                                                 |      |

| Two-wire Interface Support                                           |      |

| Real-Time Clock with Software Trim                                   |      |

| PLL and Clocking                                                     |      |

| Timers                                                               |      |

| Interrupt Controller                                                 |      |

| Dual LED Drivers                                                     |      |

| General Purpose Input/Output (GPIO)                                  |      |

| Reset and Power Management                                           |      |

| Hardware Debug Interface                                             |      |

| 12-Channel DMA Controller                                            |      |

| Electrical Specifications                                            | 12   |

| Absolute Maximum Ratings                                             | . 12 |

| Recommended Operating Conditions                                     | . 12 |

| DC Characteristics                                                   | . 13 |

| Timings                                                              | 14   |

| Memory Interface                                                     |      |

| Ethernet MAC Interface                                               |      |

| Audio Interface                                                      |      |

| AC'97                                                                |      |

| LCD Interface                                                        | . 37 |

| ADC                                                                  | . 38 |

| JTAG                                                                 | . 39 |

| 272 Pin TFBGA Package Outline                                        | 40   |

| 272 TFBGA Diagram                                                    |      |

| 272 Pin TFBGA Pinout (Bottom View)                                   | 41   |

| Acronyms and Abbreviations                                           |      |

| Units of Measurement                                                 |      |

|                                                                      |      |

| UBDEBING INCUBINATION                                                | 49   |

## **List of Figures**

| Figure 1. Timing Diagram Drawing Key                                         | 14 |

|------------------------------------------------------------------------------|----|

| Figure 2. SDRAM Load Mode Register Cycle Timing Measurement                  | 15 |

| Figure 3. SDRAM Burst Read Cycle Timing Measurement                          | 16 |

| Figure 4. SDRAM Burst Write Cycle Timing Measurement                         | 17 |

| Figure 5. SDRAM Auto Refresh Cycle Timing Measurement                        | 18 |

| Figure 6. Static Memory Single Word Read Cycle Timing Measurement            | 19 |

| Figure 7. Static Memory Single Word Write Cycle Timing Measurement           | 20 |

| Figure 8. Static Memory Multiple Word Read 8-bit Cycle Timing Measurement    | 21 |

| Figure 9. Static Memory Multiple Word Write 8-bit Cycle Timing Measurement   | 22 |

| Figure 10. Static Memory Multiple Word Read 16-bit Cycle Timing Measurement  | 23 |

| Figure 11. Static Memory Multiple Word Write 16-bit Cycle Timing Measurement | 24 |

| Figure 12. Static Memory Burst Read Cycle Timing Measurement                 | 25 |

| Figure 13. Static Memory Burst Write Cycle Timing Measurement                | 26 |

| Figure 14. Static Memory Single Read Wait Cycle Timing Measurement           |    |

| Figure 15. Static Memory Single Write Wait Cycle Timing Measurement          |    |

| Figure 16. Static Memory Turnaround Cycle Timing Measurement                 | 29 |

| Figure 17. Ethernet MAC Timing Measurement                                   |    |

| Figure 18. TI Single Transfer Timing Measurement                             | 33 |

| Figure 19. Microwire Frame Format, Single Transfer                           | 33 |

| Figure 20. SPI Format with SPH=1 Timing Measurement                          | 34 |

| Figure 21. Inter-IC Sound (I2S) Timing Measurement                           | 35 |

| Figure 22. AC '97 Configuration Timing Measurement                           | 36 |

| Figure 23. LCD Timing Measurement                                            | 37 |

| Figure 24. ADC Transfer Function                                             | 38 |

| Figure 25. JTAG Timing Measurement                                           | 39 |

| Figure 26. 272 Pin TFBGA Diagram                                             | 40 |

| Figure 27. 272 Pin TFBGA Pinout                                              | 42 |

## **List of Tables**

| Table A. Change History                                                                  | 2    |

|------------------------------------------------------------------------------------------|------|

| Table B. General Purpose Memory Interface Pin Assignments                                | 6    |

| Table C. Ethernet Media Access Controller Pin Assignments                                | 7    |

| Table D. Audio Interfaces Pin Assignment                                                 | 7    |

| Table E. LCD Interface Pin Assignments                                                   | 8    |

| Table F. Touch Screen Interface with 12-bit Analog-to-Digital Converter Pin Assignments. | 8    |

| Table G. 64-Key Keypad Interface Pin Assignments                                         | 8    |

| Table H. Universal Asynchronous Receiver / Transmitters Pin Assignments                  | 9    |

| Table I. Triple Port USB Host Pin Assignments                                            | 9    |

| Table J. Two-Wire Port with EEPROM Support Pin Assignments                               | 9    |

| Table K. Real-Time Clock with Pin Assignments                                            |      |

| Table L. PLL and Clocking Pin Assignments                                                | . 10 |

| Table M.External Interrupt Controller Pin Assignment                                     |      |

| Table N. Dual LED Pin Assignments                                                        | . 10 |

| Table O. General Purpose Input/Output Pin Assignment                                     |      |

| Table P. Reset and Power Management Pin Assignments                                      | . 11 |

| Table Q. Hardware Debug Interface                                                        | . 11 |

| Table R. 272 Pin Diagram Dimensions                                                      | . 41 |

| Table S. Pin Descriptions                                                                | . 46 |

| Table T. Pin Multiplex Usage Information                                                 | . 47 |

#### **Processor Core - ARM920T**

The ARM920T is a Harvard architecture processor with separate 16 kbyte instruction and data caches with an 8-word line length but a unified memory. The processor utilizes a five-stage pipeline consisting of fetch, decode, execute, memory and write stages. Key features include:

- ARM (32-bit) and Thumb (16-bit compressed) instruction sets

- 32-bit Advanced Micro-Controller Bus Architecture (AMBA)

- 16 kbyte Instruction Cache with lockdown

- 16 kbyte Data Cache (programmable write-through or write-back) with lockdown

- MMU for Linux<sup>®</sup>, Microsoft<sup>®</sup> Windows<sup>®</sup> CE and other operating systems

- Translation Look Aside Buffers with 64 Data and 64 Instruction Entries

- Programmable Page Sizes of 1 Mbyte, 64 kbyte, 4 kbyte, and 1 kbyte

- · Independent lockdown of TLB Entries

## MaverickCrunch<sup>™</sup> Math Engine

The MaverickCrunch Engine is a mixed-mode coprocessor designed primarily to accelerate the math processing required to rapidly encode digital audio formats. It accelerates single- and double-precision integer and floating point operations plus an integer multiply-accumulate (MAC) instruction that is considerably faster than the ARM920T's native MAC instruction. The ARM920T coprocessor interface is utilized thereby sharing its memory interface and instruction stream. Hardware forwarding and interlock allows the ARM to handle looping and addressing while MaverickCrunch handles computation. Features include:

- · IEEE-754 single and double precision floating point

- 32/64-bit integer

- Add/multiply/compare

- Integer MAC 32-bit input with 72-bit accumulate

- Integer Shifts

- · Floating point to/from integer conversion

- · Sixteen 64-bit register files

- · Four 72-bit accumulators

## MaverickKey<sup>™</sup> Unique ID

MaverickKey unique hardware programmed IDs are a solution to the growing concern over secure web content and commerce. With Internet security playing an important role in the delivery of digital media such as books or music, traditional software methods are quickly becoming unreliable. The MaverickKey unique IDs

provide OEMs with a method of utilizing specific hardware IDs such as those assigned for SDMI (Secure Digital Music Initiative) or any other authentication mechanism.

Both a specific 32-bit ID as well as a 128-bit random ID are programmed into the EP9307 through the use of laser probing technology. These IDs can then be used to match secure copyrighted content with the ID of the target device the EP9307 is powering, and then deliver the copyrighted information over a secure connection. In addition, secure transactions can benefit by also matching device IDs to server IDs. MaverickKey IDs provide a level of hardware security required for today's Internet appliances.

## General Purpose Memory Interface (SDRAM, SRAM, ROM, FLASH)

The EP9307 features a unified memory address model where all memory devices are accessed over a common address/data bus. A separate internal port is dedicated to the read-only Raster/LCD refresh engine, while the rest of the memory accesses are performed via the Processor bus. The SRAM memory controller supports 8, 16 and 32-bit devices and accommodates an internal boot ROM concurrently with 32-bit SDRAM memory.

- 1 to 4 banks of 32-bit, 100 MHz SDRAM

- One internal port dedicated to the Raster/LCD Refresh Engine (Read Only)

- Address and data bus shared between SDRAM, SRAM, ROM, and FLASH memory

- NOR FLASH memory supported

Table B. General Purpose Memory Interface Pin Assignments

| Pin Mnemonic          | Pin Description                   |

|-----------------------|-----------------------------------|

| SDCLK                 | SDRAM Clock                       |

| SDCLKEN               | SDRAM Clock Enable                |

| SDCSn[3:0]            | SDRAM Chip Selects 3-0            |

| RASn                  | SDRAM RAS                         |

| CASn                  | SDRAM CAS                         |

| SDWEn                 | SDRAM Write Enable                |

| CSn[7:6] and CSn[3:0] | Chip Selects 7, 6, 3, 2, 1, 0     |

| AD[25:0]              | Address Bus 25-0                  |

| DA[31:0]              | Data Bus 31-0                     |

| DQMn[3:0]             | SDRAM Output Enables / Data Masks |

| WRn                   | SRAM Write Strobe                 |

| RDn                   | SRAM Read/OE Strobe               |

| WAITn                 | SRAM Wait Input                   |

#### Ethernet Media Access Controller (MAC)

The MAC subsystem is compliant with the ISO/TEC 802.3 topology for a single shared medium with several stations. Multiple MII-compliant PHYs are supported. Features include:

- Supports 1/10/100 Mbps transfer rates for home/small-business/large-business applications

- Interfaces to an off-chip PHY through industry standard Media Independent Interface (MII)

Table C. Ethernet Media Access Controller Pin Assignments

| Pin Mnemonic | Pin Description       |

|--------------|-----------------------|

| MDC          | Management Data Clock |

| MDIO         | Management Data I/O   |

| RXCLK        | Receive Clock         |

| MIIRXD[3:0]  | Receive Data          |

| RXDVAL       | Receive Data Valid    |

| RXERR        | Receive Data Error    |

| TXCLK        | Transmit Clock        |

| MIITXD[3:0]  | Transmit Data         |

| TXEN         | Transmit Enable       |

| TXERR        | Transmit Error        |

| CRS          | Carrier Sense         |

| CLD          | Collision Detect      |

## Serial Interfaces (SPI, I<sup>2</sup>S and AC '97)

The SPI port can be configured as a master or a slave, supporting the National Semiconductor<sup>®</sup>, Motorola<sup>®</sup>, and Texas Instruments<sup>®</sup> signaling protocols.

The AC'97 port supports multiple codecs for multichannel audio output with a single stereo input. The I<sup>2</sup>S port can be configured to support two channel, 24 bit audio.

These ports are multiplexed so that I<sup>2</sup>S port 0 will take over either the AC'97 pins or the SPI pins. The second and third I2S ports' serial input and serial output pins are multiplexed with EGPIO[4,5,6,13]. The clocks supplied in the first I2S port are also used for the second and third I2S ports.

- Normal Mode: One SPI Port and one AC'97 Port

- I<sup>2</sup>S on SSP Mode: One AC'97 Port and up to three I<sup>2</sup>S Ports

- I<sup>2</sup>S on AC'97 Mode: One SPI Port and up to three I<sup>2</sup>S Ports

Note: I<sup>2</sup>S may not be output on AC'97 and SSP ports at the same time.

Table D. Audio Interfaces Pin Assignment

| Pin     | Normal Mode            | I2S on SSP<br>Mode       | I2S on AC'97<br>Mode |

|---------|------------------------|--------------------------|----------------------|

| Name    | Pin<br>Description     | Pin Description          | Pin Description      |

| SCLK1   | SPI Bit Clock          | I2S Serial Clock         | SPI Bit Clock        |

| SFRM1   | SPI Frame Clock        | I2S Frame Clock          | SPI Frame Clock      |

| SSPRX1  | SPI Serial Input       | I2S Serial Input         | SPI Serial Input     |

| SSPTX1  | SPI Serial<br>Output   | I2S Serial Output        | SPI Serial Output    |

|         |                        | (No I2S Master<br>Clock) |                      |

| ARSTn   | AC'97 Reset            | AC'97 Reset              | I2S Master Clock     |

| ABITCLK | AC'97 Bit Clock        | AC'97 Bit Clock          | I2S Serial Clock     |

| ASYNC   | AC'97 Frame<br>Clock   | AC'97 Frame<br>Clock     | I2S Frame Clock      |

| ASDI    | AC'97 Serial<br>Input  | AC'97 Serial Input       | I2S Serial Input     |

| ASDO    | AC'97 Serial<br>Output | AC'97 Serial<br>Output   | I2S Serial Output    |

#### Raster/LCD Interface

The Raster/LCD interface provides data and interface signals for a variety of display types. It features fully programmable video interface timing for non-interlaced flat panel or dual scan displays. Resolutions up to 1024 x 768 are supported from a unified SDRAM based frame buffer. A 16-bit PWM provides control for LCD panel contrast. LCD specific features include:

- Timing and interface signals for digital LCD and TFT displays

- Full programmability for either non-interlaced or dualscan color and grayscale flat panel displays

- Dedicated data path to SDRAM controller for improved system performance

- Pixel depths of 4, 8, 16, or 24 bits per pixel or 256 levels of grayscale

- Hardware Cursor up to 64 x 64 pixels

- 256 x 18 Color Lookup Table

- Hardware Blinking

- · 8-bit interface to low-end panel

Table E. LCD Interface Pin Assignments

| Pin Mnemonic | Pin Description                                        |

|--------------|--------------------------------------------------------|

| SPCLK        | Pixel Clock                                            |

| P[17:0]      | Pixel Data Bus [17:0]                                  |

| HSYNC/LP     | Horizontal<br>Synchronization/Line Pulse               |

| VCSYNC/FP    | Vertical or Composite<br>Synchronization / Frame Pulse |

| BLANK        | Composite Blank                                        |

| BRIGHT       | Pulse Width Modulated Brightness                       |

### **Graphics Accelerator**

The EP9307 contains a hardware graphics acceleration engine that improves graphic performance by handling block copy, block fill and hardware line draw operations. The Graphics Accelerator is used in the system to offload graphics operations from the processor.

Pixel depths supported by the Graphics Accelerator are 4, 8, 16 or 24 bits per pixel (bpp). The 24 bits per pixel mode can be operated as packed (4 pixels every 3 words) or unpacked (1 pixel per word with the high byte unused.)

The block copy operations of the Graphics Accelerator are similar to a DMA (Direct Memory Access) transfer that understands pixel organization, block width, transparency, and transformation from 1bpp to higher 4, 8, 16 or 24 bpp.

The line draw operations also allow for solid lines or dashed lines. The colors for line drawing can be either foreground color and background color or foreground color with the background being transparent.

#### Touch Screen Interface with 12-bit Analogto-digital Converter (ADC)

The touch screen interface performs all sampling, averaging, ADC range checking, and control for a wide variety of analog resistive touch screens. This controller only interrupts the processor when a meaningful change occurs. The touch screen hardware may be disabled and the switch matrix and ADC controlled directly if desired. Features include:

- Support for 4-, 5-, 7-, or 8-wire analog resistive touch screens.

- Flexibility unused lines may be used for temperature sensing or other functions.

- · Touch screen interrupt function.

Table F. Touch Screen Interface with 12-bit Analog-to-Digital Converter Pin Assignments

| Pin Mnemonic | Pin Description                             |

|--------------|---------------------------------------------|

| Xp, Xm       | Touch screen ADC X Axis                     |

| Yp, Ym       | Touch screen ADC Y Axis                     |

| SXp, SXm     | Touch screen ADC X Axis<br>Voltage Feedback |

| SYp, SYm     | Touch screen ADC Y Axis<br>Voltage Feedback |

#### 64-key Keypad Interface

The keypad circuitry scans an 8 x 8 array of 64 normally open, single pole switches. Any one or two keys depressed will be de-bounced and decoded. An interrupt is generated whenever a stable set of depressed keys is detected. If the keypad is not utilized, the 16 column/row pins may be used as general purpose I/O. The Keypad interface:

- Provides scanning, debounce, and decoding for a 64key switch array.

- · Scans an 8-row by 8-column matrix.

- May decode 2 keys at once.

- Generates an interrupt when a new stable key is determined.

- Also generates a 3-key reset interrupt.

Table G. 64-Key Keypad Interface Pin Assignments

| Pin Mnemonic | Pin<br>Description          | Alternative Usage   |

|--------------|-----------------------------|---------------------|

| COL[7:0]     | Key Matrix Column<br>Inputs | General Purpose I/O |

| ROW[7:0]     | Key Matrix Row<br>Inputs    | General Purpose I/O |

## Universal Asynchronous Receiver/Transmitters (UARTs)

Three 16550-compatible UARTs are supplied. Two provide asynchronous HDLC (High-level Data Link Control) protocol support for full duplex transmit and receive. The HDLC receiver handles framing, address matching, CRC checking, control-octet transparency, and optionally passes the CRC to the host at the end of the packet. The HDLC transmitter handles framing, CRC generation, and control-octet transparency. The host must assemble the frame in memory before transmission. The HDLC receiver and transmitter use the UART FIFOs to buffer the data streams. A third IrDA® compatible UART is also supplied.

- UART1 supports modem bit rates up to 115.2 kbps, supports HDLC and includes a 16 byte FIFO for receive and a 16 byte FIFO for transmit. Interrupts are generated on Rx, Tx and modem status change.

- UART2 contains an IrDA encoder operating at either the slow (up to 115 kbps), medium (0.576 or 1.152 Mbps), or fast (4 Mbps) IR data rates. It also has a 16 byte FIFO for receive and a 16 byte FIFO for transmit.

- UART3 supports HDLC and includes a 16 byte FIFO for receive and a 16 byte FIFO for transmit. Interrupts are generated on Rx and Tx.

Table H. Universal Asynchronous Receiver / Transmitters Pin Assignments

| Pin Mnemonic | Pin Name - Description                        |

|--------------|-----------------------------------------------|

| TXD0         | UART1 Transmit                                |

| RXD0         | UART1 Receive                                 |

| CTSn         | UART1 Clear To<br>Send / Transmit Enable      |

| DSRn/DCDn    | UART1 Data Set<br>Ready / Data Carrier Detect |

| DTRn         | UART1 Data Terminal Ready                     |

| RTSn         | UART1 Ready To Send                           |

| EGPIO[0]/RI  | UART1 Ring Indicator                          |

| TXD1/SIROUT  | UART2 Transmit / IrDA<br>Output               |

| RXD1/SIRIN   | UART2 Receive / IrDA Input                    |

| TXD2         | UART3 Transmit                                |

| RXD2         | UART3 Receive                                 |

| TENn         | HDLC3 Transmit Enable                         |

#### **Internal Boot ROM**

The Internal 16-kbyte ROM allows booting from FLASH memory, SPI or UART. Consult the EP9307 User's Guide for operational details.

#### **Triple-port USB Host**

The USB Open Host Controller Interface (Open HCI) provides full-speed serial communications ports at a baud rate of 12 Mbits/sec. Up to 127 USB devices (printer, mouse, camera, keyboard, etc.) and USB hubs can be connected to the USB host in the USB "tiered-star" topology.

This includes the following features:

- Compliance with the USB 2.0 specification

- Compliance with the Open HCI Rev 1.0 specification

- Supports both low-speed (1.5 Mbps) and full-speed (12 Mbps) USB device connections

- Root HUB integrated with 3 downstream USB ports

- Transceiver buffers integrated, over-current protection on ports

- Supports power management

- · Operates as a master on the bus

The Open HCI host controller initializes the master DMA transfer with the AHB bus:

- Fetches endpoint descriptors and transfer descriptors

- Accesses endpoint data from system memory

- Accesses the HC communication area

- · Writes status and retire transfer descriptor

Table I. Triple Port USB Host Pin Assignments

| Pin Mnemonic | Pin Name - Description |

|--------------|------------------------|

| USBp[2:0]    | USB Positive signals   |

| USBm[2:0]    | USB Negative Signals   |

#### **Two-wire Interface Support**

The two-wire interface provides communication and control for synchronous-serial-driven devices.

Table J. Two-Wire Port with EEPROM Support Pin Assignments

| Pin Mnemonic | Pin Name - Description   | Alternative<br>Usage   |

|--------------|--------------------------|------------------------|

| EECLK        | Two-wire Interface Clock | General<br>Purpose I/O |

| EEDATA       | Two-wire Interface Data  | General<br>Purpose I/O |

#### **Real-Time Clock with Software Trim**

The software trim feature on the real time clock (RTC) provides software controlled digital compensation of the 32.768 KHz input clock. This compensation is accurate to  $\pm 1.24$  sec/month.

Note: A real time clock <u>must</u> be connected to RTCXTALI or the EP9307 device will not boot.

Table K. Real-Time Clock with Pin Assignments

| Pin Mnemonic | Pin Name - Description            |

|--------------|-----------------------------------|

| RTCXTALI     | Real-Time Clock Oscillator Input  |

| RTCXTALO     | Real-Time Clock Oscillator Output |

#### **PLL and Clocking**

The Processor and the Peripheral Clocks operate from a single 14.7456 MHz crystal.

The Real Time Clock operates from a 32.768 KHz external oscillator.

Table L. PLL and Clocking Pin Assignments

| Pin Mnemonic | Pin Name - Description |

|--------------|------------------------|

| XTALI        | Main Oscillator Input  |

| XTALO        | Main Oscillator Output |

| VDD_PLL      | Main Oscillator Power  |

| GND_PLL      | Main Oscillator Ground |

#### **Timers**

The Watchdog Timer ensures proper operation by requiring periodic attention to prevent a reset-on-time-out.

Two 16-bit timers operate as free running down-counters or as periodic timers for fixed interval interrupts and have a range of 0.03 ms to 4.27 seconds.

One 32-bit timer, plus a 6-bit prescale counter, has a range of 0.03  $\mu s$  to 73.3 hours.

One 40-bit debug timer, plus a 6-bit prescale counter, has a range of  $1.0 \mu s$  to 12.7 days.

#### Interrupt Controller

The interrupt controller allows up to 62 interrupts to generate an Interrupt Request (IRQ) or Fast Interrupt Request (FIQ) signal to the processor core. Thirty-two hardware priority assignments are provided for assisting IRQ vectoring, and two levels are provided for FIQ vectoring. This allows time critical interrupts to be processed in the shortest time possible. Internal interrupts may be programmed as active high or active

low level sensitive inputs. GPIO pins programmed as interrupts may be programmed as active high level sensitive, active low level sensitive, rising edge triggered, falling edge triggered, or combined rising/falling edge triggered.

- Supports 64 interrupts from a variety of sources (such as UARTs, GPIO, and key matrix)

- Routes interrupt sources to either the ARM920T's IRQ or FIQ (Fast IRQ) inputs

- Three dedicated off-chip interrupt lines operate as active high level sensitive interrupts

- Any of the 16 GPIO lines maybe configured to generate interrupts

- Software supported priority mask for all FIQs and IRQs

Table M. External Interrupt Controller Pin Assignment

| Pin Mnemonic | Pin Name - Description      |

|--------------|-----------------------------|

| INT[2:0]     | External Interrupts 2, 1, 0 |

#### **Dual LED Drivers**

Two pins are assigned specifically to drive external LEDs.

Table N. Dual LED Pin Assignments

| Pin Mnemonic | Pin Name -<br>Description | Alternative Usage   |

|--------------|---------------------------|---------------------|

| GRLED        | Green LED                 | General Purpose I/O |

| REDLED       | Red LED                   | General Purpose I/O |

### General Purpose Input/Output (GPIO)

The 14 EGPIO pins may each be configured individually as an output, an input, or an interrupt input.

There are 22 pins that may alternatively be used as input, output, or open-drain pins, but do not support interrupts. These pins are:

- Key Matrix ROW[7:0], COL[7:0]

- Ethernet MDIO

- Both LED Outputs

- · Two-wire Clock and Data

- GGPIO[2]

- HGPIO[7:2]

6 pins may alternatively be used as inputs only:

- CTSn, DSRn/DCDn

- · 4 Interrupt Lines

2 pins may alternatively be used as outputs only:

- RTSn

- ARSTn

Table O. General Purpose Input/Output Pin Assignment

| Pin Mnemonic                     | Pin Name - Description                                          |

|----------------------------------|-----------------------------------------------------------------|

| EGPIO[15]<br>EGPIO[13:0]         | Expanded General Purpose Input / Output Pins with Interrupts    |

| FGPIO[7]<br>FGPIO[5]<br>FGPIO[0] | Expanded General Purpose Input / Output<br>Pins with Interrupts |

decrement, or stay at the same value. All DMA addresses are physical, not virtual addresses.

#### **Reset and Power Management**

The chip may be reset through the PRSTn pin or through the open drain common reset pin, RSTOn.

Clocks are managed on a peripheral-by-peripheral basis and may be turned off to conserve power.

The processor clock is dynamically adjustable from 0 to 200 MHz (184 MHz for industrial conditions).

Table P. Reset and Power Management Pin Assignments

| Pin Mnemonic | Pin Name - Description                                              |

|--------------|---------------------------------------------------------------------|

| PRSTn        | Power On Reset                                                      |

| RSTOn        | User Reset In/Out – Open Drain –<br>Preserves Real Time Clock value |

#### **Hardware Debug Interface**

The JTAG interface allows use of ARM's Multi-ICE or other in-circuit emulators.

Table Q. Hardware Debug Interface

| Pin Mnemonic | Pin Name - Description |

|--------------|------------------------|

| TCK          | JTAG Clock             |

| TDI          | JTAG Data In           |

| TDO          | JTAG Data Out          |

| TMS          | JTAG Test Mode Select  |

| TRSTn        | JTAG Port Reset        |

#### 12-Channel DMA Controller

The DMA module contains 12 separate DMA channels. These may be used for peripheral-to-memory or memory-to-peripheral access. Two of these are dedicated to memory-to-memory transfers. Each DMA channel is connected to the 16-bit DMA request bus.

The request bus is a collection of requests, Serial Audio and UARTs. Each DMA channel can be used independently or dedicated to any request signal. For each DMA channel, source and destination addressing can be independently programmed to increment,

## **Electrical Specifications**

### **Absolute Maximum Ratings**

(All grounds = 0 V, all voltages with respect to 0 V)

| Parameter                                      |          | Symbol                             | Min | Max                          | Unit        |    |

|------------------------------------------------|----------|------------------------------------|-----|------------------------------|-------------|----|

| Power Supplies                                 |          | RVDD<br>CVDD<br>VDD_PLL<br>VDD_ADC |     | 3.96<br>2.16<br>2.16<br>3.96 | V<br>V<br>V |    |

| Total Power Dissipation                        | (Note 1) |                                    |     | -                            | 2           | W  |

| Input Current per Pin, DC (Except supply pins) |          |                                    |     | -                            | ±10         | mA |

| Output current per pin, DC                     |          |                                    |     | -                            | ±50         | mA |

| Digital Input voltage                          | (Note 2) |                                    |     | -0.3                         | RVDD+0.3    | V  |

| Storage temperature                            |          |                                    |     | -40                          | +125        | °C |

Note: 1. Includes all power generated due to AC and/or DC output loading.

WARNING: Operation beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

## **Recommended Operating Conditions**

(All grounds = 0 V, all voltages with respect to 0 V)

| Parameter                                  | Symbol         | Min  | Тур  | Max  | Unit |

|--------------------------------------------|----------------|------|------|------|------|

|                                            | RVDD           | 3.0  | 3.3  | 3.6  | V    |

| Power Supplies                             | CVDD           | 1.71 | 1.80 | 1.94 | V    |

| Supplies                                   | VDD_PLL        | 1.71 | 1.80 | 1.94 | V    |

|                                            | VDD_ADC        | 3.0  | 3.3  | 3.6  | V    |

| Operating Ambient Temperature - Commercial | T <sub>A</sub> | 0    | +25  | +70  | °C   |

| Operating Ambient Temperature - Industrial | T <sub>A</sub> | -40  | +25  | +85  | °C   |

| Processor Clock Speed - Commercial         | FCLK           | -    | -    | 200  | MHz  |

| Processor Clock Speed - Industrial         | FCLK           | -    | -    | 184  | MHz  |

| System Clock Speed - Commercial            | HCLK           | -    | -    | 100  | MHz  |

| System Clock Speed - Industrial            | HCLK           | -    | -    | 92   | MHz  |

<sup>2.</sup> The power supply pins are at maximum values listed in "Recommended Operating Conditions", below.

#### **DC Characteristics**

$(T_A = 0 \text{ to } 70^{\circ} \text{ C}; \text{CVDD} = \text{VDD\_PLL} = 1.8; \text{RVDD} = 3.3 \text{ V};$

All grounds = 0 V; all voltages with respect to 0 V unless otherwise noted)

| Parameter                  |              |          | Symbol          | Min         | Max         | Unit |

|----------------------------|--------------|----------|-----------------|-------------|-------------|------|

| High level output voltage  | lout = -4 mA | (Note 3) | V <sub>oh</sub> | 0.85 × RVDD | -           | V    |

| Low level output voltage   | lout = 4 mA  |          | V <sub>ol</sub> | -           | 0.15 × RVDD | V    |

| High level input voltage   |              | (Note 4) | V <sub>ih</sub> | 0.65 × RVDD | VDD + 0.3   | V    |

| Low level input voltage    |              | (Note 4) | V <sub>il</sub> | -0.3        | 0.35 × RVDD | V    |

| High level leakage current | Vin = 3.3 V  | (Note 4) | I <sub>ih</sub> | -           | 10          | μΑ   |

| Low level leakage current  | Vin = 0      | (Note 4) | l <sub>il</sub> | -           | -10         | μΑ   |

| Parameter                            |                            | Min | Тур       | Max       | Unit     |

|--------------------------------------|----------------------------|-----|-----------|-----------|----------|

| Power Supply Pins (Outputs Unloaded) |                            |     |           |           |          |

| Power Supply Current:                | CVDD/VDD_PLL Total<br>RVDD |     | 190<br>45 | 240<br>80 | mA<br>mA |

| Low-Power Mode Supply Current        | CVDD/VDD_PLL Total<br>RVDD |     | 2<br>1.0  | 3.5<br>2  | mA<br>mA |

Note: 3. For open drain pins, high level output voltage is dependent on the external load.

<sup>4.</sup> All inputs that do not include internal pull-ups or pull-downs, must be externally driven for proper operation (See Table S on page 46). If an input is not driven, it should be tied to power or ground, depending on the particular function. If an I/O pin is not driven and programmed as an input, it should be tied to power or ground through its own resistor.

## **Timings**

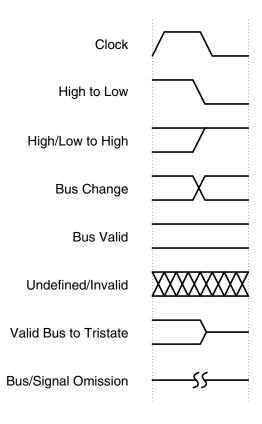

#### **Timing Diagram Conventions**

This data sheet contains one or more timing diagrams. The following key explains the components used in these diagrams. Any variations are clearly labelled when they occur. Therefore, no additional meaning should be attached unless specifically stated.

Figure 1. Timing Diagram Drawing Key

#### **Timing Conditions**

Unless specified otherwise, the following conditions are true for all timing measurements.

- $T_A = 0 \text{ to } 70^{\circ} \text{ C}$

- CVDD = VDD\_PLL = 1.8V

- RVDD = 3.3 V

- All grounds = 0 V

- Logic 0 = 0 V, Logic 1 = 3.3 V

- Output loading = 50 pF

- Timing reference levels = 1.5 V

- The Processor Bus Clock (HCLK) is programmable and is set by the user. The frequency is typically between 33 MHz and 100 MHz (92 MHz for industrial conditions).

## **Memory Interface**

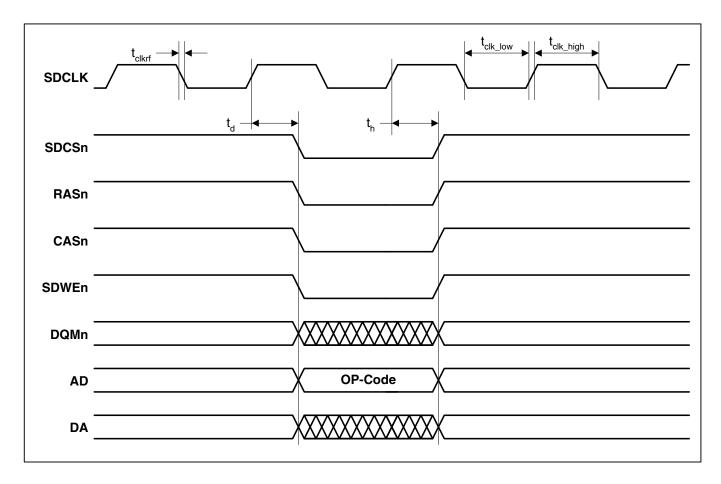

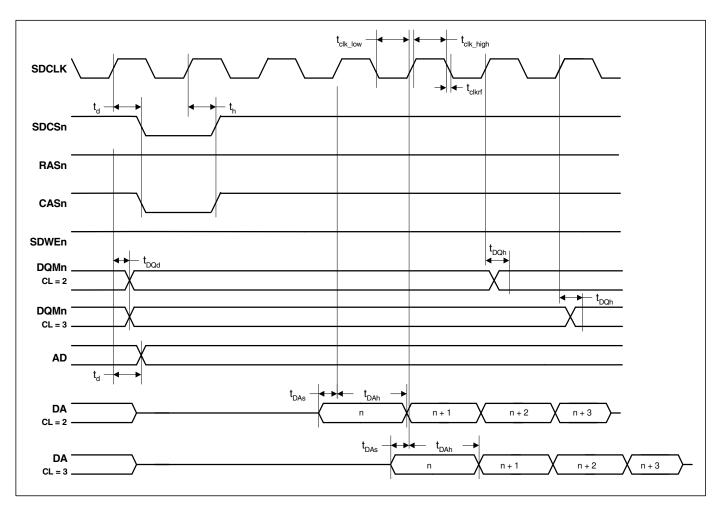

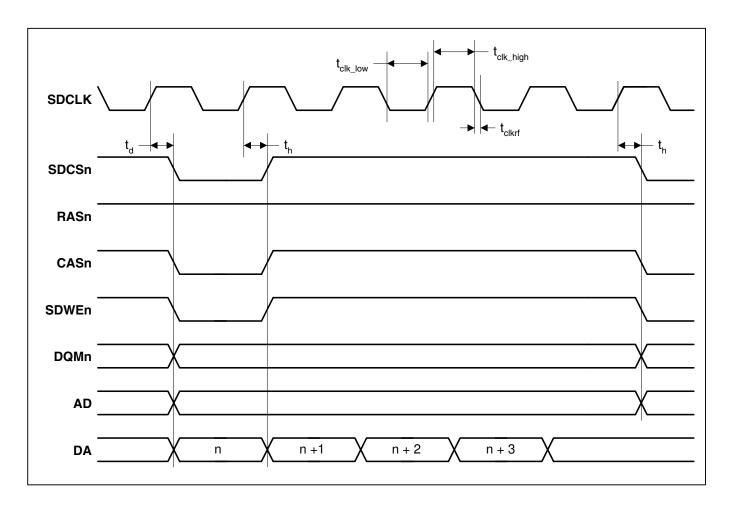

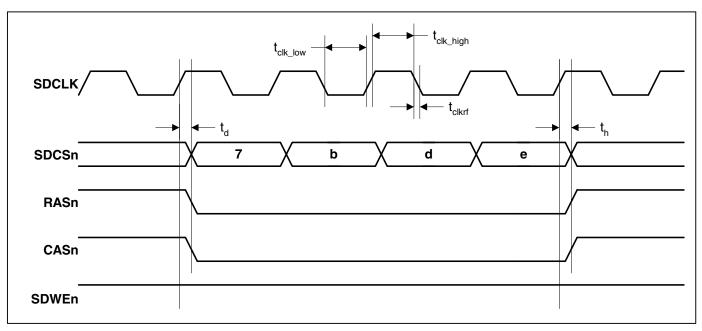

Figure 2 through Figure 5 define the timings associated with all phases of the SDRAM. The following table contains the values for the timings of each of the SDRAM modes.

| Parameter                                 | Symbol                | Min | Тур                      | Max | Unit |

|-------------------------------------------|-----------------------|-----|--------------------------|-----|------|

| SDCLK high time                           | t <sub>clk_high</sub> | -   | (t <sub>HCLK</sub> ) / 2 | -   | ns   |

| SDCLK low time                            | t <sub>clk_low</sub>  | -   | (t <sub>HCLK</sub> ) / 2 | -   | ns   |

| SDCLK rise/fall time                      | t <sub>clkrf</sub>    | -   | 2                        | 4   | ns   |

| Signal delay from SDCLK rising edge time  | t <sub>d</sub>        | -   | -                        | 8   | ns   |

| Signal hold from SDCLK rising edge time   | t <sub>h</sub>        | 1   | -                        | -   | ns   |

| DQMn delay from SDCLK rising edge time    | t <sub>DQd</sub>      | -   | -                        | 8   | ns   |

| DQMn hold from SDCLK rising edge time     | t <sub>DQh</sub>      | 1   | -                        | -   | ns   |

| DA valid setup to SDCLK rising edge time  | t <sub>DAs</sub>      | 2   | -                        | -   | ns   |

| DA valid hold from SDCLK rising edge time | t <sub>DAh</sub>      | 3   | -                        | -   | ns   |

## SDRAM Load Mode Register Cycle

Figure 2. SDRAM Load Mode Register Cycle Timing Measurement

## SDRAM Burst Read Cycle

Figure 3. SDRAM Burst Read Cycle Timing Measurement

## SDRAM Burst Write Cycle

Figure 4. SDRAM Burst Write Cycle Timing Measurement

## SDRAM Auto Refresh Cycle

Note: Chip select shown as bus to illustrate multiple devices being put into auto refresh in one access

Figure 5. SDRAM Auto Refresh Cycle Timing Measurement

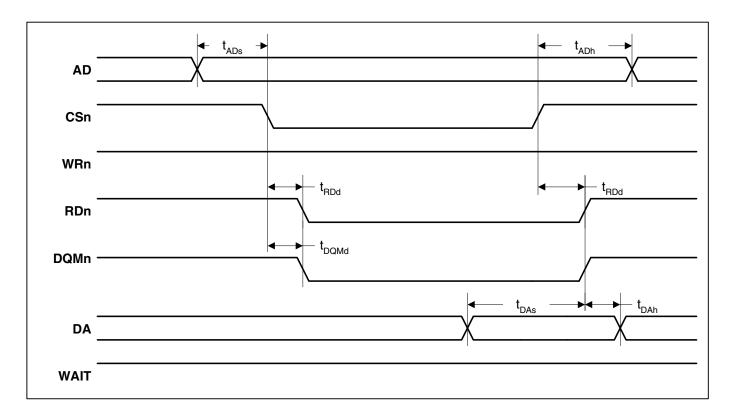

### Static Memory Single Word Read Cycle

| Parameter                            | Symbol            | Min                    | Тур                            | Max | Unit |

|--------------------------------------|-------------------|------------------------|--------------------------------|-----|------|

| AD setup to CSn assert time          | t <sub>ADs</sub>  | 0                      | -                              | -   | ns   |

| AD hold from CSn deassert time       | t <sub>ADh</sub>  | thclk                  | -                              | -   | ns   |

| RDn assert time                      | t <sub>RDpw</sub> | -                      | t <sub>HCLK</sub> × (WST1 + 2) | -   | ns   |

| CSn to RDn delay time                | t <sub>RDd</sub>  | -                      | -                              | 3   | ns   |

| CSn assert to DQMn assert delay time | t <sub>DQMd</sub> | -                      | -                              | 1   | ns   |

| DA setup to RDn deassert time        | t <sub>DAs</sub>  | t <sub>HCLK</sub> + 12 | -                              | -   | ns   |

| DA hold from RDn deassert time       | t <sub>DAh</sub>  | 0                      | -                              | -   | ns   |

See "Timing Conditions" on page 14 for definition of HCLK.

Figure 6. Static Memory Single Word Read Cycle Timing Measurement

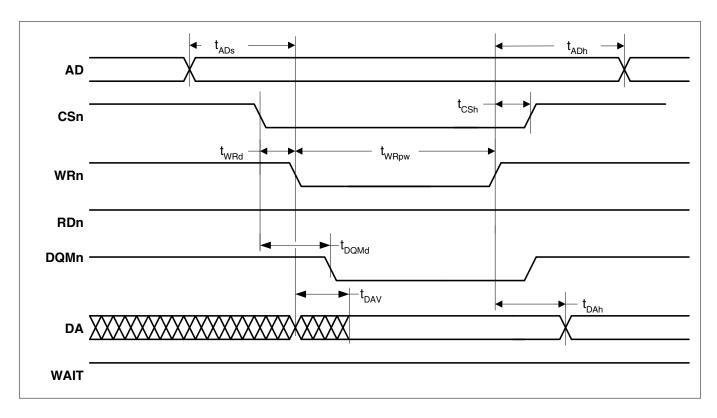

## Static Memory Single Word Write Cycle

| Parameter                          | Symbol            | Min                   | Тур                            | Max | Unit |

|------------------------------------|-------------------|-----------------------|--------------------------------|-----|------|

| AD setup to WRn assert time        | t <sub>ADs</sub>  | t <sub>HCLK</sub> - 3 | -                              | -   | ns   |

| AD hold from WRn deassert time     | t <sub>ADh</sub>  | t <sub>HCLK</sub> ×2  | -                              | -   | ns   |

| WRn deassert to CSn deassert time  | t <sub>CSh</sub>  | 7                     | -                              | -   | ns   |

| CSn to WRn assert delay time       | t <sub>WRd</sub>  | -                     | -                              | 2   | ns   |

| WRn assert time                    | t <sub>WRpw</sub> | -                     | t <sub>HCLK</sub> × (WST1 + 1) | -   | ns   |

| CSn to DQMn assert delay time      | t <sub>DQMd</sub> | -                     | -                              | 1   | ns   |

| WRn deassert to DA transition time | t <sub>DAh</sub>  | t <sub>HCLK</sub>     | -                              | -   | ns   |

| WRn assert to DA valid             | t <sub>DAV</sub>  | -                     | -                              | 8   | ns   |

Figure 7. Static Memory Single Word Write Cycle Timing Measurement

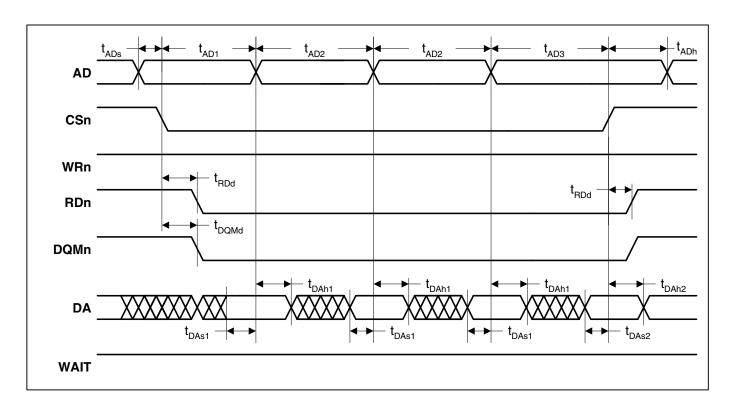

### Static Memory 32-bit Read on 8-bit External Bus

| Parameter                             | Symbol             | Min                    | Тур                                | Max | Unit |

|---------------------------------------|--------------------|------------------------|------------------------------------|-----|------|

| AD setup to CSn assert time           | t <sub>ADs</sub>   | t <sub>HCLK</sub>      | -                                  | -   | ns   |

| CSn assert to Address transition time | t <sub>AD1</sub>   | -                      | t <sub>HCLK</sub> × (WST1 + 1)     | -   | ns   |

| Address assert time                   | t <sub>AD2</sub>   | -                      | t <sub>HCLK</sub> × (WST1 + 1)     | -   | ns   |

| AD transition to CSn deassert time    | t <sub>AD3</sub>   | -                      | t <sub>HCLK</sub> × (WST1 + 2)     | -   | ns   |

| AD hold from CSn deassert time        | t <sub>ADh</sub>   | t <sub>HCLK</sub>      | -                                  | -   | ns   |

| RDn assert time                       | t <sub>RDpwL</sub> | -                      | t <sub>HCLK</sub> × (4 × WST1 + 5) | -   | ns   |

| CSn to RDn delay time                 | t <sub>RDd</sub>   | -                      | -                                  | 3   | ns   |

| CSn assert to DQMn assert delay time  | t <sub>DQMd</sub>  | -                      | -                                  | 1   | ns   |

| DA setup to AD transition time        | t <sub>DAs1</sub>  | 15                     | -                                  | -   | ns   |

| DA setup to RDn deassert time         | t <sub>DAs2</sub>  | t <sub>HCLK</sub> + 12 | -                                  | -   | ns   |

| DA hold from AD transition time       | t <sub>DAh1</sub>  | 0                      | -                                  | -   | ns   |

| DA hold from RDn deassert time        | t <sub>DAh2</sub>  | 0                      | -                                  | -   | ns   |

Figure 8. Static Memory Multiple Word Read 8-bit Cycle Timing Measurement

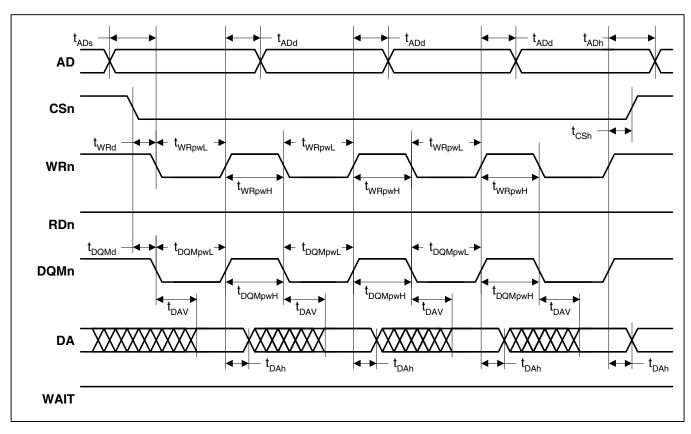

## Static Memory 32-bit Write on 8-bit External Bus

| Parameter                                 | Symbol              | Min                   | Тур                            | Max                          | Unit |

|-------------------------------------------|---------------------|-----------------------|--------------------------------|------------------------------|------|

| AD setup to WRn assert time               | t <sub>ADs</sub>    | t <sub>HCLK</sub> – 3 | -                              | -                            | ns   |

| WRn/DQMn deassert to AD transition time   | t <sub>ADd</sub>    | -                     | -                              | t <sub>HCLK</sub> + 6        | ns   |

| AD hold from WRn deassert time            | t <sub>ADh</sub>    | t <sub>HCLK</sub> × 2 | -                              | -                            | ns   |

| CSn hold from WRn deassert time           | t <sub>CSh</sub>    | 7                     | -                              | -                            | ns   |

| CSn to WRn assert delay time              | t <sub>WRd</sub>    | -                     | -                              | 2                            | ns   |

| WRn assert time                           | t <sub>WRpwL</sub>  | -                     | t <sub>HCLK</sub> × (WST1 + 1) | -                            | ns   |

| WRn deassert time                         | t <sub>WRpwH</sub>  | -                     | t <sub>HCLK</sub> × 2          | (t <sub>HCLK</sub> × 2) + 14 | ns   |

| CSn to DQMn assert delay time             | t <sub>DQMd</sub>   | -                     | -                              | 1                            | ns   |

| DQMn assert time                          | t <sub>DQMpwL</sub> | -                     | t <sub>HCLK</sub> × (WST1 + 1) | -                            | ns   |

| DQMn deassert time                        | t <sub>DQMpwH</sub> | -                     | -                              | (t <sub>HCLK</sub> × 2) + 7  | ns   |

| WRn / DQMn deassert to DA transition time | t <sub>DAh</sub>    | t <sub>HCLK</sub>     | -                              | -                            | ns   |

| WRn / DQMn assert to DA valid time        | t <sub>DAV</sub>    | -                     | -                              | 8                            | ns   |

Figure 9. Static Memory Multiple Word Write 8-bit Cycle Timing Measurement

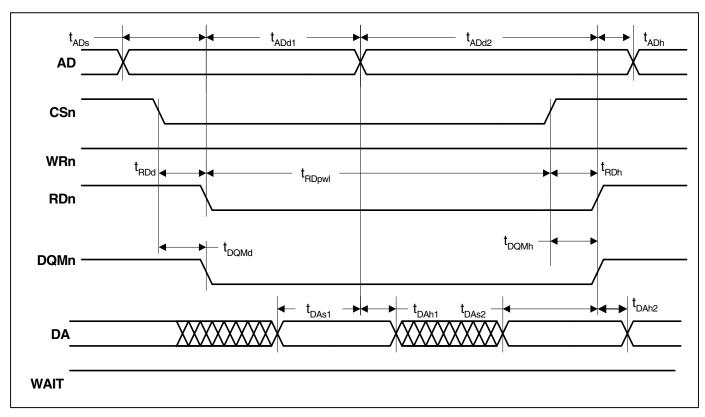

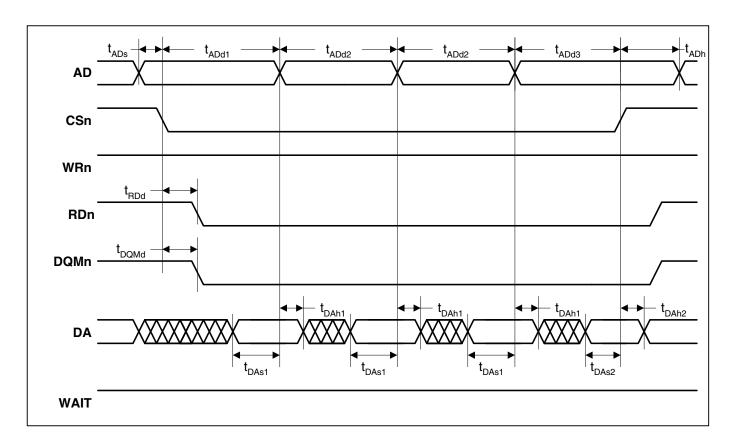

### Static Memory 32-bit Read on 16-bit External Bus

| Parameter                            | Symbol             | Min                    | Тур                                     | Max | Unit |

|--------------------------------------|--------------------|------------------------|-----------------------------------------|-----|------|

| AD setup to CSn assert time          | t <sub>ADs</sub>   | t <sub>HCLK</sub>      | -                                       | -   | ns   |

| CSn assert to AD transition time     | t <sub>ADd1</sub>  | -                      | t <sub>HCLK</sub> ×(WST1 + 1)           | -   | ns   |

| AD transition to CSn deassert time   | t <sub>ADd2</sub>  | -                      | t <sub>HCLK</sub> × (WST1 + 2)          | -   | ns   |

| AD hold from CSn deassert time       | t <sub>ADh</sub>   | t <sub>HCLK</sub>      | -                                       | -   | ns   |

| RDn assert time                      | t <sub>RDpwL</sub> | -                      | $t_{HCLK} \times ((2 \times WST1) + 3)$ | -   | ns   |

| CSn to RDn delay time                | t <sub>RDd</sub>   | -                      | -                                       | 3   | ns   |

| CSn assert to DQMn assert delay time | t <sub>DQMd</sub>  | -                      | -                                       | 1   | ns   |

| DA setup to AD transition time       | t <sub>DAs1</sub>  | 15                     | -                                       | -   | ns   |

| DA to RDn deassert time              | t <sub>DAs2</sub>  | t <sub>HCLK</sub> + 12 | -                                       | -   | ns   |

| DA hold from AD transition time      | t <sub>DAh1</sub>  | 0                      | -                                       | -   | ns   |

| DA hold from RDn deassert time       | t <sub>DAh2</sub>  | 0                      | -                                       | -   | ns   |

Figure 10. Static Memory Multiple Word Read 16-bit Cycle Timing Measurement

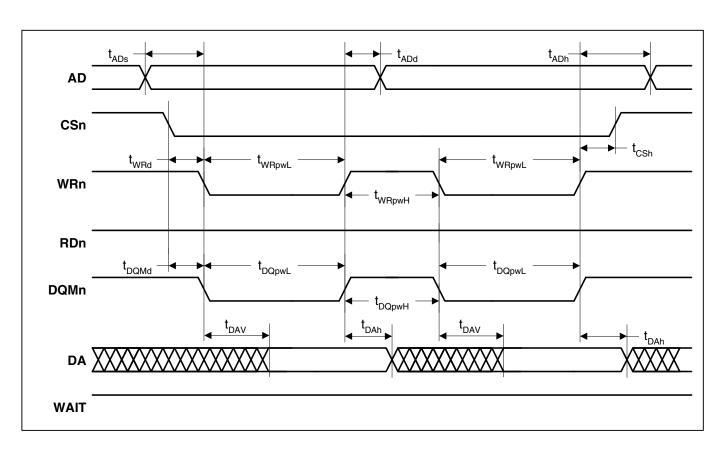

## Static Memory 32-bit Write on 16-bit External Bus

| Parameter                                 | Symbol              | Min                   | Тур                            | Max                          | Unit |

|-------------------------------------------|---------------------|-----------------------|--------------------------------|------------------------------|------|

| AD setup to WRn assert time               | t <sub>ADs</sub>    | t <sub>HCLK</sub> - 3 | -                              | -                            | ns   |

| WRn/DQMn deassert to AD transition time   | t <sub>ADd</sub>    | -                     | -                              | t <sub>HCLK</sub> + 6        | ns   |

| AD hold from WRn deassert time            | t <sub>ADh</sub>    | t <sub>HCLK</sub> × 2 | -                              | -                            | ns   |

| CSn hold from WRn deassert time           | t <sub>CSh</sub>    | 7                     | -                              | -                            | ns   |

| CSn to WRn assert delay time              | t <sub>WRd</sub>    | -                     | -                              | 2                            | ns   |

| WRn assert time                           | t <sub>WRpwL</sub>  | -                     | t <sub>HCLK</sub> × (WST1 + 1) | -                            | ns   |

| WRn deassert time                         | t <sub>WRpwH</sub>  | -                     | -                              | (t <sub>HCLK</sub> × 2) + 14 | ns   |

| CSn to DQMn assert delay time             | t <sub>DQMd</sub>   | -                     | -                              | 1                            | ns   |

| DQMn assert time                          | t <sub>DQMpwL</sub> | -                     | t <sub>HCLK</sub> × (WST1 + 1) | -                            | ns   |

| DQMn deassert time                        | t <sub>DQMpwH</sub> | -                     | -                              | (t <sub>HCLK</sub> × 2) + 7  | ns   |

| WRn / DQMn deassert to DA transition time | t <sub>DAh1</sub>   | t <sub>HCLK</sub>     | -                              | -                            | ns   |

| WRn / DQMn assert to DA valid time        | t <sub>DAV</sub>    | -                     | -                              | 8                            | ns   |

Figure 11. Static Memory Multiple Word Write 16-bit Cycle Timing Measurement

### Static Memory Burst Read Cycle

| Parameter                               | Symbol            | Min                    | Тур                            | Max | Unit |

|-----------------------------------------|-------------------|------------------------|--------------------------------|-----|------|

| CSn assert to Address 1 transition time | t <sub>ADd1</sub> | -                      | t <sub>HCLK</sub> × (WST1 + 1) | -   | ns   |

| Address assert time                     | t <sub>ADd2</sub> | -                      | t <sub>HCLK</sub> × (WST2 + 1) | -   | ns   |

| AD transition to CSn deassert time      | t <sub>ADd3</sub> | -                      | t <sub>HCLK</sub> × (WST1 + 2) | -   | ns   |

| AD hold from CSn deassert time          | t <sub>ADh</sub>  | t <sub>HCLK</sub>      | -                              | -   | ns   |

| CSn to RDn delay time                   | t <sub>RDd</sub>  | -                      | -                              | 3   | ns   |

| CSn to DQMn assert delay time           | t <sub>DQMd</sub> | -                      | -                              | 1   | ns   |

| DA setup to AD transition time          | t <sub>DAs1</sub> | 15                     | -                              | -   | ns   |

| DA setup to CSn deassert time           | t <sub>DAs2</sub> | t <sub>HCLK</sub> + 12 | -                              | -   | ns   |

| DA hold from AD transition time         | t <sub>DAh1</sub> | 0                      | -                              | -   | ns   |

| DA hold from RDn deassert time          | t <sub>DAh2</sub> | 0                      | -                              | -   | ns   |

Note: These characteristics are valid when the Page Mode Enable (Burst Mode) bit is set. See the User's Guide for details.

Figure 12. Static Memory Burst Read Cycle Timing Measurement