Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# EQCO62T20.3 6.25 Gbps Asymmetric Coax Driver EQCO31T20.3 3.125 Gbps Asymmetric Coax Driver

#### **Features**

- Complies with the CoaXPress v1.1 Camera Standard <sup>(1)</sup>

- Supports up to 68 Meters of Cable at 6.25 Gbps Using High-Quality Coax

- Supports up to 212 Meters of Cable at 1.25 Gbps Using High-Quality Coax

- Single-Chip Solutions for Both the Camera Side and the Frame Grabber Side, Making a Bidirectional Connection Over a Single 75Ω Coax Cable

- · Full-Duplex, Bidirectional Data Channel

- Downlink Speeds from 1.25 Gbps up to 6.25 Gbps; Differential Interfacing Straightforward with Internal Termination Resistors

- Uplink Supporting 21 Mbps, Allowing Nanoseconds Precise Triggering Events Driven by the Frame Grabber

- Supports Power Distribution Over the Coax up to 900 mA, Powering the Camera Through the Same Coax Transporting Data Signals

- Low Power Consumption (<70 mW, 1.2V supply)</li>

- 16-Pin, 0.65 mm Pin Pitch, 4 mm QFN Package

- Small PCB Footprint for EQCO62T20 and Off-Chip Components, with Guaranteed RF-Performance

- -40°C to +85°C Industrial Temperature Range

- · Pb-Free and RoHS Compliant

### **Applications**

- · High-Definition/High-Bandwidth Links to Cameras

- Machine Vision for Semiconductor Chips and Display Panel Inspection Systems

- · Military, Aerospace, Medical Applications

- Broadcast and Surveillance Camera Systems

- Traffic License Plate and Monitoring Systems

- High-Speed Inspection Systems for Food Inspection, Bottling Inspection, Panel Inspection, etc.

- Any application requiring a single coax cable which carries power, video data and camera control stream

#### Introduction

The EQCO62T/R20<sup>(2)</sup> chipset is a driver/equalizer chipset that forms a bidirectional, full-duplex communication link over a single coax cable.

The EQCO62T/R20 chipset is designed to transport up to 6.25 Gbps over the downlink channel and to transport 21 Mbps over the uplink channel. The EQCO62T20 is designed to transmit the downlink signal up to 6.25 Gbps and receive the uplink signal. The EQCO62R20 is designed to receive the downlink signal up to 6.25 Gbps and to transmit the uplink signal. Power can be transferred over the same cable via external inductors.

The chipset is designed to work with several types of  $75\Omega$  coaxial cables, including legacy cables as well as thin, flexible lightweight cables.

- Note 1: CoaXPress V1.1 standard. Free download from the JIIA website: http://jiia.org/en/standardization/list/

- 2: The EQCO31T20 and EQCO31R20 are lower-speed versions of the EQCO62T20 and EQCO62R20, with a maximum bit rate of 3.125 Gbps for the high-speed downlink and the same uplink speed.

# **Typical Link Performance**

Table 1, Table 2 and Table 3 give an overview of typical link performance at room temperature for the link containing the EQCO62T20 coax driver in conjunction with the EQCO62R20 receiver, using the downlink channel, uplink channel and power transmission simultaneously. Performance for EQCO62T/R20 and EQCO31T/R20 is equal for bit rates up to 3.125 Gbps.

TABLE 1: BELDEN TYPICAL LINK PERFORMANCE

|            | Name | Belden 7731A     | Belden 1694A         | Belden 1505A       | Belden 1505F | Belden 1855A      |

|------------|------|------------------|----------------------|--------------------|--------------|-------------------|

|            | Туре | Long<br>Distance | Industry<br>Standard | Compromise<br>Coax | Flexible     | Thinnest<br>Cable |

| Diameter   | (mm) | 10.3             | 6.99                 | 5.94               | 6.15         | 4.03              |

| 1.25 Gbps  | (m)  | 194              | 130                  | 107                | 80           | 55                |

| 2.5 Gbps   | (m)  | 162              | 110                  | 94                 | 66           | 55                |

| 3.125 Gbps | (m)  | 147              | 100                  | 86                 | 60           | 55                |

| 5.0 Gbps   | (m)  | 87               | 60                   | 52                 | 35           | 38                |

| 6.25 Gbps  | (m)  | 58               | 40                   | 35                 | 23           | 25                |

TABLE 2: GEPCO TYPICAL LINK PERFORMANCE

|            | Name | Gepco<br>VHD1100 | Gepco<br>VSD2001     | Gepco<br>VPM2000   | Gepco<br>VHD2000M | Gepco<br>VDM230   |

|------------|------|------------------|----------------------|--------------------|-------------------|-------------------|

|            | Туре | Long<br>Distance | Industry<br>Standard | Compromise<br>Coax | Flexible          | Thinnest<br>Cable |

| Diameter   | (mm) | 10.3             | 6.91                 | 6.15               | 6.15              | 4.16              |

| 1.25 Gbps  | (m)  | 212              | 140                  | 109                | 81                | 66                |

| 2.5 Gbps   | (m)  | 185              | 120                  | 94                 | 67                | 66                |

| 3.125 Gbps | (m)  | 169              | 110                  | 86                 | 61                | 62                |

| 5.0 Gbps   | (m)  | 102              | 66                   | 53                 | 36                | 38                |

| 6.25 Gbps  | (m)  | 68               | 44                   | 35                 | 24                | 25                |

TABLE 3: CANARE TYPICAL LINK PERFORMANCE<sup>(1)</sup>

|            | <u></u> |                  |                      |                    |                  |                    |  |  |

|------------|---------|------------------|----------------------|--------------------|------------------|--------------------|--|--|

|            | Name    | Canare<br>L-7CFB | Canare<br>L-5CFB     | Canare<br>L-4CFB   | Canare<br>L-3CFB | Canare<br>L-2.5CFB |  |  |

|            | Туре    | Long<br>Distance | Industry<br>Standard | Compromise<br>Coax | Thin Cable       | Thinnest<br>Cable  |  |  |

| Diameter   | (mm)    | 10.2             | 7.7                  | 6.1                | 5.5              | 4                  |  |  |

| 1.25 Gbps  | (m)     | 165              | 118                  | 94                 | 72               | 43                 |  |  |

| 2.5 Gbps   | (m)     | 135              | 98                   | 79                 | 66               | 43                 |  |  |

| 3.125 Gbps | (m)     | 122              | 88                   | 71                 | 60               | 43                 |  |  |

| 5.0 Gbps   | (m)     | 71               | 52                   | 42                 | 36               | 30                 |  |  |

| 6.25 Gbps  | (m)     | 46               | 34                   | 28                 | 24               | 20                 |  |  |

Note 1: Specifications from Canare are only up to 2 GHz. 5 Gbps and 6.25 Gbps performance are by extrapolation.

#### **Table of Contents**

| 1.0 | Device Overview            | 4  |

|-----|----------------------------|----|

| 2.0 | Application Information    | 8  |

|     | Electrical Characteristics |    |

| 4 0 | Packaging                  | 17 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 1.0 DEVICE OVERVIEW

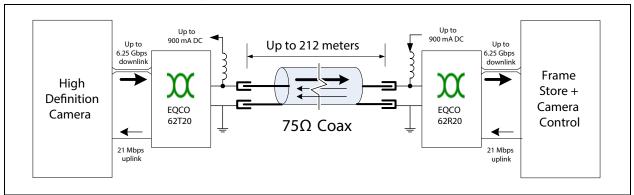

The EQCO62T/R20 single-coax chipset is designed to simultaneously transmit and receive signals along with power on a single  $75\Omega$  coax cable. In one direction, a downlink signal is transmitted. In the opposite direction, a lower-speed uplink is provided. The EQCO62T/R20 chipset consists of two chips. The EQCO62T20 is a high-speed line driver with an integrated low-speed receiver. The EQCO62R20 is a high-speed receiver with an integrated low-speed transmitter. Figure 1-1 illustrates a typical EQCO62T/R20 link setup.

The downlink signal is transmitted with 600 mV transmit amplitude at the EQCO62T20 side. This signal is attenuated in the coax and recovered by an equalizer integrated in the EQCO62R20. The low-speed uplink is transmitted with a lower amplitude of 130 mV to limit the crosstalk with the downlink channel.

The downlink channel is intended for 8B/10B NRZ coded data with bitrates from 1.25 Gbps up to 6.25 Gbps. The low-speed uplink operates at a bit rate of 21 Mbps, and has a single-ended LVTLL input and output.

In addition to the downlink channel and the low-speed uplink, the system allows power transmission over the coax by using ferrite beads and external inductors. These external inductors give the communication channel a high-pass characteristic. The uplink receiver inside the EQCO62T20 chip recovers the signal lost by this high-pass filter. Appropriate inductors need to be selected for correct operation of the link. Correct operation is only guaranteed with the inductor combination used in Figure 2-1, even though other components might be suited.

The EQCO62T/R20 chipset is compatible with the CoaXPress v1.1 camera standard.

FIGURE 1-1: TYPICAL EQCO62T/R20 LINK SETUP

# 1.1 Pinout and Pin Description

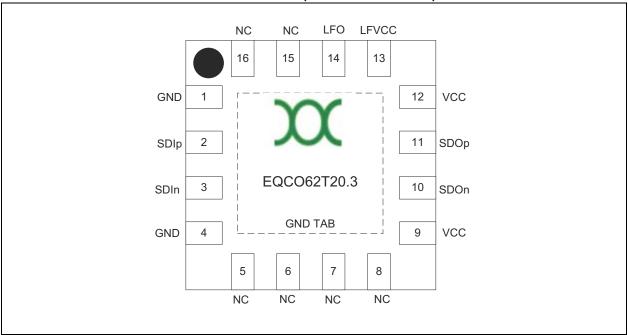

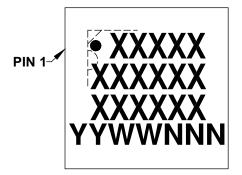

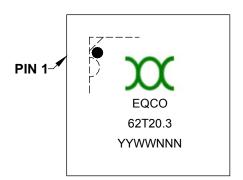

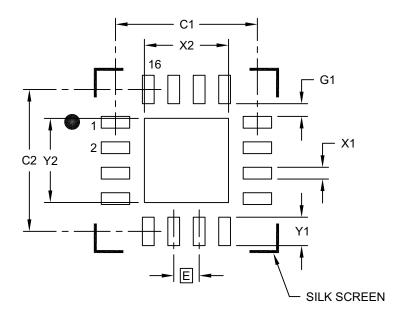

FIGURE 1-2: EQCO62T20.3 PIN DIAGRAM(VIEWED FROM TOP)

TABLE 1-1: EQCO62T20.3 PIN DESCRIPTIONS

| Pin Number         | Pin Name  | Signal Type         | Description                                                                                                                                                                                                                                 |

|--------------------|-----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (TAB)              | GND       | Power               | Connect to ground.                                                                                                                                                                                                                          |

| 9, 12              | VCC       | Power               | Connect to +1.2V of power supply.                                                                                                                                                                                                           |

| 1, 4               | GND       | Power               | Connect to ground of power supply.                                                                                                                                                                                                          |

| 2, 3               | SDIp/SDIn | Differential Input  | Serial input positive/negative differential serial input. Typical input swing is $2x300$ mV. Minimal input swing is $2x250$ mV. $2x50\Omega$ on-chip termination resistor.                                                                  |

| 11, 10             | SDOp/SDOn | Differential Output | Differential serial output pair. On-Chip $75\Omega$ termination resistors. SDOp is connected to the coax cable by a capacitor. SDOn needs to be connected to GND by $75\Omega$ termination resistor and capacitor. Swing is fixed to VCC/2. |

| 13                 | LFVCC     | Power               | Power supply for the uplink output (between 1.2V and 3.3V).                                                                                                                                                                                 |

| 14                 | LFO       | Output              | Low-frequency uplink output. LVTTL with output swing equal to LFVCC. Supports capacitive loads up to 20 pF for 21 Mbps operation.                                                                                                           |

| 5, 6, 7, 8, 15, 16 | NC        | _                   | Do not connect. Leave these pins floating. Used for internal testing.                                                                                                                                                                       |

#### 1.1.1 SDIp/SDIn

SDIp/SDIn together form a differential input pair. The serial data received on these pins will be transmitted on SDOp/SDOn. The input pre-driver automatically corrects for variations in signal levels and different edge slew rates at these inputs before they go into the active splitter/combiner for transmission over the coax.

Between SDIp and SDIn inputs, there is a termination resistor of  $100\Omega$ . The intention is to always use AC coupling.

A transmit wake-up detection circuit puts both the input pre-driver and the output driver into a low-power mode when no signal is detected on the SDIp/SDIn signal pair.

## 1.1.2 SDOp/SDOn

The signal at the inputs SDIp/SDIn is transmitted onto the cable by outputs SDOp/SDOn. Both outputs are internally terminated with  $75\Omega$ .

The signal on the SDOp pin is the sum of the incoming signal (i.e. the signal transmitted by the EQCO62R20 on the far end side of the coax) and the outgoing signal (i.e. the signal created based on SDIp/SDIn). The farend signal is extracted by subtraction of the near-end signal and the far-end signal, and is restored by the uplink receiver inside the EQCO62T20 chip. The SDOn signal carries a precise anti-phase signal to the transmitted signal on SDOp. SDOn must be connected directly to GND at the connector via a resistor precisely matched to the impedance of the coaxial cable used and an AC coupling capacitor.

#### 1.1.3 LFO

LFO is the output of the uplink receiver inside the EQCO62T20. The maximum allowed capacitance at the output is 20 pF, with rise and fall times of 5 ns. The maximum output current is 1 mA when LFVCC is 3.3V.

#### 1.1.4 LFVCC

The output driver of the uplink receiver in the EQCO62T20 has a separate power supply pin. The power supply voltages can be 1.2V up to 3.3V. The output swing at LFO is equal to this power supply voltage. A filter capacitor must be placed close to the LFVVC pin of the EQCO62T20.

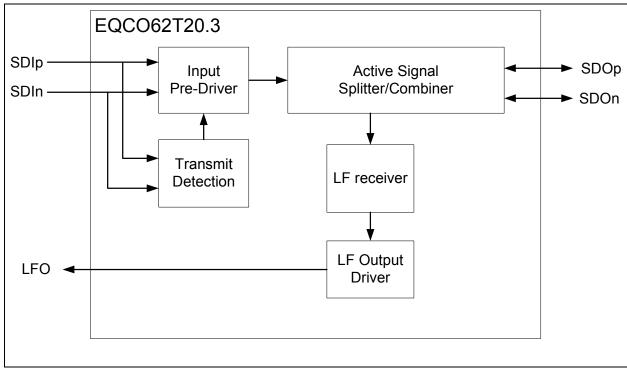

### 1.2 Circuit Operation

FIGURE 1-3: EQC062T20.3 BLOCK DIAGRAM SHOWING ELECTRICAL CONNECTIONS

#### 1.2.1 PRE-DRIVER

The pre-driver removes any dependency for the amplitude and rise time of the incoming signal on SDI.

### 1.2.2 ACTIVE SIGNAL SPLITTER/ COMBINER

The active splitter/combiner controls the amplitude and rise time of the outgoing coax signal and transmits it via a  $75\Omega$  output termination resistor. The output resistor, when balanced with the coax characteristic impedance, also forms part of a hybrid splitter circuit which subtracts the TX output from the signal on the SDO output to give yield the far-end TX signal.

#### 1.2.3 TRANSMIT DETECTION

The transmit detection detects if an input signal is applied at SDI. The detection circuit looks at the signal amplitude of SDI; if no signal is detected, the pre-driver and output driver are disabled. The LF receiver then continues to operate independently. At the moment the output driver is turned on or off, there can be a bit error in the uplink channel, e.g. by the LF-receiver.

#### 1.2.4 LF RECEIVER

The uplink receiver removes unwanted crosstalk from the transmitted near-end signal. Afterwards, the uplink signal is restored by detecting edges coming from the uplink signal. At the moment the high-speed output driver is turned on or off, there can be a bit error in the uplink channel, e.g. by the LF-receiver. The initial output state of the LF receiver can be wrong, and subsequent bits will still be received correctly.

#### 1.2.5 LF OUTPUT DRIVER

The uplink output driver converts the signal detected by the LF receiver to an LVTTL signal with a controlled rise and fall time. It is required to set the output signal amplitude of this LVTTL signal by connecting the LFVCC to the appropriate power supply voltage (max 3.3V).

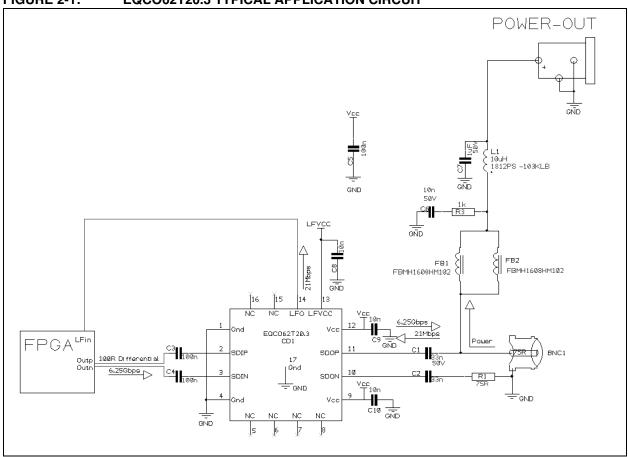

### 2.0 APPLICATION INFORMATION

Figure 2-1 illustrates a typical schematic implementation.

FIGURE 2-1: EQCO62T20.3 TYPICAL APPLICATION CIRCUIT

TABLE 2-1: COMPONENT RECOMMENDATION FOR THE EQCO62T20.3 BOARD LAYOUT

| Element     | Value                         | Size      | Recommended Component                     |

|-------------|-------------------------------|-----------|-------------------------------------------|

| Fb1, Fb2    | 1 kΩ @ 100 MHz Ferrite Bead   | 0603      | FBMH1608HM102 from Taiyo Yuden (Critical) |

| L1          | 10 μH                         | 1812      | 1812PS_103 from Coilcraft (Critical)      |

| R1          | 75Ω ±1%                       | 0402      |                                           |

| R3          | 1 kΩ                          | 0402      |                                           |

| C1          | 33 nF, 50V, X7R               | 0603      |                                           |

| C2          | 33 nF, X7R                    | 0402/0603 |                                           |

| C3, C4, C5  | 100 nF, X7R                   | 0402      |                                           |

| C6          | 10 nF, 50V, X7R               | 0402      |                                           |

| C7          | 1 μF, 50V, X7R                | 0805      |                                           |

| C8, C9, C10 | 10 nF, X7R                    | 0402      |                                           |

| BNC1        | 75Ω right angle BNC connector |           | 5413558-1 from Tyco (Recommended)         |

Ferrite Beads Fb1 and Fb2 (FBMH1608HM102 from Taiyo Yuden) and inductor L1 (1812PS\_103 from Coilcraft [10  $\mu$ H]) are recommended for CoaXPress. For other applications the inductor value can be larger, leading to a physical larger inductor.

Connector BNC1 (75 $\Omega$  right angle BNC connector 5413558-1 from Tyco) is recommended for CoaXPress.

Other inductors/ferrite beads/BNC connectors can possibly be used, however, they must be selected carefully for their RF-performance, since performance can decrease significantly.

#### 2.1 **Guidelines for PCB Layout**

When using the EQCO62T/R20 chipset at its full purpose, including low-speed uplink and power supply transmission, it is important not to disturb the RFperformance of the high-speed downlink channel. Implementing the circuit illustrated in Figure 2-1 with a different PCB layout will in first instance not deliver full data sheet performance. The simplest way of meeting optimal performance, including jitter and return-loss requirements, is to precisely follow the component and layout recommendations. Note that at multi-gigabit speeds, using "equivalent" components or small PCB layout changes (even moving a via) can have significant detrimental effects.

The easiest way for achieving the requirements of the CoaXPress 1.1 specification is to use the recommended circuits, components and layout illustrated in Figure 2-1. For easy implementation, Microchip will provide the Gerber file. Please ask for it by email.

Note: Email address: coaxpress@microchip.com

#### 2.1.1 RIGHT ANGLE BNC

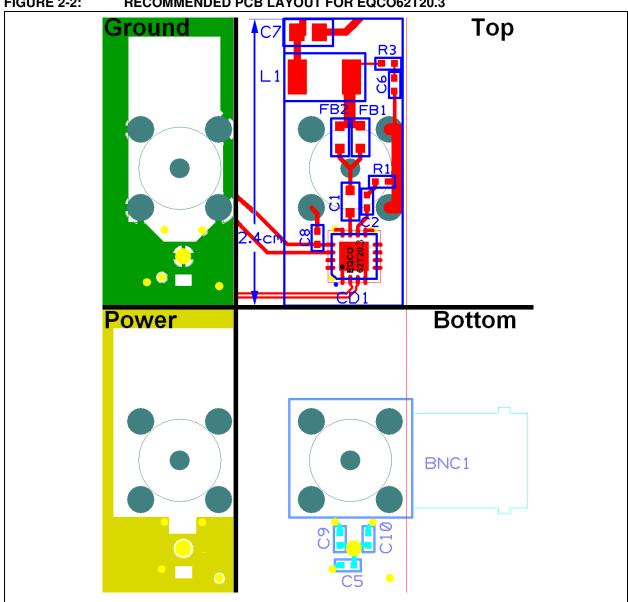

Figure 2-2 below shows the four layers of the recommended footprint for the EQCO62T20.3 chip and the off-chip components that are critical for the RF-performance of the system.

FIGURE 2-2: **RECOMMENDED PCB LAYOUT FOR EQCO62T20.3**

In this layout, the size of the PCB area needed for the chip is minimized. Approximately two times the BNC footprint area is required for the full bidirectional system: including the necessary elements for the power transport.

The differential input of the chip must be a  $100\Omega$ differential transmission line. To minimize the parasitic capacitance of the input pins, a cut-out of the ground and power plane underneath the input pins is recommended. For best performance, no vias should be used in this high-speed signal path.

A large cut-out underneath the right angle BNC connector, the AC coupling capacitors, ferrite beads and inductor is needed for minimal parasitics.

This proposed layout is designed to be largely independent of the used PCB-layer stack. This will work as well for four, six or even higher numbers of layers. Possible extra layers should have cut-outs as large as the full proposed footprint.

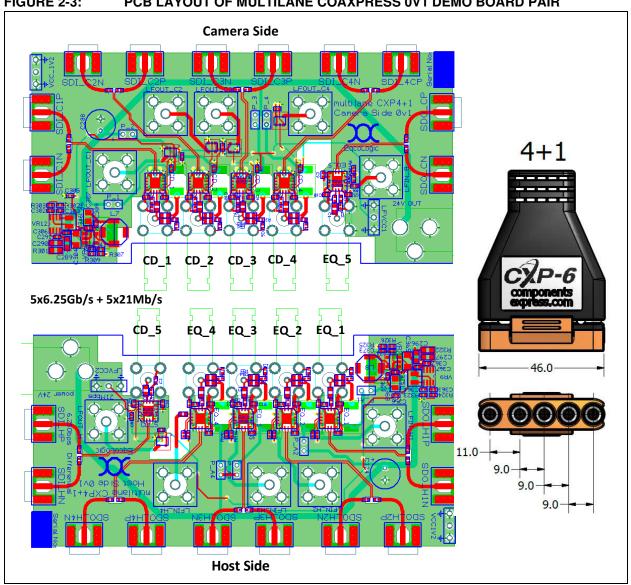

**FIGURE 2-3:** PCB LAYOUT OF MULTILANE COAXPRESS 0V1 DEMO BOARD PAIR

## 2.1.2 MULTILANE COAXPRESS 4+1 LAYOUT WITH DIN1.0/2.3 CONNECTORS

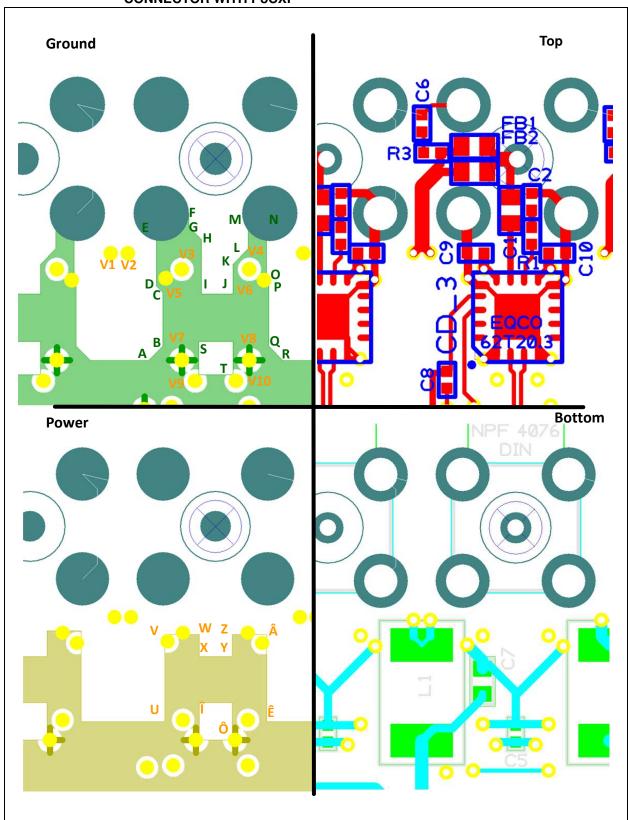

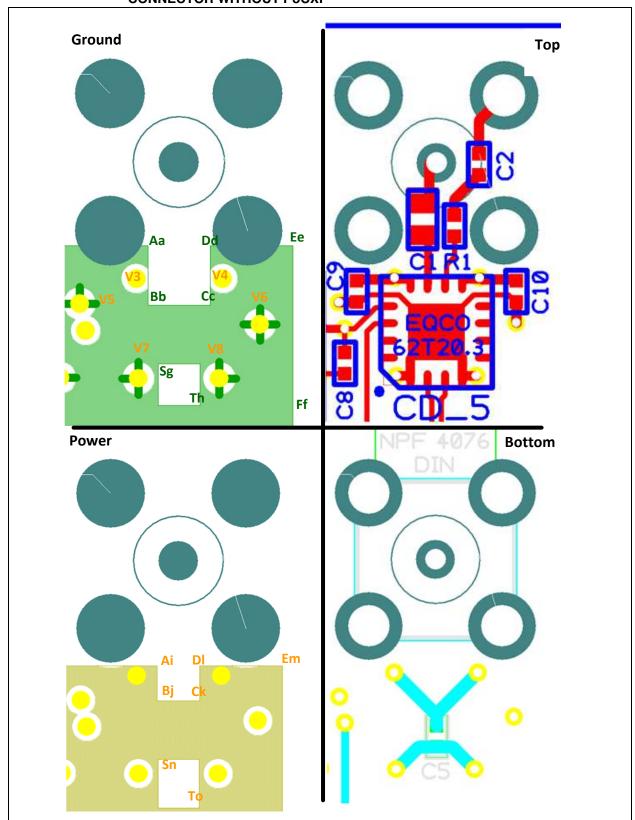

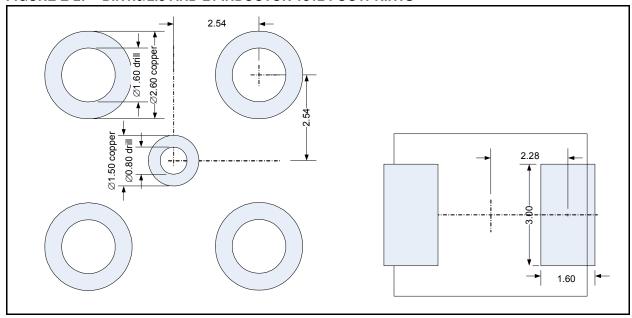

Figure 2-3 shows an example of a Multilane CoaXPress 4+1 setup. The recommended Din1.0/2.3 connector is the NPF 4076 from Cambridge Connectors. The cable example shows the pitches in millimeters. Figure 2-4 shows the four layers of the recommended footprints and the off-chip components that are critical for RF-performance of the cable drivers CD\_1 to CD\_4 at the camera side, which have Power over CoaXPress (PoCXP). Figure 2-5 shows the variant without PoCXP used for CD 5 at the host side. The exact dimensions in millimeters are given in Section 4.1 "Package Marking Information". It is recommended to copy these dimensions, especially the connection between the DIN1.0/2.3 connector and the chip, as this is a complex entity with coupled currents and compensated parasitic capacitances.

Despite the critical layout, this proposed layout is designed to be largely independent of the used PCB-layer stack, as the critical parts are mainly the top-layer only. This will work as well for four, six or even higher numbers of layers. Possible extra layers should have cut-outs as large as the full proposed footprint.

In these layouts, the size of the PCB area needed for the chip is minimized. This allows multiple lanes close together.

Only two of four connector GND pins are connected to the GND plane to reduce the capacitance.

The differential CD inputs must be a  $100\Omega$  differential transmission line. A cut-out of the ground and power plane underneath the input pins is recommended to minimize the parasitic capacitance. For best performance, no vias should be used in this high-speed signal path.

The Components Express 4+1 connector in Figure 2-3 is only shown as an example. Other connector configurations are available with DIN1.0/2.3 connectors such as 6+1, 2+1, 1+1, dual or single lane configurations.

FIGURE 2-4: RECOMMENDED PCB LAYOUT FOR EQCO62T20.3 WITH DIN1.0/2.3 CONNECTOR WITH PoCXP

FIGURE 2-5: RECOMMENDED PCB LAYOUT FOR EQCO62T20.3 WITH DIN1.0/2.3 CONNECTOR WITHOUT PoCXP

#### 2.2 Guidelines for Power Receive Unit

At the Power-OUT connection, the voltage supply for the camera (including the power supply for the EQCO62T20.3) is expected.

This load current should have low ripple. High-frequency ripple will be rejected by C7/L1/FB1/FB2 filtering in the reference circuit. However, mid-frequency ripple is to be avoided by the power supply itself.

In a typical application, one could want to step-down from the 24V supply to all supply voltages needed inside the camera. It is in this case preferred to use a DC-to-DC converter that has a high switching frequency (e.g. 2 MHz) above one that has lower switching frequency (200 kHz). The latter typically induces larger voltage spikes at the Power-OUT connection. These will be only partially filtered out by said filter; the remainder will become crosstalk for the uplink channel.

When too much crosstalk remains on the uplink channel, additional power supply filtering is required. This may be achieved by placing an extra filter network (not shown) in series with the Power-OUT node.

#### 2.3 Power Over CoaXPress

The EQCO62T20.3 is compatible with the Power over CoaXPress system (PoCXP). Hence, power can be switched on and off by the host (e.g. frame grabber) through the 10  $\mu$ H inductor specified by the CXP standard. This switching is supported through a relay and through an electronic switch.

Powering through a wide-band bias-T is also supported.

The EQCO62T20.3 is also protected against the following events:

- Hot plugging by frame grabber: in case the frame grabber has already applied its 24V on the coax when connecting the cable, no damage will occur to the EQCO62T20.3 when connecting the powered coax cable.

- Fast turn on and turn off of power supply by frame grabber

Direct 24V application, i.e. not through a 10  $\mu$ H inductor, is not supported since it causes permanent damage to the EQCO62T20 device.

### 3.0 ELECTRICAL CHARACTERISTICS

# 3.1 Absolute Maximum Ratings

Stresses beyond those listed under this section may cause permanent damage to the device. These are stress ratings only and are not tested. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

TABLE 3-1: ABSOLUTE MAXIMUM RATINGS

| Parameter                | Conditions                           | Min. | Тур. | Max. | Units |

|--------------------------|--------------------------------------|------|------|------|-------|

| Storage Temperature      |                                      | -65  | _    | +150 | °C    |

| Ambient Temperature      | Power Applied                        | -55  | _    | +125 | °C    |

| Operating Temperature    | Normal Operation<br>(VCC = 1.2V ±5%) | -40  | _    | +85  | °C    |

| Supply Voltage to Ground |                                      | -0.5 | _    | +1.4 | V     |

| DC Input Voltage         |                                      | -0.5 | _    | +1.6 | V     |

| DC Voltage to Outputs    |                                      | -0.5 | _    | +1.6 | V     |

| Current into Outputs     | Outputs Low                          | _    | _    | 90   | mA    |

TABLE 3-2: ELECTRICAL CHARACTERISTICS (OVER THE OPERATING VCC AND -40 TO +85°C RANGE)

| Parameter            | Description                                                               | Min.  | Тур.  | Max.  | Unit |  |  |

|----------------------|---------------------------------------------------------------------------|-------|-------|-------|------|--|--|

| Power Supply         | Power Supply                                                              |       |       |       |      |  |  |

| VCC                  | Supply Voltage                                                            | 1.15  | 1.2   | 1.25  | V    |  |  |

| Is                   | Supply Current, both Transmitting and Receiving                           | _     | 60    | _     | mA   |  |  |

| I <sub>sr</sub>      | Supply Current when only Receiving                                        | _     | 30    | _     | mA   |  |  |

| SDIp/SDIn Input      |                                                                           |       |       |       |      |  |  |

| $\triangle V_i$      | Input Amplitude V <sub>SDIP,n</sub>                                       | 2x250 | 2x300 | _     | mV   |  |  |

| V <sub>turnon</sub>  | △Vi to Turn On Transmit Function                                          | _     | 2x150 | 2x250 | mV   |  |  |

| V <sub>turnoff</sub> | △Vi to Turn Off Transmit Function                                         | 2x50  | 2x150 | _     | mV   |  |  |

| R <sub>input</sub>   | Differential Input Termination                                            | _     | 2x50  | _     | Ω    |  |  |

| SDOp Connection to   | о Соах                                                                    |       |       |       |      |  |  |

| Z <sub>coax</sub>    | Coax Cable Characteristic Impedance                                       | _     | 75    | _     | Ω    |  |  |

| R <sub>SDOP</sub>    | Input Impedance between SDOp and VCC/GND                                  | _     | 75    | _     | Ω    |  |  |

| R <sub>loss</sub>    | Coax Return Loss as Seen on SDOp pin<br>Frequency Range = 5 MHz-1 GHz     | _     | _     | -15   | dB   |  |  |

| R <sub>loss</sub>    | Coax Return Loss as Seen on SDOp pin<br>Frequency Range = 1 GHz-1.5 GHz   | _     | _     | -10   | dB   |  |  |

| R <sub>loss</sub>    | Coax Return Loss as Seen on SDOp pin<br>Frequency Range = 1.5 GHz-3.2 GHz | _     | _     | -7    | dB   |  |  |

| △V <sub>TX</sub>     | Transmit Amplitude                                                        | 500   | 600   | 700   | mV   |  |  |

| t <sub>rise_tx</sub> | Rise/Fall Time 20% to 80% of △Vtx                                         | _     | _     | 80    | ps   |  |  |

| DCD                  | Duty Cycle Distortion on of V <sub>SDOp</sub>                             | _     | 5     | _     | ps   |  |  |

# TABLE 3-2: ELECTRICAL CHARACTERISTICS (OVER THE OPERATING VCC AND -40 TO +85°C RANGE) (CONTINUED)

| LFO Output (LVTTL-Like) |                                                               |     |   |     |    |  |

|-------------------------|---------------------------------------------------------------|-----|---|-----|----|--|

| LFVCC                   | Uplink Output Driver Power Supply                             | 1.2 | _ | 3.3 | V  |  |

| t <sub>rise LFO</sub>   | Rise/Fall Time 20% to 80% of VLFO for 20 pF Load LFVCC = 1.2V | _   | 6 | _   | ns |  |

|                         | LFVCC = 3.3V                                                  | _   | 5 | _   | ns |  |

## TABLE 3-3: JITTER NUMBERS

| Parameter                                             | Conditions                                                                                                                                         | Min. | Тур. | Max. | Units |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Additive Peak to Peak Jitter on SDOp/SDOn (EQCO62T20) | Downlink Signal = 1.25 up to<br>6.25 Gbps, prbs7                                                                                                   | _    | _    | 30   | ps    |

| EQCO31T20                                             | Downlink Signal = 1.25 up to 3.125 Gbps, prbs7                                                                                                     | _    | _    | 30   | ps    |

| Peak to Peak Jitter on LFO                            | 0-130m Belden 1694A coax, Over Full<br>VCC and Temperature Range;<br>Low-Speed Signal = 21 Mbps, 8B/10B,<br>Downlink Signal= 1.25-6.25 Gbps,8B/10B | _    | _    | 15   | ns    |

### 4.0 PACKAGING INFORMATION

# 4.1 Package Marking Information

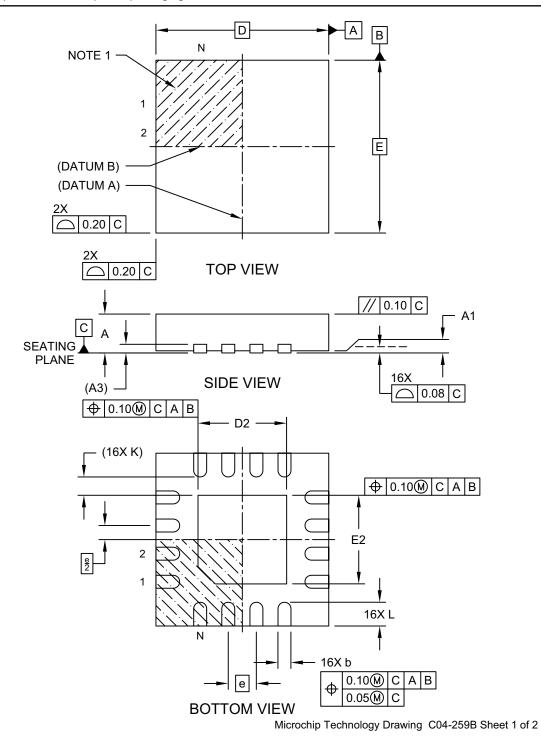

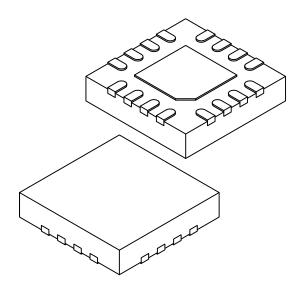

16-Lead Plastic Quad Flat, No Lead Package – 4x4x0.9 mm Body [QFN]

16-Lead QFN (4x4x0.9 mm)

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

# 16-Lead Plastic Quad Flat, No Lead Package (8E) - 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# 16-Lead Plastic Quad Flat, No Lead Package (8E) - 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |                |           |      |

|-------------------------|-------------|----------------|-----------|------|

| Dimension               | Limits      | MIN            | NOM       | MAX  |

| Number of Pins          | N           |                | 16        |      |

| Pitch                   | е           |                | 0.65 BSC  |      |

| Overall Height          | Α           | 0.80           | 0.87      | 0.95 |

| Standoff                | A1          | 0.00           | 0.02      | 0.05 |

| Terminal Thickness      | A3          |                | 0.20 REF  |      |

| Overall Width           | E           |                | 4.00 BSC  |      |

| Exposed Pad Width       | E2          | 1.95           | 2.05      | 2.15 |

| Overall Length          | D           |                | 4.00 BSC  |      |

| Exposed Pad Length      | D2          | 1.95           | 2.05      | 2.15 |

| Terminal Width          | b           | 0.25 0.30 0.35 |           |      |

| Terminal Length         | L           | 0.45 0.55 0.65 |           |      |

| Terminal-to-Exposed-Pad | K           |                | 0.425 REF |      |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-259B Sheet 2 of 2

# 16-Lead Plastic Quad Flat, No Lead Package (8E) - 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |          |       |       |

|---------------------------------|-------------|----------|-------|-------|

| Dimension                       | Limits      | MIN      | NOM   | MAX   |

| Contact Pitch                   | Е           | 0.65 BSC |       |       |

| Optional Center Pad Width       | X2          |          |       | 2.15  |

| Optional Center Pad Length      | Y2          |          |       | 2.15  |

| Contact Pad Spacing             | C1          |          | 3.625 |       |

| Contact Pad Spacing             | C2          |          | 3.625 |       |

| Contact Pad Width (X16)         | X1          |          |       | 0.30  |

| Contact Pad Length (X16)        | Y1          |          |       | 0.725 |

| Contact Pad to Center Pad (X16) | G1          | 0.20     |       |       |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2259A

# **APPENDIX A: REVISION HISTORY**

# Revision B (March 2016)

- Updated Section 4.0 "Packaging Information".

- Removed electrostatic discharge ratings from Table 3-1.

- · Minor typographical changes.

# **Revision A (August 2014)**

This is the initial release of the document in the Microchip format. This replaces EqcoLogic document version 1v5.

#### TABLE A-1: REVISION HISTORY

| Version | Date    | Comments                                                           |  |

|---------|---------|--------------------------------------------------------------------|--|

| 1v5     | 1/27/14 | Added references                                                   |  |

| 1v4     | 4/10/12 | Added Multilane CoaXPress 4+1 layout with DIN1.0/2.3 connectors    |  |

| 1v3     | 10/4/11 | Section 5.5 on PoXCXP was added                                    |  |

| 1v2     | 9/29/11 | C1 and C2 in application circuit of Figure 5 have changed to 33 nF |  |

| 1v1     | 8/31/11 | Quality review                                                     |  |

| 1v0     | 8/30/11 | Initial release of this document                                   |  |

### APPENDIX B: TYPICAL LINE DRIVER CHARACTERISTICS

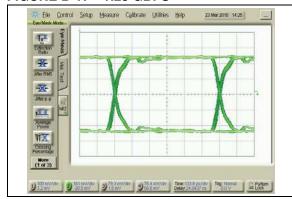

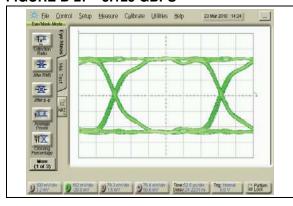

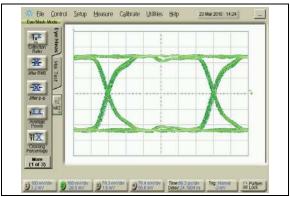

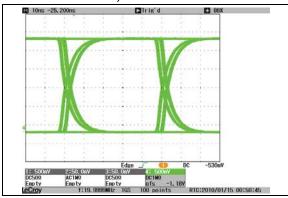

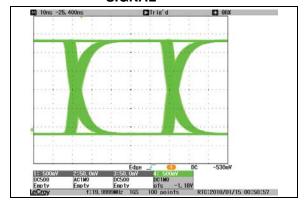

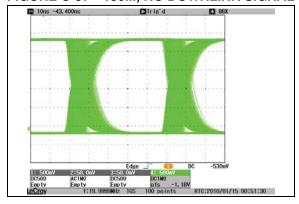

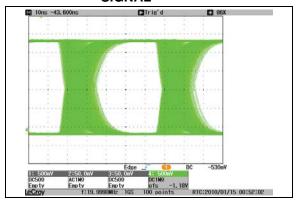

All measurements at VCC = 1.2V, Temp = +25°C, data pattern = PRBS7, 2x300 mV input amplitude.

**Note:** The imperfections in the output eye are caused by the limited bandwidth of the  $75\Omega$  to  $50\Omega$  matching pad that was used in this setup. The output amplitude is reduced due to this matching pad.

### FIGURE B-1: 1.25 GBPS

### FIGURE B-2: 3.125 GBPS

#### FIGURE B-3: 6.25 GBPS (EQCO62T20 ONLY)

### FIGURE B-4: 2.5 GBPS

FIGURE B-5: 5 GBPS (EQCO62T20 ONLY)

### APPENDIX C: TYPICAL UPLINK CHARACTERISTICS

All measurements at VCC = 1.2V, Temp = +25°C, data pattern = 8B/10B test pattern at 21 Mbps, 110 mV transmit amplitude using Belden 1694A coaxial cable. Measurements include power supply transmission; EQCO62T20 is powered over the cable. Measured into 15 pF capacitive load.

FIGURE C-1: 0M, NO DOWNLINK SIGNAL

FIGURE C-2: 0M, DOWNLINK SIGNAL = 1.25 GBPS, 8B/10B CODED SIGNAL

FIGURE C-3: 130M, NO DOWNLINK SIGNAL

FIGURE C-4: 130M, DOWNLINK SIGNAL = 1.25 GBPS, 8B/10B CODED SIGNAL

### APPENDIX D: TYPICAL RETURN-LOSS

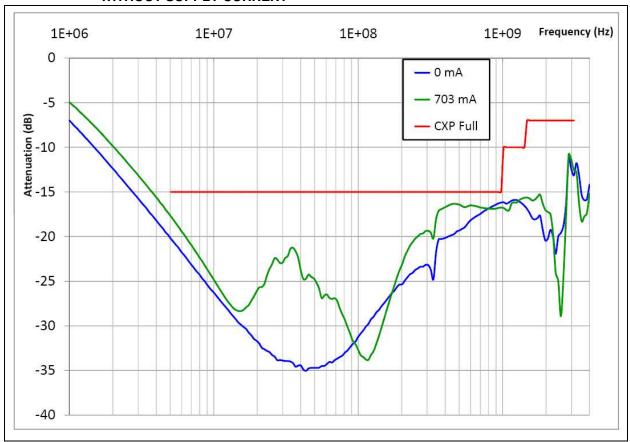

Figure D-1 shows the return-loss at the BNC connector of the EQCO62T20.3 evaluation board as shown in Section 2.0 "Application Information" and Section 2.1 "Guidelines for PCB Layout" with a supply current of 0 mA and 703 mA (maximum supply current for CoaXPress) through the inductor (L1) and the ferrite beads (Fb1 & Fb2) and compares it with the CoaXPress (Full-Speed) return-loss specification.

FIGURE D-1: RETURN-LOSS OF THE EQCO62T20.3 BNC EVALUATION BOARD WITH AND WITHOUT SUPPLY CURRENT

# APPENDIX E: FOOTPRINTS USED FOR THE MULTILANE COAXPRESS LAYOUT

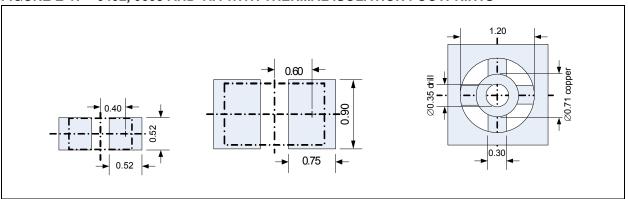

FIGURE E-1: 0402, 0603 AND VIA WITH THERMAL ISOLATION FOOTPRINTS

FIGURE E-2: DIN1.0/2.3 AND L1 INDUCTOR 1812 FOOTPRINTS

TABLE E-1: COMPONENT POSITIONS OF Figure 2-4

| TABLE 2 1. Com Chen Tool Tool Tool Tool Tool Tool Tool Too |            |        |        |       |        |  |  |

|------------------------------------------------------------|------------|--------|--------|-------|--------|--|--|

| Component                                                  | Footprint  | X      | Υ      | Angle |        |  |  |

| NPF 4076                                                   | DIN1.0/2.3 | 0      | 0      | _     | Bottom |  |  |

| EQCO62T20.3                                                | QFN        | 0      | -7.4   | _     |        |  |  |

| C1 (50V)                                                   | 0603       | -0.325 | -2.4   | 90°   |        |  |  |

| C2                                                         | 0402       | 0.675  | -2     | 90°   |        |  |  |

| R1                                                         | 0402       | 0.675  | -3.6   | 90°   |        |  |  |

| FB1                                                        | 0603       | -2.025 | 0.6    | _     |        |  |  |

| FB2                                                        | 0603       | -2.025 | -0.6   | _     |        |  |  |

| R3                                                         | 0402       | -4.025 | 0.3    | _     |        |  |  |

| C6 (50V)                                                   | 0402       | -4.5   | 1.675  | 90°   |        |  |  |

| C9                                                         | 0402       | -1.975 | -4.4   | _     |        |  |  |

| C10                                                        | 0402       | 1.875  | -4.4   | _     |        |  |  |

| C8                                                         | 0402       | -3.325 | -10.35 | 90°   |        |  |  |