Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## USB 2.0 Protection IC with Battery Charger Detection

#### **Features**

- · VBUS Over-Voltage Protection

- Protects internal circuits from VBUS up to 9V

- Over-Voltage/Under-Voltage Lockout opens VBUS switch

- Interrupt to indicate Over-Voltage/Under-Voltage Lockout

- Integrated Low R<sub>DSON</sub> FET

- USB Port ESD Protection (DP/DM/VBUS)

- ±15kV (air discharge)

- ±15kV (contact discharge)

- IEC 61000-4-2 level 4 ESD protection without external devices

- High Speed USB Mux for multiplexing the USB lanes between different functions (USB3750 only)

- Switch the USB connector between two different functions

- High bandwidth USB switch passes HS USB signals

- Provides USB Battery Charger Detection for:

- USB-IF Battery Charging compliant Dedicated Charging Ports (DCP)

- USB-IF Battery Charging compliant Charging Downstream Port (CDP)

- Standard Downstream Port (SDP); i.e. USB host or downstream hub port

- Dedicated SE1 type chargers

- Dead Battery Provision Support (USB375x-1 only)

- Allows 100 mA trickle charging from VBUS when attached to a Standard Downstream Port (SDP) while not enumerated

- Built-in 100mA current limiting option

- Microchip RapidCharge Anywhere™ Provides:

- 3-times the charging current through a USB port over traditional solutions

- USB-IF Battery Charging 1.2 compliance to any portable device

- Charging current up to 1.5Amps via compatible USB host or dedicated charger

- Dedicated Charging Port (DCP), Charging (CDP) & Standard (SDP) Downstream Port support

- flexPWR<sup>®</sup> Technology

- Extremely low current design ideal for battery powered applications

- Maximizes power delivered to the system

- Industrial Operating Temperature -40°C to +85°C

- 16-Pin QFN RoHS compliant package; (3.0 mm x 3.0 mm x 0.9 mm height

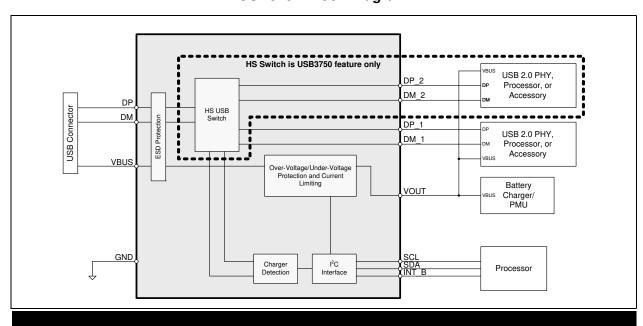

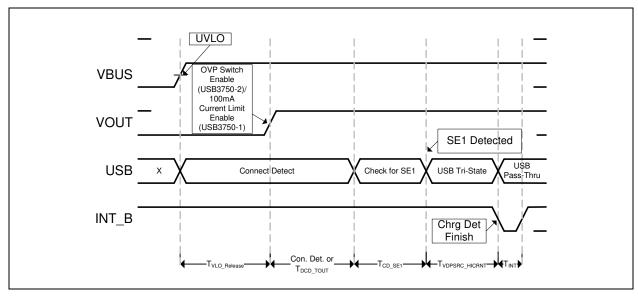

#### **USB375x Block Diagram**

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### **Table of Contents**

| 1.0 Introduction                        | . 4 |

|-----------------------------------------|-----|

| 2.0 Pin Layout                          | . 5 |

| 3.0 Electrical Specifications           |     |

| 4.0 General Operation                   | 12  |

| 5.0 Application Notes                   | 22  |

| 6.0 Package Information                 | 25  |

| Appendix A: Data Sheet Revision History | 27  |

| The Microchip Web Site                  |     |

| Customer Change Notification Service    | 28  |

| Customer Support                        | 28  |

| Product Identification System           |     |

#### 1.0 INTRODUCTION

The USB375x integrates many features that have historically been discrete devices in a mobile product. This device provides significant VBUS protection for the entire system, robust USB interface ESD protection, a USB 2.0 compliant High Speed switch, and USB-IF Battery Charger Detection (revision 1.2) capabilities that are essential to the latest mobile products.

Several advanced features allow the USB375x to be optimized for portable applications and to reduce both eBOM part count and printed circuit board (PCB) area. Outstanding ESD robustness eliminates the need for external ESD protection devices.

In addition to the integrated ESD protection on the USB interface, the USB375x provides VBUS Over-Voltage Protection (OVP).

The USB375x integrated battery charger detection circuitry supports USB-IF Battery Charger Detection. Battery charger detection will begin automatically whenever VBUS rises above the UVLO threshold, and can also be completed manually through the I<sup>2</sup>C interface. The USB375x can detect a range of USB battery chargers including a Standard Downstream Port (SDP), a Charging Downstream Port (CDP), and a Dedicated Charging Port (DCP). For more information on USB battery charger detection, please see the USB Battery Charging Specification, Revision 1.2 (Note 1).

The I<sup>2</sup>C interface gives processor control over the USB Switch, charger detection, OVLO settings, and status of the USB375x. In addition, custom charger detection can be implemented through the I<sup>2</sup>C interface.

The USB375x family is enabled with Microchip's RapidCharge Anywhere<sup>TM</sup> which supports USB-IF Battery Charging 1.2 for any portable device (Note 1). RapidCharge Anywhere<sup>TM</sup> provides three times the charging current through a USB port over traditional solutions which translate up to 1.5 amps via compatible USB host or dedicated charger. In addition, this provides a complete USB charging ecosystem between device and host ports such as Dedicated Charging Port (DCP), Charging (CDP) and Standard (SDP) Downstream Ports.

#### 1.1 Reference Documents

- · Universal Serial Bus Specification, Revision 2.0

- USB Battery Charging Specification, Revision 1.2 (Note 1)

**Note 1:** The device's Data Contact Detect Timeout parameter does not conform to the USB Battery Charging Specification. However, this will not affect other factors in charger detection. Refer to Table 3-2, "Electrical Specifications," on page 7 for additional information.

#### 2.0 PIN LAYOUT

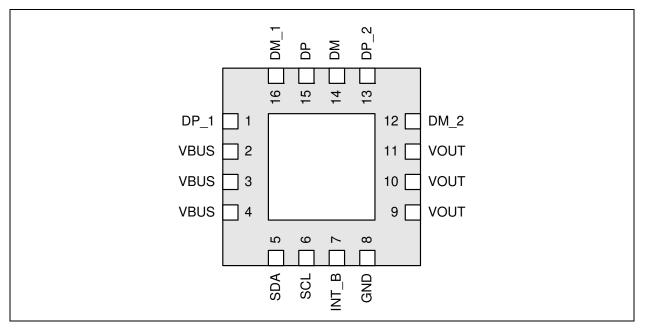

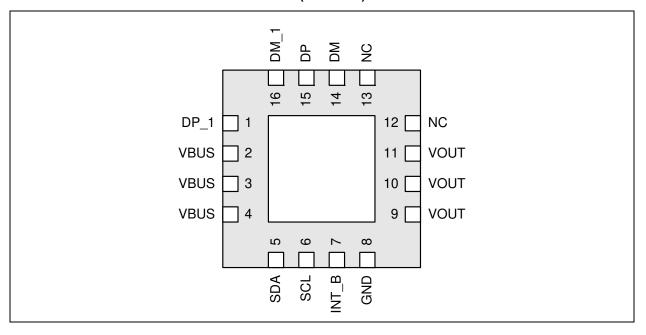

#### 2.1 Pin Diagram

The USB375x is available in a QFN (3 x 3 mm) package. The USB3750 pin diagram is detailed in Figure 2-1. The USB3751 pin diagram is detailed in Figure 2-2.

FIGURE 2-1: QFN PACKAGE DIAGRAM (USB3750)

FIGURE 2-2: QFN PACKAGE DIAGRAM (USB3751)

#### 2.2 Pin Definitions

The following table details the ball/pin definitions for the package diagrams above.

| Pin | Name      | Type/<br>Direction    | Description                                                                                                                                   |  |  |

|-----|-----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15  | DP        | Analog                | USB Mux Output                                                                                                                                |  |  |

| 14  | DM        | Analog                |                                                                                                                                               |  |  |

| 1   | DP_1      | Analog                | USB Mux Input 1                                                                                                                               |  |  |

| 16  | DM_1      | Analog                |                                                                                                                                               |  |  |

| 13  | DP_2 / NC | Analog                | USB Mux Input 2 (USB3750 Only) These pins are No Connects for the USB3751 (do not connect)                                                    |  |  |

| 12  | DM_2 / NC | Analog                | Those pine are the commons for the common,                                                                                                    |  |  |

| 8   | GND       | Analog                | Ground. The QFN package flag should also connected to ground.                                                                                 |  |  |

| 6   | SCL       | Input                 | I <sup>2</sup> C Clock input. This pin is an open drain output and requires a 10Kohm pull-up.                                                 |  |  |

| 5   | SDA       | Open Drain/<br>IO     | Bi-Directional I <sup>2</sup> C data. This pin is an open drain output and requires a 10Kohm pull-up.                                         |  |  |

| 7   | INT_B     | Open Drain/<br>Output | Open Drain Interrupt. This pin is an open drain output that is pulled low when an interrupt occurs. A 10Kohm pull-up is required on this pin. |  |  |

| 9   |           | Analog                | Overvoltage switch output. This pin is connected to VBUS when the overvoltage protection switch is enabled. It is also the output             |  |  |

| 10  | VOUT      | , maiog               | of the 100mA current limit. The three <b>VOUT</b> pins must be connected together. When <b>VBUS</b>                                           |  |  |

| 11  | ı         |                       | is between UVLO and OVLO <b>VOUT</b> is connected to <b>VBUS</b> . When <b>VBUS</b> is below UVLO or above OVLO the USB375x will tri-state.   |  |  |

| 2   |           | Analog                | VBUS pin of the USB connector. The three VBUS pins must be connected together. When the                                                       |  |  |

| 3   | VBUS      |                       | OVP switch is closed, the VBUS pin will be isolated from VOUT. When the OVP switch is open, VBUS will be connected to VOUT.                   |  |  |

| 4   |           |                       | The USB375x is powered from this pin.                                                                                                         |  |  |

#### 3.0 ELECTRICAL SPECIFICATIONS

### 3.1 Absolute Maximum Ratings

TABLE 3-1: ABSOLUTE MAXIMUM RATINGS

| Description                  | Rating        | Unit                             |   |

|------------------------------|---------------|----------------------------------|---|

| VBUS Voltage to GND          |               | -0.3 to 9.0                      | V |

| VOUT Voltage to GND          |               | -0.3 to 7.5                      | V |

| Any other pin to GND         |               | -0.3 to 5.5                      | V |

| Operating Temperature Range  | -40 to +85    | С                                |   |

| Storage Temperature Range    |               | -55 to +150                      | С |

| ESD Rating                   | HBM           | 8,000                            | V |

|                              | IEC-61000-4-2 | 15,000 (Air)<br>15,000 (Contact) | V |

| ESD Rating (SDA, SCL, INT_B) | HBM           | 1,500                            | V |

Stresses beyond the Absolute Maximum Ratings may damage the USB375x.

### 3.2 Electrical Specifications

TABLE 3-2: ELECTRICAL SPECIFICATIONS

| Characteristic                                                                                     | Symbol                | MIN  | TYP | MAX  | Units | Conditions                                                |  |  |  |

|----------------------------------------------------------------------------------------------------|-----------------------|------|-----|------|-------|-----------------------------------------------------------|--|--|--|

| $V_{VBUS} = 5.0V$ , $T_A = -40C$ to 85C, all typical values at $T_A = 27C$ unless otherwise noted. |                       |      |     |      |       |                                                           |  |  |  |

| VBUS Characteristics                                                                               |                       |      |     |      |       |                                                           |  |  |  |

| VBUS Operating range                                                                               | V <sub>VBUS</sub>     | 2    |     | 9    | ٧     |                                                           |  |  |  |

| VBUS Over Voltage Lockout (USB3750 Only)                                                           | V <sub>OVLO</sub>     | 6.2  |     | 6.9  | V     | USB3750 Only                                              |  |  |  |

| VBUS Over Voltage Lockout (USB3751 Only)                                                           | V <sub>OVLO</sub>     | 5.45 |     | 6.15 | V     | USB3751 Only                                              |  |  |  |

| VBUS Under Voltage Lockout                                                                         | $V_{\text{UVLO}}$     | 3.3  | 3.4 | 3.8  | V     |                                                           |  |  |  |

| VBUS Over Voltage Hysteresis                                                                       | V <sub>OVLO</sub>     |      | 100 |      | mV    |                                                           |  |  |  |

| VBUS Under Voltage Hysteresis                                                                      | V <sub>UVLO</sub>     |      | 100 |      | mV    |                                                           |  |  |  |

| Operating Current (OVP open)                                                                       | I <sub>DD_OFF</sub>   |      | 110 |      | uA    | V <sub>VBUS</sub> < V <sub>UVLO</sub>                     |  |  |  |

| Operating Current (OVP closed)                                                                     | I <sub>DD_ON</sub>    | 75   | 115 | 370  | uA    | V <sub>UVLO</sub> < V <sub>VBUS</sub> < V <sub>OVLO</sub> |  |  |  |

| Operating Current (100mA Limit enabled)                                                            | I <sub>DD</sub>       | 150  | 185 | 480  | uA    | V <sub>UVLO</sub> < V <sub>VBUS</sub> < V <sub>OVLO</sub> |  |  |  |

| VBUS Switch Characteristics                                                                        |                       |      | •   |      |       |                                                           |  |  |  |

| Overvoltage Switch ON Resistance                                                                   | R <sub>ON_VBUS</sub>  |      | 70  |      | mohm  | QFN package                                               |  |  |  |

| Overvoltage Switch Current                                                                         |                       |      |     | 1.8  | Α     | V <sub>UVLO</sub> < V <sub>VBUS</sub> < V <sub>OVLO</sub> |  |  |  |

| Overvoltage Switch OFF<br>Leakage                                                                  | I <sub>OFF_VBUS</sub> |      |     | 1    | uA    | VBUS = 5.0V; VOUT = 0V                                    |  |  |  |

| VBUS Resistance to Ground                                                                          | R <sub>VBUS</sub>     | 100  |     |      | Kohm  |                                                           |  |  |  |

| VBUS Capacitance                                                                                   | C <sub>VBUS</sub>     | 1.0  |     |      | uF    |                                                           |  |  |  |

| Charger Detection Characteristics                                                                  | s 4.4 < <b>VBUS</b> < | 5.5V |     |      |       |                                                           |  |  |  |

| DP and DM leakage                                                                                  |                       |      |     | 1    | uA    | 0.0V < Vpin < 3.3V                                        |  |  |  |

| Data Source Voltage                                                                                | V <sub>DAT_SRC</sub>  | 0.5  |     | 0.7  | V     | I <sub>DAT_SRC</sub> > 250uA                              |  |  |  |

| Data Detect Voltage                                                                                | $V_{DAT\_REF}$        | 0.25 |     | 0.4  | V     |                                                           |  |  |  |

TABLE 3-2: ELECTRICAL SPECIFICATIONS (CONTINUED)

| Characteristic                           | Symbol                         | MIN   | TYP | MAX  | Units | Conditions                      |

|------------------------------------------|--------------------------------|-------|-----|------|-------|---------------------------------|

| Data Connect Detect Current<br>Source    | I <sub>DP_SRC</sub>            | 7     |     | 13   | uA    |                                 |

| Data Sink Current                        | I <sub>DAT_SINK</sub>          | 50    |     | 150  | uA    |                                 |

| DP/DM Single Ended RX<br>Threshold       | V <sub>SE_RX</sub>             | 0.8   |     | 1.95 | V     | 4.75V < VBUS < 5.25V            |

| SE1 High Current Charger RX<br>Threshold | V <sub>SE_RXH</sub>            | 2.1   |     | 2.56 | V     | 4.75V < VBUS < 5.25V            |

| DP/DM Pull Down Resistors                | R <sub>PD</sub>                | 14.25 |     | 24.8 | Kohm  |                                 |

| USB Mux Characteristics (USB3)           | 750 Only)                      |       |     |      |       |                                 |

| USB Mux On Resistance                    | R <sub>ON_USB</sub>            |       |     | 10   | ohm   | 0V < Vin < 3.3V                 |

|                                          |                                |       |     | 2.5  |       | 0V < Vin < 0.4V                 |

| USB Mux Off Leakage                      | I <sub>OFF_USB</sub>           |       |     | 0.85 | uA    | 0V < Vin < 3.3V                 |

| On Capacitance                           | C <sub>ON_USB</sub>            |       |     | 9    | pF    |                                 |

| Off Capacitance                          | C <sub>OFF_USB</sub>           |       |     | 6.5  | pF    |                                 |

| Off Isolation                            |                                |       |     | -35  | dB    | $R_L = 50$ ohm, $F = 250MHz$    |

| Crosstalk                                |                                |       |     | -40  | dB    | $R_L = 50$ ohm, $F = 250MHz$    |

| Bandwidth (-3dB)                         | BW                             |       |     | 1000 | MHz   | $R_L = 50$ ohm, $C_L = 0pF$     |

|                                          |                                |       |     | 800  |       | $R_L = 50$ ohm, $C_L = 5pF$     |

|                                          |                                |       |     | 500  |       | $R_L = 50$ ohm, $C_L = 10pF$    |

| Control Signal Characteristics           |                                |       |     |      |       |                                 |

| Input Logic High Threshold               | V <sub>IN_H</sub>              | 1.4   |     |      | ٧     | VBUS > UVLO                     |

| Input Logic Low Threshold                | V <sub>IN_L</sub>              |       |     | 0.4  | ٧     | VBUS > UVLO                     |

| Output Drive Strength                    | V <sub>OUT_L</sub>             |       |     | 0.4  | V     | VBUS > UVLO, 4.0mA sink current |

| Control Signal Leakage Current           |                                |       | 1   |      | nA    | 0 < Vpin < <b>VOUT</b>          |

| Timing Characteristics                   |                                |       |     |      |       |                                 |

| Clock Accuracy                           | T <sub>CLK</sub>               | 0.5   | 1   | 2    | ms    | Oscillator Accuracy             |

| Soft POR Reset Time                      | T <sub>SOFT_POR</sub>          |       |     | 20   | ms    | Time to autoclear Soft POR.     |

| UVLO and OVLO Release Timer              | T <sub>VLO_ RELEASE</sub>      | 3     |     | 6.5  | ms    |                                 |

| UVLO and OVLO Engage Time                | T <sub>VLO_ENGAGE</sub>        | 0.5   |     | 1.7  | ms    |                                 |

| Data Contact Detect Timeout              | T <sub>DCD_TOUT</sub>          | 40    |     | 150  | ms    | See Note 1                      |

| Vdat_src and Idat_sink Enable Time       | T <sub>VDPSRC_ON</sub>         | 40    | 80  | 160  | ms    |                                 |

| Delay from Vdat_det to OVP switch enable | T <sub>VDPSRC_HICR</sub><br>NT | 40    | 80  | 160  | ms    |                                 |

| SE1 Charger Detection wait for SE1 timer | T <sub>CD_SE1</sub>            | 40    | 80  | 160  | ms    |                                 |

| Interrupt Self Clear Timer               | T <sub>INT</sub>               | 0.5   | 1   | 2    | ms    |                                 |

**Note 1:** The device's Data Contact Detect Timeout (T<sub>DCD\_TOUT</sub>) parameter does not conform to the USB Battery Charging Specification's T<sub>DCD\_TOUT</sub> minimum of 300 ms. However, this will not affect other factors in charger detection.

### 3.3 Timing Diagrams

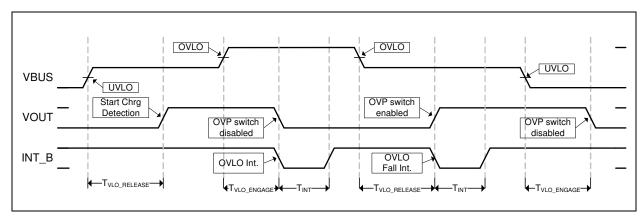

#### 3.3.1 UVLO AND OVLO TIMING

The timing diagram below shows the operation of the OVP switch as VBUS crosses the UVLO and OVLO thresholds. The behavior of the INT\_B signal is also shown in Figure 3-1 below.

FIGURE 3-1: UVLO AND OVLO TIMING

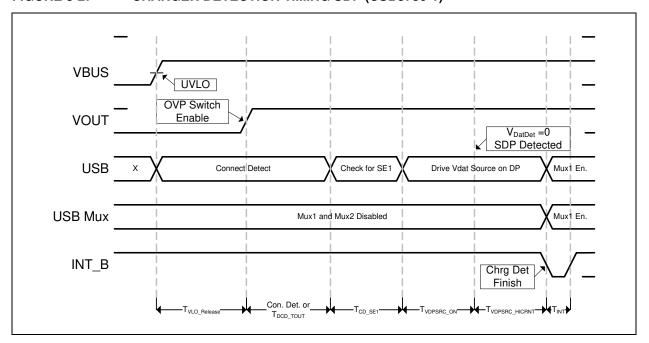

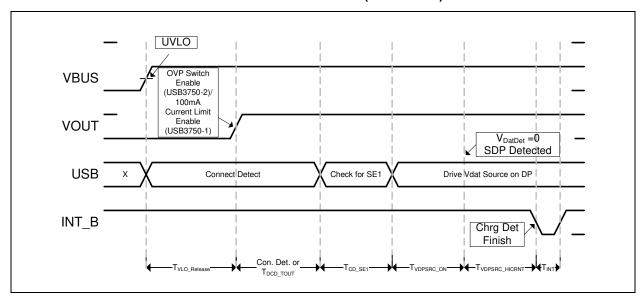

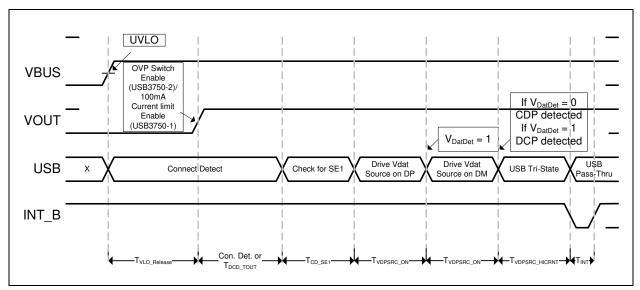

#### 3.3.2 AUTOMATIC CHARGER DETECTION TIMING

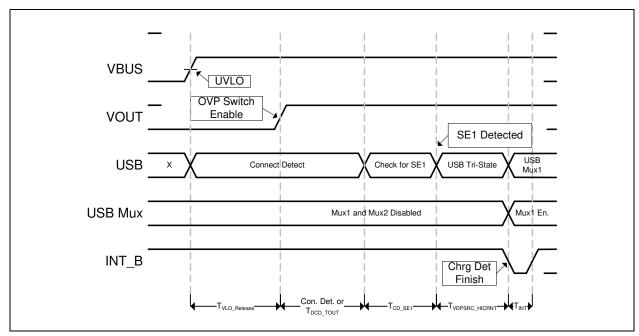

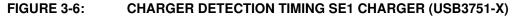

The timing diagrams below illustrate the automatic charger detection timing that is followed when implementing the automatic charger detection flow charts shown in this section.

FIGURE 3-2: CHARGER DETECTION TIMING SDP (USB3750-1)

FIGURE 3-3: CHARGER DETECTION TIMING SDP (USB3751-X)

FIGURE 3-4: CHARGER DETECTION TIMING DCP OR CDP (USB3751-X)

FIGURE 3-5: CHARGER DETECTION TIMING SE1 CHARGER (USB3750-1)

#### 4.0 GENERAL OPERATION

The USB375x is an integrated USB protection device, battery charger detection device, and High Speed USB mux (USB3750 only). The USB375x is designed to protect a USB product from electrical overstress on the USB connector. The USB375x includes several features designed to improve the reliability and speed the design of products designed with a USB interface.

The USB3750 includes a high bandwidth HS USB mux. The mux allows high speed signals to pass through and still meet HS USB signaling requirements.

The USB375x will protect the system from ESD stress events on **VBUS**, **DP**, and **DM**. The USB375x provides ESD protection to the IEC-61000 ESD specification.

The low resistance VBUS overvoltage protection switch protects the internal circuitry from VBUS over voltage events. When VBUS is outside the safe operating range VBUS switch will automatically open.

The USB375x also includes the capability to detect various USB battery chargers, including those defined in the USB Battery Charging Specification, Revision 1.2.

To support the device dead battery conditions as defined in the USB Battery Charging Specification, Revision 1.2, the USB375x-1 has the ability to drive  $V_{DAT\_SRC}$  on **DP** which allows a device with a dead battery to draw 100mA from a USB host. This will allow a device to charge a dead battery without violating the USB specifications. The USB375x-1 also includes a current limit to prevent the unconfigured current from exceeding 100mA. Note, this feature is not available with the USB375x-2.

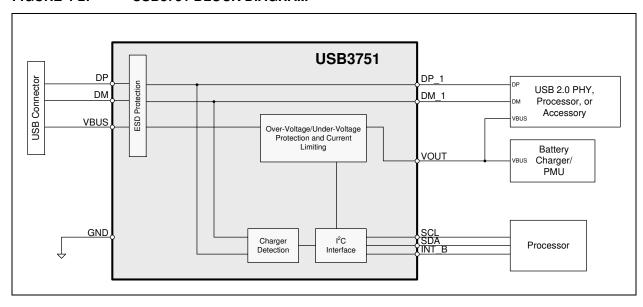

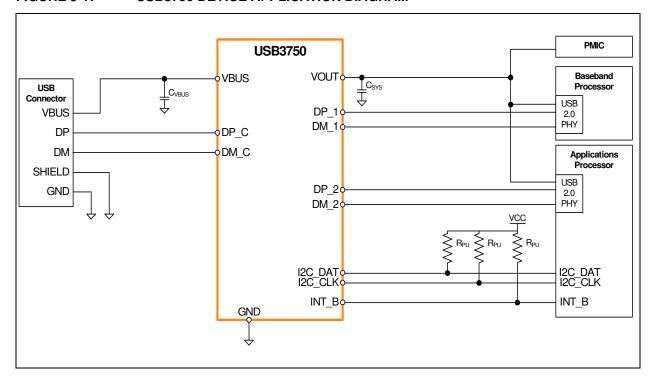

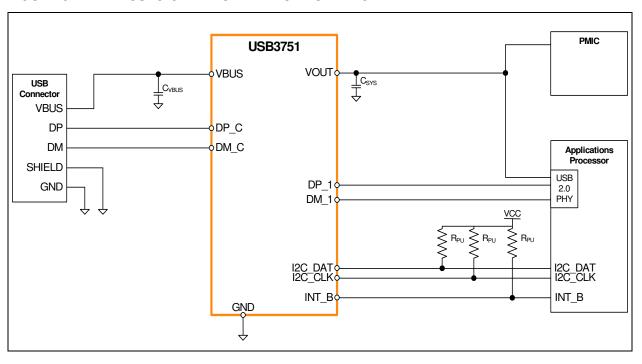

The USB3750 block diagram is shown Figure 4-1 and the USB3751 block diagram is shown Figure 4-2.

FIGURE 4-1: USB3750 BLOCK DIAGRAM

#### FIGURE 4-2: USB3751 BLOCK DIAGRAM

#### 4.1 VBUS Protection Switch

The USB375x protects the entire system from errant VBUS voltages, whether over-voltage or under-voltage conditions. The device is able to dynamically monitor the VBUS voltage levels and take appropriate action by opening the integrated VBUS Protection Switch when these errant conditions occur. Specifically, when VBUS is below the Under Voltage Lock-Out (UVLO) level or above the Over Voltage Lock-Out (OVLO) level, the VBUS switch will open thereby disconnecting the VBUS pin from VOUT. See Section 3.3 for UVLO and OVLO timing diagrams. Manual control of the VBUS Switch, as well as switch configuration can be handled through the I<sup>2</sup>C interface. See Section 4.4.2 for I<sup>2</sup>C register descriptions.

#### 4.1.1 100MA CURRENT LIMIT (USB375X-1 ONLY)

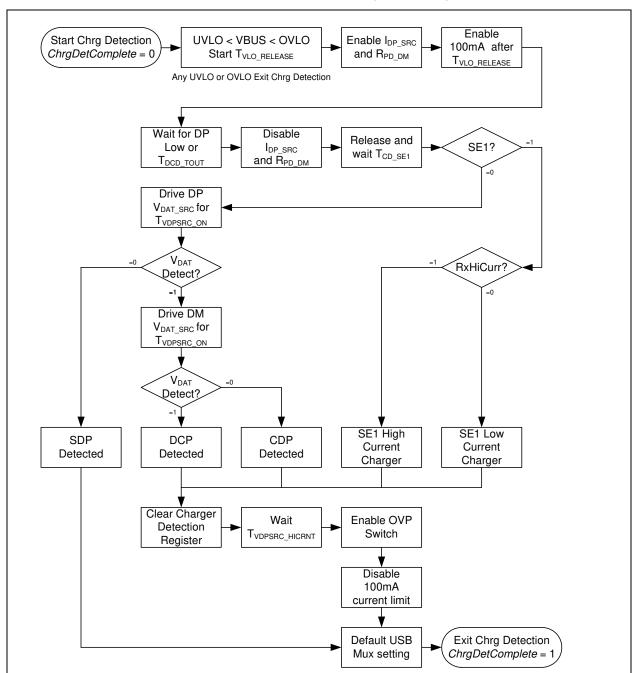

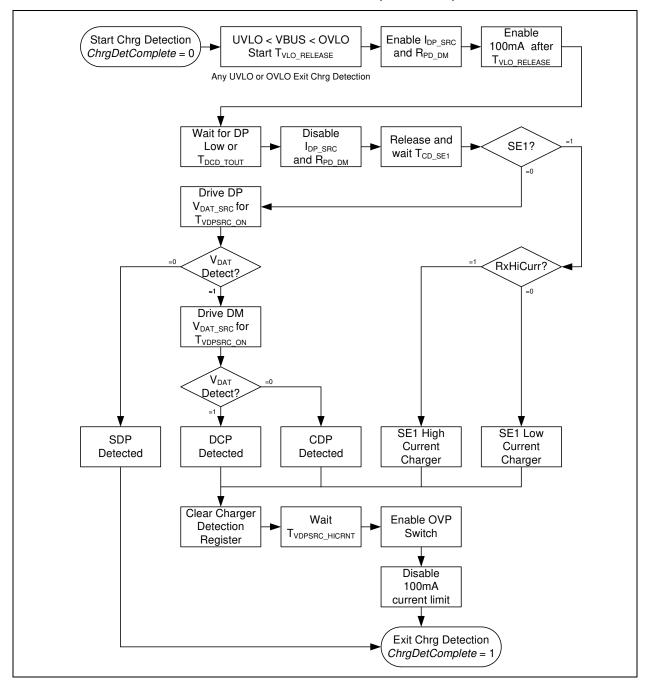

bit The USB375x-1 provides a 100mA current limit feature which allows a portable system with a dead battery to still draw 100mA from a compliant host. When plugged into a Standard Downstream Port (SDP), the USB375x-1 will enable the 100mA current limit until the system controller enables the OVP switch in the I<sup>2</sup>C registers of the USB375x-1. When plugged into any other charger, the USB375x-1 will enable the 100mA current limit during charger detection, and will disable the 100mA current limit once charger detection has completed. Figure 4-6 details the charger detection flow of the USB375x-1.

#### 4.2 Charger Detection

The USB375x includes the circuitry required to implement the USF-IF Battery Charging Specification (revision 1.2). The USB375x will automatically perform a charger detection upon start-up. The USB375x includes a state machine to provide the detection of a wide variety of USB charger detection methods listed in Table 4-1. When any of the USB chargers are plugged into the system, the USB375x will detect a charger plug in event, determine what type of charger it is, and write the type of charger information into the I<sup>2</sup>C register as shown in the following table. In addition, there are two methods to alert the system that a charger has been detected by the USB375x. The first was through the I<sup>2</sup>C register as mentioned above. The second is through the INT\_B pin. When a compliant charger is plugged in and detected, the USB375x will automatically drive the INT\_B signal low. Figure 4-4 details the automatic charger detection flow of the USB3751-1, and Figure 4-6 details the automatic charger detection flow of the USB3751-2.

TABLE 4-1: VALID CHARGERS

| USB Charger Type                                                              | DP/DM<br>Profile                               | I <sup>2</sup> C Reg 0<br>Bits[7:5]<br>( <i>ChargerType)</i> |

|-------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------|

| DCP (Dedicated Charging Port, defined in Battery Charging 1.2 specification)  | Shorted < 200ohm                               | 001                                                          |

| CDP (Charging Downstream Port, defined in Battery Charging 1.2 specification) | V <sub>DP</sub> reflected to V <sub>DM</sub>   | 010<br>(EnhancedChrgDet = 1)                                 |

| SDP<br>(Standard Downstream Port)<br>USB Host or downstream hub port          | 15Kohm<br>pull-down on <b>DP</b> and <b>DM</b> | 011                                                          |

| SE1 Charger Low Current Charger                                               | DP = 2.0V<br>DM = 2.0V                         | 100<br>(SE1ChrgDet =1)                                       |

| SE1 Charger High Current Charger                                              | DP = 2.0V<br>DM = 2.7V                         | 101<br>(SE1ChrgDet =1)                                       |

#### 4.2.1 CHARGER DETECTION CIRCUITRY

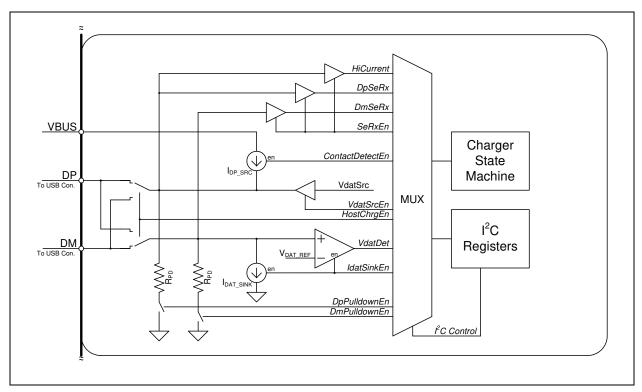

The charger detection circuitry shown Figure 4-3 is used to detect the type charger attached to the USB connector.

FIGURE 4-3: USB CHARGER DETECTION BLOCK DIAGRAM

**Note:** The *italic names* in the Figure 4-3 correspond to bits in the I<sup>2</sup>C register set.

The *VdatDet* output is qualified with the Linestate[1:0] value. If the Linestate is not equal to 00b the *VdatDet* signal will not assert.

For the USB3750, *EnableMux1* or *EnableMux2* should not be set while charger detection operations are performed. During the automatic charger detection *EnableMux1* or *EnableMux2* will be disabled. These will need to be disabled by the I<sup>2</sup>C master if a custom charger detection is performed through I<sup>2</sup>C.

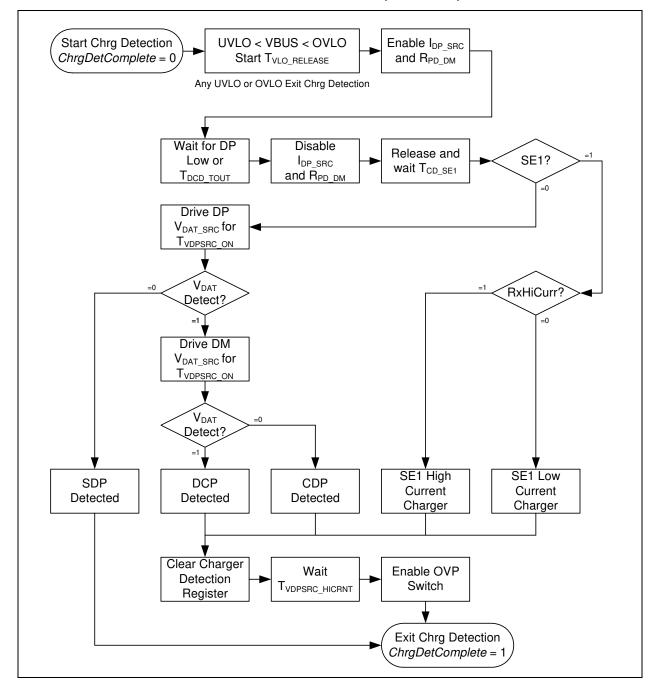

#### 4.2.2 AUTOMATIC CHARGER DETECTION

Automatic charger detection will be begin after VBUS crosses the UVLO threshold, and will follow the flow charts shown below in Figure 4-4 and Figure 4-6. The flow chart timing can be found in Section 3.3.2. When automatic charger detection has completed, the INT\_B signal will go low, and the type of charger that was detected will be reflected in the *ChargerType* bits of I<sup>2</sup>C REG 0 BITS [7:5].

FIGURE 4-4: CHARGER DETECTION FLOW CHART (USB3750-1)

FIGURE 4-5: CHARGER DETECTION FLOW CHART (USB3751-1)

FIGURE 4-6: CHARGER DETECTION FLOW CHART (USB3751-2)

#### 4.3 USB Mux (USB3750 Only)

The USB mux is designed to pass High Speed USB signals to the USB connector, and allows for two USB inputs to be multiplexed into one USB output. Either switch path is enabled through the I<sup>2</sup>C interface, and the switch paths are disabled in the event of UVLO or OVLO.

The USB Mux is designed to pass USB signals from 0 to 3.3V. It is not designed to pass signals that go above 3.3V or below ground.

During power-up and charger detection the USB Mux switches will be disabled regardless of the *EnableMux1* and *EnableMux2* settings.

Once power-up and charger detection are complete EnableMux1 is enabled by default.

#### 4.4 USB375x Registers

All registers are reset when VBUS goes below UVLO. All registers are accessed through the I<sup>2</sup>C interface defined below.

#### 4.4.1 I<sup>2</sup>C INTERFACE

The SDA and SCL pins comprise the  $I^2C$  interface of the USB375x. The  $I^2C$  master controls all traffic to the USB375x. If the USB375x has a change in status it can assert the **INT\_B** by pulling this line to ground. The USB375x **INT\_B** line will stay low and then auto-clear after 1mS or until cleared by reading the Status Register. This prevents **INT\_B** from masking other interrupts if the line is shared with other  $I^2C$  devices.

SCL, SDA, and INT\_B will be tri-stated until VBUS is above the UVLO. VBUS must be present to operate the I<sup>2</sup>C interface.

**SCL** is an input only pad. **SDA** is bi-directional and can be configured as an input or an open drain output during I<sup>2</sup>C operations.

**SDA**, and **INT\_B** are open collector when configured as an output. This requires an external pull-up resistor on **SDA** and **INT\_B**.

The USB375x-1 requires I<sup>2</sup>C communications in order for the default USB path to be enabled. By default, the 100mA current limit is enabled. Only devices that draw <100mA will be enabled through the path as part of dead battery provision support. In order to bypass this limit, bits 0 (EnableOVP Switch) and 2 (OverideVBUS) in Register 1 (Configuration Register) need to be set via I<sup>2</sup>C.

#### 4.4.2 I<sup>2</sup>C REGISTER ACCESS

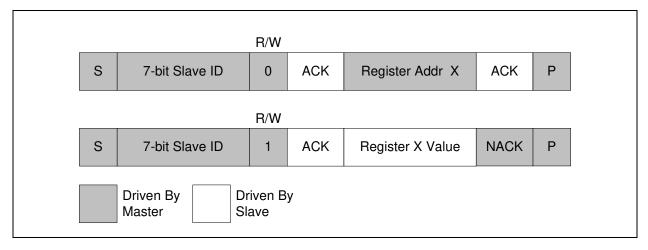

#### 4.4.2.1 I<sup>2</sup>C Read Command

The slave supports two types of reads, single reads, and continuous reads. In a single read the master asserts a NACK after the first read data. The format for a single read is shown in Figure 4-7. The read command has three phases. These three phases are device address phase, register address phase, and read data phase. Each phase is terminated by an ACK or NACK. The device address phase consists of the 7-bit slave address followed by a '1' to indicate a read. If the address matches the slave's address then the slave drives an ACK. The register address phase consists of an 8-bit register address. The slave will always ACK the register address. In the data phase the slave will return the register read data. If the register address was a valid register than the slave will return the data, otherwise it will return 0xFF.

#### FIGURE 4-7: I<sup>2</sup>C SINGLE READ

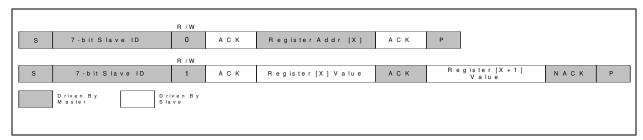

The continuous read command is similar to the single read command, however after the read data the master will drive an ACK and then provide another register address. The master will then wait for the read data as shown in Figure 4-8. The continuous read is terminated by the master by driving a NACK after the last read data and then asserting a STOP condition.

FIGURE 4-8: I<sup>2</sup>C CONTINUOUS READ

|   |                                  | R/W |     |                    |     |                         |      |   |

|---|----------------------------------|-----|-----|--------------------|-----|-------------------------|------|---|

| S | 7-bit Slave ID                   | 0   | ACK | Register Addr [X]  | ACK | Р                       |      |   |

|   |                                  | R/W |     |                    |     |                         |      |   |

| S | 7-bit Slave ID                   | 1   | ACK | Register [X] Value | ACK | Register [X+1]<br>Value | NACK | Р |

|   | Driven By Master Driven By Slave |     |     |                    |     |                         |      |   |

#### 4.4.2.2 I<sup>2</sup>C Write Command

Similar to the read commands, the slave supports two types of write commands. The single write command is show in Figure 4-9. The slave will always ACK the write data. Only the lower 4 bits of the register address are decoded. Writes to undefined and read-only registers will be ignored.

FIGURE 4-9: I<sup>2</sup>C SINGLE WRITE

|   |                | R/W           |     |                 |     |                    |     |   |

|---|----------------|---------------|-----|-----------------|-----|--------------------|-----|---|

| S | 7-bit Slave ID | 0             | ACK | Register X Addr | ACK | Register [X] Value | ACK | Р |

|   |                | iven B<br>ave | у   |                 |     |                    |     |   |

The continuous write is shown in Figure 4-10. In this case after the ACK of the write data, the master will drive the next register address. The continuous write will be terminated when the master asserts a STOP.

FIGURE 4-10: I<sup>2</sup>C CONTINUOUS WRITE

### 4.4.3 I<sup>2</sup>C ADDRESS

The default  $I^2C$  address is 1101000. The two LSB are set by the OTP registers.

TABLE 4-2: I<sup>2</sup>C ADDRESS

| MSB |   |   |   |   |   |   | LSB |

|-----|---|---|---|---|---|---|-----|

| 1   | 1 | 0 | 1 | 0 | 0 | 0 | R/W |

#### 4.4.4 REG 0: STATUS REGISTER

This register indicates the current status of the USB375x.

| Field Name         | Bit | Access | Default | Description                                                                                                                                                                                                                                                                                                                                 |

|--------------------|-----|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OVLO Status        | 0   | rd     | 0       | Over Voltage Lockout Comparator Status. Set to 0b when VBUS goes above the OVLO threshold.                                                                                                                                                                                                                                                  |

| OVLO Latch         | 1   | rd     | 0       | Set to 1b when an unmasked OVLO interrupt occurs on OVLO Status. Auto cleared when this register is read.                                                                                                                                                                                                                                   |

| OVP SwitchStatus   | 2   | rd     | 0       | Indicates the status of the OVP switch. A 0b indicates the OVP switch is closed. A 1b indicates that the OVP switch is open.                                                                                                                                                                                                                |

| CurrentLimitStatus | 3   | rd     | 0       | Indicates the status of the 100mA Current Limit. A 1b indicates that the current limit is enabled.                                                                                                                                                                                                                                          |

| ChrgDetComplete    | 4   | rd     | 0       | A 1b Indicates Charger Detection has completed.                                                                                                                                                                                                                                                                                             |

| ChargerType        | 7:5 | rd     | 000     | This register indicates the result of the automatic charger detection.  000 = ChargerDetection is not complete  001 = DCP  010 = CDP  011 = SDP  100 = SE1 Low Current Charger  101 = SE1 High Current Charger  If EnhancedChrgDet = 0 the USB375x is unable to distinguish between a DCP and a CDP and will return DCP as the ChargerType. |

#### 4.4.5 REG 1: CONFIGURATION REGISTER

| Field Name           | Bit | Access | Default | Description                                                                                                                                                                                                                                        |

|----------------------|-----|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EnableOVP Switch     | 0   | r/w    | 0       | The OVP switch will be enabled when this bit is set to 1b.                                                                                                                                                                                         |

| EnableCurrentLimit   | 1   | r/w    | 0       | Controls the 100mA current limit block. The 100mA current limit will be enabled when this bit is set to 1b and the OverrideCurrentLimit bit is also set to 1b.                                                                                     |

| OverideVBUS          | 2   | r/w    | 0       | When this bit is set to 1b the OVP switch is controlled by the <i>EnableOVP Switch</i> bit.                                                                                                                                                        |

| OverrideCurrentLimit | 3   | r/w    | 0       | When this bit is set to 1b the current limit is controlled by the <i>EnableCurrentLimit</i> bit.                                                                                                                                                   |

| Reserved             | 4   | r/w    | 0       | Reserved                                                                                                                                                                                                                                           |

| EnableMux1           | 5   | r/w    | 1       | When this bit is set to 1b the Mux 1 path is enabled (USB3750 Only)                                                                                                                                                                                |

| EnableMux2           | 6   | r/w    | 0       | When this bit is set to 1b the Mux 2 path is enabled (USB3750 Only)                                                                                                                                                                                |

| SoftPOR              | 7   | r/w    | 0       | Hardware reset. When this bit is set to 1b, the USB375x will reset and restart the POR sequence. This bit will autoclear in T <sub>SOFT_POR</sub> . The USB375x registers should not be accessed until the T <sub>SOFT_POR</sub> time has expired. |

#### 4.4.6 REG 2: BATTERY CHARGER REGISTER

These bits allow  $I^2C$  control of the battery charger circuits. This will allow for custom defined charger detection algorithm to be implemented. By default the  $I^2C$  control bit is off and this register is under control of the charger detection state machine. Once the charger detection state machine is complete the  $I^2C$  master can set the  $I^2C$  control register to control the charger detection circuits.

| Field Name               | Bit | Access | Default | Description                                                                                                                                                                                                                                      |

|--------------------------|-----|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SeRxEn                   | 0   | r/w    | 0       | Single Ended Receiver Enable. Wen this bit is set to 1b the single ended receivers will be enabled                                                                                                                                               |

| ContactDetectEn          | 1   | r/w    | 0       | Contact Detect Current Source Enable. When this bit is set to 1b the IDP_SRC current source shown in Figure 4-3 will be enabled.                                                                                                                 |

| VdatSrcEn                | 2   | r/w    | 0       | Vdat voltage source enable. When this bit is set to 1b the VdatSrc voltage source shown in Figure 4-3 will be enabled.                                                                                                                           |

| HostChrgEn               | 3   | r/w    | 0       | When this bit is set to 1b, the charger detection connections of DP and DM are swapped. The USB signal path is not reversed. This is required when differentiating between a Charging Downstream Port (CDP) and a Dedicated Charging Port (DCP). |

| IdatSinkEn               | 4   | r/w    | 0       | Idat current sink enable. When this bit is set to 1b the IdatSinkEn current source shown in Figure 4-3 will be enabled.                                                                                                                          |

| DpPulldownEn             | 5   | r/w    | 0       | DP 15K pull down resistor enable. When this bit is set to 1b the RPD 15K pull down resistor on DP shown in Figure 4-3 will be enabled.                                                                                                           |

| DmPulldownEn             | 6   | r/w    | 0       | DM 15K pull down resistor enable. When this bit is set to 1b the RPD 15K pull down resistor on DM shown in Figure 4-3 will be enabled.                                                                                                           |

| I <sup>2</sup> C Control | 7   | r/w    | 0       | When this bit is set to 0b the bits [6:0] are disconnected from the Battery Charger circuits. When this bit is set to 1b, bits [6:0] will control the charger detection circuits.                                                                |

#### 4.4.7 REG 3: BATTERY CHARGER STATUS REGISTER

| Field Name  | Bit | Access | Default | Description                                                                                                            |  |

|-------------|-----|--------|---------|------------------------------------------------------------------------------------------------------------------------|--|

| VdatDet     | 0   | rd     | 0       | Indicates Vdat Det comparator output. A 1b indicates that the VdatDet comparator shown in Figure 4-3 has been tripped. |  |

| DpSeRx      | 1   | rd     | 0       | DP Single Ended Receiver Status. A 1b indicates that the DP signal is above the V <sub>SE_RX</sub> threshold.          |  |

| DmSeRx      | 2   | rd     | 0       | DM Single Ended Receiver Status. A 1b indicates that the DM signal is above the V <sub>SE_RX</sub> threshold.          |  |

| RxHiCurrent | 3   | rd     | 0       | DM high current SE1 charger output. A 1b indicates that the DM signal is above the V <sub>SE_RXH</sub> threshold.      |  |

| Reserved    | 7:4 | r      | 0000    | Read Only.                                                                                                             |  |

#### 5.0 APPLICATION NOTES

### 5.1 Application Diagram

TABLE 5-1: COMPONENT VALUES IN APPLICATION DIAGRAMS

| Reference<br>Designator | Value            | Description                                                                                 | Notes                                                      |

|-------------------------|------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|

| R <sub>PU</sub>         | 10 kΩ            | Pull-up required for I <sup>2</sup> C and INT_B operation.                                  | Pull up to I <sup>2</sup> C and INT_B power domain on SOC. |

| C <sub>VBUS</sub>       | 1μF to 10μF      | Capacitor to ground required by the USB Specification. Microchip recommends $<1\Omega$ ESR. | Place near the USB connector.                              |

| C <sub>SYS</sub>        | System dependent | System bulk capacitance                                                                     | Optional. Not required for USB375x operation.              |

FIGURE 5-1: USB3750 DEVICE APPLICATION DIAGRAM

#### FIGURE 5-2: USB3751 DEVICE APPLICATION DIAGRAM

#### 5.2 ESD Performance

The USB375x is protected from ESD strikes. By eliminating the requirement for external ESD protection devices, board space is conserved, and the board manufacturer is enabled to reduce cost. The advanced ESD structures integrated into the USB375x protect the device whether or not it is powered up.

#### 5.2.1 HUMAN BODY MODEL (HBM) PERFORMANCE

HBM testing verifies the ability to withstand the ESD strikes like those that occur during handling and manufacturing, and is done without power applied to the IC. To pass the test, the device must have no change in operation or performance due to the event. The USB375x HBM performance is detailed in .

#### 5.2.2 EN/IEC 61000-4-2 PERFORMANCE

The EN/IEC 61000-4-2 ESD specification is an international standard that addresses system-level immunity to ESD strikes while the end equipment is operational. In contrast, the HBM ESD tests are performed at the device level with the device powered down.

Microchip contracts with Independent laboratories to test the USB375x to EN/IEC 61000-4-2 in a working system. Reports are available upon request. Please contact your Microchip representative, and request information on 3rd party ESD test results. The reports show that systems designed with the USB375x can safely provide the ESD performance shown in without additional board level protection.

In addition to defining the ESD tests, EN/IEC 61000-4-2 also categorizes the impact to equipment operation when the strike occurs (ESD Result Classification). The USB375x maintains an ESD Result Classification 1 or 2 when subjected to an EN/IEC 61000-4-2 (level 4) ESD strike.

Both air discharge and contact discharge test techniques for applying stress conditions are defined by the EN/IEC 61000-4-2 ESD document.

#### 5.2.2.1 Air Discharge

To perform this test, a charged electrode is moved close to the system being tested until a spark is generated. This test is difficult to reproduce because the discharge is influenced by such factors as humidity, the speed of approach of the electrode, and construction of the test equipment.

#### 5.2.2.2 Contact Discharge

The uncharged electrode first contacts the USB connector to prepare this test, and then the probe tip is energized. This yields more repeatable results, and is the preferred test method. The independent test laboratories contracted by Microchip provide test results for both types of discharge methods.

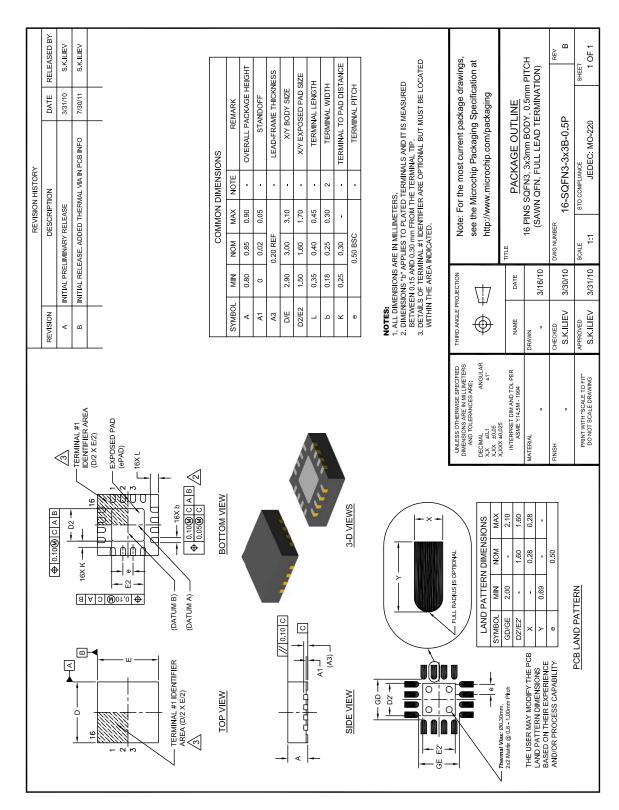

#### 6.0 PACKAGE INFORMATION

FIGURE 6-1: 16-PIN QFN PACKAGE OUTLINE, 3 X 3 MM BODY, 0.5 MM PITCH