Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Enpirion Power Datasheet EY1602 40V, Low Quiescent Current, 50mA Linear Regulator

DS-1046 Datashee:

The Altera® Enpirion® EY1602 is a wide input voltage range, low quiescent current linear regulator ideally suited for "always-on" and "keep alive" applications. The EY1602 operates from an input voltage of +6V to +40V under normal operating conditions, consuming only 18µA of quiescent current at no load.

The EY1602 has an adjustable output voltage range from 1.223V to 12V. It features an EN pin that can be used to put the device into a low-quiescent current shutdown mode where it draws only  $1.8\mu A$  of supply current. The device features automatic thermal shutdown and current limit protection.

The EY1602 is rated over the -40°C to +125°C temperature range and is available in an 8 lead EPSOIC with exposed pad package..

TABLE 1. KEY DIFFERENCES IN FAMILY OF 40V LDO PARTS

| PART NUMBER  | MIN. I <sub>OUT</sub> | ADJ OR FIXED V <sub>out</sub> |

|--------------|-----------------------|-------------------------------|

| EY1602SI-ADJ | 50mA                  | ADJ                           |

| EY1603TI-ADJ | 150mA                 | ADJ                           |

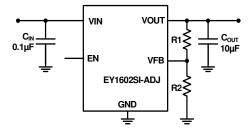

# $\begin{array}{c|c} C_{\text{IN}} & V_{\text{IN}} & P_{\text{AD}} & V_{\text{OUT}} \\ \downarrow & \downarrow & \\ 0.1 \mu\text{F} & & \\ \end{array}$

FIGURE 1. TYPICAL APPLICATION

## **Features**

- Wide V<sub>IN</sub> range of 6V to 40V

- Adjustable output voltage from 1.223V to 12V

- Guaranteed 50mA output current

- Ultra low 18µA typical quiescent current

- Low 1.8µA of typical shutdown current

- ±1% accurate voltage reference

- Low dropout voltage of 120mV at 50mA

- 40V tolerant logic level (TTL/CMOS) enable input

- Stable operation with 10µF output capacitor

- 5kV ESD HBM rated

- Thermal shutdown and current limit protection

## **Applications**

- FPGA applications

- Industrial

- Networking

- Telecom

FIGURE 2. QUIESCENT CURRENT vs LOAD CURRENT (AT UNITY GAIN),  $V_{\rm IN} = 14V$

101 Innovation Drive San Jose, CA 95134 www.altera.com

09618

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Ordering Information**

| PART<br>Number            | PART<br>Marking   | TEMP. RANGE<br>(°C) | ENABLE<br>PIN | OUTPUT VOLTAGE<br>(V) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|---------------------------|-------------------|---------------------|---------------|-----------------------|----------------------|----------------|

| EY1602SI-ADJ<br>(Notes 1) | 1602AS            | -40 to +125         | Yes           | Adjustable            | 8 Ld EPSOIC          | M8.15B         |

| EVB-EY1602SI-ADJ          | Evaluation Platfo | rm                  |               |                       |                      |                |

### **NOTES:**

- 1. Add "-T\*" suffix for tape and reel.

- 2. These Altera Enpirion Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Altera Enpirion Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

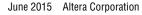

# **Pin Configuration**

## **Pin Descriptions**

| PIN NUMBER | PIN NAME | DESCRIPTION                                                                                                        |

|------------|----------|--------------------------------------------------------------------------------------------------------------------|

| 1          | VIN      | Input voltage pin. A minimum 0.1µF X5R/X7R capacitor is required for proper operation. Range: 6V to 40V            |

| 2, 3, 6    | NC       | Pins have internal termination and can be left not connected. Connection to ground is optional.                    |

| 4          | EN       | High on this pin enables the device. Range: 0V to V <sub>IN</sub>                                                  |

| 5          | GND      | Ground pin.                                                                                                        |

| 7          | VFB      | This pin is connected to the external feedback resistor divider, which sets the LDO output voltage.Range: 0V to 3V |

| 8          | VOUT     | Regulated output voltage. A 10μF X5R/X7R output capacitor is required for stability. Range: 0V to 12V              |

| -          | PAD      | It is recommended to solder the PAD to the ground plane.                                                           |

## **Absolute Maximum Ratings**

| VIN Pin to GND VoltageGND - 0.3V to +45V               |

|--------------------------------------------------------|

| VOUT Pin to GND Voltage                                |

| EN Pin to GND Voltage GND - 0.3V to VIN                |

| VFB Pin to GND Voltage GND - 0.3V to 3V                |

| Output Short-circuit DurationIndefinite                |

| ESD Rating                                             |

| Human Body Model (Tested per JESD22-A114E) 5kV         |

| Machine Model (Tested per JESD-A115-A) 200V            |

| Charge Device Model (Tested per JESD22-C101C) 2.2kV    |

| Latch Up (Tested per JESD78B; Class II, Level A) 100mA |

|                                                        |

## **Thermal Information**

| Thermal Resistance (Typical)    | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|---------------------------------|----------------------|----------------------|

| 8 Ld EPSOIC Package (Notes 3, 4 | 4) 50                | 9                    |

| Maximum Junction Temperature.   |                      | +150°C               |

| Maximum Storage Temperature R   | ange 6               | 65°C to +175°C       |

| Pb-Free Reflow Profile          |                      |                      |

## **Recommended Operating Conditions**

| Ambient Temperature Range . | 40°C to +125°C  |

|-----------------------------|-----------------|

| VIN Pin to GND Voltage      | +6V to +40V     |

| VOUT Pin to GND Voltage     | +1.223V to +12V |

| EN Pin to GND Voltage       | 0V to +40V      |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 3.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features.

- 4. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Recommended Operating Conditions, unless otherwise noted.  $V_{IN} = 14V$ ,  $I_{OUT} = 1mA$ ,  $C_{IN} = 0.1\mu F$ ,  $C_{OUT} = 10\mu F$ ,  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical specifications are at  $T_A = +25^{\circ}C$ . **Boldface limits apply over the operating temperature range, -40^{\circ}C to +125^{\circ}C**.

| PARAMETER                      | SYMBOL                          | TEST CONDITIONS                                                          | MIN<br>(Note 7) | ТҮР   | MAX<br>(Note 7)<br>40 | UNIT<br>V |

|--------------------------------|---------------------------------|--------------------------------------------------------------------------|-----------------|-------|-----------------------|-----------|

| Input Voltage Range            | V <sub>IN</sub>                 |                                                                          | 6               |       |                       |           |

| Guaranteed Output Current      | I <sub>OUT</sub>                | $V_{IN} = V_{OUT} + VDO$                                                 | 50              |       |                       | mA        |

| VFB Reference Voltage          | $V_{REF}$                       | EN = High, V <sub>IN</sub> = 14V, I <sub>OUT</sub> = 0.1mA               | 1.211           | 1.223 | 1.235                 | V         |

| Line Regulation                | $\Delta V_{OUT}/\Delta V_{IN}$  | $3V \le V_{IN} \le 40V$ , $I_{OUT} = 1$ mA                               |                 | 0.04  | 0.115                 | %         |

| Load Regulation                | $\Delta V_{OUT}/\Delta I_{OUT}$ | $V_{IN} = V_{OUT} + V_{D,} I_{OUT} = 100 \mu A \text{ to } 50 \text{mA}$ |                 | 0.25  | 0.5                   | %         |

| Dropout Voltage (Note 5)       | $\Delta V_{D0}$                 | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> = 3.3V                          |                 | 10    | 38                    | mV        |

|                                |                                 | I <sub>OUT</sub> = 50mA, V <sub>OUT</sub> = 3.3V                         |                 | 130   | 340                   | mV        |

|                                |                                 | I <sub>OUT</sub> = 1mA, V <sub>OUT</sub> = 5V                            |                 | 10    | 48                    | mV        |

|                                |                                 | I <sub>OUT</sub> = 50mA, V <sub>OUT</sub> = 5V                           |                 | 120   | 350                   | mV        |

| Shutdown Current               | I <sub>SHDN</sub>               | EN = LOW                                                                 |                 | 1.8   | 3.64                  | μΑ        |

| Quiescent Current              | IQ                              | EN = HIGH, I <sub>OUT</sub> = 0mA                                        |                 | 18    | 24                    | μΑ        |

|                                |                                 | EN = HIGH, I <sub>OUT</sub> = 1mA                                        |                 | 22    | 42                    | μΑ        |

|                                |                                 | EN = HIGH, I <sub>OUT</sub> = 10mA                                       |                 | 34    | 60                    | μA        |

|                                |                                 | EN = HIGH, I <sub>OUT</sub> = 50mA                                       |                 | 56    | 82                    | μΑ        |

| Power Supply Rejection Ratio   | PSRR                            | f = 100Hz; Vin_ripple = 500mV <sub>P-P</sub> ; Load = 50mA               |                 | 58    |                       | dB        |

| EN FUNCTION                    |                                 |                                                                          | '               |       |                       |           |

| EN Threshold Voltage           | V <sub>EN_H</sub>               | V <sub>OUT</sub> = Off to On                                             |                 |       | 1.485                 | V         |

|                                | V <sub>EN_L</sub>               | V <sub>OUT</sub> = On to Off                                             | 0.935           |       |                       | ٧         |

| EN Pin Current                 | I <sub>EN</sub>                 | V <sub>OUT</sub> = 0V                                                    |                 | 0.026 |                       | μΑ        |

| EN to Regulation Time (Note 6) | t <sub>EN</sub>                 |                                                                          |                 | 1.65  | 1.93                  | ms        |

| PROTECTION FEATURES            |                                 |                                                                          |                 | 1     | ı                     |           |

| Output Current Limit           | I <sub>LIMIT</sub>              | V <sub>OUT</sub> = 0V                                                    | 60              | 118   |                       | mA        |

**Electrical Specifications** Recommended Operating Conditions, unless otherwise noted.  $V_{IN} = 14V$ ,  $I_{OUT} = 1mA$ ,  $C_{IN} = 0.1 \mu F$ ,  $C_{OUT} = 10 \mu F$ ,  $C_{AUT} = 10 \mu F$ ,  $C_{AU$

| PARAMETER                   | SYMBOL            | TEST CONDITIONS             | MIN<br>(Note 7) | TYP  | MAX<br>(Note 7) | UNIT |

|-----------------------------|-------------------|-----------------------------|-----------------|------|-----------------|------|

| Thermal Shutdown            | T <sub>SHDN</sub> | Junction Temperature Rising |                 | +165 |                 | °C   |

| Thermal Shutdown Hysteresis | T <sub>HYST</sub> |                             |                 | +20  |                 | °C   |

### NOTES:

- 5. Dropout voltage is defined as  $(V_{IN}$   $V_{OUT})$  when  $V_{OUT}$  is 2% below the value of  $V_{OUT}$  when  $V_{IN}$  =  $V_{OUT}$  + 3V.

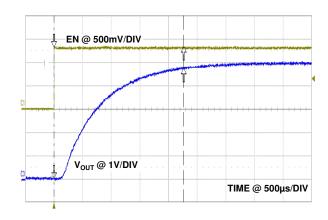

- 6. Enable to Regulation is the time the output takes to reach 95% of its final value with  $V_{IN}$  = 14V and EN is taken from  $V_{IL}$  to  $V_{IH}$  in 5ns. The output voltage is set at 5V.

- 7. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

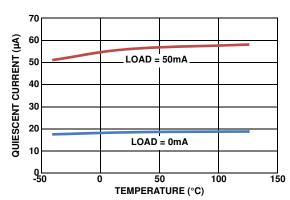

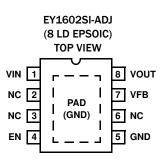

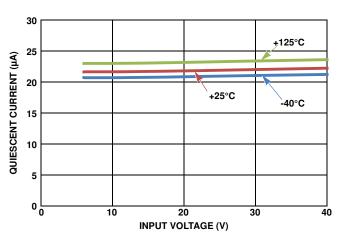

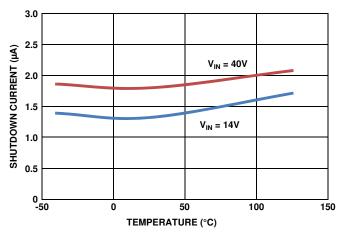

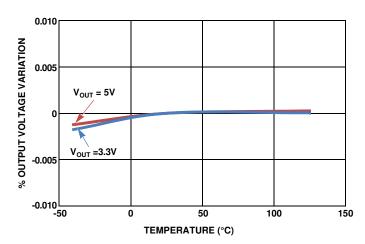

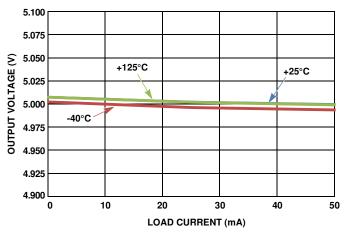

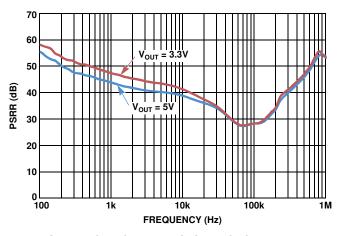

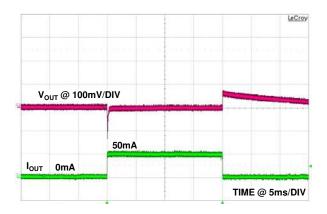

# **Typical Performance Curves** $V_{IN} = 14V$ , $I_{OUT} = 1mA$ , $V_{OUT} = 5V$ , $T_J = +25$ °C unless otherwise specified.

FIGURE 3. QUIESCENT CURRENT vs LOAD CURRENT

FIGURE 4. QUIESCENT CURRENT VS INPUT VOLTAGE (NO LOAD)

FIGURE 5. SHUTDOWN CURRENT VS TEMPERATURE (EN = 0)

FIGURE 6. OUTPUT VOLTAGE vs TEMPERATURE (LOAD = 50mA)

# **Typical Performance Curves** $V_{IN} = 14V$ , $I_{OUT} = 1$ mA, $V_{OUT} = 5V$ , $T_J = +25$ °C unless otherwise specified. (Continued)

FIGURE 7. OUTPUT VOLTAGE VS LOAD CURRENT

FIGURE 8. START-UP WAVEFORM

FIGURE 9. POWER SUPPLY REJECTION RATIO (LOAD = 50mA)

FIGURE 10. LOAD TRANSIENT RESPONSE

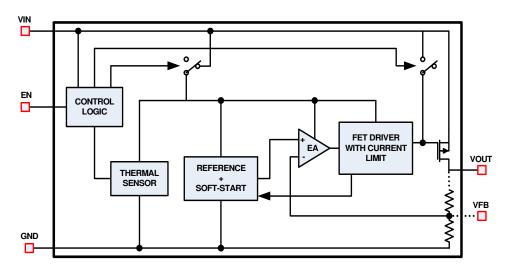

# **Block Diagram**

# **Functional Description**

## **Functional Overview**

The EY1602 is a high performance, high voltage, low-dropout regulator (LDO) with 50mA sourcing capability. The part is rated to operate over the  $-40^{\circ}C$  to  $+125^{\circ}C$  temperature range. Featuring ultra-low quiescent current, it makes an ideal choice for "always-on" applications. It works well under a "load dump condition" where the input voltage could rise up to 40V. The device also features current limit and thermal shutdown protection.

## **Enable Control**

The EY1602 features an Enable pin. When it is pulled low, the IC goes into shutdown mode. In this condition, the device draws less than  $2\mu A$ . Driving the pin high turns the device on. For always on operation, the EN pin can be tied directly to VIN.

## **Current Limit Protection**

The EY1602 has internal current limit functionality to protect the regulator during fault conditions. During current limit, the output sources a fixed amount of current largely independent of the output voltage. If the short or overload is removed from VOUT, the output returns to normal voltage regulation mode.

## **Thermal Fault Protection**

In the event that the die temperature exceeds typically +165°C, the output of the LDO will shut down until the die temperature cools down to typically +145°C. The level of power dissipated, combined with the ambient temperature and the thermal impedance of the package, will determine if the junction temperature exceeds the thermal shutdown temperature. Also see the section on "Power Dissipation".

## **Application Information**

## **Input and Output Capacitors**

For the output, a ceramic capacitor (X5R or X7R) with a capacitance of  $10\mu F$  is recommended for the EY1602 to maintain stability. The ground connection of the output capacitor should be routed directly to the GND pin of the device and also placed close to the IC. A minimum of  $0.1\mu F$  (X5R or X7R) is recommended at the input.

## **Output Voltage Setting**

The output voltage is programmed using an external resistor divider, as shown in Figure 11.

FIGURE 11. SETTING OUTPUT VOLTAGE

The output voltage is calculated using Equation 1:

$$V_{OUT} = 1.223 V \times \left(\frac{R1}{R2} + 1\right)$$

(EQ. 1)

## **Power Dissipation**

The junction temperature must not exceed the range specified in "Recommended Operating Conditions" on page 3. The power dissipation can be calculated using Equation 2:

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_{GND}$$

(EQ. 2)

The maximum allowable junction temperature,  $T_{J(MAX)}$  and the maximum expected ambient temperature,  $T_{A(MAX)}$  will determine the maximum allowable junction temperature rise ( $\Delta T_1$ ), as shown in Equation 3:

$$\Delta T_{J} = T_{J(MAX)} - T_{A(MAX)}$$

(EQ. 3)

To calculate the maximum ambient operating temperature, use the junction-to-ambient thermal resistance ( $\theta_{JA}$ ), as shown in Equation 4:

$$T_{J(MAX)} = P_{D(MAX)} \times \theta_{JA} + T_{A}$$

(EQ. 4)

## **Board Layout Recommendations**

A good PCB layout is important to achieve expected performance. Consideration should be taken when placing the components and routing the trace to minimize the ground impedance, and keep the parasitic inductance low. The input and output capacitors should have a good ground connection and be placed as close to the IC as possible. The VFB feedback trace should be away from other noisy traces. Connect the exposed pad to the ground plane for better heat dissipation. Thermal vias on the PAD increases heat dissipation.

## **Document Revision History**

The table lists the revision history for this document.

| Date          | Version | Changes                           |  |  |

|---------------|---------|-----------------------------------|--|--|

| June 2015     | 1.1     | Updated the output voltage range. |  |  |

| February 2014 | 1.0     | Initial release.                  |  |  |

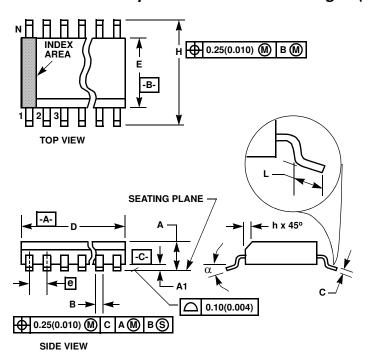

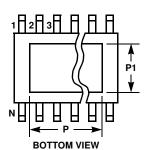

## Small Outline Exposed Pad Plastic Packages (EPSOIC)

M8.15B 8 LEAD NARROW BODY SMALL OUTLINE EXPOSED PAD PLASTIC PACKAGE

|        | INCHES |        | MILLIN   |       |       |

|--------|--------|--------|----------|-------|-------|

| SYMBOL | MIN    | MAX    | MIN      | MAX   | NOTES |

| Α      | 0.056  | 0.066  | 1.43     | 1.68  | -     |

| A1     | 0.001  | 0.005  | 0.03     | 0.13  | -     |

| В      | 0.0138 | 0.0192 | 0.35     | 0.49  | 9     |

| С      | 0.0075 | 0.0098 | 0.19     | 0.25  | -     |

| D      | 0.189  | 0.196  | 4.80     | 4.98  | 3     |

| E      | 0.150  | 0.157  | 3.81     | 3.99  | 4     |

| е      | 0.050  | BSC    | 1.27 BSC |       | -     |

| Н      | 0.230  | 0.244  | 5.84     | 6.20  | -     |

| h      | 0.010  | 0.016  | 0.25     | 0.41  | 5     |

| L      | 0.016  | 0.035  | 0.41     | 0.89  | 6     |

| N      | 8      |        |          | 8     | 7     |

| α      | 0°     | 8°     | 0°       | 8°    | -     |

| Р      | -      | 0.094  | -        | 2.387 | 11    |

| P1     | -      | 0.094  | -        | 2.387 | 11    |

Rev. 5 8/10

### NOTES:

June 26, 2015

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual

- index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: INCH. Converted millimeter dimensions are not necessarily exact.

- Dimensions "P" and "P1" are thermal and/or electrical enhanced variations. Values shown are maximum size of exposed pad within lead count and body size.