Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### eZ80F91 Development Kit

**User Manual**

**PRELIMINARY**

UM014205-0203

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

#### **ZiLOG Worldwide Headquarters**

532 Race Street San Jose, CA 95126 Telephone: 408.558.8500

Fax: 408.558.8300 www.zilog.com

#### Document Disclaimer

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

©2003 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

## Safeguards

The following precautions must be observed when working with the devices described in this document.

**Caution:** Always use a grounding strap to prevent damage resulting from electrostatic discharge (ESD).

## Table of Contents

| Safeguardsiii                          |

|----------------------------------------|

| List of Figures vii                    |

| List of Tables ix                      |

| Introduction                           |

| Kit Features                           |

| Hardware Specifications                |

| eZ80F91 Development Kit Overview       |

| eZ80 <sup>®</sup> Development Platform |

| Functional Description                 |

| Physical Dimensions 9                  |

| Operational Description                |

| eZ80F91 Module Interface               |

| Application Module Interface           |

| I/O Functionality                      |

| Embedded Modem Socket Interface        |

| eZ80® Development Platform Memory      |

| LEDs                                   |

| Push Buttons                           |

| Jumpers                                |

| Connectors                             |

| Console                                |

| Modem 40                               |

| I <sup>2</sup> C Devices               |

| eZ80F91 Module                         |

| Functional Description                 |

| Fast Buffer                            |

| Physical Dimensions                    |

| Operational Description                |

| eZ80F91 Module Memory                  | 48 |

|----------------------------------------|----|

| Reset Generator                        | 49 |

| IrDA Transceiver                       | 49 |

| Flash Loader Utility                   | 51 |

| Mounting the Module                    | 51 |

| Changing the Power Supply Plug         | 52 |

| ZPAKII                                 | 54 |

| ZDI Target Interface Module            | 54 |

| JTAG                                   | 54 |

| Application Modules                    | 54 |

| ZDS II                                 | 55 |

| Troubleshooting                        | 57 |

| Overview                               |    |

| Cannot Download Code                   | 57 |

| IrDA Port Not Working                  | 57 |

| Contacting ZiLOG Customer Support      | 57 |

| Schematic Diagrams                     | 59 |

| eZ80 <sup>®</sup> Development Platform | 59 |

| eZ80F92 Module                         | 64 |

| Appendix A                             | 67 |

| General Array Logic Equations          | 67 |

| U10 Address Decoder                    | 67 |

| U15 Address Decoder                    | 70 |

| Customer Feedback Form                 | 75 |

#### vii

## List of Figures

| Figure 1.  | eZ80 <sup>®</sup> Development Platform Block Diagram with eZ80F91 Module |

|------------|--------------------------------------------------------------------------|

| Figure 2.  | The eZ80® Development Platform                                           |

| C          |                                                                          |

| Figure 3.  | The eZ80F91 Module 6                                                     |

| Figure 4.  | Basic eZ80 <sup>®</sup> Development Platform Block Diagram 8             |

| Figure 5.  | Physical Dimensions of the eZ80 <sup>®</sup> Development Platform 9      |

| Figure 6.  | eZ80 <sup>®</sup> Development Platform Peripheral Bus Connector          |

|            | Pin Configuration—JP1                                                    |

| Figure 7.  | eZ80® Development Platform I/O Connector Pin                             |

|            | Configuration—JP2                                                        |

| Figure 8.  | Trigger Pins J21 and J22                                                 |

| Figure 9.  | Embedded Modem Socket Interface—J1, J5, and J9 27                        |

| Figure 10. | Memory Map of the eZ80 <sup>®</sup> Development Platform and             |

|            | eZ80F91 Module                                                           |

| Figure 11. | Possible Bus Contention without Fast Buffer 43                           |

| Figure 12. | Physical Dimensions of the eZ80F91 Module 45                             |

| Figure 13. | eZ80F91 Module—Top Layer                                                 |

| Figure 14. | eZ80F91 Module—Bottom Layer 47                                           |

| Figure 15. | IrDA Hardware Connections 50                                             |

| Figure 16. | 9VDC Universal Power Supply Components 52                                |

| Figure 17. | Inserting a New Plug Configuration 53                                    |

| Figure 18. | eZ80 <sup>®</sup> Development Platform Schematic Diagram,                |

|            | #1 of 5 59                                                               |

| Figure 19. | eZ80® Development Platform Schematic Diagram,                            |

|            | #2 of 5                                                                  |

| Figure 20. | eZ80® Development Platform Schematic Diagram,                            |

| -          | #3 of 5                                                                  |

| Figure 21. | eZ80® Development Platform Schematic Diagram,      |    |

|------------|----------------------------------------------------|----|

|            | #4 of 5                                            | 62 |

| Figure 22. | eZ80® Development Platform Schematic Diagram,      |    |

|            | #5 of 5—RS-485 Cable                               | 63 |

| Figure 23. | eZ80F92 Module Schematic Diagram, #1 of 3—Connecto | rs |

|            | and Miscellaneous                                  | 64 |

| Figure 24. | eZ80F92 Module Schematic Diagram, #2 of 3—CPU and  |    |

|            | PHY                                                | 65 |

| Figure 25. | eZ80F92 Module Schematic Diagram, #3 of 3—Module   |    |

|            | Memory                                             | 66 |

#### iv

## List of Tables

| Table 1.  | eZ80 <sup>®</sup> Development Platform Hardware Specifications 2 |

|-----------|------------------------------------------------------------------|

| Table 2.  | eZ80 <sup>®</sup> Development Platform Peripheral Bus Connector  |

|           | Identification—JP11,3                                            |

| Table 3.  | eZ80 <sup>®</sup> Development Platform I/O Connector             |

|           | Identification—JP21                                              |

| Table 4.  | GPIO Connector J6                                                |

| Table 5.  | CPU Bus Connector J8                                             |

| Table 6.  | LED and Port Emulation Addresses                                 |

| Table 7.  | LED Anode/GPIO Output Control Register 24                        |

| Table 8.  | GPIO Data Register                                               |

| Table 9.  | Connector J5                                                     |

| Table 10. | Connector J9                                                     |

| Table 11. | Connector J1                                                     |

| Table 12. | Bit Access to the LED Cathode, Modem, and Triggers 33            |

| Table 13. | J2—DIS_IrDA                                                      |

| Table 14. | J3—DIS_EM                                                        |

| Table 15. | J7—FlashWE (Off-Chip)                                            |

| Table 16. | J11—DIS_Flash (Off-Chip)                                         |

| Table 17. | J12—5VDC/3.3VDC for an Embedded Modem 37                         |

| Table 18. | J14—RI 37                                                        |

| Table 19. | J15—RS485_1_EN                                                   |

| Table 20. | J16—RS485_2_EN                                                   |

| Table 21. | J17—RT_1                                                         |

| Table 22. | J18—RT_2 39                                                      |

| Table 23. | I <sup>2</sup> C Addresses                                       |

### Introduction

The eZ80F91 Development Kit provides a general-purpose platform for evaluating the capabilities and operation of ZiLOG's eZ80F91 microcontroller. The eZ80F91 is a member of ZiLOG's eZ80Acclaim! product family, which offers on-chip Flash capability. The eZ80F91 Development Kit features two primary boards: the eZ80® Development Platform and the eZ80F91 Module. This arrangement provides a full development platform when using both boards. It can also provide a smaller-sized reference platform with the eZ80F91 Module as a stand-alone development tool.

### **Kit Features**

The key features of the eZ80F91 Development Kit are:

- eZ80<sup>®</sup> Development Platform:

- Up to 2MB fast SRAM (12ns access time; 1MB factory-installed, with 512KB on module, 512KB on platform)

- Embedded modem socket with a U.S. telephone line interface

- I<sup>2</sup>C EEPROM

- I<sup>2</sup>C configuration register

- GPIO, logic circuit, and memory headers

- Supported by ZiLOG Developer Studio II and the eZ80<sup>®</sup> C-Compiler

- LEDs, including a 7x5 LED matrix

- Platform configuration jumpers

- Two RS232 connectors—console, modem

- RS485 connector with cable assembly

- ZiLOG Debug Interface (ZDI)

- JTAG Debug Interface

- 9VDC power connector

- Telephone jack

- eZ80F91 Module:

- eZ80F91 device operating at 50MHz, with 256KB of internal Flash memory and 8KB of internal SRAM memory

- 512KB of off-chip SRAM memory

- 1 MB of off-chip Flash memory (footprint)

- On-chip Ethernet Media Access Controller (EMAC)

- Ethernet port

- IrDA port

- Real-Time Clock with battery backup

- Two headers compatible with the eZ80<sup>®</sup> Development Platform

- ZPAKII Debug Tool

- eZ80<sup>®</sup> Software and Documentation CD-ROM

### **Hardware Specifications**

Table 1 lists the specifications of the eZ80<sup>®</sup> Development Platform.

## Table 1. eZ80<sup>®</sup> Development Platform Hardware Specifications

| Operating Temperature: | 20°C ±5°C |

|------------------------|-----------|

| Operating Voltage:     | 9 VDC     |

### eZ80F91 Development Kit Overview

The purpose of the eZ80F91 Development Kit is to provide the developer with a set of tools for evaluating the features of the eZ80F91 microcontroller and to be able to develop a new application before building application hardware.

The eZ80 $^{\$}$  Development Platform is designed to accept a number of application-specific modules and eZ80 $^{\$}$ -based add-on modules, including the eZ80F91 Module featured in this kit.

The eZ80 $^{\otimes}$  Development Platform, together with its plugged-in eZ80F91 Module, can operate in stand-alone mode with Flash memory, or interface via the ZPAKII Debug Tool to a host PC running ZiLOG Developer Studio II Integrated Development Environment (ZDS IDE) software.

The address bus, data bus, and all eZ80F91 Module control signals are buffered on the eZ80<sup>®</sup> Development Platform to provide sufficient drive capability.

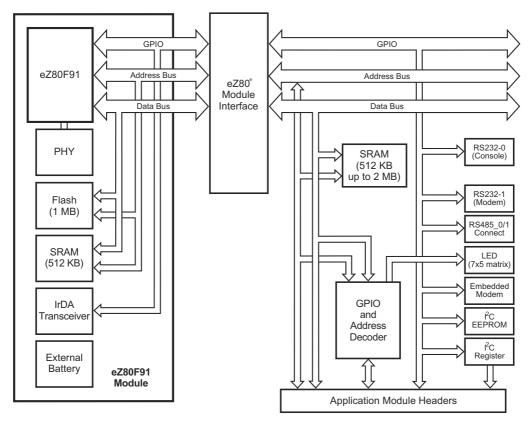

A block diagram of the eZ80 $^{\odot}$  Development Platform and the eZ80F91 Module is shown in Figure 1.

Figure 1. eZ80<sup>®</sup> Development Platform Block Diagram with eZ80F91 Module

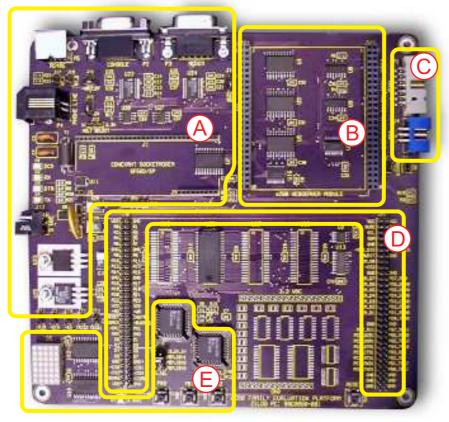

Figure 2 is a photographic representation of the eZ80® Development Platform segmented into its key blocks, as shown in the legend for the figure.

Note: Key to blocks A-E.

- A. Power and serial communications.

- B. eZ80F91 Module interface.

- C. JTAG and ZDI debug interfaces.

- D. Application module interfaces.

- E. GPIO and LED with Address Decoder.

Figure 2. The eZ80<sup>®</sup> Development Platform

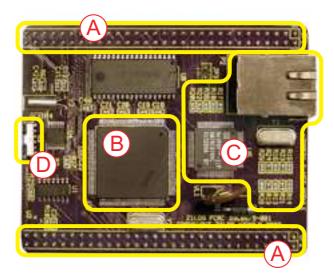

Figure 3 is a photographic representation of the eZ80F91 Module segmented into its key blocks, as shown in the legend for the figure.

Note: Key to blocks A–C.

- A. eZ80F91 Module interfaces.

- B. eZ80F91 CPU.

- C. 10/100 BaseT Ethernet Interface

- D. IrDA transceiver.

Figure 3. The eZ80F91 Module

The structures of the eZ80<sup>®</sup> Development Platform and the eZ80F91 Module are illustrated in the <u>Schematic Diagrams</u> starting on page 59.

## eZ80® Development Platform

This section describes the eZ80 $^{\otimes}$  Development Platform hardware, its key components and its interfaces, including programming information such as memory maps and register definitions.

### **Functional Description**

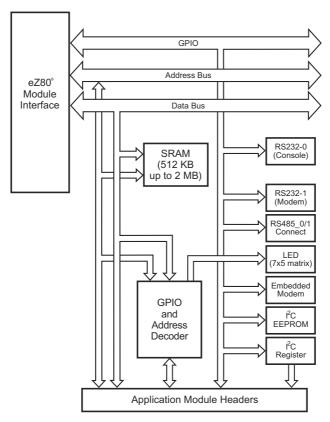

The eZ80<sup>®</sup> Development Platform consists of seven major hardware blocks. These blocks, listed below, are diagrammed in Figure 4.

- eZ80F91 Module interface (2 female headers)

- Power supply for the eZ80® Development Platform, the eZ80F91 Module, and application modules

- Application Module interface (2 male headers)

- GPIO and LED matrix

- Two RS232 serial communications ports

- Two RS485 ports

- Embedded modem interface

- I<sup>2</sup>C devices

Figure 4. Basic eZ80<sup>®</sup> Development Platform Block Diagram

### **Physical Dimensions**

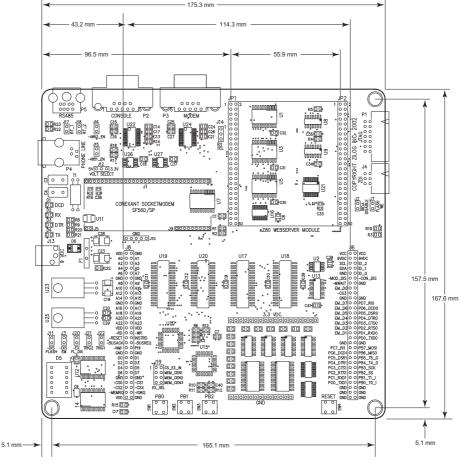

The dimensions of the eZ80 $^{\otimes}$  Development Platform PCB is 177.8 mm x 182.9 mm. The overall height is 38.1 mm. See Figure 5.

Figure 5. Physical Dimensions of the eZ80® Development Platform

### **Operational Description**

The eZ80<sup>®</sup> Development Platform can accept any eZ80<sup>®</sup>-core-based modules, provided that the module interfaces correctly to the eZ80<sup>®</sup> Development Platform. The purpose of the eZ80<sup>®</sup> Development Platform is to provide the application developer with a tool to evaluate the features of the eZ80F91, and to develop an application without building additional hardware.

#### eZ80F91 Module Interface

The eZ80<sup>®</sup> Development Platform provides an easy interface for connecting each of the development modules in the eZ80<sup>®</sup> family, including the eZ80F91 Module. The eZ80F91 Module interface consists of two 50-pin receptacles, JP1 and JP2, as described in the pages that follow.

Almost all of these receptacles' signals are connected directly to the CPU. Five input signals, in particular, offer options to the application developer by disabling certain functions of the eZ80F91 Module.

These five input signals<sup>1</sup> are:

- Disable Flash (DIS Flash)

- Flash Write Enable (FlashWE)

- Disable IrDA (DIS\_IrDA)

- <u>F91\_WE</u>

- RTC\_VDD

A description of these five signals follows.

**Disable Flash.** When active Low, the DIS\_Flash input signal disables the Flash chip on the eZ80F91 Module.

<sup>1.</sup> These input signals are only used if external Flash memory is present on the eZ80F91 Module. As shipped from the factory, external Flash is not installed.

11

**Flash Write Enable.** When active Low, the FlashWE input signal enables write operations on the Flash boot block of the eZ80F91 Module.

**Disable IrDA.** When the  $\overline{DIS\_IrDA}$  input signal is pulled Low, the IrDA transceiver, located on the eZ80F91 Module, is disabled. As a result, UART0 can be used with the RS232 or the RS485 interfaces on the eZ80® Development Platform.

**F91\_WE.** When the  $\overline{F91}$ \_WE signal is active Low, internal Flash on the eZ80F91 Module is enabled for writing. This signal is inverted from the WP signal of on the eZ80F91 Module.

**RTC\_VDD**. RTC\_VDD is a test point for the Real Time Clock power supply.

#### **Peripheral Bus Connector**

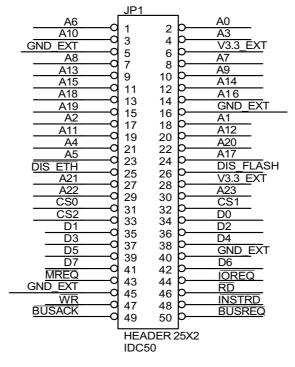

Figure 6 illustrates the pin layout of the Peripheral Bus Connector in the 50-pin header, located at position JP1 on the eZ80<sup>®</sup> Development Platform. Table 2 identifies the pins and their functions.

Figure 6. eZ80<sup>®</sup> Development Platform Peripheral Bus Connector Pin Configuration—JP1

## Table 2. eZ80<sup>®</sup> Development Platform Peripheral Bus Connector Identification—JP1<sup>1,3</sup>

| Pin# | Symbol   | Signal Direction | Active Level | eZ80F91 Signal <sup>2</sup> |

|------|----------|------------------|--------------|-----------------------------|

| 1    | A6       | Bidirectional    |              | Yes                         |

| 2    | A0       | Bidirectional    |              | Yes                         |

| 3    | A10      | Bidirectional    |              | Yes                         |

| 4    | A3       | Bidirectional    |              | Yes                         |

| 5    | GND      |                  |              |                             |

| 6    | $V_{DD}$ |                  |              |                             |

| 7    | A8       | Bidirectional    |              | Yes                         |

| 8    | A7       | Bidirectional    |              | Yes                         |

| 9    | A13      | Bidirectional    |              | Yes                         |

| 10   | A9       | Bidirectional    |              | Yes                         |

| 11   | A15      | Bidirectional    |              | Yes                         |

| 12   | A14      | Bidirectional    |              | Yes                         |

| 13   | A18      | Bidirectional    |              | Yes                         |

| 14   | A16      | Bidirectional    |              | Yes                         |

| 15   | A19      | Bidirectional    |              | Yes                         |

#### Notes:

- For the sake of simplicity in describing the interface, Power and Ground nets are omitted from this table. The entire interface is represented in the eZ80F91 Module Schematics on pages 64 through 66.

- 2. The Power and Ground nets are connected directly to the eZ80F91 device.

- 3. Additional note: external capacitive loads on RD, WR, IORQ, MREQ, D0–D7 and A0–A23 should be below 10 pF to satisfy the timing requirements for the eZ80 CPU. All unused inputs should be pulled to either V<sub>DD</sub> or GND, depending on their inactive levels to reduce power consumption and to reduce noise sensitivity. To prevent EMI, the EZ80CLK output can be deactivated via software in the eZ80F91's Peripheral Power-Down Register.

### Table 2. eZ80<sup>®</sup> Development Platform Peripheral Bus Connector Identification—JP1<sup>1,3</sup> (Continued)

| Pin# | Symbol          | Signal Direction | Active Level | eZ80F91 Signal <sup>2</sup> |

|------|-----------------|------------------|--------------|-----------------------------|

| 16   | GND             |                  |              |                             |

| 17   | A2              | Bidirectional    |              | Yes                         |

| 18   | A1              | Bidirectional    |              | Yes                         |

| 19   | A11             | Bidirectional    |              | Yes                         |

| 20   | A12             | Bidirectional    |              | Yes                         |

| 21   | A4              | Bidirectional    |              | Yes                         |

| 22   | A20             | Bidirectional    |              | Yes                         |

| 23   | A5              | Bidirectional    |              | Yes                         |

| 24   | A17             | Bidirectional    |              | Yes                         |

| 25   | DIS_ETH         | Output           | Low          | No                          |

| 26   | DIS_FLASH       | Output           | Low          | No                          |

| 27   | A21             | Bidirectional    |              | Yes                         |

| 28   | V <sub>DD</sub> |                  |              |                             |

| 29   | A22             | Bidirectional    |              | Yes                         |

| 30   | A23             | Bidirectional    |              | Yes                         |

#### Notes:

- For the sake of simplicity in describing the interface, Power and Ground nets are omitted from this table. The entire interface is represented in the eZ80F91 Module Schematics on pages 64 through 66.

- 2. The Power and Ground nets are connected directly to the eZ80F91 device.

- 3. Additional note: external capacitive loads on RD, WR, IORQ, MREQ, D0–D7 and A0–A23 should be below 10 pF to satisfy the timing requirements for the eZ80 CPU. All unused inputs should be pulled to either V<sub>DD</sub> or GND, depending on their inactive levels to reduce power consumption and to reduce noise sensitivity. To prevent EMI, the EZ80CLK output can be deactivated via software in the eZ80F91's Peripheral Power-Down Register.

### Table 2. eZ80<sup>®</sup> Development Platform Peripheral Bus Connector Identification—JP1<sup>1,3</sup> (Continued)

| Pin# | Symbol | Signal Direction | Active Level | eZ80F91 Signal <sup>2</sup> |

|------|--------|------------------|--------------|-----------------------------|

| 31   | CS0    | Input            | Low          | Yes                         |

| 32   | CS1    | Input            | Low          | Yes                         |

| 33   | CS2    | Input            | Low          | Yes                         |

| 34   | D0     | Bidirectional    |              | Yes                         |

| 35   | D1     | Bidirectional    |              | Yes                         |

| 36   | D2     | Bidirectional    |              | No                          |

| 37   | D3     | Bidirectional    |              | Yes                         |

| 38   | D4     | Bidirectional    |              | Yes                         |

| 39   | D5     | Bidirectional    |              | Yes                         |

| 40   | GND    |                  |              |                             |

| 41   | D7     | Bidirectional    |              | Yes                         |

| 42   | D6     | Bidirectional    |              | Yes                         |

| 43   | MREQ   | Bidirectional    | Low          | Yes                         |

| 44   | IORQ   | Bidirectional    | Low          | Yes                         |

| 45   | GND    |                  |              |                             |

|      |        |                  |              |                             |

#### Notes:

- For the sake of simplicity in describing the interface, Power and Ground nets are omitted from this table. The entire interface is represented in the eZ80F91 Module Schematics on pages 64 through 66.

- 2. The Power and Ground nets are connected directly to the eZ80F91 device.

- 3. Additional note: external capacitive loads on RD, WR, IORQ, MREQ, D0–D7 and A0–A23 should be below 10pF to satisfy the timing requirements for the eZ80 CPU. All unused inputs should be pulled to either V<sub>DD</sub> or GND, depending on their inactive levels to reduce power consumption and to reduce noise sensitivity. To prevent EMI, the EZ80CLK output can be deactivated via software in the eZ80F91's Peripheral Power-Down Register.