Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## eZ80Acclaim!® Flash Microcontrollers

## eZ80F91 MCU

**Product Specification**

PS019215-0910

Warning:

DO NOT USE IN LIFE SUPPORT

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

### **Document Disclaimer**

©2010 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

eZ80, Z80, and eZ80Acclaim! are registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

## **Revision History**

Each instance in the Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages or appropriate links given in the table below.

| Date              | Revision Level Section Description |                                                                                                                                                                                                                                             | Page<br>Number                                                                                                                                     |                                                 |

|-------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| September<br>2010 | 15                                 | All                                                                                                                                                                                                                                         | Updated logos and copyright date.                                                                                                                  | All                                             |

| August<br>2008    | 14                                 | Ordering Information                                                                                                                                                                                                                        | Updated Part Number Description section.                                                                                                           | 360                                             |

| May 2008          | 13                                 | Introduction, Figure 48, ZDI-<br>Supported Protocol, and<br>Figure 49                                                                                                                                                                       | Replaced ZPAK II with USB Smart Cable                                                                                                              | 231, 232,<br>and 233                            |

| September<br>2007 | 12                                 | General-Purpose Input/ Output, Flash Memory, Universal Asynchronous Receiver/Transmitter, Serial Peripheral Interface, Real- Time Clock Control Register, I <sup>2</sup> C Serial I/O Interface, Pin Description, and Ordering Information. | Updated Table 1, Figure 6, Flash<br>Program Control Register, UART<br>Transmitter, Figure 40, Table 93, I2C<br>Registers and Ordering Information. | 4, 53,<br>112,174,<br>176, 201,<br>223, and 359 |

| February<br>2007  | 11                                 |                                                                                                                                                                                                                                             | —Alternate Functions, Register Map - Electrical Characteristics chapters.                                                                          | 27, 45, 54,<br>339                              |

PS019215-0910 Revision History

| Date      | Revision<br>Level | Section                                        | Description                                                                                                                                                                                                            | Page<br>Number |

|-----------|-------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| June 2006 | 10                | Global modifications                           | Updated for new release.                                                                                                                                                                                               | All            |

|           |                   | Pin Identification on the eZ80F91 Device       | Table 3: The description of the following pins modified: pins 55, 61, 63 and 69                                                                                                                                        | 6              |

|           |                   | General-Purpose Input/<br>Output               | GPIO chapter totally rewritten                                                                                                                                                                                         | 49             |

|           |                   | Chip Selects and Wait States                   | Input/Output chip select operation modified                                                                                                                                                                            | 65             |

|           |                   | Flash Memory                                   | The following sections are modified in Flash memory chapter: Erasing Flash memory, Information page characteristics, Flash Write/Erase protection register, Flash program control registers, and Table 43.             | 97             |

|           |                   | Real-Time Clock Overview                       | Added a note in real time clock overview section                                                                                                                                                                       | 159            |

|           |                   | Universal Asynchronous<br>Receiver/Transmitter | Table 102 and 109 modified                                                                                                                                                                                             | 175            |

|           |                   | Infrared Encoder/Decoder<br>Control Registers  | The field [7:4] modified in Table 111                                                                                                                                                                                  | 199            |

|           |                   | Zilog Debug Interface                          | Updated the Introduction section,<br>Added two paragraphs to ZDI Read<br>Memory Registers                                                                                                                              | 231            |

|           |                   | On-Chip Oscillators                            | On page 349, Figure 63: Recommended Crystal Oscillator Configuration, the value of inductance L is changed to 3.3 $\mu$ H. On page 351, Table 232, changed serial resistance value from 40 k $\Omega$ to 50 k $\Omega$ | 336            |

|           |                   | POR and VBO Electrical Characteristics         | In Table 235: Min, Typ, and Max values of VBO voltage threshold modified and added IS <sub>por_vbo</sub> parameter                                                                                                     | 341            |

|           |                   | Ordering Information                           | Ordering information modified                                                                                                                                                                                          | 359            |

PS019215-0910 **Revision History**

## **Table of Contents**

| Architectural Overview                                 |

|--------------------------------------------------------|

| Features                                               |

| Block Diagram                                          |

| Pin Description                                        |

| Pin Characteristics                                    |

| System Clock Source Options                            |

| Register Map 2                                         |

| eZ80 <sup>®</sup> CPU Core 3                           |

| Features 3                                             |

| New Instructions                                       |

| Reset 4                                                |

| External Reset Input and Indicator 4                   |

| Power-On Reset 4                                       |

| Voltage Brownout Reset 4                               |

| Low-Power Modes                                        |

| SLEEP Mode                                             |

| HALT Mode                                              |

| Clock Peripheral Power-Down Registers4                 |

| General-Purpose Input/Output                           |

| GPIO Operation                                         |

| GPIO Interrupts                                        |

| GPIO Control Registers                                 |

| Interrupt Controller 5                                 |

| Maskable Interrupts                                    |

| GPIO Port Interrupts                                   |

| Chip Selects and Wait States                           |

| Memory and I/O Chip Selects 6                          |

| Memory Chip Select Operation                           |

| Input/Output Chip Select Operation 6                   |

| Wait States 6                                          |

| WAIT Input Signal                                      |

| Chip Selects During Bus Request/Bus Acknowledge Cycles |

PS019215-0910 **Table of Contents**

### eZ80F91 MCU | **Product Specification**

# zilog | vi

| ١ | ı |

|---|---|

|     | Bus Mode Controller                    | 70  |

|-----|----------------------------------------|-----|

|     | eZ80 <sup>®</sup> Bus Mode             | 71  |

|     | Z80 <sup>®</sup> Bus Mode              | 71  |

|     | Intel Bus Mode                         | 73  |

|     | Motorola Bus Mode                      | 80  |

|     | Chip Select Registers                  | 85  |

|     | Bus Arbiter                            | 89  |

| Raı | ndom Access Memory                     | 93  |

|     | RAM Control Registers                  | 94  |

| Fla | sh Memory                              | 97  |

|     | Flash Memory Overview                  | 98  |

|     | Reading Flash Memory                   | 98  |

|     | Memory Read                            | 99  |

|     | Programming Flash Memory               | 99  |

|     | Erasing Flash Memory                   | 101 |

|     | Information Page Characteristics       | 102 |

|     | Flash Control Registers                | 102 |

| Wa  | tchdog Timer                           | 115 |

|     | Watchdog Timer Operation               | 116 |

|     | Watchdog Timer Registers               |     |

| Pro | ogrammable Reload Timers               | 121 |

|     | Basic Timer Operation                  | 122 |

|     | Specialty Timer Modes                  | 126 |

|     | Timer Port Pin Allocation              | 129 |

|     | Timer Registers                        | 130 |

|     | Multi-PWM Mode                         | 145 |

|     | PWM Master Mode                        | 148 |

|     | Modification of Edge Transition Values | 148 |

|     | AND/OR Gating of the PWM Outputs       | 149 |

|     | PWM Nonoverlapping Output Pair Delays  | 150 |

|     | Multi-PWM Power-Trip Mode              | 152 |

|     | Multi-PWM Control Registers            | 153 |

| Rea | al-Time Clock                          | 159 |

|     | Real-Time Clock Overview               | 159 |

PS019215-0910 **Table of Contents**

### eZ80F91 MCU Product Specification

|   |   | • |

|---|---|---|

|   |   |   |

| • | • |   |

|        | Real-Time Clock Alarm                                   | 160         |

|--------|---------------------------------------------------------|-------------|

|        | Real-Time Clock Oscillator and Source Selection         | 160         |

|        | Real-Time Clock Battery Backup                          | 160         |

|        | Real-Time Clock Recommended Operation                   | 160         |

|        | Real-Time Clock Registers                               | 161         |

| Uni    | iversal Asynchronous Receiver/Transmitter               | 175         |

|        | UART Functional Description                             | 176         |

|        | UART Functions                                          | 176         |

|        | UART Interrupts                                         | 178         |

|        | UART Recommended Usage                                  | 179         |

|        | Baud Rate Generator                                     | 181         |

|        | BRG Control Registers                                   | 182         |

|        | UART Registers                                          | 183         |

| Infr   | rared Encoder/Decoder                                   | 195         |

|        | Functional Description                                  | 195         |

|        | Transmit                                                | 196         |

|        | Receive                                                 | 196         |

|        | Jitter                                                  | 198         |

|        | Infrared Encoder/Decoder Signal Pins                    | 198         |

|        | Loopback Testing                                        | 198         |

| Ser    | fial Peripheral Interface                               | <b>20</b> 1 |

|        | SPI Signals                                             | 202         |

|        | SPI Functional Description                              | 204         |

|        | SPI Flags                                               | 204         |

|        | SPI Baud Rate Generator                                 | 205         |

|        | Data Transfer Procedure with SPI Configured as a Master | 205         |

|        | Data Transfer Procedure with SPI Configured as a Slave  | 206         |

|        | SPI Registers                                           | 206         |

| $I^2C$ | Serial I/O Interface                                    | <b>21</b> 1 |

|        | I <sup>2</sup> C General Characteristics                | 211         |

|        | Transferring Data                                       | 213         |

|        | Clock Synchronization                                   | 214         |

|        | Operating Modes                                         | 216         |

|        | I2C Registers                                           | 223         |

PS019215-0910 **Table of Contents**

### eZ80F91 MCU Product Specification

## zilog

| ī | ī | ı |

|---|---|---|

|   |   |   |

|   |   |   |

| Zilog Debug Interface                                   | 231 |

|---------------------------------------------------------|-----|

| Introduction                                            | 231 |

| ZDI-Supported Protocol                                  | 232 |

| ZDI Clock and Data Conventions                          | 233 |

| ZDI Start Condition                                     | 233 |

| ZDI Register Addressing                                 | 235 |

| ZDI Write Operations                                    | 236 |

| ZDI Read Operations                                     | 237 |

| Operation of the eZ80F91 Device during ZDI Break Points | 238 |

| Bus Requests During ZDI Debug Mode                      | 238 |

| ZDI Write Only Registers                                | 239 |

| ZDI Read Only Registers                                 | 240 |

| ZDI Register Definitions                                | 241 |

| On-Chip Instrumentation                                 | 257 |

| Introduction to On-Chip Instrumentation                 | 257 |

| OCI Activation                                          | 258 |

| OCI Interface                                           | 258 |

| JTAG Boundary Scan                                      | 259 |

| Phase-Locked Loop                                       | 265 |

| Overview                                                | 265 |

| PLL Normal Operation                                    | 267 |

| Power Requirement to the Phase-Locked Loop Function     | 268 |

| PLL Registers                                           | 268 |

| PLL Characteristics                                     | 272 |

| eZ80 <sup>®</sup> CPU Instruction Set                   | 275 |

| Opcode Map                                              |     |

| Ethernet Media Access Controller                        |     |

| EMAC Functional Description                             | 288 |

| EMAC Interrupts                                         | 292 |

| EMAC Shared Memory Organization                         | 292 |

| EMAC and the System Clock                               | 296 |

| EMAC Operation in HALT Modes                            | 297 |

| EMAC Registers                                          | 297 |

| EMAC Interpacket Gap                                    | 306 |

PS019215-0910 Table of Contents

### eZ80F91 MCU Product Specification

| On-Chip Oscillators                                    | . 335 |

|--------------------------------------------------------|-------|

| Primary Crystal Oscillator Operation                   | . 335 |

| 32 kHz Real-Time Clock Crystal Oscillator Operation    | . 337 |

| Electrical Characteristics                             | . 339 |

| Absolute Maximum Ratings                               | . 339 |

| DC Characteristics                                     | . 339 |

| POR and VBO Electrical Characteristics                 | . 340 |

| Flash Memory Characteristics                           | . 341 |

| Current Consumption Under Various Operating Conditions | . 341 |

| AC Characteristics                                     | . 344 |

| External Memory Read Timing                            | . 346 |

| External Memory Write Timing                           | . 347 |

| External I/O Read Timing                               | . 349 |

| External I/O Write Timing                              | . 350 |

| Wait State Timing for Read Operations                  | . 352 |

| Wait State Timing for Write Operations                 | . 353 |

| General-Purpose Input/Output Port Input Sample Timing  | . 354 |

| General-Purpose I/O Port Output Timing                 | . 354 |

| External Bus Acknowledge Timing                        | . 355 |

| Packaging                                              |       |

| Ordering Information                                   | . 359 |

| Part Number Description                                |       |

| Index                                                  |       |

| Customer Support                                       | . 375 |

PS019215-0910 Table of Contents

## **Architectural Overview**

Zilog's eZ80F91 device is a member of Zilog's family of eZ80Acclaim!<sup>®</sup> Flash microcontrollers. The eZ80F91 is a high-speed microcontroller with a maximum clock speed of 50 MHz and single-cycle instruction fetch. It operates in Z80<sup>®</sup>-compatible addressing mode (64 KB) or full 24-bit addressing mode (16 MB). The rich peripheral set of the eZ80F91 makes it suitable for a variety of applications, including industrial control, embedded communication, and point-of-sale terminals.

### **Features**

Key features of eZ80F91 device include:

- Single-cycle instruction fetch, high-performance, pipelined eZ80<sup>®</sup> CPU core (referred as *The CPU* in this document)

- 10/100 BaseT ethernet media access controller with Media-Independent Interface (MII)

- 256 KB Flash memory

- 16 KB SRAM (8 KB user and 8 KB Ethernet)

- Low-power features including SLEEP mode, HALT mode, and selective peripheral power-down control

- Two Universal Asynchronous Receiver/Transmitter (UART) with independent Baud Rate Generators (BRG)

- Serial Peripheral Interface (SPI) with independent clock rate generator

- I<sup>2</sup>C with independent clock rate generator

- IrDA-compliant infrared encoder/decoder

- Glueless external peripheral interface with 4 Chip Selects, individual Wait State generators, an external WAIT input pin—supports Z80-, Intel-, and Motorola-style buses

- Fixed-priority vectored interrupts (both internal and external) and interrupt controller

- Real-time clock with separate V<sub>DD</sub> pin for battery backup and selectable on-chip

32 kHz oscillator or external 50/60 Hz input

- Four 16-bit Counter/Timers with prescalers and direct input/output drive

- Watchdog Timer with internal oscillator clocking option

- 32 bits of General-Purpose Input/Output (GPIO)

- On-Chip Instrumentation (OCI<sup>TM</sup>) and Zilog Debug Interfaces (ZDI)

- IEEE 1149.1-compatible JTAG

- 144-pin LQFP and BGA packages

- 3.0 V to 3.6 V supply voltage with 5 V tolerant inputs

- Operating Temperature Range:

- Standard: 0 °C to +70 °C

- Extended: -40 °C to +105 °C

Note:

All signals with an  $\overline{\text{overline}}$  are active Low. For example, the signal  $\overline{\text{DCD1}}$  is active when it is a logical 0 (Low) state.

The power connections conventions are provided in the table below.

| Connection | Circuit  | Device   |  |

|------------|----------|----------|--|

| Power      | $V_{CC}$ | $V_{DD}$ |  |

| Ground     | GND      | $V_{SS}$ |  |

### **Block Diagram**

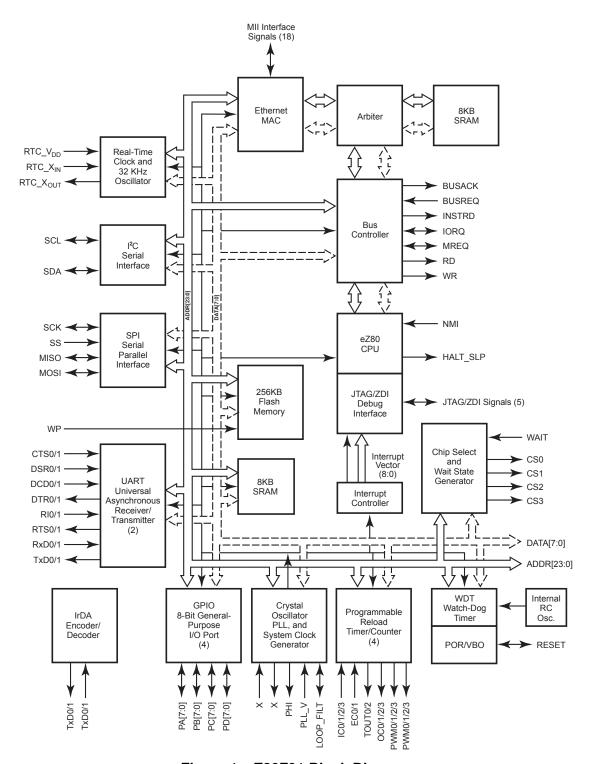

Figure 1 on page 3 displays a block diagram of the eZ80F91 microcontroller.

Figure 1. eZ80F91 Block Diagram

### **Pin Description**

Table 1 lists the pin configuration of the eZ80F91 device in the 144-BGA package.

Table 1. eZ80F91 144-BGA Pin Configuration

|   | 12               | 11              | 10                      | 9            | 8               | 7                       | 6               | 5          | 4               | 3               | 2               | 1               |

|---|------------------|-----------------|-------------------------|--------------|-----------------|-------------------------|-----------------|------------|-----------------|-----------------|-----------------|-----------------|

| Α | SDA              | SCL             | PA0                     | PA4          | PA7             | COL                     | TxD0            | $V_{DD}$   | Rx_DV           | MDC             | WPn             | A0              |

| В | $V_{SS}$         | PHI             | PA1                     | PA3          | $V_{DD}$        | TxD3                    | Tx_EN           | $V_{SS}$   | RxD1            | MDIO            | A2              | A1              |

| С | PB6              | PB7             | $V_{DD}$                | PA5          | V <sub>SS</sub> | TxD2                    | Tx_CLK          | Rx_<br>CLK | RxD3            | A3              | $V_{SS}$        | $V_{DD}$        |

| D | PB1              | PB3             | PB5                     | $V_{SS}$     | CRS             | TxD1                    | Rx_ER           | RxD2       | A4              | A8              | A6              | A7              |

| Ε | PC7              | $V_{DD}$        | PB0                     | PB4          | PA2             | Tx_ER                   | RxD0            | A5         | A11             | $V_{SS}$        | $V_{DD}$        | A10             |

| F | PC3              | PC4             | PC5                     | $V_{SS}$     | PB2             | PA6                     | A9              | A17        | A15             | A14             | A13             | A12             |

| G | V <sub>SS</sub>  | PC0             | PC1                     | PC2          | PC6             | PLL_<br>V <sub>SS</sub> | V <sub>SS</sub> | A23        | A20             | V <sub>SS</sub> | $V_{DD}$        | A16             |

| Н | X <sub>OUT</sub> | X <sub>IN</sub> | PLL_<br>V <sub>DD</sub> | $V_{DD}$     | PD7             | TMS                     | V <sub>SS</sub> | D5         | V <sub>SS</sub> | A21             | A19             | A18             |

| J | V <sub>SS</sub>  | V <sub>DD</sub> | LOOP<br>FILT_<br>OUT    | PD4          | TRIGOUT         | RTC_<br>V <sub>DD</sub> | NMIn            | WRn        | D2              | CS0n            | V <sub>DD</sub> | A22             |

| K | PD5              | PD6             | PD3                     | TDI          | V <sub>SS</sub> | $V_{DD}$                | RESETn          | RDn        | $V_{DD}$        | D1              | CS2n            | CS1n            |

| L | PD1              | PD2             | TRSTn                   | TCK          | RTC_<br>XOUT    | BUSACKn                 | WAITn           | MREQn      | D6              | D4              | D0              | CS3n            |

| M | PD0              | V <sub>SS</sub> | TDO                     | HALT<br>SLPn | RTC_<br>XIN     | BUSREQn                 | INSTRDn         | IORQn      | D7              | D3              | V <sub>SS</sub> | V <sub>DD</sub> |

Note: Lowercase n suffix indicates an active-low signal in this table only

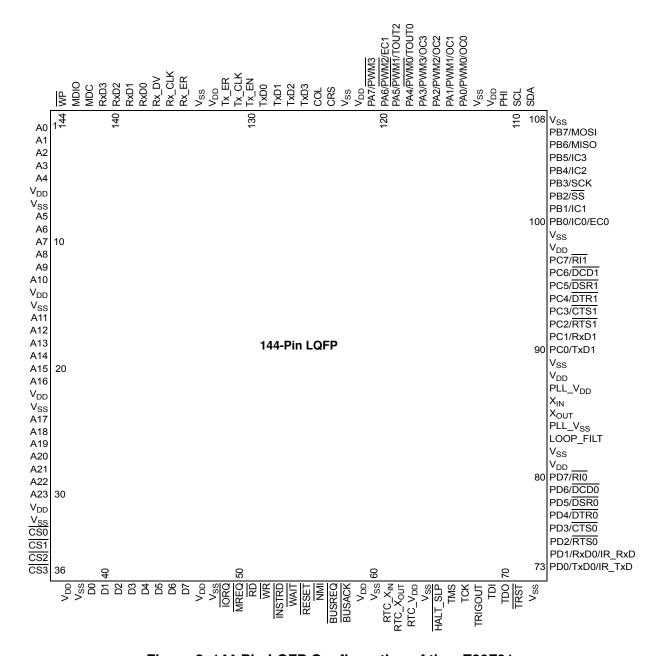

Figure 2 displays the pin layout of the eZ80F91 device in the 144-pin LQFP package.

Figure 2. 144-Pin LQFP Configuration of the eZ80F91

### **Pin Characteristics**

Table 2 lists the pins and functions of the eZ80F91 MCU's 144-pin LQFP package and 144-BGA package.

Table 2. Pin Identification on the eZ80F91 Device

| LQFP<br>Pin No | BGA<br>Pin No | Symbol          | Function     | Signal Direction | Description                                                                                                                                                                                                                                                     |

|----------------|---------------|-----------------|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | A1            | ADDR0           | Address Bus  | Bidirectional    | Configured as an output in normal                                                                                                                                                                                                                               |

| 2              | B1            | ADDR1           | Address Bus  | Bidirectional    | operation. The address bus selects a location in memory or I/O space to be                                                                                                                                                                                      |

| 3              | B2            | ADDR2           | Address Bus  | Bidirectional    | read or written. Configured as an input                                                                                                                                                                                                                         |

| 4              | C3            | ADDR3           | Address Bus  | Bidirectional    | during bus acknowledge cycles. Drives the Chip Select/Wait State                                                                                                                                                                                                |

| 5              | D4            | ADDR4           | Address Bus  | Bidirectional    | Generator block to generate Chip Selects.                                                                                                                                                                                                                       |

| 6              | C1            | $V_{DD}$        | Power Supply |                  | Power Supply.                                                                                                                                                                                                                                                   |

| 7              | C2            | V <sub>SS</sub> | Ground       |                  | Ground.                                                                                                                                                                                                                                                         |

| 8              | E5            | ADDR5           | Address Bus  | Bidirectional    | Configured as an output in normal                                                                                                                                                                                                                               |

| 9              | D2            | ADDR6           | Address Bus  | Bidirectional    | operation. The address bus selects a location in memory or I/O space to be                                                                                                                                                                                      |

| 10             | D1            | ADDR7           | Address Bus  | Bidirectional    | read or written. Configured as an input                                                                                                                                                                                                                         |

| 11             | D3            | ADDR8           | Address Bus  | Bidirectional    | during bus acknowledge cycles. Drives the Chip Select/Wait State                                                                                                                                                                                                |

| 12             | F6            | ADDR9           | Address Bus  | Bidirectional    | Generator block to generate Chip                                                                                                                                                                                                                                |

| 13             | E1            | ADDR10          | Address Bus  | Bidirectional    | Selects.                                                                                                                                                                                                                                                        |

| 14             | E2            | $V_{DD}$        | Power Supply |                  | Power Supply.                                                                                                                                                                                                                                                   |

| 15             | E3            | V <sub>SS</sub> | Ground       |                  | Ground.                                                                                                                                                                                                                                                         |

| 16             | E4            | ADDR11          | Address Bus  | Bidirectional    | Configured as an output in normal operation. The address bus selects a location in memory or I/O space to be read or written. Configured as an input during bus acknowledge cycles. Drives the Chip Select/Wait State Generator block to generate Chip Selects. |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP<br>Pin No | BGA<br>Pin No | Symbol          | Function      | Signal Direction      | Description                                                                                   |

|----------------|---------------|-----------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------|

| 17             | F1            | ADDR12          | Address Bus   | Bidirectional         | Configured as an output in normal                                                             |

| 18             | F2            | ADDR13          | Address Bus   | Bidirectional         | operation. The address bus selects a location in memory or I/O space to be                    |

| 19             | F3            | ADDR14          | Address Bus   | Bidirectional         | read or written. Configured as an input                                                       |

| 20             | F4            | ADDR15          | Address Bus   | Bidirectional         | during bus acknowledge cycles. Drives the Chip Select/Wait State                              |

| 21             | G1            | ADDR16          | Address Bus   | Bidirectional         | Generator block to generate Chip Selects.                                                     |

| 22             | G2            | $V_{DD}$        | Power Supply  |                       | Power Supply.                                                                                 |

| 23             | G3            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                       |

| 24             | F5            | ADDR17          | Address Bus   | Bidirectional         | Configured as an output in normal                                                             |

| 25             | H1            | ADDR18          | Address Bus   | Bidirectional         | operation. The address bus selects a location in memory or I/O space to be                    |

| 26             | H2            | ADDR19          | Address Bus   | Bidirectional         | read or written. Configured as an input                                                       |

| 27             | G4            | ADDR20          | Address Bus   | Bidirectional         | during bus acknowledge cyclesDrives the Chip Select/Wait State                                |

| 28             | НЗ            | ADDR21          | Address Bus   | Bidirectional         | Generator block to generate Chip                                                              |

| 29             | J1            | ADDR22          | Address Bus   | Bidirectional         | Selects.                                                                                      |

| 30             | G5            | ADDR23          | Address Bus   | Bidirectional         | _                                                                                             |

| 31             | J2            | $V_{DD}$        | Power Supply  |                       | Power Supply.                                                                                 |

| 32             | H4            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                       |

| 33             | J3            | CS0             | Chip Select 0 | Output, Active<br>Low | CSO Low indicates that an access is occurring in the defined CSO memory or I/O address space. |

| 34             | K1            | CS1             | Chip Select 1 | Output, Active<br>Low | CS1 Low indicates that an access is occurring in the defined CS1 memory or I/O address space. |

| 35             | K2            | CS2             | Chip Select 2 | Output, Active<br>Low | CS2 Low indicates that an access is occurring in the defined CS2 memory or I/O address space. |

| 36             | L1            | CS3             | Chip Select 3 | Output, Active<br>Low | CS3 Low indicates that an access is occurring in the defined CS3 memory or I/O address space. |

| 37             | M1            | V <sub>DD</sub> | Power Supply  |                       | Power Supply.                                                                                 |

| 38             | M2            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                       |

|                |               |                 |               |                       |                                                                                               |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP<br>Pin No | BGA<br>Pin No | Symbol          | Function                | Signal Direction             | Description                                                                                                                                                                                                                            |

|----------------|---------------|-----------------|-------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39             | L2            | DATA0           | Data Bus                | Bidirectional                | The data bus transfers data to and                                                                                                                                                                                                     |

| 40             | K3            | DATA1           | Data Bus                | Bidirectional                | from I/O and memory devices. The _eZ80F91 drives these lines only                                                                                                                                                                      |

| 41             | J4            | DATA2           | Data Bus                | Bidirectional                | during Write cycles when the                                                                                                                                                                                                           |

| 42             | M3            | DATA3           | Data Bus                | Bidirectional                | eZ80F91 is the bus master.                                                                                                                                                                                                             |

| 43             | L3            | DATA4           | Data Bus                | Bidirectional                | -                                                                                                                                                                                                                                      |

| 44             | H5            | DATA5           | Data Bus                | Bidirectional                | -                                                                                                                                                                                                                                      |

| 45             | L4            | DATA6           | Data Bus                | Bidirectional                | -                                                                                                                                                                                                                                      |

| 46             | M4            | DATA7           | Data Bus                | Bidirectional                | -                                                                                                                                                                                                                                      |

| 47             | K4            | V <sub>DD</sub> | Power Supply            |                              | Power Supply.                                                                                                                                                                                                                          |

| 48             | G6            | V <sub>SS</sub> | Ground                  |                              | Ground.                                                                                                                                                                                                                                |

| 49             | M5            | ĪORQ            | Input/Output<br>Request | Bidirectional,<br>Active Low | IORQ indicates that the CPU is accessing a location in I/O space. RD and WR indicate the type of access. The eZ80F91 device does not drive this line during RESET. It is an input during bus acknowledge cycles.                       |

| 50             | L5            | MREQ            | Memory<br>Request       | Bidirectional,<br>Active Low | MREQ Low indicates that the CPU is accessing a location in memory. The RD, WR, and INSTRD signals indicate the type of access. The eZ80F91 device does not drive this line during RESET. It is an input during bus acknowledge cycles. |

| 51             | K5            | RD              | Read                    | Output,<br>Active Low        | RD Low indicates that the eZ80F91 device is reading from the current address location. This pin is in a high-impedance state during bus acknowledge cycles.                                                                            |

| 52             | J5            | WR              | Write                   | Output, Active<br>Low        | WR indicates that the CPU is writing to the current address location. This pin is in a high-impedance state during bus acknowledge cycles.                                                                                             |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP   | BGA    |                 |                               |                                                                                  |                                                                                                                                                                                                                                                               |

|--------|--------|-----------------|-------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No | Pin No | Symbol          | Function                      | Signal Direction                                                                 | Description                                                                                                                                                                                                                                                   |

| 53     | M6     | INSTRD          | Instruction<br>Read Indicator | Output, Active<br>Low                                                            | INSTRD (with MREQ and RD) indicates the eZ80F91 device is fetching an instruction from memory. This pin is in a high-impedance state during bus acknowledge cycles.                                                                                           |

| 54     | L6     | WAIT            | WAIT Request                  | Schmitt-trigger input, Active Low                                                | Driving the WAIT pin Low forces the CPU to wait additional clock cycles for an external peripheral or external memory to complete its Read or Write operation.                                                                                                |

| 55     | K6     | RESET           | Reset                         | Bidirectional,<br>Active Low<br>Schmitt-trigger<br>input or open<br>drain output | This signal is used to initialize the eZ80F91, and/or allow the ez80F91 to signal when it resets. See reset section for the timing details. This Schmitt-trigger input allows for RC rise times.                                                              |

| 56     | J6     | NMI             | Nonmaskable<br>Interrupt      | Schmitt-trigger<br>input, Active Low,<br>edge-triggered<br>interrupt             | The NMI input is a higher priority input than the maskable interrupts. It is always recognized at the end of an instruction, regardless of the state of the interrupt enable control bits. This input includes a Schmitt- trigger to allow for RC rise times. |

| 57     | M7     | BUSREQ          | Bus Request                   | Schmitt-trigger input, Active Low                                                | External devices request the eZ80F91 device to release the memory interface bus for their use by driving this pin Low.                                                                                                                                        |

| 58     | L7     | BUSACK          | Bus<br>Acknowledge            | Output, Active<br>Low                                                            | The eZ80F91 device responds to a Low on BUSREQ making the address, data, and control signals high impedance, and by driving the BUSACK line Low. During bus acknowledge cycles ADDR[23:0], IORQ, and MREQ are inputs.                                         |

| 59     | K7     | V <sub>DD</sub> | Power Supply                  |                                                                                  | Power Supply.                                                                                                                                                                                                                                                 |

| 60     | H6     | V <sub>SS</sub> | Ground                        |                                                                                  | Ground.                                                                                                                                                                                                                                                       |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP<br>Pin No | BGA<br>Pin No | Symbol               | Function                             | Signal Direction      | Description                                                                                                                                                                                                                                                                                                                   |

|----------------|---------------|----------------------|--------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61             | M8            | RTC_X <sub>IN</sub>  | Real-Time<br>Clock Crystal<br>Input  | Input                 | This pin is the input to the low-power 32 kHz crystal oscillator for the Realtime clock. If the Real-time clock is disabled or not used, this input must be left floating or tied to VSS to minimize any input current leakage.                                                                                               |

| 62             | L8            | RTC_X <sub>OUT</sub> | Real-Time<br>Clock Crystal<br>Output | Bidirectional         | This pin is the output from the low-power 32 kHz crystal oscillator for the Real-Time Clock. This pin is an input when the RTC is configured to operate from 50/60 Hz input clock signals and the 32 kHz crystal oscillator is disabled.                                                                                      |

| 63             | J7            | RTC_V <sub>DD</sub>  | Real-Time<br>Clock Power<br>Supply   |                       | Power supply for the Real-Time Clock and associated 32 kHz oscillator. Isolated from the power supply to the remainder of the chip. A battery is connected to this pin to supply constant power to the Real-Time Clock and 32 kHz oscillator. If the Real-time clock is disabled or not used this output must be tied to Vdd. |

| 64             | K8            | V <sub>SS</sub>      | Ground                               |                       | Ground.                                                                                                                                                                                                                                                                                                                       |

| 65             | M9            | HALT_SLP             | HALT and<br>SLEEP<br>Indicator       | Output, Active<br>Low | A Low on this pin indicates that the CPU has entered either HALT or SLEEP mode because of execution of either a HALT or SLP instruction.                                                                                                                                                                                      |

| 66             | H7            | TMS                  | JTAG Test<br>Mode Select             | Input                 | JTAG Mode Select Input.                                                                                                                                                                                                                                                                                                       |

| 67             | L9            | TCK                  | JTAG Test<br>Clock                   | Input                 | JTAG and ZDI clock input.                                                                                                                                                                                                                                                                                                     |

| 68             | J8            | TRIGOUT              | JTAG Test<br>Trigger Output          | Output                | Active High trigger event indicator.                                                                                                                                                                                                                                                                                          |

| 69             | K9            | TDI                  | JTAG Test<br>Data In                 | Bidirectional         | JTAG data input pin. Functions as ZDI data I/O pin when JTAG is disabled. This pin has an internal pull-up resistor in the pad.                                                                                                                                                                                               |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP   | BGA    |                 |                       |                                   |                                                                                                                                                                                                                                                                         |

|--------|--------|-----------------|-----------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No | Pin No | Symbol          | Function              | Signal Direction                  | Description                                                                                                                                                                                                                                                             |

| 70     | M10    | TDO             | JTAG Test<br>Data Out | Output                            | JTAG data output pin.                                                                                                                                                                                                                                                   |

| 71     | L10    | TRST            | JTAG Reset            | Schmitt-trigger input, Active Low | JTAG reset input pin.                                                                                                                                                                                                                                                   |

| 72     | M11    | V <sub>SS</sub> | Ground                |                                   | Ground.                                                                                                                                                                                                                                                                 |

| 73     | M12    | PD0             | GPIO Port D           | Bidirectional                     | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port D pin, when programmed as output is selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|        |        | TxD0            | UART<br>Transmit Data | Output                            | This pin is used by the UART to transmit asynchronous serial data. This signal is multiplexed with PD0.                                                                                                                                                                 |

|        |        | IR_TxD          | IrDA Transmit<br>Data | Output                            | This pin is used by the IrDA encoder/decoder to transmit serial data. This signal is multiplexed with PD0.                                                                                                                                                              |

| 74     | L12    | PD1             | GPIO Port D           | Bidirectional                     | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port D pin, when programmed as output is selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|        |        | RxD0            | Receive Data          | Input                             | This pin is used by the UART to receive asynchronous serial data. This signal is multiplexed with PD1.                                                                                                                                                                  |

|        |        | IR_RxD          | IrDA Receive<br>Data  | Input                             | This pin is used by the IrDA encoder/decoder to receive serial data. This signal is multiplexed with PD1.                                                                                                                                                               |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP<br>Pin No | BGA<br>Pin No | Symbol | Function               | Signal Direction      | Description                                                                                                                                                                                                                                                             |

|----------------|---------------|--------|------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 75             | L11           | PD2    | GPIO Port D            | Bidirectional         | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port D pin, when programmed as output is selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|                |               | RTS0   | Request to<br>Send     | Output,<br>Active Low | Modem control signal from UART. This signal is multiplexed with PD2.                                                                                                                                                                                                    |

| 76             | K10           | PD3    | GPIO Port D            | Bidirectional         | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port D pin, when programmed as output is selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|                |               | CTS0   | Clear to Send          | Input, Active Low     | Modem status signal to the UART.<br>This signal is multiplexed with PD3.                                                                                                                                                                                                |

| 77             | J9            | PD4    | GPIO Port D            | Bidirectional         | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port D pin, when programmed as output is selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|                |               | DTR0   | Data Terminal<br>Ready | Output,<br>Active Low | Modem control signal to the UART.<br>This signal is multiplexed with PD4.                                                                                                                                                                                               |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP<br>Pin No | BGA<br>Pin No | Symbol              | Function                             | Signal Direction  | Description                                                                                                                                                                                                                                                             |

|----------------|---------------|---------------------|--------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78             | K12           | PD5                 | GPIO Port D                          | Bidirectional     | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port D pin, when programmed as output is selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|                |               | DSR0                | Data Set<br>Ready                    | Input, Active Low | Modem status signal to the UART.<br>This signal is multiplexed with PD5.                                                                                                                                                                                                |

| 79             | K11           | PD6                 | GPIO Port D                          | Bidirectional     | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port D pin, when programmed as output is selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|                |               | DCD0                | Data Carrier<br>Detect               | Input, Active Low | Modem status signal to the UART.<br>This signal is multiplexed with PD6.                                                                                                                                                                                                |

| 80             | H8            | PD7                 | GPIO Port D                          | Bidirectional     | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port D pin, when programmed as output is selected to be an open-drain or open-source output. Port D is multiplexed with one UART. |

|                |               | RI0                 | Ring Indicator                       | Input, Active Low | Modem status signal to the UART.<br>This signal is multiplexed with PD7.                                                                                                                                                                                                |

| 81             | J11           | $V_{DD}$            | Power Supply                         |                   | Power Supply.                                                                                                                                                                                                                                                           |

| 82             | J12           | $V_{SS}$            | Ground                               |                   | Ground.                                                                                                                                                                                                                                                                 |

| 83             | J10           | LOOP_FILT           | PLL Loop Filter                      | Analog            | Loop Filter pin for the Analog PLL.                                                                                                                                                                                                                                     |

| 84             | G7            | PLL_V <sub>SS</sub> | Ground                               |                   | Ground for Analog PLL.                                                                                                                                                                                                                                                  |

| 85             | H12           | X <sub>OUT</sub>    | System Clock<br>Oscillator<br>Output | Output            | This pin is the output of the onboard crystal oscillator. When used, a crystal must be connected between $X_{\text{IN}}$ and $X_{\text{OUT}}$ .                                                                                                                         |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP<br>Pin No | BGA<br>Pin No | Symbol              | Function                         | Signal Direction                               | Description                                                                                                                                                                                                                                                             |

|----------------|---------------|---------------------|----------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 86             | H11           | X <sub>IN</sub>     | System Clock<br>Oscillator Input | Input                                          | This pin is the input to the onboard crystal oscillator for the primary system clock. If an external oscillator is used, its clock output must be connected to this pin. When a crystal is used, it must be connected between $X_{IN}$ and $X_{OUT}$ .                  |

| 87             | H10           | PLL_V <sub>DD</sub> | Power Supply                     |                                                | Power Supply for Analog PLL.                                                                                                                                                                                                                                            |

| 88             | H9            | $V_{DD}$            | Power Supply                     |                                                | Power Supply.                                                                                                                                                                                                                                                           |

| 89             | G12           | V <sub>SS</sub>     | Ground                           |                                                | Ground.                                                                                                                                                                                                                                                                 |

| 90             | G11           | PC0                 | GPIO Port C                      | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port C pin, when programmed as output is selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|                |               | TxD1                | Transmit Data                    | Output                                         | This pin is used by the UART to transmit asynchronous serial data. This signal is multiplexed with PC0.                                                                                                                                                                 |

| 91             | G10           | PC1                 | GPIO Port C                      | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port C pin, when programmed as output is selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|                |               | RxD1                | Receive Data                     | Schmitt-trigger input                          | This pin is used by the UART to receive asynchronous serial data. This signal is multiplexed with PC1.                                                                                                                                                                  |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP<br>Pin No | BGA<br>Pin No | Symbol | Function               | Signal Direction                               | Description                                                                                                                                                                                                                                                             |

|----------------|---------------|--------|------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 92             | G9            | PC2    | GPIO Port C            | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port C pin, when programmed as output is selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|                |               | RTS1   | Request to<br>Send     | Output, Active<br>Low                          | Modem control signal from UART. This signal is multiplexed with PC2.                                                                                                                                                                                                    |

| 93             | F12           | PC3    | GPIO Port C            | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port C pin, when programmed as output is selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|                |               | CTS1   | Clear to Send          | Schmitt-trigger input, Active Low              | Modem status signal to the UART. This signal is multiplexed with PC3.                                                                                                                                                                                                   |

| 94             | F11           | PC4    | GPIO Port C            | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port C pin, when programmed as output is selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|                |               | DTR1   | Data Terminal<br>Ready | Output, Active<br>Low                          | Modem control signal to the UART. This signal is multiplexed with PC4.                                                                                                                                                                                                  |

Table 2. Pin Identification on the eZ80F91 Device (Continued)

| LQFP   | BGA    |          |                        | 0. 15                                          | <b>5</b>                                                                                                                                                                                                                                                                |

|--------|--------|----------|------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No | Pin No | Symbol   | Function               | Signal Direction                               | Description                                                                                                                                                                                                                                                             |

| 95     | F10    | PC5      | GPIO Port C            | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port C pin, when programmed as output is selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        |        | DSR1     | Data Set<br>Ready      | Schmitt-trigger input, Active Low              | Modem status signal to the UART. This signal is multiplexed with PC5.                                                                                                                                                                                                   |

| 96     | G8     | PC6      | GPIO Port C            | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is individually programmed as input or output and is also used individually as an interrupt input. Each Port C pin, when programmed as output is selected to be an open-drain or open-source output. Port C is multiplexed with one UART. |

|        |        | DCD1     | Data Carrier<br>Detect | Schmitt-trigger input, Active Low              | Modem status signal to the UART. This signal is multiplexed with PC6.                                                                                                                                                                                                   |