# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconduc

June 2011

# FAB2200 Audio Subsystem with Stereo Class-G Headphone Amplifier and 1.2W Mono Class-D Speaker Amplifier

#### Features

- Single Supply: 2.8V 5.25V

- Pop and Click Suppression

- Differential or Single-Ended Audio Inputs

- Rejects TDMA Noise from GSM Handsets

- Filterless Fully Differential Class-D Speaker Amplifier

- Programmable Edge-Rate Control and Spread Spectrum Minimize EMI

- 1.2W into 8Ω at 4.2V, THD+N < 10%

- 970mW into 8 $\Omega$  at 4.2V, THD+N < 1%

- 90% Efficiency

- Automatic Gain Control Limits Distortion and Protects Speakers at All Battery Voltages

- Noise Gate Improves Audio Quality

- Headphone Amplifier

- Power-Saving Class-G Operation

- Audio Taper I<sup>2</sup>C Volume Control

- Capacitor-Free Outputs

- Integrated Regulated Charge Pump

- SGND Pin Eliminates Ground-Loop Noise

- Noise Gate Improves Audio Quality

- DPST Analog Bypass Switch

- I<sup>2</sup>C Control

- Low-Power Shutdown Mode

- Current Limit and Thermal Protection

- 25-Bump, 0.4mm Pitch WLCSP Package

# Description

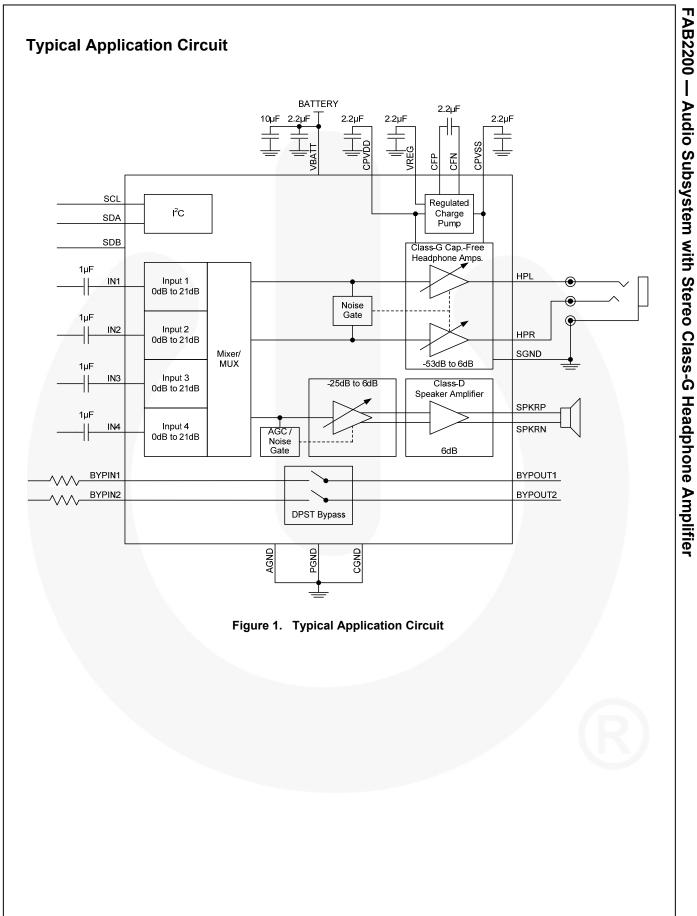

The FAB2200 combines a capacitor-free stereo headphone amplifier with a monolithic class-D speaker amplifier.

An integrated charge pump generates multiple supply rails for a ground-centered class-G headphone output. The charge pump is regulated for high Power Supply Rejection Ratio (PSRR).

The filterless class-D amplifier can be connected directly to a speaker without external filters.

The programmable Automatic Gain Control (AGC) limits maximum speaker output levels to protect speakers without introducing distortion. It can also dynamically limit clipping as the battery voltage falls.

The noise gate can automatically mute the speaker or headphone amplifiers to reduce noise when input signals are low.

## Applications

- Cellular Handsets

- Notebook Computers

- Tablet PCs

| Ordering I | nformation |

|------------|------------|

|------------|------------|

| Part Number Operating Temperature Range |             | Package                                                         | Packing Method               |  |

|-----------------------------------------|-------------|-----------------------------------------------------------------|------------------------------|--|

| FAB2200UCX                              | -4010 +85 0 | 25-Bump, 0.4mm Pitch, Wafer-Level<br>Chip-Scale Package (WLCSP) | 3000 Units on<br>Tape & Reel |  |

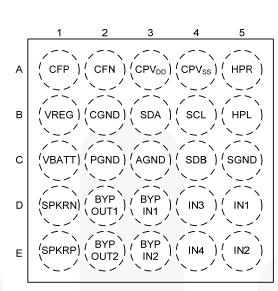

# **Pin Definitions**

**Pin Configuration**

| WLCSP | Name              | Description                                                               | Туре         |

|-------|-------------------|---------------------------------------------------------------------------|--------------|

| C1    | VBATT             | Power supply for speaker amplifier                                        | Power        |

| B2    | PGND              | Charge pump ground                                                        | Power        |

| C2    | PGND              | Power ground                                                              | Power        |

| C3    | AGND              | Analog ground                                                             | Power        |

| B1    | VREG              | Charge pump regulator – do not connect to an external power supply        | Power        |

| A3    |                   | Charge pump output – positive power supply for headphone amplifier        | Power        |

| A4    | CPV <sub>SS</sub> | Charge pump output – negative mirror of CPV <sub>DD</sub>                 | Power        |

| A1    | CFP               | Charge pump flying capacitor positive terminal                            | Power        |

| A2    | CFN               | Charge pump flying capacitor negative terminal                            | Power        |

| D5    | IN1               | Line level audio input                                                    | Input        |

| E5    | IN2               | Line level audio input                                                    | Input        |

| D4    | IN3               | Line level audio input                                                    | Input        |

| E4    | IN4               | Line level audio input                                                    | Input        |

| B5    | HPL               | Left headphone output                                                     | Output       |

| A5    | HPR               | Right headphone output                                                    | Output       |

| C5    | SGND              | Sense ground – connect to AGND close to shield terminal of headphone jack | Input        |

| E1    | SPKRP             | Positive speaker output                                                   | Output       |

| D1    | SPKRN             | Negative speaker output                                                   | Output       |

| D3    | BYPIN1            | Analog bypass switch input                                                | Input        |

| E3    | BYPIN2            | Analog bypass switch input                                                | Input        |

| D2    | BYPOUT1           | Analog bypass switch output                                               | Output       |

| E2    | BYPOUT2           | Analog bypass switch output                                               | Output       |

| C4    | SDB               | Shutdown control                                                          | Input        |

| B4    | SCL               | I <sup>2</sup> C clock input                                              | Input        |

| B3    | SDA               | I <sup>2</sup> C data I/O                                                 | Bi-direction |

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The Absolute Maximum Ratings are stress ratings only. All voltages are referenced to GND.

| Symbol            | Parameter                                              | Min.                   | Max.                   | Unit |

|-------------------|--------------------------------------------------------|------------------------|------------------------|------|

| VBATT             | Voltage on VBATT Pin                                   | -0.3                   | 6.0                    | V    |

| V <sub>IN</sub>   | Voltage on IN1, IN2, IN3, IN4, HPL, HPR Pins           | CPV <sub>SS</sub> -0.3 | CPV <sub>DD</sub> +0.3 | V    |

| V <sub>SGND</sub> | Voltage on SGND Pin                                    | -0.3                   | 0.3                    | V    |

| Vs                | Voltage on SDA, SCL, SDB Pins                          | -0.3                   | V <sub>BATT</sub> +0.3 | V    |

| V <sub>SP</sub>   | Voltage on SPKRP, SPKRN Pins                           | -0.3                   | V <sub>BATT</sub> +0.3 | V    |

| V <sub>BYP</sub>  | Voltage on BYPIN1, BYPIN2, BYPOUT1, BYPOUT2 Pins       | -0.3                   | V <sub>BATT</sub> +0.3 | V    |

|                   | Duration of SPKRP, SPKRN Short Circuit to GND or VBATT |                        | Continuous             |      |

|                   | Duration of Short Circuit Between SPKRP and SPKRN      |                        | Continuous             |      |

|                   | Duration of HPL, HPR Short Circuit to GND              |                        | Continuous             |      |

# **Reliability Information**

| Symbol           | Parameter                                                             | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------------------------------------|------|------|------|------|

| TJ               | Junction Temperature                                                  |      |      | +150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                             | -65  |      | +150 | °C   |

| TL               | Peak Reflow Temperature                                               |      |      | +300 | °C   |

| θ <sub>JA</sub>  | Thermal Resistance, JEDEC Standard, Multilayer Test Boards, Still Air |      | 60   |      | °C/W |

| TSD              | Thermal Shutdown Threshold                                            |      | +150 |      | °C   |

| T <sub>HYS</sub> | Thermal Shutdown Hysteresis                                           |      | +35  |      | °C   |

# **ESD** Protection

| Symbol Parameter |                                                                                                                                                                                                                                      | Condition | Min. | Unit |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|

| HBM              | HBM Human Body Model (HBM)<br>HBM HUMAN HIGH HIGH HIGH HIGH HIGH HIGH HIGH HIG |           | 3    | kV   |

| CDM              | M Charged Device Model (CDM) JESD22-C101-C Level III,<br>IEC61340-3-3 Level C4,<br>ESD-STM5.3.1-1999 Level C4                                                                                                                        |           | 2    | kV   |

#### Notes:

1. Device-use-level ESD tests are conducted at the connector pins.

External ESD suppressor ASIP protects the amplifier outputs. Suppressor is between amplifier and connector; 15Ω serial resistance + 5nF capacitor and Zener diodes (14V breakdown voltage) connected to the ground. In addition, there is a ferrite bead in series between the suppressor and the connector.

3. The air discharge test can be ignored if the contact discharge test range is increased to the same voltages as air discharge (contact discharge is more stable and repeatable test than air discharge).

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol            |                             |      | Max. | Unit |

|-------------------|-----------------------------|------|------|------|

| T <sub>A</sub>    | Operating Temperature Range | -40  | +85  | °C   |

| V <sub>BATT</sub> | Supply Voltage Range        | 2.80 | 5.25 | V    |

## **Electrical Characteristics**

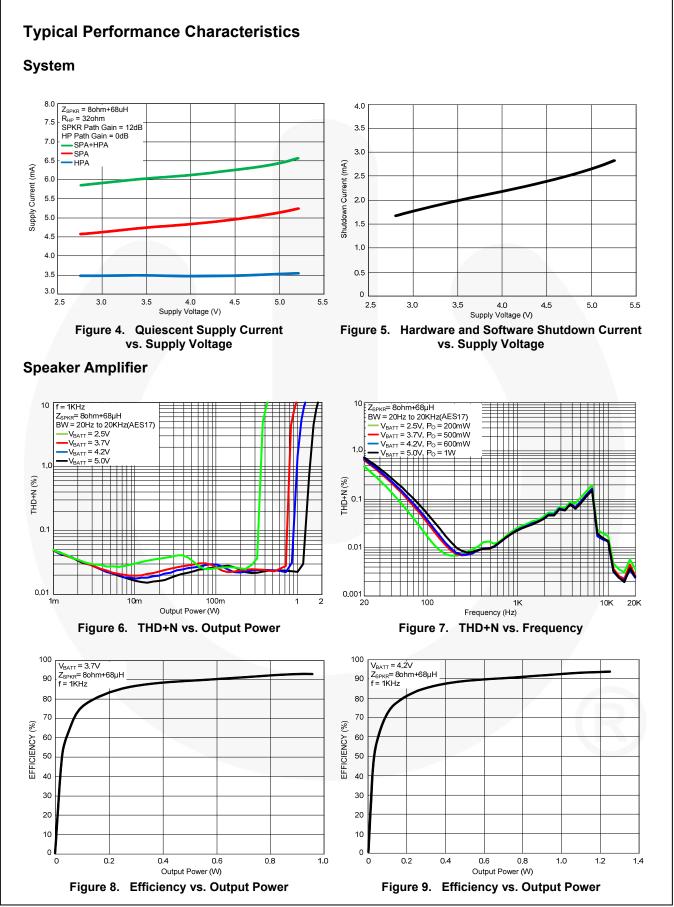

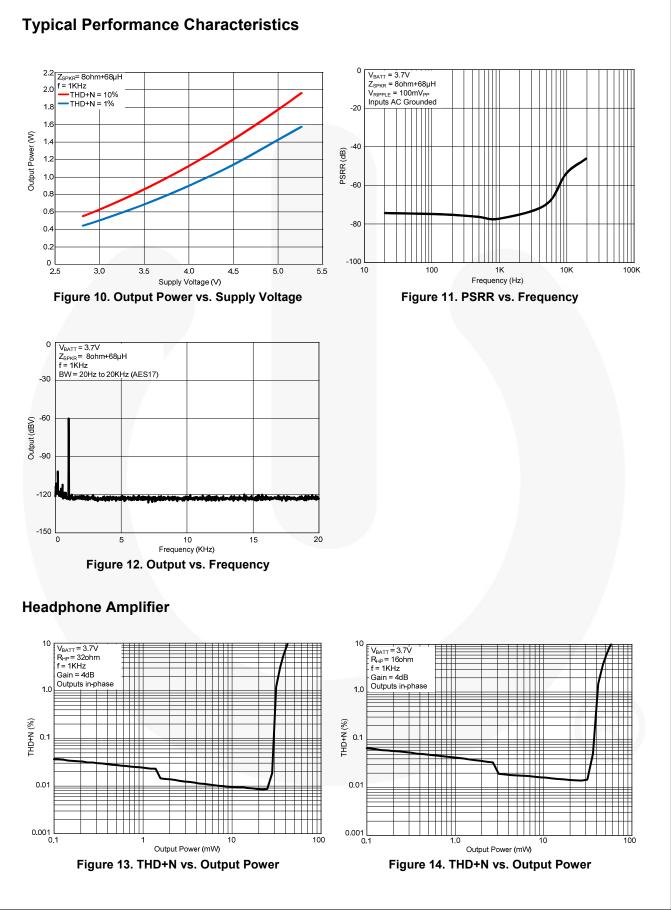

Unless otherwise noted: HPA uses stereo single-ended inputs, SPA uses differential input, unused inputs AC are grounded,  $f_{IN}$  = 1KHz, AGC off, PGAINxx = 0dB, HPxVOL = 0dB, PRESENTGAIN = 6dB, ERC = 1, SSMT = 000, SHDNB = 1, SDB = 1.8V, SDA and SCL pull-up voltage = 1.8V,  $Z_{SPK}$  = 8 $\Omega$ +68 $\mu$ H,  $R_{HP}$  = 32 $\Omega$ , speaker amplifier and headphone amplifier on. Typical values are at  $V_{BATT}$  = 3.7V,  $T_A$  = 25°C. Minimum and maximum values are at  $V_{BATT}$  = 2.8V to 5.25V,  $T_A$  = -40°C to 85°C.

| Symbol           | Parameter                                                  | Conditio                                                                                                                 | ons                                          | Min. | Тур.  | Max. | Unit               |  |

|------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|-------|------|--------------------|--|

|                  |                                                            | Headphone Amplifiers<br>Speaker Amplifier Dis<br>DIFFIN43=1                                                              |                                              |      | 3.5   |      |                    |  |

| I <sub>DD</sub>  | Quiescent Supply Current<br>(Z <sub>SPK</sub> = Open)      | Headphone Amplifiers<br>Speaker Amplifier Ena<br>DIFFIN21=1                                                              |                                              |      | 4.7   |      | mA                 |  |

|                  |                                                            | Headphone and Spea<br>Enabled                                                                                            | aker Amplifiers                              |      | 6.2   |      |                    |  |

|                  | Shutdown Current                                           | SHDNB = 0, SDB = 1                                                                                                       | .8V                                          |      | 2.2   |      |                    |  |

| I <sub>SD</sub>  | Shutdown Current                                           | SHDNB = 1, SDB = G                                                                                                       | ND                                           |      | 2.2   |      | μA                 |  |

| t <sub>on</sub>  | Turn-On Time                                               | Time from Shutdown to Full Speaker<br>and Headphone Operation, ZCD and<br>Ramps Disabled                                 |                                              |      | 1.25  |      | ms                 |  |

| Р                | Input Desistance                                           | PGAINxx = 0dB                                                                                                            |                                              |      | 21.0  |      | ΚΩ                 |  |

| R <sub>IN</sub>  | Input Resistance                                           | PGAINxx = 12dB                                                                                                           |                                              |      | 8.5   |      | 1/77               |  |

|                  | Maximum Input Signal Swing                                 | PGAINxx = 0dB                                                                                                            |                                              |      | 2.300 |      |                    |  |

|                  | (V <sub>BATT</sub> = 2.8V to 5.25V,<br>Single-Ended Input) | PGAINxx = 12dB                                                                                                           |                                              |      | 0.575 |      | V <sub>pk-pk</sub> |  |

| Analog By        | pass Switch                                                |                                                                                                                          |                                              |      |       |      |                    |  |

| R <sub>ON</sub>  | On Resistance                                              | $I_{BYPOUTx} = 20mA,$<br>BYPx = 0V and<br>V <sub>BATT</sub> , BYPEN = 1                                                  | T <sub>A</sub> = 25°C                        |      |       | 1    | Ω                  |  |

| THD              | Total Harmonic Distortion                                  | V <sub>DIF</sub> = 2V <sub>PP</sub> , V <sub>CM</sub> =<br>V <sub>BATT</sub> /2, f = 1kHz,<br>BYPEN = 1,                 | Series<br>Resistance is<br>10Ω per<br>Switch |      | 0.05  | 0.25 | %                  |  |

|                  |                                                            | Load = 8Ω                                                                                                                | No Series<br>Resistors                       |      | 0.10  |      |                    |  |

| I <sub>OFF</sub> | Off Isolation                                              | BYPEN = 0, 10KHz $1V_{RMS}$ Sine<br>Wave Applied Across BYPOUT1 and<br>BYPOUT2, BYPIN1 and BYPIN2 to<br>GND = $50\Omega$ |                                              |      | 94    |      | dB                 |  |

Continued on the following page...

www.fairchildsemi.com

# Electrical Characteristics (Continued)

Unless otherwise noted: HPA uses stereo single-ended inputs, SPA uses differential input, unused inputs AC are grounded,  $f_{IN}$  = 1KHz, AGC off, PGAINxx = 0dB, HPxVOL = 0dB, PRESENTGAIN = 6dB, ERC = 1, SSMT = 000, SHDNB = 1, SDB = 1.8V, SDA and SCL pull-up voltage = 1.8V,  $Z_{SPK}$  = 8 $\Omega$ +68µH,  $R_{HP}$  = 32 $\Omega$ , speaker amplifier and headphone amplifier on. Typical values are at  $V_{BATT}$  = 3.7V,  $T_A$  = 25°C. Minimum and maximum values are at  $V_{BATT}$  = 2.80V to 5.25V,  $T_A$  = -40°C to 85°C.

| Symbol           | Parameter                               | Conditio                                                                           | ons                                      | Min. | Тур.  | Max.  | Unit             |

|------------------|-----------------------------------------|------------------------------------------------------------------------------------|------------------------------------------|------|-------|-------|------------------|

| Speaker A        | mplifier                                |                                                                                    |                                          |      | 1     | 1     |                  |

|                  |                                         | PRESENTGAIN = Mute                                                                 |                                          |      | ±0.5  |       |                  |

| Vos              | Output Offset Voltage                   | PRESENTGAIN = 6dB                                                                  |                                          |      | ±2.5  |       | mV               |

|                  |                                         | Peak Voltage,                                                                      | Into Shutdown                            |      | -70   |       |                  |

| K <sub>CP</sub>  | Click-and-Pop Level                     | A-Weighted,<br>32 Samples per Second,<br>PRESENTGAIN = Mute,<br>Inputs AC Grounded | Out of Shutdown                          |      | -70   |       | dB∨              |

|                  |                                         |                                                                                    | V <sub>BATT</sub> = 2.8V to<br>5.25V     |      | 74    |       |                  |

| PSRR             | Power-Supply Rejection<br>Ratio         | Inputs AC Grounded                                                                 | f = 217Hz,<br>100mV <sub>PP</sub> Ripple |      | 77    |       | dB               |

|                  |                                         |                                                                                    | f = 1kHz,<br>100mV <sub>PP</sub> Ripple  |      | 75    |       |                  |

|                  |                                         | THD+N < 1%, ERC Disat<br>V <sub>BATT</sub> = 4.2V                                  | oled, SSMT = 100,                        |      | 970   |       |                  |

|                  |                                         | THD+N < 10%, ERC Disa<br>100, V <sub>BATT</sub> = 4.2V                             | abled, SSMT =                            |      | 1200  |       |                  |

| P <sub>OUT</sub> | Output Power                            | THD+N < 10%, ERC Disabled,<br>SSMT = 100, V <sub>BATT</sub> = 3.7V                 |                                          |      | 930   |       | mW               |

|                  |                                         | THD+N < 10%, ERC Enabled, SSMT = 000, $V_{BATT} = 3.7V$                            |                                          |      | 945   |       |                  |

|                  |                                         | THD+N < 1%, ERC                                                                    | V <sub>BATT</sub> = 4.2V                 | 930  | 975   |       |                  |

|                  |                                         | Enabled, SSMT = 000                                                                | V <sub>BATT</sub> = 3.7V                 |      | 750   | )     | 1                |

| THD+N            | Total Harmonic<br>Distortion Plus Noise | P <sub>OUT</sub> = 350mW                                                           |                                          |      | 0.030 | 0.075 | %                |

|                  |                                         | A-Weighted, $P_{OUT} =$                                                            | DIFFINxx = 0<br>(Single-Ended)           |      | 97    |       |                  |

| SNR              | Signal to Naise Patio                   | 720mŴ, Headphone<br>Amplifiers Off                                                 | DIFFINxx = 1<br>(Differential)           | 90   | 97    |       | dD               |

| SINK             | Signal-to-Noise Ratio                   | A-Weighted, P <sub>OUT</sub> = 720mW, Headphone                                    | DIFFINxx = 0<br>(Single-Ended)           |      | 97    |       | dB               |

|                  |                                         | Amplifiers On                                                                      | DIFFINxx = 1<br>(Differential)           |      | 97    |       |                  |

| Vn               | Output Noise                            | A-Weighted, Headphone Amps Off,<br>DIFFINxx = 0, Inputs AC Grounded                |                                          |      | 32    |       | μV <sub>RM</sub> |

|                  | Output Frequency                        | Spread Spectrum, SSMT                                                              | = 000                                    |      | 330   |       | KHz              |

|                  |                                         | Fixed Frequency, SSMT                                                              | = 100                                    |      | 330   |       |                  |

| I <sub>OUT</sub> | Output Current Limit                    |                                                                                    |                                          |      | 1.3   |       | Α                |

|                  | Efficiency                              | P <sub>OUT</sub> = 720mW, f = 1kHz                                                 |                                          |      | 90    |       | %                |

|                  | Mute Attenuation                        |                                                                                    |                                          |      | 100   |       | dB               |

Continued on the following page...

## Electrical Characteristics (Continued)

Unless otherwise noted: HPA uses stereo single-ended inputs, SPA uses differential input, unused inputs AC are grounded,  $f_{IN}$  = 1KHz, AGC off, PGAINxx = 0dB, HPxVOL = 0dB, PRESENTGAIN = 6dB, ERC = 1, SSMT = 000, SHDNB = 1, SDB = 1.8V, SDA and SCL pull-up voltage = 1.8V,  $Z_{SPK}$  =  $8\Omega$ +68µH,  $R_{HP}$  =  $32\Omega$ , speaker amplifier and headphone amplifier on. Typical values are at  $V_{BATT}$  = 3.7V,  $T_A$  =  $25^{\circ}$ C. Minimum and maximum values are at  $V_{BATT}$  = 2.80V to 5.25V,  $T_A$  =  $-40^{\circ}$ C to  $85^{\circ}$ C.

| Symbol             | Parameter                           | Conditions                                                            | 5                                                          | Min.                                     | Тур.       | Max.  | Unit             |  |

|--------------------|-------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------|------------|-------|------------------|--|

| Headpho            | ne Amplifiers                       |                                                                       |                                                            |                                          |            |       |                  |  |

|                    |                                     | N4 and N2 On                                                          | IN1 and IN2 On,                                            | $P_{OUT} = 2x50\mu W$<br>into $32\Omega$ |            | 4.4   | 4.4              |  |

| I <sub>VBATT</sub> | Supply Current                      | IN3 and IN4 Off, DIFFIN43=1,<br>Speaker Amplifier Off                 | $P_{OUT} = 2x250\mu W$<br>into $32\Omega$                  |                                          | 5.8        |       | mA               |  |

|                    |                                     |                                                                       | $P_{OUT} = 2x500 \mu W$<br>into $32\Omega$                 |                                          | 6.8        |       |                  |  |

| Vos                | Output Offset Voltage               | HPxVOL = Mute                                                         |                                                            |                                          | ±0.15      |       | mV               |  |

| K <sub>CP</sub>    | Click-and-Pop Level                 | Peak Voltage, A-Weighted,<br>32 Samples per Second,<br>HPxVOL = Mute, | Into Shutdown<br>Out of Shutdown                           |                                          | -70<br>-70 | -     | dBV              |  |

|                    |                                     | Inputs AC Grounded                                                    |                                                            |                                          | -70        |       |                  |  |

|                    |                                     |                                                                       | V <sub>BATT</sub> = 2.8V to<br>5.25V                       |                                          | 95         |       |                  |  |

| PSRR               | Power-Supply Rejection<br>Ratio     | Inputs AC Grounded                                                    | f = 217Hz,<br>V <sub>RIPPLE</sub> =<br>200mV <sub>PP</sub> |                                          | 95         |       | dB               |  |

|                    |                                     |                                                                       | $f = 1KHz, V_{RIPPLE}$<br>= 200mV <sub>PP</sub>            |                                          | 95         |       |                  |  |

|                    | Output Power                        | THD+N < 1%                                                            | R <sub>HP</sub> = 16Ω                                      |                                          | 39         |       | mW               |  |

| P <sub>OUT</sub> C |                                     |                                                                       | $R_{HP} = 32\Omega$<br>HPxV <sub>OL</sub> = 4dB            | 27                                       | 31         |       |                  |  |

|                    |                                     | THD+N < 10%                                                           | $R_{HP} = 32\Omega$<br>HPxV <sub>OL</sub> = 6dB            |                                          | 41         |       |                  |  |

| THD+N              | Total Harmonic                      | $R_{HP}$ = 32 $\Omega$ , $P_{OUT}$ = 20mW                             |                                                            |                                          | 0.010      | 0.075 | %                |  |

|                    | Distortion Plus Noise               | $R_{HP}$ = 16 $\Omega$ , $P_{OUT}$ = 10mW                             |                                                            |                                          | 0.020      |       | 70               |  |

|                    |                                     | A-Weighted, P <sub>OUT</sub> = 32mW,<br>Speaker Amplifier Off         | DIFFINxx = 0<br>(Single-Ended)                             | 95                                       | 100        |       |                  |  |

| SNR                | Signal-to-Noise Ratio               | HPxVOL = 4dB                                                          | DIFFINxx = 1<br>(Differential)                             |                                          | 100        |       | dB               |  |

| UNIX               | Signal-to-Noise Ratio               | A-Weighted, P <sub>OUT</sub> = 32mW,<br>Speaker Amplifier On          | DIFFINxx = 0<br>(Single-Ended)                             |                                          | 100        |       | uD               |  |

|                    |                                     | HPxVOL = 4dB                                                          | DIFFINxx = 1<br>(Differential)                             |                                          | 103        |       |                  |  |

|                    | Output Noise                        | A-Weighted, Speaker Amplifier                                         | Off, DIFFINxx = 0                                          |                                          | 6.5        |       | μV <sub>RM</sub> |  |

| CL                 | Capacitive Drive                    |                                                                       |                                                            |                                          | 100        |       | pF               |  |

| X <sub>TALK</sub>  | Crosstalk                           | HPL to HPR, HPR to HPL, Po                                            | = 15mW                                                     |                                          | -85        |       | dB               |  |

| f <sub>P</sub>     | Charge-Pump Frequency               | /                                                                     |                                                            |                                          | 1.3        |       | MHz              |  |

| Av                 | Headphone Gain<br>Accuracy          | Across All Gain Stages                                                |                                                            |                                          | ±0.4       |       | dB               |  |

|                    | Channel-to-Channel<br>Gain Tracking | HPL to HPR, HPxVOL = 0dB                                              |                                                            |                                          | ±0.3       |       | %                |  |

|                    | Channel-to-Channel<br>Gain Tracking | HPL to HPR Across Entire Pre<br>Volume Range                          | -Amplifier and                                             |                                          | ±1         |       | %                |  |

|                    | Mute Attenuation                    | •                                                                     |                                                            |                                          | 100        |       | dB               |  |

# I<sup>2</sup>C DC Electrical Characteristics

Unless otherwise noted,  $V_{BATT}$  = 2.80V to 5.25V and  $T_A$  = -40°C to 85°C.

| Symbol          | Deremeter                | Conditions                                            | Fast Mode (400kHz) |      |      |

|-----------------|--------------------------|-------------------------------------------------------|--------------------|------|------|

|                 | Parameter                | Conditions                                            | Min.               | Max. | Unit |

| VIL             | Low-Level Input Voltage  | V <sub>BATT</sub> 2.80V to 5.25V                      | -0.3               | 0.6  | V    |

| V <sub>IH</sub> | High-Level Input Voltage | V <sub>BATT</sub> 2.80V to 5.25V                      | 1.3                |      | V    |

| V <sub>OL</sub> | Low-level Output Voltage | at 3mA Sink Current<br>(Open-Drain or Open-Collector) | 0                  | 0.4  | V    |

| I <sub>IH</sub> | High-Level Input Current | Each I/O Pin, Input Voltage = V <sub>BATT</sub>       | -1                 | 1    | μA   |

| IIL             | Low-Level Input Current  | Each I/O Pin, Input Voltage = 0V                      | -1                 | 1    | μA   |

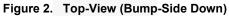

# I<sup>2</sup>C AC Electrical Characteristics

Unless otherwise noted,  $V_{BATT}$  = 2.80V to 5.25V and  $T_A$  = -40°C to 85°C.

| Ourseland           | Demonster                                                         | Fa       | Fast Mode |      |  |  |

|---------------------|-------------------------------------------------------------------|----------|-----------|------|--|--|

| Symbol              | Parameter                                                         | Min.     | Max.      | Unit |  |  |

| f <sub>SCL</sub>    | SCL Clock Frequency                                               | 0        | 400       | kHz  |  |  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6      |           | μs   |  |  |

| t <sub>LOW</sub>    | LOW Period of SCL Clock                                           | 1.3      |           | μs   |  |  |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock                                          | 0.6      |           | μs   |  |  |

| t <sub>su;sta</sub> | Set-up Time for Repeated START Condition                          | 0.6      |           | μs   |  |  |

| $t_{HD;DAT}$        | Data Hold Time                                                    | 0        | 0.9       | μs   |  |  |

| t <sub>su;dat</sub> | Data Set-up Time <sup>(4)</sup>                                   | 100      |           | ns   |  |  |

| tr                  | Rise Time of SDA and SCL Signals <sup>(5)</sup>                   | 20+0.1Cb | 300       | ns   |  |  |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals <sup>(5)</sup>                   | 20+0.1Cb | 300       | ns   |  |  |

| t <sub>su;sто</sub> | Set-up Time for STOP Condition                                    | 0.6      |           | μs   |  |  |

| t <sub>BUF</sub>    | Bus Free Time between STOP and START Conditions                   | 1.3      |           | μs   |  |  |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0        | 50        | ns   |  |  |

Notes:

- 4. A fast-mode I<sup>2</sup>C-Bus<sup>®</sup> device can be used in a standard-mode system, but the requirement t<sub>SU;DAT</sub> ≥ 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>r\_max</sub> + t<sub>SU;DAT</sub> = 1000 + 250 = 1250ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

- C<sub>b</sub> equals the total capacitance of one bus line in pf. If mixed with high-speed mode devices, faster fall times are allowed according to the I<sup>2</sup>C specification.

FAB2200 — Audio Subsystem with Stereo Class-G Headphone Amplifier

# **Functional Description**

#### Shutdown Mode

When SHDNB bit is set to 0 or the SDB pin is grounded, the FAB2200 enters low-power Shutdown Mode.

While SHDNB=0 and SDB is HIGH, I<sup>2</sup>C communication is available. I<sup>2</sup>C values are preserved. Values are not reset on exiting Shutdown Mode.

If the SDB pin is grounded,  $I^2C$  communication is unavailable.  $I^2C$  values are not preserved. Values are reset to default values after SDB goes HIGH.

#### Inputs During Shutdown

To achieve low supply current during shutdown, all inputs must be at DC levels (except the BYPASS pins). Audio inputs must be AC grounded.  $V_{BATT}$  must be within recommended operating conditions. I<sup>2</sup>C pins must be grounded or pulled HIGH with no toggling. If AC is presented to the inputs during shutdown, standby current may increase slightly, but there are no other negative effects.

#### **Thermal Shutdown**

If the junction temperature of the device exceeds the thermal shutdown threshold (see *Electrical Characteristics table*), the device protects itself by shutting down. The device remains shut down until the junction temperature falls below the thermal shutdown hysteresis.

The  $I^2C$  port remains functional and the OVRTEMP bit is set to O. This bit remains set until it is read. If the device is still in thermal shutdown when the bit is read, it remains set to 1. Otherwise, the bit is cleared to 0.

#### **Over-Current Shutdown**

If the output current limit of either amplifier is exceeded (*see the Electrical Characteristics table*), the amplifier in question shuts down for approximately one second. After one second, the amplifier is re-enabled. If the amplifier output current exceeds the limit again, the cycle repeats.

During current-limit shutdown, the  $I^2C$  port remains functional. If the current-limit shutdown was caused by the speaker amplifier, the OVRCURSP bit is set to 1. This bit remains set until it is read. If the speaker amplifier is still in current-limit shutdown when the bit is read, it remains set to 1. Otherwise, the bit is cleared to 0.

#### Signal Path

The input channels have a pre-amplifier stage that can be set from 0dB to 21dB of gain. The headphone amplifiers have separate volume controls that range from -53dB to 6dB. The speaker amplifier has a volume control that ranges from -25dB to 6dB. In addition, the speaker amplifier has a fixed gain of 6dB.

A variety of combinations of these signals can be routed to the headphone amplifiers or the speaker amplifier (*see Table 1*). For example, to connect the left headphone amplifier channel to IN3 and IN1, set the SELHPL3 and SELHPL1 bits to 1. SELHPL4 and SELHPL2 should be set to 0.

The DIFFIN43 and DIFFIN21 bits configure the inputs as differential pairs. When configured as differential, the even-numbered selection bit should be 1 and the oddnumbered selection bit should be 0. For example, if channels 4 and 3 are a differential pair that should be connected to the speaker amplifier, DIFFIN43 and SELSPA4 should be set to 1. SELSPA3, SELSPA2, and SELSPA1 should be set to 0.

Amplifier channels that have no inputs selected should be muted (HPxVOL = 00000 or STARTGAIN = 000000). If an amplifier channel has no input selection bits set to 1, the amplifier channel is turned off. When the speaker amplifier is turned off, the SPKRP and SPKRN outputs stop switching.

Unused audio input pins must be AC grounded.

An integrated Dual-Pole Single-Throw (DPST) analog bypass switch can be used to route system audio signals. For example, baseband audio can be routed to the speaker by connecting the BYPOUTx pins to the SPKRx pins. Baseband audio outputs would then be connected to the BYPINx pins through optional external resistors if the baseband device expects a higher impedance than the existing speaker.

Gain for the headphone amplifier signal path is defined by PGAINxx + HPxVOL.

Gain for the speaker amplifier signal path is defined by PGAINxx + PRESENTGAIN + 6dB.

Internal signal amplitude should not exceed  $2.3V_{PP}$ . Extra caution should be taken when mixing signals. For example, if IN1 is mixed with IN3, the maximum peak to peak amplitude of IN1 plus the maximum peak to peak amplitude of IN3 should not exceed  $2.3V_{PP}$ .

| DIFFIN43 | DIFFIN21 | SELxxx4 | SELxxx3 | SELxxx2 | SELxxx1 | xxx Amplifier Input       |

|----------|----------|---------|---------|---------|---------|---------------------------|

| Х        | Х        | 0       | 0       | 0       | 0       | xxx Amplifier Channel Off |

| 0        | 0        | 0       | 0       | 0       | 1       | IN1                       |

| 0        | 0        | 0       | 0       | 1       | 0       | IN2                       |

| 0        | 0        | 0       | 0       | 1       | 1       | IN2 + IN1                 |

| 0        | 0        | 0       | 1       | 0       | 0       | IN3                       |

| 0        | 0        | 0       | 1       | 0       | 1       | IN3 + IN1                 |

| 0        | 0        | 0       | 1       | 1       | 0       | IN3 + IN2                 |

| 0        | 0        | 0       | 1       | 1       | 1       | IN3 + IN2 + IN1           |

| 0        | 0        | 1       | 0       | 0       | 0       | IN4                       |

| 0        | 0        | 1       | 0       | 0       | 1       | IN4 + IN1                 |

| 0        | 0        | 1       | 0       | 1       | 0       | IN4 + IN2                 |

| 0        | 0        | 1       | 0       | 1       | 1       | IN4 + IN2 + IN1           |

| 0        | 0        | 1       | 1       | 0       | 0       | IN4 + IN3                 |

| 0        | 0        | 1       | 1       | 0       | 1       | IN4 + IN3 + IN1           |

| 0        | 0        | 1       | 1       | 1       | 0       | IN4 + IN3 + IN2           |

| 0        | 0        | 1       | 1       | 1       | 1       | IN4 + IN3 + IN2 + IN1     |

| 0        | 1        | 0       | 0       | 0       | 0       | xxx Amplifier Channel Off |

| 0        | 1        | 0       | 0       | 0       | 1       | Not Supported             |

| 0        | 1        | 0       | 0       | 1       | 0       | IN2 - IN1                 |

| 0        | 1        | 0       | 0       | 1       | 1       |                           |

|          |          |         | -       |         |         | Not Supported<br>IN3      |

| 0        | 1        | 0       | 1       | 0       | 0       |                           |

| 0        | 1        | 0       | 1       | 0       | 1       | Not Supported             |

| 0        | 1        | 0       | 1       | 1       | 0       | IN3 + (IN2 - IN1)         |

| 0        | 1        | 0       | 1       | 1       | 1       | Not Supported             |

| 0        | 1        | 1       | 0       | 0       | 0       | IN4                       |

| 0        | 1        | 1       | 0       | 0       | 1       | Not Supported             |

| 0        | 1        | 1       | 0       | 1       | 0       | IN4 + (IN2 - IN1)         |

| 0        | 1        | 1       | 0       | 1       | 1       | Not Supported             |

| 0        | 1        | 1       | 1       | 0       | 0       | IN4 + IN3                 |

| 0        | 1        | 1       | 1       | 0       | 1       | Not Supported             |

| 0        | 1        | 1       | 1       | 1       | 0       | IN4 + IN3 + (IN2 - IN1)   |

| 0        | 1        | 1       | 1       | 1       | 1       | Not Supported             |

| 1        | 0        | 0       | 0       | 0       | 0       | xxx Amplifier Channel Off |

| 1        | 0        | 0       | 0       | 0       | 1       | IN1                       |

| 1        | 0        | 0       | 0       | 1       | 0       | IN2                       |

| 1        | 0        | 0       | 0       | 1       | 1       | IN2 + IN1                 |

| 1        | 0        | 0       | 1       | 0       | 0       | Not Supported             |

| 1        | 0        | 0       | 1       | 0       | 1       | Not Supported             |

| 1        | 0        | 0       | 1       | 1       | 0       | Not Supported             |

| 1        | 0        | 0       | 1       | 1       | 1       | Not Supported             |

| 1        | 0        | 1       | 0       | 0       | 0       | IN4 - IN3                 |

| 1        | 0        | 1       | 0       | 0       | 1       | (IN4 - IN3) + IN1         |

|          |          |         | -       |         |         | (IN4 - IN3) + IN2         |

| 1        | 0        | 1       | 0       | 1       | 0       |                           |

| 1        | 0        | 1       | 0       |         | 1       | (IN4 - IN3) + IN2 + IN1   |

| 1        | 0        | 1       | 1       | 0       | 0       | Not Supported             |

| 1        | 0        | 1       | 1       | 0       | 1       | Not Supported             |

| 1        | 0        | 1       | 1       | 1       | 0       | Not Supported             |

| 1        | 0        | 1       | 1       | 1       | 1       | Not Supported             |

| 1        | 1        | 0       | 0       | 0       | 0       | xxx Amplifier Channel Off |

| 1        | 1        | 0       | 0       | 0       | 1       | Not Supported             |

| 1        | 1        | 0       | 0       | 1       | 0       | IN2 - IN1                 |

| 1        | 1        | 0       | 0       | 1       | 1       | Not Supported             |

| 1        | 1        | 0       | 1       | 0       | 0       | Not Supported             |

| 1        | 1        | 0       | 1       | 0       | 1       | Not Supported             |

| 1        | 1        | 0       | 1       | 1       | 0       | Not Supported             |

| 1        | 1        | 0       | 1       | 1       | 1       | Not Supported             |

| 1        | 1        | 1       | 0       | 0       | 0       | IN4 - IN3                 |

| 1        | 1        | 1       | 0       | 0       | 1       | Not Supported             |

| 1        | 1        | 1       | 0       | 1       | 0       | (IN4 - IN3) + (IN2 - IN1) |

| 1        | 1        | 1       | 0       | 1       | 1       | Not Supported             |

| 1        | 1        | 1       | 1       | 0       | 0       | Not Supported             |

| 1        | 1        | 1       | 1       | 0       | 0       |                           |

|          |          |         |         |         |         | Not Supported             |

| 1        | 1        | 1       | 1       | 1       | 0       | Not Supported             |

| 1        | 1        | 1       | 1       | 1       | 1       | Not Supported             |

# Class-G Headphone Amplifier with Capacitor Free Outputs

The FAB2200 includes a regulated charge pump that derives  $CPV_{DD}$  and  $CPV_{SS}$  (the headphone amplifier power supplies) from VBATT. When the headphone output amplitude is low, the  $CPV_{DD}$  is 1.3V and  $CPV_{SS}$  is -1.3V. When needed,  $CPV_{DD}$  and  $CPV_{SS}$  dynamically increase to 1.8V and -1.8V, respectively, to allow for higher output amplitudes. The combination of an efficient regulated charge pump and class-G operation allows low headphone amplifier power dissipation, resulting in longer battery run time.

The negative  $CPV_{SS}$  rail allows the headphone amplifier output to be centered at 0V and eliminates the need for output DC blocking capacitors.

The FAB2200 headphone outputs can be placed in High-Impedance Mode by setting the HIZx bits to 1 (*see Table 2*). This can be useful if the system's headphone jack is shared with other devices. For proper high-

impedance operation, the device must not be in Shutdown Mode. Voltages on HPL and HPR must not exceed  $\pm 1.8V$ .

# Table 2.Headphone Amplifier OutputImpedance, HIZx=1

| Output Impedance (Ω) | Frequency (KHz) |

|----------------------|-----------------|

| 11800                | 40              |

| 760                  | 6000            |

| 470                  | 13000           |

# Headphone Volume Control Ramp and Zero-Crossing Detection

The HPRAMP, HPRAMPSPEED, and HPZCD bits control the headphone amplifiers' volume controls when  $HPxV_{OL}$  is changed.

#### Table 3. Headphone Volume Change Behavior

| HPRAMP | HPZCD | Behavior When HPxVOL Changes                                                                                                                                                                                                                                           |  |  |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0      | 0     | Volume changes immediately.                                                                                                                                                                                                                                            |  |  |

| 0      | 1     | For each channel, wait until a zero crossing occurs in the input before changing volume. If a zero crossing does not occur within HPRAMPSPEED, volume is forced to the new setting.                                                                                    |  |  |

| 1      | 0     | Volume is ramped to the new setting at a rate of HPRAMPSPEED per step.                                                                                                                                                                                                 |  |  |

| 1      | 1     | Volume is changed by one step when a zero crossing occurs. If a zero crossing does not occur within HPRAMPSPEED, a step is forced. Only the first zero crossing within HPRAMPSPEED triggers a volume change – volume does not change again until the next HPRAMPSPEED. |  |  |

#### Table 4. Headphone Volume Change Timing

| HPRAMPSPEED[1:0] | Ramp and ZCD Time Between Steps (ms) |

|------------------|--------------------------------------|

| 00               | 0.25                                 |

| 01               | 2.00                                 |

| 10               | 16.00                                |

| 11               | 128.00                               |

# Programmable Headphone Amplifier Noise Gate

The headphone noise gate automatically mutes the headphone amplifier when its input amplitudes are low to reduce noise during inactivity. This function is not recommended for music playback, but is effective for speech. The amplitude is measured after input preamplifiers and before the headphone amplifier volume controls. The headphone noise gate threshold level is set by the HPNGTHRESH register. The amplitudes of both channels must be less than the noise gate threshold for a time determined by the HPNGTIME register. When the noise gate mutes the amplifier, the HPNGTRIP bit is set to 1.

If either channel's input amplitude goes above the headphone noise gate threshold, both amplifiers are unmuted and the HPNGTRIP bit is set to 0. The amplifiers are returned to the former HPxVOL values.

If either channel is in High-Impedance Mode (HIZx=1), all inputs to that headphone should be deselected (SELHPxx=0) so the noise gate ignores the HIZ channel.

If the HPNGZRA bit is set to 0, the headphone noise gate attack (mute) function occurs immediately rather than waiting for zero-crossing detection or ramping. If the HPNGZRA bit is set to 1, the headphone noise gate attack function obeys headphone zero-crossing detection and ramp settings.

If the HPNGZRR bit is set to 0, the headphone noise gate release (un-mute) function occurs immediately rather than waiting for zero-crossing detection or ramping. If the HPNGZRR bit is set to 1, the headphone noise gate release (un-mute) function obeys headphone zero crossing detection and ramp settings.

# Table 5. Headphone Noise Gate Threshold Voltage

| <u> </u>            |                                  |  |  |

|---------------------|----------------------------------|--|--|

| HPNGTHRESH<br>[2:0] | Noise Gate Threshold $(mV_{pk})$ |  |  |

| 000                 | Headphone Noise Gate Disabled    |  |  |

| 001                 | 2.8                              |  |  |

| 010                 | 5.7                              |  |  |

| 011                 | 11.3                             |  |  |

| 100                 | 22.6                             |  |  |

| 101                 | 45.3                             |  |  |

| 110                 | 90.5                             |  |  |

| 111                 | 181.0                            |  |  |

#### Table 7. Headphone Noise Gate Timing

| HPNGTIME [2:0] | Time (ms) |

|----------------|-----------|

| 000            | 10        |

| 001            | 20        |

| 010            | 40        |

| 011            | 80        |

| 100            | 160       |

| HPNGTIME [2:0] | Time (ms) |

|----------------|-----------|

| 101            | 320       |

| 110            | 640       |

| 111            | Reserved  |

Certain combinations of HPRAMP, HPZCD, HPNGZRA, and HPNGZRR are valid as shown in Table 8. Combinations not listed may produce unpredictable results (X = don't care).

| Table 8. | Valid Headphone Amplifier Ramp / |

|----------|----------------------------------|

| Zero Cro | ssing / Noise Gate Combinations  |

| HPRAMP | HPZCD | HPNGZRA | HPNGZRR |

|--------|-------|---------|---------|

| 0      | 0     | Х       | Х       |

| Х      | Х     | 1       | 1       |

| 1      | Х     | 1       | 0       |

#### **Class-D Speaker Amplifier**

The class-D amplifier achieves greater than 90% efficiency.

Programmable spread spectrum and edge rate control minimize electromagnetic interference (EMI). Rise and fall times are limited to 20ns per transition at all power levels.

# Programmable Automatic Gain Control (AGC)

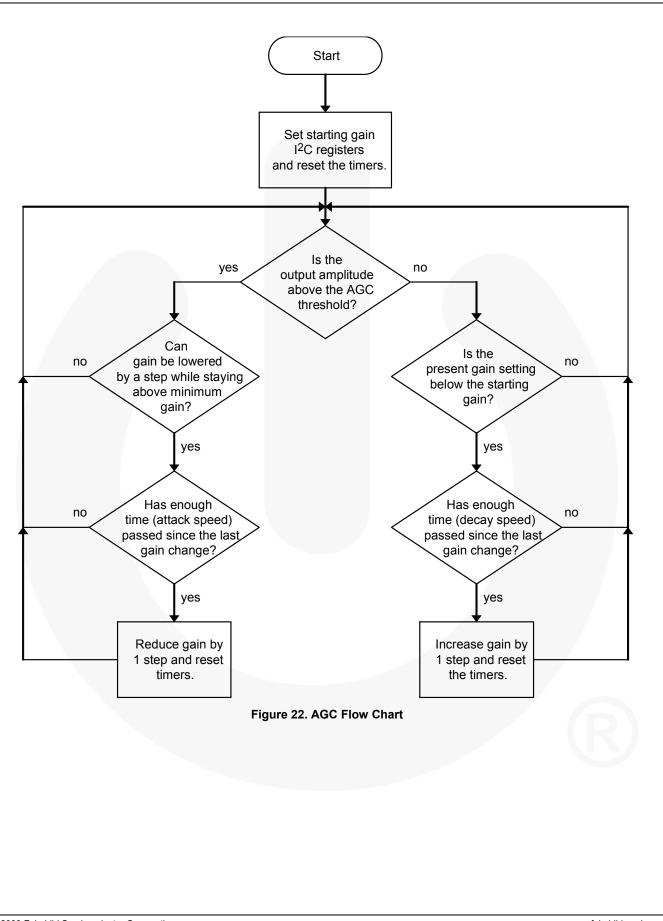

The speaker amplifier's AGC can be used to limit output amplitude and reduce clipping as supply voltage varies. The AGC allows high-volume settings while minimizing distortion and protecting the speaker element.

AGC works by comparing the threshold voltage against a proposed output amplitude (the signal's amplitude after all gain stages, before the PWM modulator). If the threshold is exceeded, gain is dynamically reduced until the output voltage level no longer exceeds the threshold or the minimum gain setting. When the output voltage level no longer exceeds the threshold, gain is slowly increased until either the output voltage level exceeds the threshold again or the starting gain is reached.

AGC settings should not be changed while the speaker amplifier is on. Before making changes to THMAX, THVBATT, AGCATTACK, AGCRELEASE, or AGCMIN; the speaker amplifier should be turned off by clearing all SELSPAn bits to 0 or clearing SHDNB to 0.

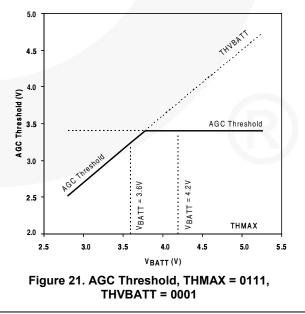

#### AGC Threshold

The AGC threshold can be thought of as a target for the maximum output amplitude. It is defined by the THMAX and THVBATT registers.

THMAX defines the maximum threshold value regardless of V<sub>BATT</sub> supply voltage. This is useful for protecting speakers from high amplitudes. Table 9 shows the THMAX threshold settings as well as the corresponding maximum RMS power (assuming a 1KHz sine wave into an  $8\Omega$  load).

| THMAX<br>[3:0] | Maximum<br>Output<br>Threshold<br>(V <sub>pk</sub> ) | Maximum Power with<br>Sine Wave and 8Ω<br>Load (mW) | THMAX<br>[3:0] | Maximum<br>Output<br>Threshold<br>(V <sub>pk</sub> ) | Maximum Power<br>with Sine Wave and<br>8Ω Load (mW) |

|----------------|------------------------------------------------------|-----------------------------------------------------|----------------|------------------------------------------------------|-----------------------------------------------------|

| 0000           | THMAX                                                | Threshold Disabled                                  | 1000           | 3.6                                                  | 810.0                                               |

| 0001           | 2.2                                                  | 302.5                                               | 1001           | 3.8                                                  | 902.5                                               |

| 0010           | 2.4                                                  | 360.0                                               | 1010           | 4.0                                                  | 1000.0                                              |

| 0011           | 2.6                                                  | 422.5                                               | 1011           | 4.2                                                  | 1102.5                                              |

| 0100           | 2.8                                                  | 490.0                                               | 1100           | 4.4                                                  | 1210.0                                              |

| 0101           | 3.0                                                  | 562.5                                               | 1101           | 4.6                                                  | 1322.5                                              |

| 0110           | 3.2                                                  | 640.0                                               | 1110           | 4.8                                                  | 1440.0                                              |

| 0111           | 3.4                                                  | 722.5                                               | 1111           | 5.0                                                  | 1562.5                                              |

THVBATT limits the amount of clipping allowed by the AGC. As  $V_{\text{BATT}}$  falls, the maximum output amplitude falls. THVBATT defines the threshold as a fraction of the  $V_{\text{BATT}}$  supply voltage. When the fraction is less than 1,

the AGC attempts to adjust gain to prevent clipping. For values greater than 1, some clipping is allowed before the AGC reduces gain (*see Table 10*).

#### Table 10. THVBATT Threshold

| THVBATT [4:0] | V <sub>BATT</sub> Fraction<br>(V/V) | THD with 1KHz<br>Sine Wave (%)<br>(V <sub>BATT</sub> =3.7V,<br>8Ω Load) | THVBATT [4:0] | V <sub>BATT</sub> Fraction<br>(V/V) | THD with 1KHz<br>Sine Wave (%)<br>(V <sub>BATT</sub> =3.7V,<br>8Ω Load) |

|---------------|-------------------------------------|-------------------------------------------------------------------------|---------------|-------------------------------------|-------------------------------------------------------------------------|

| 0000          | THVBATT Thre                        | shold Disabled                                                          | 1000          | 1.25                                | 13.0                                                                    |

| 0001          | 0.90                                | 1.0                                                                     | 1001          | 1.30                                | 14.4                                                                    |

| 0010          | 0.95                                | 3.0                                                                     | 1010          | 1.35                                | 15.6                                                                    |

| 0011          | 1.00                                | 4.9                                                                     | 1011          | 1.40                                | 16.7                                                                    |

| 0100          | 1.05                                | 6.7                                                                     | 1100          | 1.45                                | 17.7                                                                    |

| 0101          | 1.10                                | 8.5                                                                     | 1101          | 1.50                                | 18.7                                                                    |

| 0110          | 1.15                                | 10.0                                                                    | 1110          | 1.55                                | 19.6                                                                    |

| 0111          | 1.20                                | 11.6                                                                    | 1111          | 1.60                                | 20.5                                                                    |

Ultimately, the AGC threshold is whichever voltage is lower between THVBATT and THMAX. For example, if THMAX = 0111, THVBATT = 0001, and V<sub>BATT</sub> = 4.2V, the AGC threshold is 3.4V as defined by THMAX. If V<sub>BATT</sub> falls to 3.6V, the AGC threshold falls to 3.24V as defined by THVBATT (*see Figure 21*). If THVBATT and THMAX are both set to 0, the AGC is disabled.

#### Starting Gain

Starting gain is the amount of speaker gain applied when the AGC is not active. It can also be thought of as maximum gain when the AGC is active. Starting gain is controlled by the STARTGAIN register (see Table 11).

| Gain Register [5:0] | Gain (dB) | Gain Register [5:0] | Gain (dB) |

|---------------------|-----------|---------------------|-----------|

| 000000              | Mute      | 100000              | -9.5      |

| 000001              | -25.0     | 100001              | -9.0      |

| 000010              | -24.5     | 100010              | -8.5      |

| 000011              | -24.0     | 100011              | -8.0      |

| 000100              | -23.5     | 100100              | -7.5      |

| 000101              | -23.0     | 100101              | -7.0      |

| 000110              | -22.5     | 100110              | -6.5      |

| 000111              | -22.0     | 100111              | -6.0      |

| 001000              | -21.5     | 101000              | -5.5      |

| 001001              | -21.0     | 101001              | -5.0      |

| 001010              | -20.5     | 101010              | -4.5      |

| 001011              | -20.0     | 101011              | -4.0      |

| 001100              | -19.5     | 101100              | -3.5      |

| 001101              | -19.0     | 101101              | -3.0      |

| 001110              | -18.5     | 101110              | -2.5      |

| 001111              | -18.0     | 101111              | -2.0      |

| 010000              | -17.5     | 110000              | -1.5      |

| 010001              | -17.0     | 110001              | -1.0      |

| 010010              | -16.5     | 110010              | -0.5      |

| 010011              | -16.0     | 110011              | 0         |

| 010100              | -15.5     | 110100              | 0.5       |

| 010101              | -15.0     | 110101              | 1.0       |

| 010110              | -14.5     | 110110              | 1.5       |

| 010111              | -14.0     | 110111              | 2.0       |

| 011000              | -13.5     | 111000              | 2.5       |

| 011001              | -13.0     | 111001              | 3.0       |

| 011010              | -12.5     | 111010              | 3.5       |

| 011011              | -12.0     | 111011              | 4.0       |

| 011100              | -11.5     | 111100              | 4.5       |

| 011101              | -11.0     | 111101              | 5.0       |

| 011110              | -10.5     | 111110              | 5.5       |

| 011111              | -10.0     | 111111              | 6.0       |

## Table 11.Speaker Gain Values

#### AGC Attack

AGC attack occurs when the AGC determines that, after applying present gain, the output signal amplitude would be too high and gain should be stepped down by 1dB. The AGC checks an approximation of the amplitude of the output signal that includes present gain, but excludes clipping that may occur in the final output stage. All of the following conditions must be true to trigger an AGC attack:

- The amplitude is above the AGC threshold, AND

- Present gain is above the minimum gain point, AND

- Attack speed is not exceeded.

The minimum gain is determined by the AGCMIN register. The rate of gain reduction is determined by the AGCATTACK register.

#### AGC Release

When the output signal is below the AGC threshold, gain is stepped up by 1dB. The rate of gain increase is determined by the AGCRELEASE registers. Gain is increased until it reaches the starting gain or an AGC attack is triggered again.

| AGCATTACK [2:0] | AGC Attack Speed (µs/Step) | AGCATTACK [2:0] | AGC Attack Speed (µs/Step |

|-----------------|----------------------------|-----------------|---------------------------|

| 000             | 12.5                       | 100             | 200                       |

| 001             | 25.0                       | 101             | 400                       |

| 010             | 50.0                       | 110             | 800                       |

| 011             | 100.0                      | 111             | 1600                      |

#### Table 12. AGC Attack Speed

#### Table 13. AGC Release Speed

| AGCRELEASE [2:0] | AGC Release Speed<br>(ms/Step) | AGCRELEASE [2:0] | AGC Release Speed<br>(ms/Step) |  |  |

|------------------|--------------------------------|------------------|--------------------------------|--|--|

| 000              | 12.5                           | 100              | 200                            |  |  |

| 001              | 25.0                           | 101              | 400                            |  |  |

| 010              | 50.0                           | 110              | 800                            |  |  |

| 011              | 100.0                          | 111              | 1600                           |  |  |

FAB2200 — Audio Subsystem with Stereo Class-G Headphone Amplifier

# FAB2200 — Audio Subsystem with Stereo Class-G Headphone Amplifier

## Programmable Speaker Amplifier Noise Gate

The speaker noise gate automatically mutes the speaker amplifier when its input amplitude is low to reduce noise during inactivity. This function is not recommended for music playback, but is effective for speech. The amplitude is measured after input pre-amplifiers, but before the speaker amplifier's volume control. The speaker noise gate's threshold level is set by the SPNGTHRESH register. The amplitude must be less than the speaker noise gate threshold for a time determined by the SPNGTIME register. When the speaker noise gate mutes the speaker amplifier, the SPNGTRIP bit is set to 1.

If the input amplitude goes above the speaker noise gate threshold, the speaker amplifier is un-muted and the SPNGTRIP bit is set to 0. If the AGC is not enabled, the speaker amplifier is returned to its former PRESENTGAIN value. If the AGC is enabled, AGCRELEASE speed determines the new PRESENTGAIN value.

| SPNGTHRESH [2:0] | Speaker Noise Gate Threshold (mVpk)           Speaker Noise Gate Disabled |  |  |  |

|------------------|---------------------------------------------------------------------------|--|--|--|

| 000              |                                                                           |  |  |  |

| 001              | 2.8                                                                       |  |  |  |

| 010              | 5.7                                                                       |  |  |  |

| 011              | 11.3                                                                      |  |  |  |

| 100              | 22.6                                                                      |  |  |  |

| 101              | 45.3                                                                      |  |  |  |

| 110              | 90.5                                                                      |  |  |  |

| 111              | 181.0                                                                     |  |  |  |

#### Table 14. Speaker Noise Gate Threshold Voltage

#### Table 15. Speaker Noise Gate Timing

| SPNGTIME [2:0] | Time (ms) |

|----------------|-----------|

| 000            | 10        |

| 001            | 20        |

| 010            | 40        |

| 011            | 80        |

| 100            | 160       |

| 101            | 320       |

| 110            | 640       |

| 111            | Reserved  |

## Speaker Amplifier Gain Ramp and Zero-Crossing Detection (ZCD)

The SPRAMP, SPRAMPSPEED, and SPZCD bits control the speed at which PRESENTGAIN is changed when STARTGAIN is changed.

| SPRAMP | SPZCD | Behavior When STARTGAIN Is Changed                                                                                                                                                                                                                                    |

|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0     | STARTGAIN changes immediately.                                                                                                                                                                                                                                        |

| 0      | 1     | Wait until a zero crossing occurs in the input before changing STARTGAIN. If a zero crossing does not occur within SPRAMPSPEED, STARTGAIN is forced to the new setting.                                                                                               |

| 1      | 0     | STARTGAIN is ramped to the new setting at a rate of SPRAMPSPEED per step.                                                                                                                                                                                             |

| 1      | 1     | STARTGAIN is changed by one step when a zero crossing occurs. If a zero crossing does not occur within SPRAMPSPEED, a step is forced. Only the first zero crossing within SPRAMPSPEED triggers a gain change – gain does not change again until the next SPRAMPSPEED. |

#### Table 16. Speaker Gain Change Behavior

#### Table 17. Speaker Gain Change Timing

| SPRAMPSPEED[1:0] | Ramp and ZCD Time Between Steps (ms) |  |  |  |

|------------------|--------------------------------------|--|--|--|

| 00               | 0.25                                 |  |  |  |

| 01               | 2.00                                 |  |  |  |

| 10               | 16.00                                |  |  |  |

| 11               | 128.00                               |  |  |  |

SPRAMP, SPRAMPSPEED, and SPZCD have no effect on AGC and noise gate timing. AGC and noise gate timing have no effect on speaker amplifier gain ramp and zero-crossing detection. In the event of a conflict between these systems, PRESENTGAIN chooses the lowest gain setting. For example, SPRAMP is enabled with a slow SPRAMPSPEED and a fast AGCATTACK. The user changes STARTGAIN from 111111 to 000001. As the ramp function begins to ramp PRESENTGAIN down slowly (as defined by SPRAMPSPEED), a loud sound surpasses the AGC threshold. This forces PRESENTGAIN to react quickly (as defined by AGCATTACK). If the sound's amplitude falls below the AGC threshold before PRESENTGAIN reaches 000001, the quick gain reduction halts and the slow gain reduction resumes.

Valid combinations of SPRAMP, SPZCD, SPNGZRA, and SPNGZRR are shown in Table 18. Combinations not listed may produce unpredictable results.

| Table 18. | Valid Speaker | · Amplifier Ramp | / Zero Crossing | / Noise Gate Combinations |

|-----------|---------------|------------------|-----------------|---------------------------|

|-----------|---------------|------------------|-----------------|---------------------------|

| SPRAMP | SPZCD | SPNGZRA | SPNGZRR |  |

|--------|-------|---------|---------|--|

| 0      | 0     | X       | X       |  |

| X      | Х     | 1       | 1       |  |

| 1      | 1 X   |         | 0       |  |

#### Note:

6. X = don't care.

If the SPNGZRA bit is set to 0, the speaker noise gate attack (mute) function occurs immediately rather than waiting for zero-crossing detection or ramping. If the SPNGZRA bit is set to 1, the speaker noise gate attack function obeys speaker zero crossing detection and ramp settings. If the SPNGZRR bit is set to 0, the speaker noise gate release (un-mute) function occurs immediately rather than waiting for zero-crossing detection or ramping. If the SPNGZRR bit is set to 1, the speaker noise gate release (un-mute) function obeys speaker zero-crossing detection and ramp settings.

П

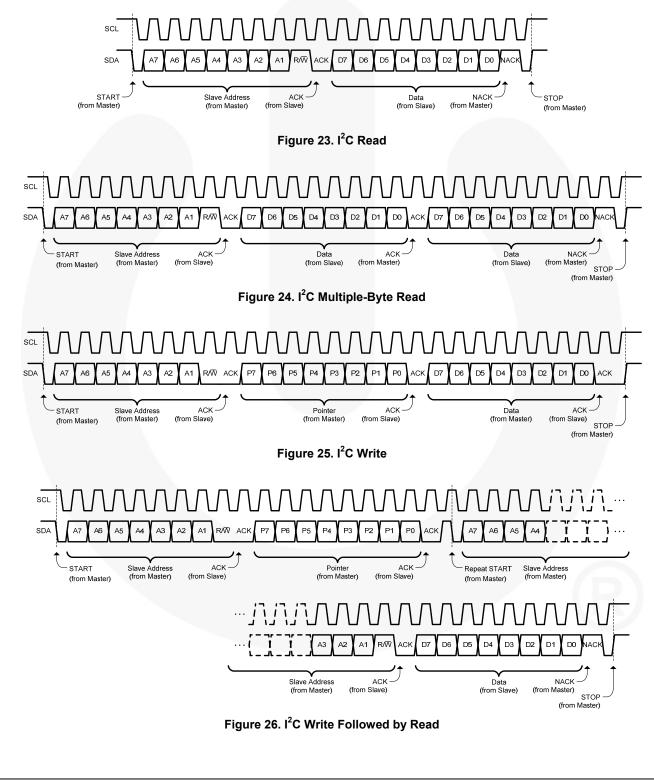

# I<sup>2</sup>C Control