# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconduc

AN3226 / FAN3227 / FAN3228 / FAN3229 I Dual 2-A High-Speed, Low-Side Gate Drivers

April 2013

# FAN3226 / FAN3227 / FAN3228 / FAN3229 **Dual 2-A High-Speed, Low-Side Gate Drivers**

## **Features**

- Industry-Standard Pinouts

- 4.5-V to 18-V Operating Range

- 3-A Peak Sink/Source at V<sub>DD</sub> = 12 V

- 2.4 A-Sink / 1.6-A Source at VOUT = 6 V

- Choice of TTL or CMOS Input Thresholds

- Four Versions of Dual Independent Drivers:

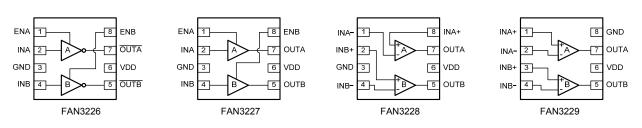

- Dual Inverting + Enable (FAN3226)

- Dual Non-Inverting + Enable (FAN3227)

- Dual Inputs in Two Pin-Out Configurations: Compatible with FAN3225x (FAN3228)

- Compatible with TPS2814D (FAN3229)

- Internal Resistors Turn Driver Off If No Inputs

- -MillerDrive<sup>™</sup> Technology

- 12-ns / 9-ns Typical Rise/Fall Times (1-nF Load)

- -Under 20-ns Typical Propagation Delay Matched within 1 ns to the Other Channel

- Double Current Capability by Paralleling Channels

- . 8-Lead 3x3 mm MLP or 8-Lead SOIC Package

- Rated from -40°C to +125°C Ambient

- Automotive Qualified to AEC-Q100 (F085 Version)

# Applications

- Switch-Mode Power Supplies

- High-Efficiency MOSFET Switching

- . Synchronous Rectifier Circuits

- DC-to-DC Converters

- Motor Control

- Servers

- Automotive-Qualified Systems (F085 version)

## Description

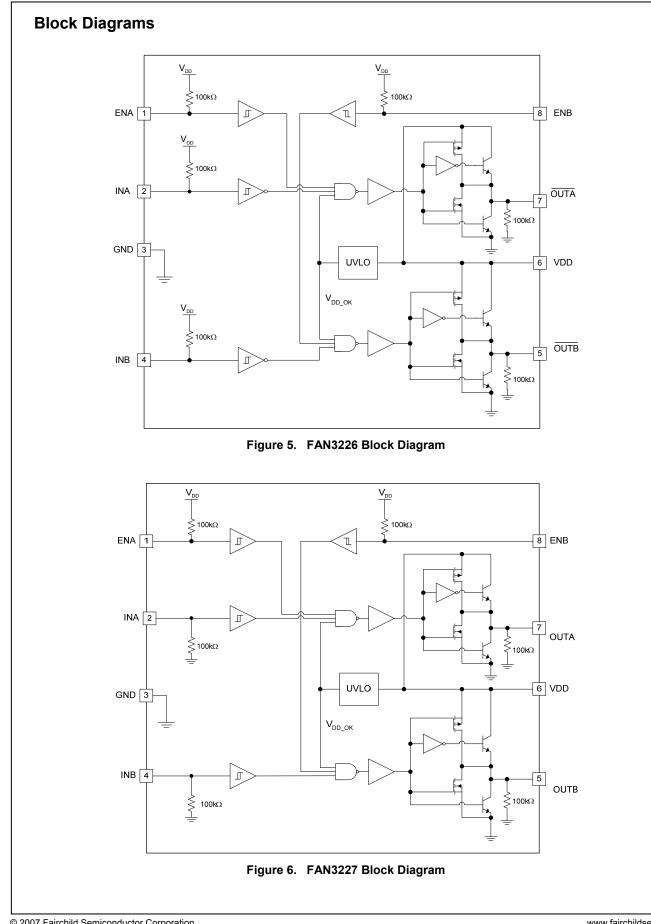

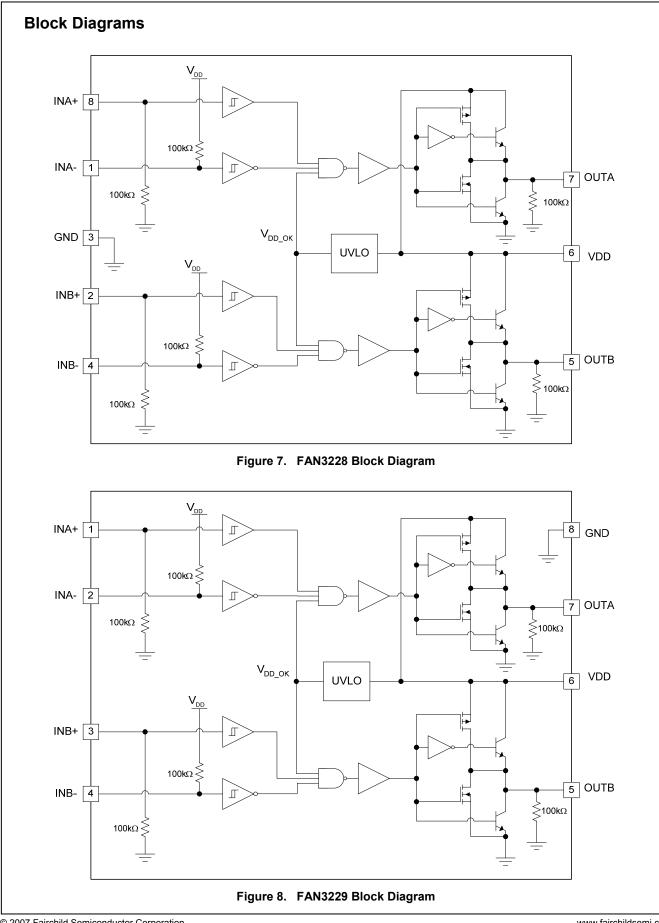

The FAN3226-29 family of dual 2 A gate drivers is designed to drive N-channel enhancement-mode MOSFETs in low-side switching applications by providing high peak current pulses during the short switching intervals. The driver is available with either TTL or CMOS input thresholds. Internal circuitry provides an under-voltage lockout function by holding the output low until the supply voltage is within the operating range. In addition, the drivers feature matched internal propagation delays between A and B channels for applications requiring dual gate drives with critical timing, such as synchronous rectifiers. This enables connecting two drivers in parallel to effectively double the current capability driving a single MOSFET.

The FAN322X drivers incorporate MillerDrive™ architecture for the final output stage. This bipolar-MOSFET combination provides high current during the Miller plateau stage of the MOSFET turn-on / turn-off process to minimize switching loss, while providing railto-rail voltage swing and reverse current capability.

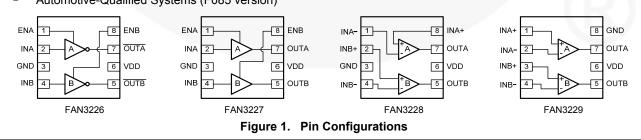

The FAN3226 offers two inverting drivers and the FAN3227 offers two non-inverting drivers. Each device has dual independent enable pins that default to ON if not connected. In the FAN3228 and FAN3229, each channel has dual inputs of opposite polarity, which allows configuration as non-inverting or inverting with an optional enable function using the second input. If one or both inputs are left unconnected, internal resistors bias the inputs such that the output is pulled low to hold the power MOSFET off.

# Related Resources

AN-6069: Application Review and Comparative Evaluation of Low-Side Gate Drivers

© 2007 Fairchild Semiconductor Corporation FAN3226 / FAN3227 / FAN3228 / FAN3229 • Rev. 1.1.0 www.fairchildsemi.com

# **Ordering Information**

| Part Number                    | Logic                                                                      | Input<br>Threshold | Package      | Packing<br>Method | Quantity<br>per Reel |

|--------------------------------|----------------------------------------------------------------------------|--------------------|--------------|-------------------|----------------------|

| FAN3226CMPX                    |                                                                            |                    | 3x3 mm MLP-8 | Tape & Reel       | 3,000                |

| FAN3226CMX                     |                                                                            | CMOS               | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3226CMX_F085 <sup>(1)</sup> | Dual Inverting Channels + Dual                                             |                    | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3226TMPX                    | Enable                                                                     |                    | 3x3 mm MLP-8 | Tape & Reel       | 3,000                |

| FAN3226TMX                     |                                                                            | TTL                | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3226TMX_F085 <sup>(1)</sup> |                                                                            |                    | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3227CMPX                    |                                                                            |                    | 3x3 mm MLP-8 | Tape & Reel       | 3,000                |

| FAN3227CMX                     | Dual Non-Inverting Channels +                                              | CMOS               | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3227CMX_F085 <sup>(1)</sup> |                                                                            |                    | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3227TMPX                    | Dual Enable                                                                |                    | 3x3 mm MLP-8 | Tape & Reel       | 3,000                |

| FAN3227TMX                     |                                                                            | TTL                | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3227TMX_F085 <sup>(1)</sup> |                                                                            |                    | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3228CMX_F085 <sup>(1)</sup> | Dual Channels of Two-Input /<br>One-Output Drivers, Pin                    | CMOS               | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3228TMX_F085 <sup>(1)</sup> | Configuration 1                                                            | TTL                | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3229CMPX                    |                                                                            |                    | 3x3 mm MLP-8 | Tape & Reel       | 3,000                |

| FAN3229CMX                     |                                                                            | CMOS               | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3229CMX_F085 <sup>(1)</sup> | Dual Channels of Two-Input /<br>One-Output Drivers, Pin<br>Configuration 2 |                    | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3229TMPX                    |                                                                            |                    | 3x3 mm MLP-8 | Tape & Reel       | 3,000                |

| FAN3229TMX                     |                                                                            | TTL                | SOIC-8       | Tape & Reel       | 2,500                |

| FAN3229TMX_F085 <sup>(1)</sup> |                                                                            |                    | SOIC-8       | Tape & Reel       | 2,500                |

All standard Fairchild Semiconductor products are RoHS compliant and many are also "Green" or going green. Green means the products are RoHS compliant AND they have limits on additional substances of Chlorine, Bromine and Antimony. *For additional information on Fairchild's "green" Eco Status, please visit: <u>http://www.fairchildsemi.com/company/green/rohs\_green.html</u>.*

Note:

1. Qualified to AEC-Q100

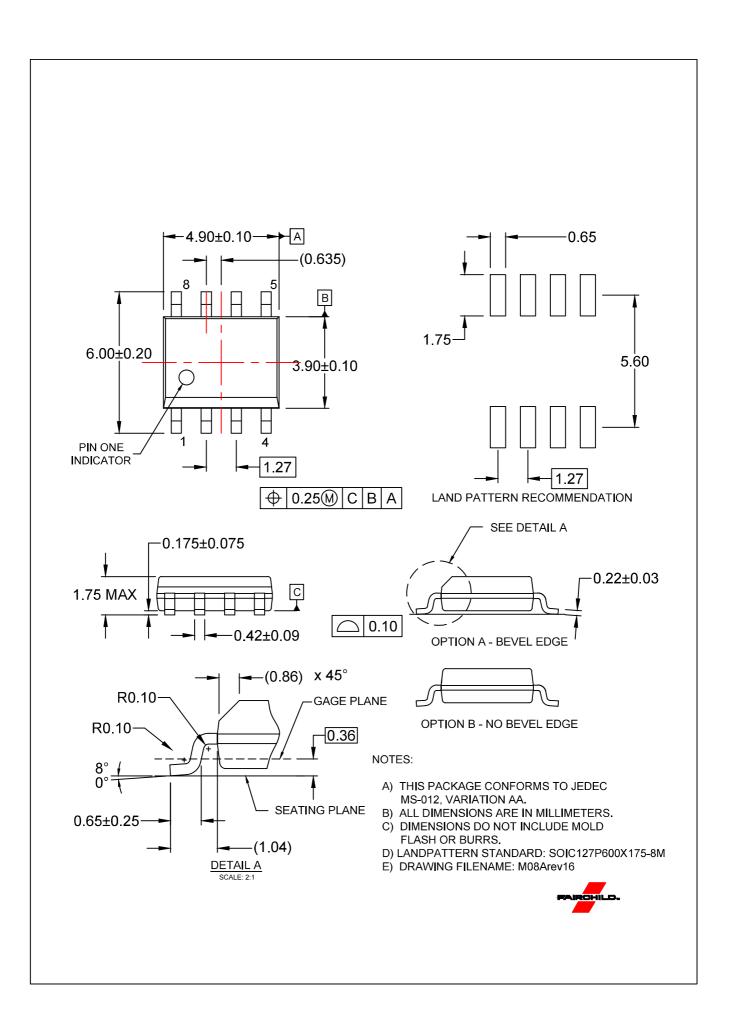

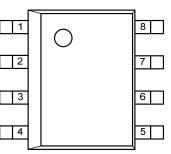

#### Package Outlines 2 1 2 3 3 6 4 4 5 Figure 2. 3x3 mm MLP-8 (Top View) Figure 3. SOIC-8 (Top View)

# Thermal Characteristics<sup>(2)</sup>

| Package                                       | $\Theta_{JL}{}^{(3)}$ | $\Theta_{JT}{}^{(4)}$ | $\Theta_{JA}^{(5)}$ | $\Psi_{JB}^{(6)}$ | ${\Psi_{JT}}^{(7)}$ | Unit |

|-----------------------------------------------|-----------------------|-----------------------|---------------------|-------------------|---------------------|------|

| 8-Lead 3x3 mm Molded Leadless Package (MLP)   | 1.6                   | 68                    | 43                  | 3.5               | 0.8                 | °C/W |

| 8-Pin Small Outline Integrated Circuit (SOIC) | 40                    | 31                    | 89                  | 43                | 3.0                 | °C/W |

Notes:

- Estimates derived from thermal simulation; actual values depend on the application. 2.

- 3. Theta JL  $(\Theta_{\mu})$ : Thermal resistance between the semiconductor junction and the bottom surface of all the leads (including any thermal pad) that are typically soldered to a PCB.

- Theta JT ( $\Theta_{\rm ur}$ ): Thermal resistance between the semiconductor junction and the top surface of the package, assuming it is 4. held at a uniform temperature by a top-side heatsink.

- 5. Theta JA  $(\Theta_{IA})$ : Thermal resistance between junction and ambient, dependent on the PCB design, heat sinking, and airflow. The value given is for natural convection with no heatsink using a 2S2P board, as specified in JEDEC standards JESD51-2, JESD51-5, and JESD51-7, as appropriate.

- Psi\_JB (Ψ<sub>JB</sub>): Thermal characterization parameter providing correlation between semiconductor junction temperature and an 6. application circuit board reference point for the thermal environment defined in Note 5. For the MLP-8 package, the board reference is defined as the PCB copper connected to the thermal pad and protruding from either end of the package. For the SOIC-8 package, the board reference is defined as the PCB copper adjacent to pin 6.

- 7. Psi JT ( $\Psi_{\text{JT}}$ ): Thermal characterization parameter providing correlation between the semiconductor junction temperature and the center of the top of the package for the thermal environment defined in Note 5.

Figure 4. Pin Configurations (Repeated)

### **Pin Definitions**

| Name | Pin Description                                                                                                                                         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENA  | <b>Enable Input for Channel A</b> . Pull pin LOW to inhibit driver A. ENA has TTL thresholds for both TTL and CMOS INx threshold.                       |

| ENB  | <b>Enable Input for Channel B</b> . Pull pin LOW to inhibit driver B. ENB has TTL thresholds for both TTL and CMOS INx threshold.                       |

| GND  | Ground. Common ground reference for input and output circuits.                                                                                          |

| INA  | Input to Channel A.                                                                                                                                     |

| INA+ | Non-Inverting Input to Channel A. Connect to VDD to enable output.                                                                                      |

| INA- | Inverting Input to Channel A. Connect to GND to enable output.                                                                                          |

| INB  | Input to Channel B.                                                                                                                                     |

| INB+ | Non-Inverting Input to Channel B. Connect to VDD to enable output.                                                                                      |

| INB- | Inverting Input to Channel B. Connect to GND to enable output.                                                                                          |

| OUTA | Gate Drive Output A: Held LOW unless required input(s) are present and V <sub>DD</sub> is above UVLO threshold.                                         |

| OUTB | Gate Drive Output B: Held LOW unless required input(s) are present and V <sub>DD</sub> is above UVLO threshold.                                         |

| OUTA | <b>Gate Drive Output A</b> (inverted from the input): Held LOW unless required input is present and $V_{DD}$ is above UVLO threshold.                   |

| OUTB | <b>Gate Drive Output B</b> (inverted from the input): Held LOW unless required input is present and $V_{DD}$ is above UVLO threshold.                   |

| P1   | <b>Thermal Pad</b> (MLP only). Exposed metal on the bottom of the package; may be left floating or connected to GND; NOT suitable for carrying current. |

| VDD  | Supply Voltage. Provides power to the IC.                                                                                                               |

# **Output Logic**

| FAN3226 ( <b>x</b> =A or B) |                  |      |  |  |

|-----------------------------|------------------|------|--|--|

| ENx                         | INx              | OUTx |  |  |

| 0                           | 0                | 0    |  |  |

| 0                           | 1 <sup>(8)</sup> | 0    |  |  |

| 1 <sup>(8)</sup>            | 0                | 1    |  |  |

| 1 <sup>(8)</sup>            | 1 <sup>(8)</sup> | 0    |  |  |

| FAN3227 ( <b>x</b> =A or B) |                  |      |  |  |

|-----------------------------|------------------|------|--|--|

| ENx                         | INx              | OUTx |  |  |

| 0                           | 0 <sup>(8)</sup> | 0    |  |  |

| 0                           | 1                | 0    |  |  |

| 1 <sup>(8)</sup>            | 0 <sup>(8)</sup> | 0    |  |  |

| 1 <sup>(8)</sup>            | 1                | 1    |  |  |

| FAN3228 and FAN3229<br>( <b>x</b> =A or B) |                  |   |  |  |  |  |

|--------------------------------------------|------------------|---|--|--|--|--|

| INx+ INx- OUTx                             |                  |   |  |  |  |  |

| 0 <sup>(8)</sup>                           | 0                | 0 |  |  |  |  |

| 0 <sup>(8)</sup>                           | 1 <sup>(8)</sup> | 0 |  |  |  |  |

| 1                                          | 0                | 1 |  |  |  |  |

| 1                                          | 1 <sup>(8)</sup> | 0 |  |  |  |  |

#### Note:

8. Default input signal if no external connection is made.

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                  |           | Max.                  | Unit |

|------------------|--------------------------------------------|-----------|-----------------------|------|

| V <sub>DD</sub>  | VDD to PGND                                | -0.3      | 20.0                  | V    |

| V <sub>EN</sub>  | ENA and ENB to GND                         | GND - 0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IN</sub>  | INA, INA+, INA–, INB, INB+ and INB– to GND | GND - 0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>OUT</sub> | OUTA and OUTB to GND                       | GND - 0.3 | V <sub>DD</sub> + 0.3 | V    |

| TL               | Lead Soldering Temperature (10 Seconds)    |           | +260                  | °C   |

| TJ               | Junction Temperature                       | -55       | +150                  | °C   |

| T <sub>STG</sub> | Storage Temperature                        | -65       | +150                  | °C   |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter                                         | Min. | Max.            | Unit |

|-----------------|---------------------------------------------------|------|-----------------|------|

| V <sub>DD</sub> | Supply Voltage Range                              | 4.5  | 18.0            | V    |

| V <sub>EN</sub> | Enable Voltage ENA and ENB                        | 0    | $V_{\text{DD}}$ | V    |

| V <sub>IN</sub> | Input Voltage INA, INA+, INA-, INB, INB+ and INB- | 0    | $V_{\text{DD}}$ | V    |

| T <sub>A</sub>  | Operating Ambient Temperature                     | -40  | +125            | °C   |

# **Electrical Characteristics**

Unless otherwise noted,  $V_{DD}$ =12 V,  $T_J$ =-40°C to +125°C. Currents are defined as positive into the device and negative out of the device.

| Symbol                      | Parameter                                    | Conditions                            | Min. | Тур. | Max.  | Unit      |

|-----------------------------|----------------------------------------------|---------------------------------------|------|------|-------|-----------|

| Supply                      | •                                            | <u>.</u>                              |      |      | •     |           |

| $V_{DD}$                    | Operating Range                              |                                       | 4.5  |      | 18.0  | V         |

|                             | Supply Current Inputs / EN                   | TTL                                   |      | 0.75 | 1.20  | mA        |

| I <sub>DD</sub>             | Not Connected                                | CMOS <sup>(9)</sup>                   |      | 0.65 | 1.05  | mA        |

| V <sub>ON</sub>             | Turn-On Voltage                              | INA=ENA=V <sub>DD</sub> , INB=ENB=0 V | 3.5  | 3.9  | 4.3   | V         |

| $V_{OFF}$                   | Turn-Off Voltage                             | INA=ENA=V <sub>DD</sub> , INB=ENB=0 V | 3.3  | 3.7  | 4.1   | V         |

| FAN322xC                    | CMX_F085, FAN322xTMX_F085 (Auto              | omotive-Qualified Versions)           |      |      |       |           |

| V <sub>ON</sub>             | Turn-On Voltage <sup>(14)</sup>              | INA=ENA=V <sub>DD</sub> , INB=ENB=0 V | 3.3  | 3.9  | 4.5   | V         |

| $V_{OFF}$                   | Turn-Off Voltage <sup>(14)</sup>             | INA=ENA=V <sub>DD</sub> , INB=ENB=0 V | 3.1  | 3.7  | 4.3   | V         |

| Inputs (FA                  | AN322xT) <sup>(10)</sup>                     |                                       |      |      |       |           |

| $V_{\text{INL}_{\text{T}}}$ | INx Logic Low Threshold                      |                                       | 0.8  | 1.2  |       | V         |

| $V_{\text{INH}\_\text{T}}$  | INx Logic High Threshold                     |                                       |      | 1.6  | 2.0   | V         |

| V <sub>HYS_T</sub>          | TTL Logic Hysteresis Voltage                 |                                       | 0.2  | 0.4  | 0.8   | V         |

| FAN322xT                    |                                              |                                       |      |      |       |           |

| I <sub>IN+</sub>            | Non-Inverting Input Current                  | IN from 0 to V <sub>DD</sub>          | -1   |      | 175   | μA        |

| I <sub>IN-</sub>            | Inverting Input Current                      | IN from 0 to V <sub>DD</sub>          | -175 |      | 1     | μA        |

| FAN322xT                    | MX_F085 (Automotive-Qualified Vers           | ions)                                 |      |      |       |           |

| I <sub>INx_T</sub>          | Non-inverting Input Current <sup>(14)</sup>  | IN=0 V                                | -1.5 |      | 1.5   | μA        |

| I <sub>INx_T</sub>          | Non-inverting Input Current <sup>(14)</sup>  | IN=V <sub>DD</sub>                    | 90   | 120  | 175.0 | μA        |

| I <sub>INx_T</sub>          | Inverting Input Current <sup>(14)</sup>      | IN=0 V                                | -175 | -120 | -90   | μA        |

| I <sub>INx_T</sub>          | Inverting Input Current <sup>(14)</sup>      | IN=V <sub>DD</sub>                    | -1.5 |      | 1.5   | μA        |

| Inputs (FA                  | AN322xC) <sup>(10)</sup>                     |                                       |      |      |       |           |

| $V_{\text{INL}_{C}}$        | INx Logic Low Threshold                      |                                       | 30   | 38   |       | $%V_{DD}$ |

| $V_{\text{INH}_{\text{C}}}$ | INx Logic High Threshold                     |                                       |      | 55   | 70    | $%V_{DD}$ |

| $V_{HYS_C}$                 | CMOS Logic Hysteresis Voltage                |                                       |      | 17   |       | $%V_{DD}$ |

| FAN322xC                    | >                                            |                                       |      |      |       |           |

| I <sub>IN+</sub>            | Non-Inverting Input Current                  | IN from 0 to V <sub>DD</sub>          | -1   |      | 175   | μA        |

| I <sub>IN-</sub>            | Inverting Input Current                      | IN from 0 to V <sub>DD</sub>          | -175 |      | 1     | μA        |

| FAN322xC                    | CMX_F085 (Automotive-Qualified Vers          | ions)                                 |      |      |       |           |

| I <sub>INx_T</sub>          | Non-inverting Input Current <sup>(14)</sup>  | IN=0 V                                | -1.5 |      | 1.5   | μA        |

| I <sub>INx_T</sub>          | Non-inverting Input Current <sup>(14)</sup>  | IN=V <sub>DD</sub>                    | 90   | 120  | 175.0 | μA        |

| I <sub>INx_T</sub>          | Inverting Input Current <sup>(14)</sup>      | IN=0 V                                | -175 | -120 | -90   | μA        |

| I <sub>INx_T</sub>          | Inverting Input Current <sup>(14)</sup>      | IN=V <sub>DD</sub>                    | -1.5 |      | 1.5   | μA        |

| ENABLE (                    | FAN3226C, FAN3226T, FAN3227C,                | FAN3227T)                             |      |      |       |           |

| $V_{\text{ENL}}$            | Enable Logic Low Threshold                   | EN from 5 V to 0 V                    | 0.8  | 1.2  |       | V         |

| $V_{\text{ENH}}$            | Enable Logic High Threshold                  | EN from 0 V to 5 V                    |      | 1.6  | 2.0   | V         |

| V <sub>HYS_T</sub>          | TTL Logic Hysteresis Voltage <sup>(11)</sup> |                                       |      | 0.4  |       | V         |

| R <sub>PU</sub>             | Enable Pull-up Resistance <sup>(11)</sup>    |                                       |      | 100  |       | kΩ        |

Continued on the following page...

# Electrical Characteristics (Continued)

Unless otherwise noted,  $V_{DD}$ =12 V,  $T_{J}$ =-40°C to +125°C. Currents are defined as positive into the device and negative out of the device.

| Symbol                 | Parameter                                                     | Conditions                                                                   | Min.     | Тур.   | Max. | Unit |

|------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------|----------|--------|------|------|

| ENABLE (               | FAN3226C, FAN3226T, FAN3227C, FA                              | N3227T) (continued)                                                          | •        |        | •    | •    |

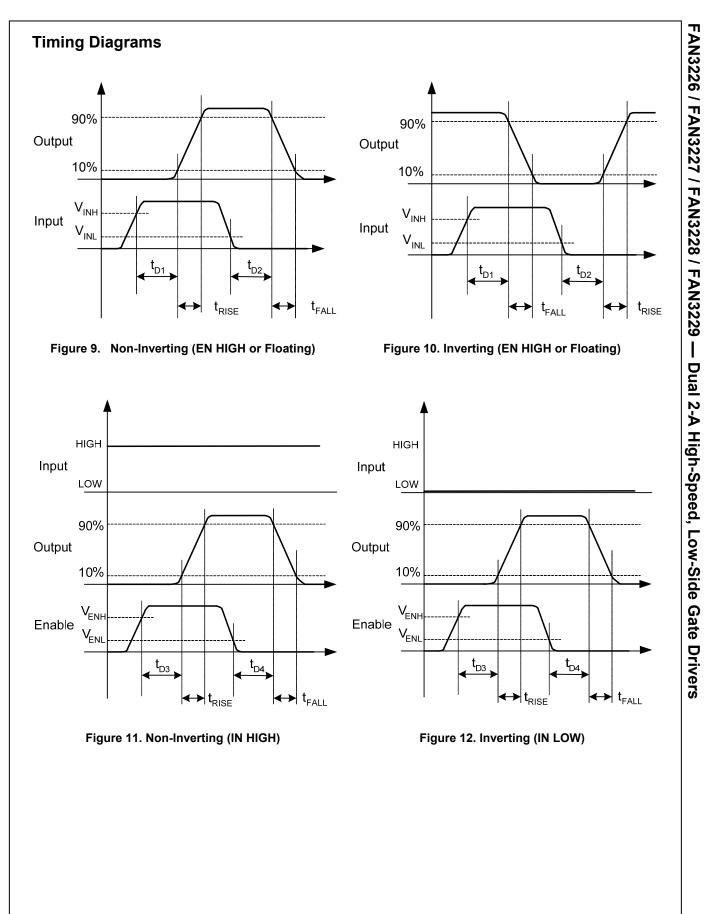

| t <sub>D3</sub>        | ENITE Output Descention Date (12)                             | 0 V to 5 V EN, 1 V/ns Slew Rate                                              | 10       | 19     | 34   | ns   |

| t <sub>D4</sub>        | EN to Output Propagation Delay <sup>(12)</sup>                | 5 V to 0 V EN, 1 V/ns Slew Rate                                              | 10       | 18     | 32   | ns   |

| FAN3226C               | MX, FAN3226TMX, FAN3227CMX, FAN                               | 3227TMX_F085 (Automotive-Quali                                               | fied Ver | sions) | •    |      |

| t <sub>D3</sub>        |                                                               | 0 V to 5 V EN, 1 V/ns Slew Rate                                              | 8        | 19     | 35   | ns   |

| t <sub>D4</sub>        | EN to Output Propagation Delay <sup>(12),(14)</sup>           | 5 V to 0 V EN, 1 V/ns Slew Rate                                              | 8        | 18     | 35   | ns   |

| Outputs                | ·                                                             |                                                                              | •        |        | •    |      |

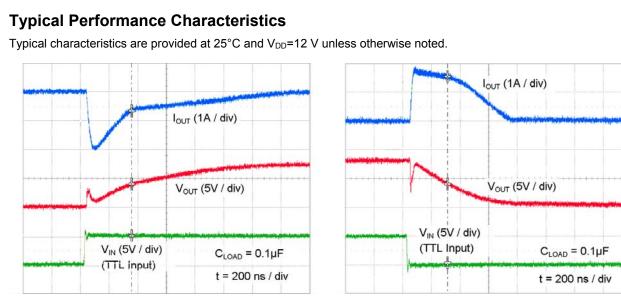

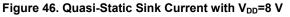

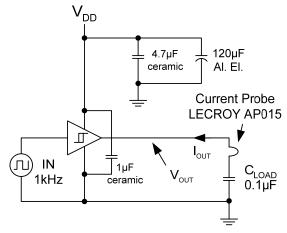

| I <sub>SINK</sub>      | OUT Current, Mid-Voltage, Sinking <sup>(11)</sup>             | OUT at V <sub>DD</sub> /2,<br>C <sub>LOAD</sub> =0.1 μF, f=1 kHz             |          | 2.4    |      | А    |

| I <sub>SOURCE</sub>    | OUT Current, Mid-Voltage,<br>Sourcing <sup>(11)</sup>         | OUT at V <sub>DD</sub> /2,<br>C <sub>LOAD</sub> =0.1 μF, f=1 kHz             |          | -1.6   |      | A    |

| I <sub>PK_SINK</sub>   | OUT Current, Peak, Sinking <sup>(11)</sup>                    | C <sub>LOAD</sub> =0.1 µF, f=1 kHz                                           |          | 3      |      | Α    |

| I <sub>PK_SOURCE</sub> | OUT Current, Peak, Sourcing <sup>(11)</sup>                   | C <sub>LOAD</sub> =0.1 µF, f=1 kHz                                           |          | -3     |      | Α    |

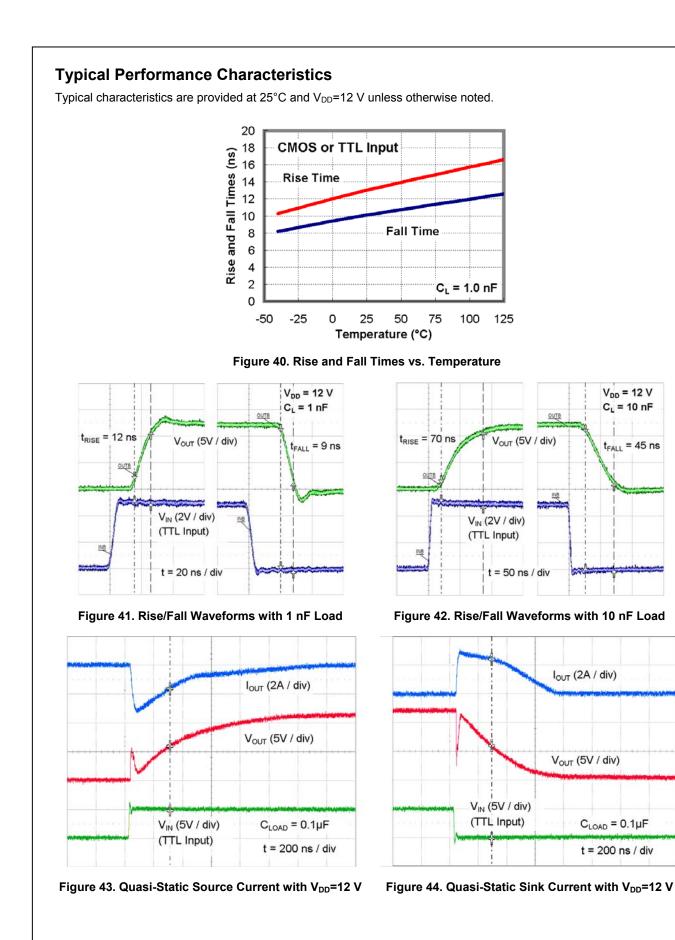

| t <sub>RISE</sub>      | Output Rise Time <sup>(13)</sup>                              | C <sub>LOAD</sub> =1000 pF                                                   |          | 12     | 22   | ns   |

| t <sub>FALL</sub>      | Output Fall Time <sup>(13)</sup>                              | C <sub>LOAD</sub> =1000 pF                                                   |          | 9      | 17   | ns   |

| I <sub>RVS</sub>       | Output Reverse Current Withstand <sup>(11)</sup>              |                                                                              |          | 500    |      | mA   |

| FAN322xT,              | FAN322xC                                                      |                                                                              | •        |        | •    |      |

| t <sub>D1</sub>        | Output Propagation Delay, CMOS                                | CMOS Input                                                                   | 7        | 15     | 30   |      |

| t <sub>D2</sub>        | Inputs <sup>(13)</sup>                                        | CMOS Input                                                                   | 6        | 15     | 29   | ns   |

| t <sub>D1</sub>        | Output Propagation Delay, TTL                                 | TTL Input                                                                    | 10       | 19     | 34   |      |

| t <sub>D2</sub>        | Inputs <sup>(13)</sup>                                        | TTL Input                                                                    | 10       | 18     | 32   | ns   |

| t <sub>DEL.MATCH</sub> | Propagation Matching Between Channels <sup>(14)</sup>         | INA=INB, OUTA and OUTB at 50% Point                                          |          | 1      | 2    | ns   |

| FAN322xTI              | MX_F085, FAN322xCMX_F085 (Automo                              | tive-Qualified Versions)                                                     |          |        |      |      |

| t <sub>D1</sub>        | Output Propagation Delay, CMOS<br>Inputs <sup>(13),(14)</sup> | CMOS Input                                                                   | 7        | 15     | 33   |      |

| t <sub>D2</sub>        | Inputs <sup>(13),(14)</sup>                                   | CMOS Input                                                                   | 6        | 15     | 42   | ns   |

| t <sub>D1</sub>        | Output Propagation Delay, TTL                                 | TTL Input                                                                    | 9        | 19     | 34   |      |

| t <sub>D2</sub>        | Inputs <sup>(13),(14)</sup>                                   | TTL Input                                                                    | 9        | 18     | 32   | ns   |

| t <sub>DEL.MATCH</sub> | Propagation Matching Between Channels <sup>(14)</sup>         | INA=INB, OUTA and OUTB at 50% Point                                          |          | 2      | 4    | ns   |

| V <sub>OH</sub>        | High Level Output Voltage <sup>(14)</sup>                     | V <sub>OH</sub> =V <sub>DD</sub> -V <sub>OUT</sub> , I <sub>OUT</sub> =-1 mA |          | 15     | 35   | mV   |

| Vol                    | Low Level Output Voltage <sup>(14)</sup>                      | I <sub>OUT</sub> = 1 mA                                                      |          | 10     | 25   | mV   |

#### Notes:

9. Lower supply current due to inactive TTL circuitry.

- 10. EN inputs have TTL thresholds; refer to the ENABLE section.

- 11. Not tested in production.

- 12. See Timing Diagrams of Figure 11 and Figure 12.

- 13. See Timing Diagrams of Figure 9 and Figure 10.

14. Apply to only F085 Version

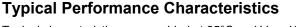

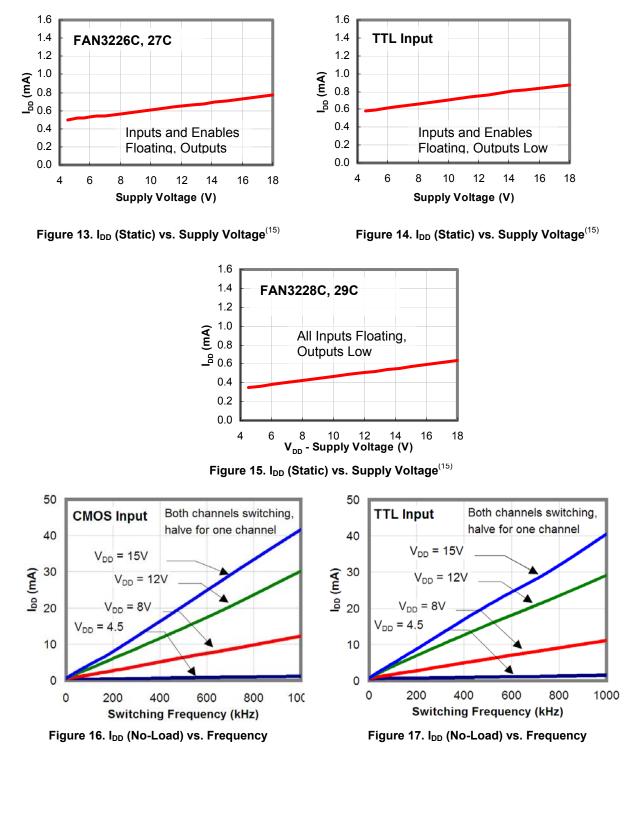

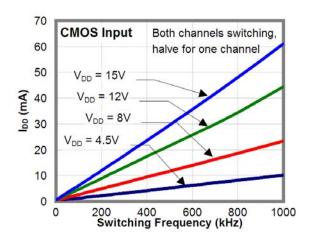

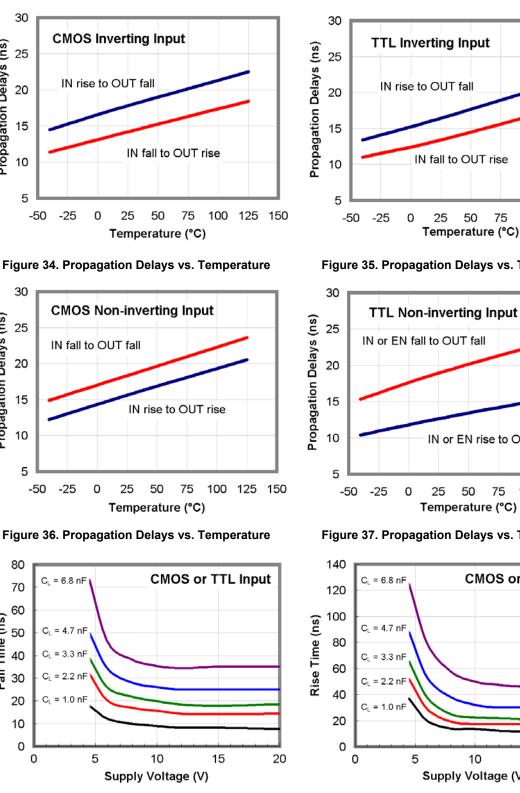

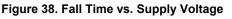

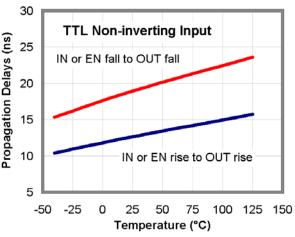

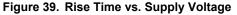

Typical characteristics are provided at 25°C and  $V_{\text{DD}}$ =12 V unless otherwise noted.

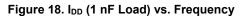

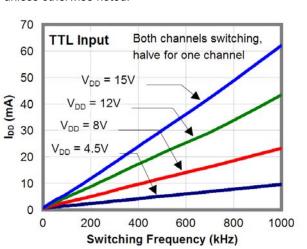

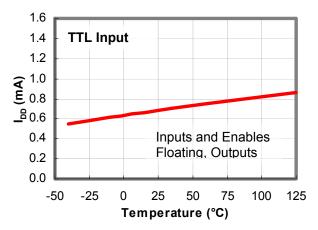

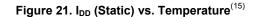

Figure 20. I<sub>DD</sub> (Static) vs. Temperature<sup>(15)</sup>

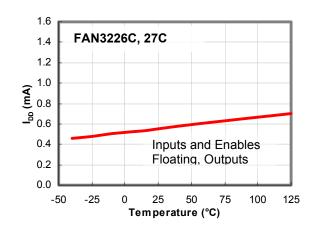

Figure 19. IDD (1 nF Load) vs. Frequency

FAN3226 / FAN3227 / FAN3228 / FAN3229 ----Dual 2-A High-Speed, Low-Side Gate Drivers

**Typical Performance Characteristics**

Propagation Delays (ns)

Propagation Delays (ns)

Fall Time (ns)

Typical characteristics are provided at 25°C and V<sub>DD</sub>=12 V unless otherwise noted.

Figure 35. Propagation Delays vs. Temperature

50

75

100

125

150

Figure 37. Propagation Delays vs. Temperature

Figure 45. Quasi-Static Source Current with V<sub>DD</sub>=8 V

#### Note:

15. For any inverting inputs pulled low, non-inverting inputs pulled high, or outputs driven high, static I<sub>DD</sub> increases by the current flowing through the corresponding pull-up/down resistor shown in the block diagram.

# **Test Circuit**

Figure 47. Quasi-Static IOUT / VOUT Test Circuit

# **Applications Information**

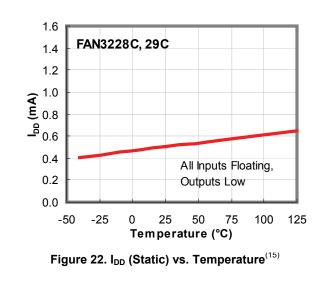

#### **Input Thresholds**

Each member of the FAN322x driver family consists of two identical channels that may be used independently at rated current or connected in parallel to double the individual current capacity. In the FAN3226 and FAN3227, channels A and B can be enabled or disabled independently using ENA or ENB, respectively. The EN pin has TTL thresholds for parts with either CMOS or TTL input thresholds. If ENA and ENB are not connected, an internal pull-up resistor enables the driver channels by default. If the channel A and channel B inputs and outputs are connected in parallel to increase the driver current capacity, ENA and ENB should be connected and driven together.

The FAN322x family offers versions in either TTL or CMOS input thresholds. In the FAN322xT, the input thresholds meet industry-standard TTL-logic thresholds independent of the  $V_{DD}$  voltage, and there is a hysteresis voltage of approximately 0.4 V. These levels permit the inputs to be driven from a range of input logic signal levels for which a voltage over 2 V is considered logic high. The driving signal for the TTL inputs should have fast rising and falling edges with a slew rate of 6 V/µs or faster, so a rise time from 0 to 3.3 V should be 550 ns or less. With reduced slew rate, circuit noise could cause the driver input voltage to exceed the hysteresis voltage and retrigger the driver input, causing erratic operation.

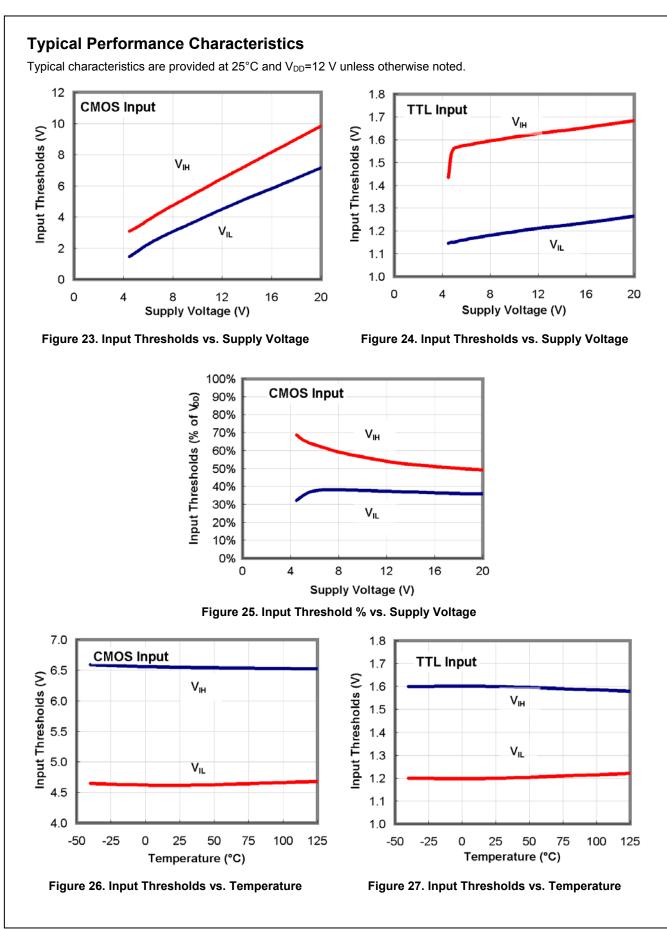

In the FAN322xC, the logic input thresholds are dependent on the V<sub>DD</sub> level and, with V<sub>DD</sub> of 12 V, the logic rising edge threshold is approximately 55% of V<sub>DD</sub> and the input falling edge threshold is approximately 38% of V<sub>DD</sub>. The CMOS input configuration offers a hysteresis voltage of approximately 17% of V<sub>DD</sub>. The CMOS inputs can be used with relatively slow edges (approaching DC) if good decoupling and bypass techniques are incorporated in the system design to prevent noise from violating the input voltage hysteresis window. This allows setting precise timing intervals by fitting an R-C circuit between the controlling signal and the IN pin of the driver. The slow rising edge at the IN pin of the driver introduces a delay between the controlling signal and the OUT pin of the driver.

#### **Static Supply Current**

In the I<sub>DD</sub> (static) typical performance characteristics (see Figure 13 - Figure 15 and Figure 20 - Figure 22), the curve is produced with all inputs / enables floating (OUT is low) and indicates the lowest static I<sub>DD</sub> current for the tested configuration. For other states, additional current flows through the 100 k $\Omega$  resistors on the inputs and outputs shown in the block diagram of each part (see Figure 5 - Figure 8). In these cases, the actual static I<sub>DD</sub> current is the value obtained from the curves plus this additional current.

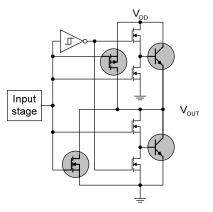

#### MillerDrive<sup>™</sup> Gate Drive Technology

FAN322x gate drivers incorporate the MillerDrive<sup>TM</sup> architecture shown in Figure 48. For the output stage, a combination of bipolar and MOS devices provide large currents over a wide range of supply voltage and temperature variations. The bipolar devices carry the bulk of the current as OUT swings between 1/3 to 2/3 V<sub>DD</sub> and the MOS devices pull the output to the high or low rail.

The purpose of the MillerDrive<sup>™</sup> architecture is to speed up switching by providing high current during the Miller plateau region when the gate-drain capacitance of the MOSFET is being charged or discharged as part of the turn-on / turn-off process.

For applications that have zero voltage switching during the MOSFET turn-on or turn-off interval, the driver supplies high peak current for fast switching even though the Miller plateau is not present. This situation often occurs in synchronous rectifier applications because the body diode is generally conducting before the MOSFET is switched on.

The output pin slew rate is determined by  $V_{DD}$  voltage and the load on the output. It is not user adjustable, but a series resistor can be added if a slower rise or fall time at the MOSFET gate is needed.

Figure 48. MillerDrive™ Output Architecture

#### **Under-Voltage Lockout**

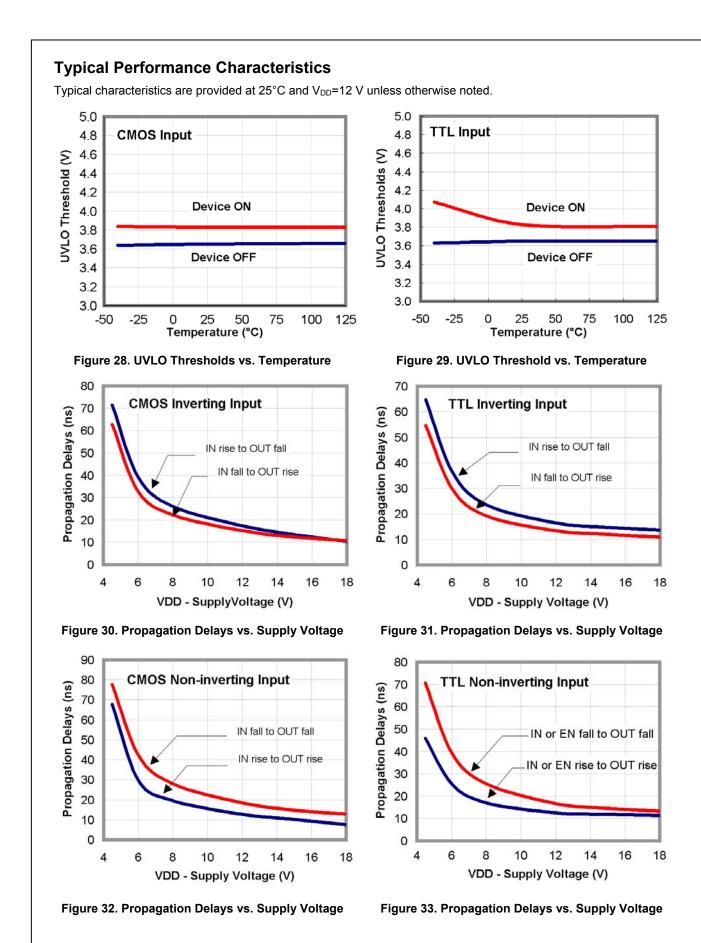

The FAN322x startup logic is optimized to drive groundreferenced N-channel MOSFETs with an under-voltage lockout (UVLO) function to ensure that the IC starts up in an orderly fashion. When  $V_{DD}$  is rising, yet below the 3.9 V operational level, this circuit holds the output low, regardless of the status of the input pins. After the part is active, the supply voltage must drop 0.2 V before the part shuts down. This hysteresis helps prevent chatter when low  $V_{DD}$  supply voltages have noise from the power switching. This configuration is not suitable for driving high-side P-channel MOSFETs because the low output voltage of the driver would turn the P-channel MOSFET on with  $V_{DD}$  below 3.9 V.

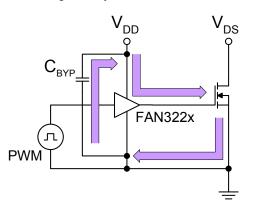

### **V**<sub>DD</sub> Bypass Capacitor Guidelines

To enable this IC to turn a device on quickly, a local high-frequency bypass capacitor  $C_{BYP}$  with low ESR and ESL should be connected between the VDD and GND pins with minimal trace length. This capacitor is in addition to bulk electrolytic capacitance of 10  $\mu$ F to 47  $\mu$ F commonly found on driver and controller bias circuits.

A typical criterion for choosing the value of  $C_{\text{BYP}}$  is to keep the ripple voltage on the  $V_{\text{DD}}$  supply to  $\leq 5\%$ . This is often achieved with a value  $\geq 20$  times the equivalent load capacitance  $C_{\text{EQV}}$ , defined here as  $Q_{\text{GATE}}/V_{\text{DD}}$ . Ceramic capacitors of 0.1  $\mu\text{F}$  to 1  $\mu\text{F}$  or larger are common choices, as are dielectrics, such as X5R and X7R with good temperature characteristics and high pulse current capability.

If circuit noise affects normal operation, the value of  $C_{BYP}$  may be increased to 50-100 times the  $C_{EQV}$ , or  $C_{BYP}$  may be split into two capacitors. One should be a larger value, based on equivalent load capacitance, and the other a smaller value, such as 1-10 nF mounted closest to the VDD and GND pins to carry the higher frequency components of the current pulses. The bypass capacitor must provide the pulsed current from both of the driver channels and, if the drivers are switching simultaneously, the combined peak current sourced from the  $C_{BYP}$  would be twice as large as when a single channel is switching.

#### Layout and Connection Guidelines

The FAN3226-26 family of gate drivers incorporates fast-reacting input circuits, short propagation delays, and powerful output stages capable of delivering current peaks over 2 A to facilitate voltage transition times from under 10 ns to over 150 ns. The following layout and connection guidelines are strongly recommended:

- Keep high-current output and power ground paths separate logic and enable input signals and signal ground paths. This is especially critical when dealing with TTL-level logic thresholds at driver inputs and enable pins.

- Keep the driver as close to the load as possible to minimize the length of high-current traces. This reduces the series inductance to improve highspeed switching, while reducing the loop area that can radiate EMI to the driver inputs and surrounding circuitry.

- If the inputs to a channel are not externally connected, the internal 100 kΩ resistors indicated on block diagrams command a low output. In noisy environments, it may be necessary to tie inputs of an unused channel to VDD or GND using short traces to prevent noise from causing spurious output switching.

- Many high-speed power circuits can be susceptible to noise injected from their own output or other external sources, possibly causing output retriggering. These effects can be obvious if the circuit is tested in breadboard or non-optimal circuit layouts with long input, enable, or output leads. For

best results, make connections to all pins as short and direct as possible.

- The FAN322x is compatible with many other industry-standard drivers. In single input parts with enable pins, there is an internal 100 kΩ resistor tied to V<sub>DD</sub> to enable the driver by default; this should be considered in the PCB layout.

- The turn-on and turn-off current paths should be minimized, as discussed in the following section.

Figure 49 shows the pulsed gate drive current path when the gate driver is supplying gate charge to turn the MOSFET on. The current is supplied from the local bypass capacitor,  $C_{BYP}$ , and flows through the driver to the MOSFET gate and to ground. To reach the high peak currents possible, the resistance and inductance in the path should be minimized. The localized  $C_{BYP}$  acts to contain the high peak current pulses within this driver-MOSFET circuit, preventing them from disturbing the sensitive analog circuitry in the PWM controller.

#### Figure 49. Current Path for MOSFET Turn-on

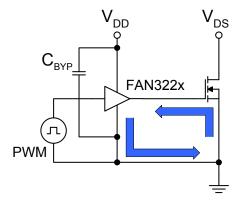

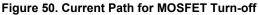

Figure 50 shows the current path when the gate driver turns the MOSFET off. Ideally, the driver shunts the current directly to the source of the MOSFET in a small circuit loop. For fast turn-off times, the resistance and inductance in this path should be minimized.

### **Truth Table of Logic Operation**

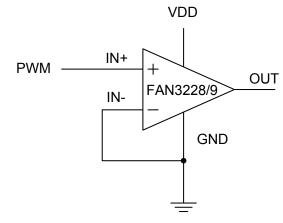

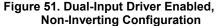

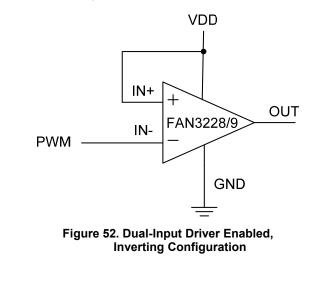

The FAN3228/FAN3229 truth table indicates the operational states using the dual-input configuration. In a non-inverting driver configuration, the IN- pin should be a logic low signal. If the IN- pin is connected to logic high, a disable function is realized, and the driver output remains low regardless of the state of the IN+ pin.

| IN+ | IN- | OUT |

|-----|-----|-----|

| 0   | 0   | 0   |

| 0   | 1   | 0   |

| 1   | 0   | 1   |

| 1   | 1   | 0   |

In the non-inverting driver configuration in Figure 51, the IN- pin is tied to ground and the input signal (PWM) is applied to IN+ pin. The IN- pin can be connected to logic high to disable the driver and the output remains low, regardless of the state of the IN+ pin.

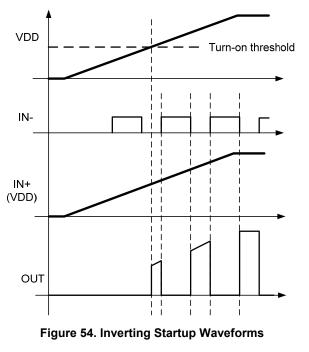

In the inverting driver application in Figure 52, the IN+ pin is tied high. Pulling the IN+ pin to GND forces the output low, regardless of the state of the IN- pin.

#### **Operational Waveforms**

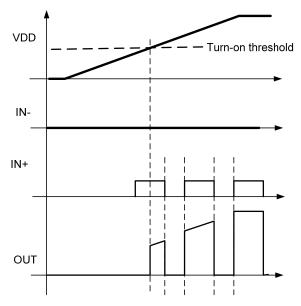

At power-up, the driver output remains low until the  $V_{DD}$  voltage reaches the turn-on threshold. The magnitude of the OUT pulses rises with  $V_{DD}$  until steady-state  $V_{DD}$  is reached. The non-inverting operation illustrated in Figure 53 shows that the output remains low until the UVLO threshold is reached, the output is in-phase with the input.

Figure 53. Non-Inverting Startup Waveforms

For the inverting configuration of Figure 52, startup waveforms are shown in Figure 54. With IN+ tied to  $V_{DD}$  and the input signal applied to IN–, the OUT pulses are inverted with respect to the input. At power-up, the inverted output remains low until the  $V_{DD}$  voltage reaches the turn-on threshold, then it follows the input with inverted phase.

#### **Thermal Guidelines**

Gate drivers used to switch MOSFETs and IGBTs at high frequencies can dissipate significant amounts of power. It is important to determine the driver power dissipation and the resulting junction temperature in the application to ensure that the part is operating within acceptable temperature limits.

The total power dissipation in a gate driver is the sum of two components,  $P_{GATE}$  and  $P_{DYNAMIC}$ :

$$P_{\text{TOTAL}} = P_{\text{GATE}} + P_{\text{DYNAMIC}}$$

(1)

Gate Driving Loss: The most significant power loss results from supplying gate current (charge per unit time) to switch the load MOSFET on and off at the switching frequency. The power dissipation that results from driving a MOSFET at a specified gate-source voltage,  $V_{GS}$ , with gate charge,  $Q_G$ , at switching frequency,  $f_{SW}$ , is determined by:

$$P_{GATE} = Q_G \cdot V_{GS} \cdot f_{SW} \cdot n \tag{2}$$

n is the number of driver channels in use (1 or 2).

Dynamic Pre-drive / Shoot-through Current: A power loss resulting from internal current consumption under dynamic operating conditions, including pin pull-up / pull-down resistors, can be obtained using the "I<sub>DD</sub> (No-Load) vs. Frequency" graphs in Typical Performance Characteristics to determine the current I<sub>DYNAMIC</sub> drawn from V<sub>DD</sub> under actual operating conditions:

$$P_{\text{DYNAMIC}} = I_{\text{DYNAMIC}} \cdot V_{\text{DD}} \cdot n \tag{3}$$

Once the power dissipated in the driver is determined, the driver junction rise with respect to circuit board can be evaluated using the following thermal equation, assuming  $\Psi_{JB}$  was determined for a similar thermal design (heat sinking and air flow):

$$T_{J} = P_{TOTAL} \cdot \Psi_{JB} + T_{B}$$

(4)

where:

T<sub>J</sub> = driver junction temperature

- \$\Psi\_{JB}\$ = (psi) thermal characterization parameter relating temperature rise to total power dissipation

- T<sub>B</sub> = board temperature in location defined in Note 2 under Thermal Resistance table.

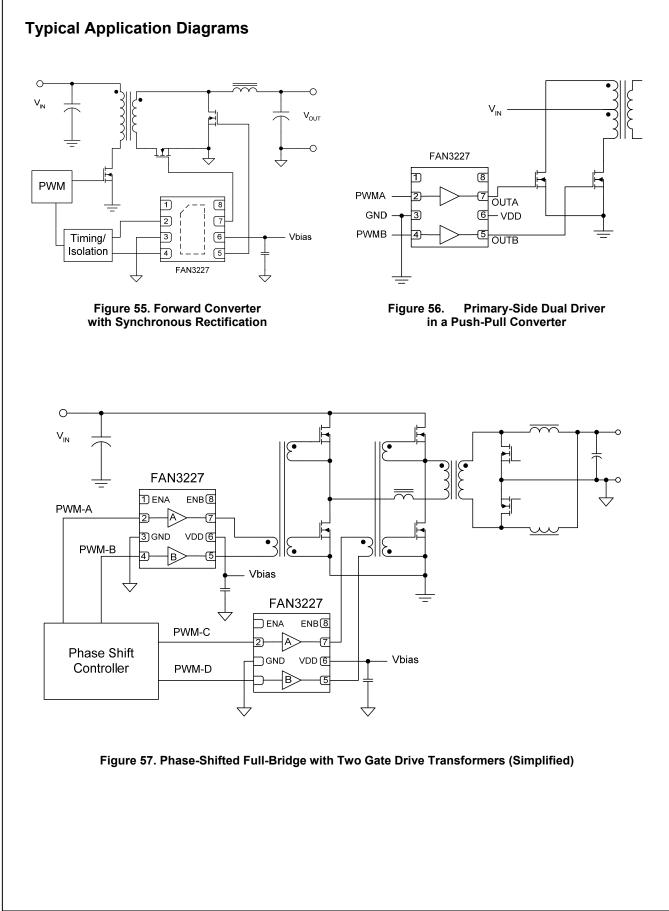

In the forward converter with synchronous rectifier shown in the typical application diagrams, the FDMS8660S is a reasonable MOSFET selection. The gate charge for each SR MOSFET would be 60 nC with  $V_{GS} = V_{DD} = 7V$ . At a switching frequency of 500 kHz, the total power dissipation is:

$P_{GATE} = 60 \text{ nC} \cdot 7 \text{ V} \cdot 500 \text{ kHz} \cdot 2 = 0.42 \text{ W}$  (5)

$P_{\text{DYNAMIC}} = 3 \text{ mA} \cdot 7 \text{ V} \cdot 2 = 0.042 \text{ W}$  (6)

$$P_{\text{TOTAL}} = 0.46 \text{ W} \tag{7}$$

The SOIC-8 has a junction-to-board thermal characterization parameter of  $\psi_{JB} = 43^{\circ}$ C/W. In a system application, the localized temperature around the device is a function of the layout and construction of the PCB along with airflow across the surfaces. To ensure reliable operation, the maximum junction temperature of the device must be prevented from exceeding the maximum rating of 150°C; with 80% derating, T<sub>J</sub> would be limited to 120°C. Rearranging Equation 4 determines the board temperature required to maintain the junction temperature below 120°C:

$$T_{\rm B} = T_{\rm J} - P_{\rm TOTAL} \bullet \Psi_{\rm JB} \tag{8}$$

$$T_B = 120^{\circ}C - 0.46 \text{ W} \cdot 43^{\circ}C/W = 100^{\circ}C$$

(9)

For comparison, replace the SOIC-8 used in the previous example with the 3x3 mm MLP package with  $\Psi_{JB} = 3.5^{\circ}$ C/W. The 3x3 mm MLP package could operate at a PCB temperature of 118°C, while maintaining the junction temperature below 120°C. This illustrates that the physically smaller MLP package with thermal pad offers a more conductive path to remove the heat from the driver. Consider tradeoffs between reducing overall circuit size with junction temperature reduction for increased reliability.

| Туре       | Part<br>Number | Gate Drive <sup>(16)</sup><br>(Sink/Src) | Input<br>Threshold       | Logic                                                                            | Package       |

|------------|----------------|------------------------------------------|--------------------------|----------------------------------------------------------------------------------|---------------|

| Single 1 A | FAN3111C       | +1.1 A / -0.9 A                          | CMOS                     | Single Channel of Dual-Input/Single-Output                                       | SOT23-5, MLP6 |

| Single 1 A | FAN3111E       | +1.1 A / -0.9 A                          | External <sup>(17)</sup> | Single Non-Inverting Channel with External Reference                             | SOT23-5, MLP6 |

| Single 2 A | FAN3100C       | +2.5 A / -1.8 A                          | CMOS                     | Single Channel of Two-Input/One-Output                                           | SOT23-5, MLP6 |

| Single 2 A | FAN3100T       | +2.5 A / -1.8 A                          | TTL                      | Single Channel of Two-Input/One-Output                                           | SOT23-5, MLP6 |

| Single 2 A | FAN3180        | +2.4 A / -1.6 A                          | TTL                      | Single Non-Inverting Channel + 3.3-V LDO                                         | SOT23-5       |

| Dual 2 A   | FAN3216T       | +2.4 A / -1.6 A                          | TTL                      | Dual Inverting Channels                                                          | SOIC8         |

| Dual 2 A   | FAN3217T       | +2.4 A / -1.6 A                          | TTL                      | Dual Non-Inverting Channels                                                      | SOIC8         |

| Dual 2 A   | FAN3226C       | +2.4 A / -1.6 A                          | CMOS                     | Dual Inverting Channels + Dual Enable                                            | SOIC8, MLP8   |

| Dual 2 A   | FAN3226T       | +2.4 A / -1.6 A                          | TTL                      | Dual Inverting Channels + Dual Enable                                            | SOIC8, MLP8   |

| Dual 2 A   | FAN3227C       | +2.4 A / -1.6 A                          | CMOS                     | Dual Non-Inverting Channels + Dual Enable                                        | SOIC8, MLP8   |

| Dual 2 A   | FAN3227T       | +2.4 A / -1.6 A                          | TTL                      | Dual Non-Inverting Channels + Dual Enable                                        | SOIC8, MLP8   |

| Dual 2 A   | FAN3228C       | +2.4 A / -1.6 A                          | CMOS                     | Dual Channels of Two-Input/One-Output, Pin Config.1                              | SOIC8, MLP8   |

| Dual 2 A   | FAN3228T       | +2.4 A / -1.6 A                          | TTL                      | Dual Channels of Two-Input/One-Output, Pin Config.1                              | SOIC8, MLP8   |

| Dual 2 A   | FAN3229C       | +2.4 A / -1.6 A                          | CMOS                     | Dual Channels of Two-Input/One-Output, Pin Config.2                              | SOIC8, MLP8   |

| Dual 2 A   | FAN3229T       | +2.4 A / -1.6 A                          | TTL                      | Dual Channels of Two-Input/One-Output, Pin Config.2                              | SOIC8, MLP8   |

| Dual 2 A   | FAN3268T       | +2.4 A / -1.6 A                          | TTL                      | 20 V Non-Inverting Channel (NMOS) and Inverting<br>Channel (PMOS) + Dual Enables | SOIC8         |

| Dual 2 A   | FAN3278T       | +2.4 A / -1.6 A                          | TTL                      | 30 V Non-Inverting Channel (NMOS) and Inverting<br>Channel (PMOS) + Dual Enables | SOIC8         |

| Dual 4 A   | FAN3213T       | +2.5 A / -1.8 A                          | TTL                      | Dual Inverting Channels                                                          | SOIC8         |

| Dual 4 A   | FAN3214T       | +2.5 A / -1.8 A                          | TTL                      | Dual Non-Inverting Channels                                                      | SOIC8         |

| Dual 4 A   | FAN3223C       | +4.3 A / -2.8 A                          | CMOS                     | Dual Inverting Channels + Dual Enable                                            | SOIC8, MLP8   |

| Dual 4 A   | FAN3223T       | +4.3 A / -2.8 A                          | TTL                      | Dual Inverting Channels + Dual Enable                                            | SOIC8, MLP8   |

| Dual 4 A   | FAN3224C       | +4.3 A / -2.8 A                          | CMOS                     | Dual Non-Inverting Channels + Dual Enable                                        | SOIC8, MLP8   |

| Dual 4 A   | FAN3224T       | +4.3 A / -2.8 A                          | TTL                      | Dual Non-Inverting Channels + Dual Enable                                        | SOIC8, MLP8   |

| Dual 4 A   | FAN3225C       | +4.3 A / -2.8 A                          | CMOS                     | Dual Channels of Two-Input/One-Output                                            | SOIC8, MLP8   |

| Dual 4 A   | FAN3225T       | +4.3 A / -2.8 A                          | TTL                      | Dual Channels of Two-Input/One-Output                                            | SOIC8, MLP8   |

| Single 9 A | FAN3121C       | +9.7 A / -7.1 A                          | CMOS                     | Single Inverting Channel + Enable                                                | SOIC8, MLP8   |

| Single 9 A | FAN3121T       | +9.7 A / -7.1 A                          | TTL                      | Single Inverting Channel + Enable                                                | SOIC8, MLP8   |

| Single 9 A | FAN3122T       | +9.7 A / -7.1 A                          | CMOS                     | Single Non-Inverting Channel + Enable                                            | SOIC8, MLP8   |

| Single 9 A | FAN3122C       | +9.7 A / -7.1 A                          | TTL                      | Single Non-Inverting Channel + Enable                                            | SOIC8, MLP8   |

| Dual 12 A  | FAN3240        | +12.0 A                                  | TTL                      | Dual-Coil Relay Driver, Timing Config. 0                                         | SOIC8         |

| Dual 12 A  | FAN3241        | +12.0 A                                  | TTL                      | Dual-Coil Relay Driver, Timing Config. 1                                         | SOIC8         |

16. Typical currents with OUTx at 6 V and  $V_{DD}$ =12 V.

17. Thresholds proportional to an externally supplied reference voltage.

FAN3226 / FAN3227 / FAN3228 / FAN3229 — Dual 2-A High-Speed, Low-Side Gate Drivers