Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

March 2011

# FAN5026 Dual DDR / Dual-Output PWM Controller

#### **Features**

- Highly Flexible, Dual Synchronous Switching PWM Controller that Includes Modes for:

- DDR Mode with In-phase Operation for Reduced Channel Interference

- 90° Phase-shifted, Two-stage DDR Mode for Reduced Input Ripple

- Dual Independent Regulators, 180° Phase Shifted

- Complete DDR Memory Power Solution

- V<sub>TT</sub> Tracks V<sub>DDQ/2</sub>

- V<sub>DDQ/2</sub> Buffered Reference Output

- Lossless Current Sensing on Low-Side MOSFET or Precision Over-Current Using Sense Resistor

- V<sub>CC</sub> Under-Voltage Lockout

- Wide Input Range: 3V to 16V

- Excellent Dynamic Response with Voltage Feedforward and Average Current-Mode Control

- Power-Good Signal

- Supports DDR-II and HSTL

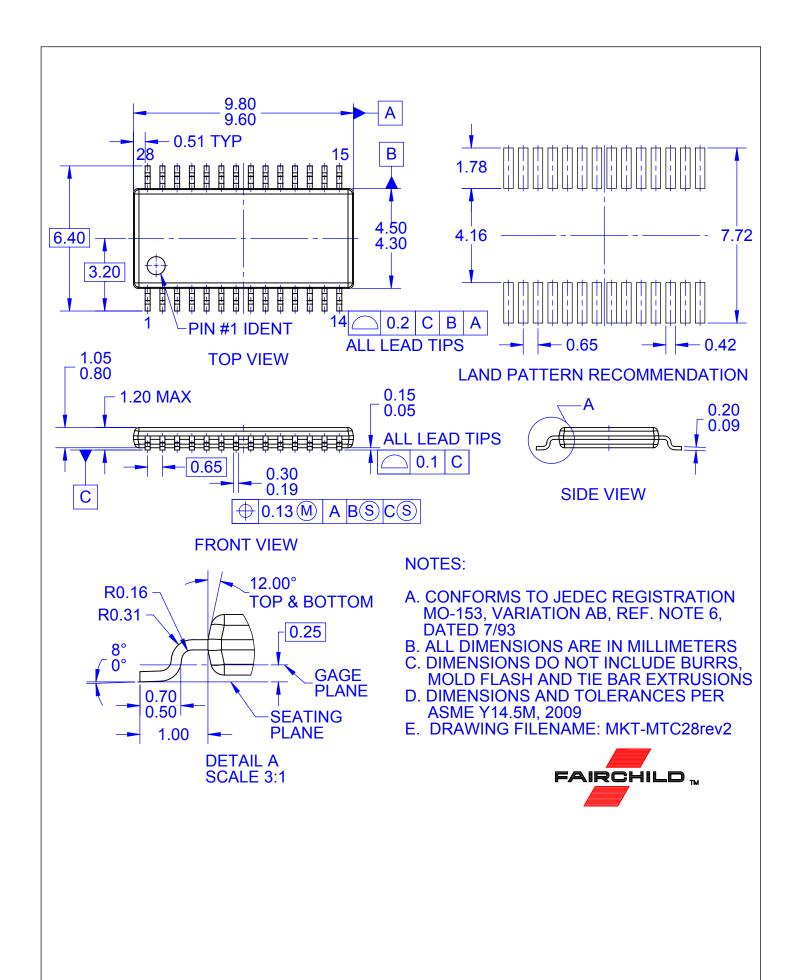

- 28-Lead Thin-Shrink Small-Outline Package

## **Applications**

- DDR V<sub>DDQ</sub> and V<sub>TT</sub> Voltage Generation

- PC Dual Power Supply

- Server DDR Power

- Desktop Computer

- Graphics Cards

## Description

The FAN5026 PWM controller provides high efficiency and regulation for two output voltages adjustable in the range of 0.9V to 5.5V required to power I/O, chip-sets, and memory banks in high-performance computers, set-top boxes, and VGA cards. Synchronous rectification and hysteretic operation at light loads contribute to high efficiency over a wide range of loads. Efficiency is enhanced by using MOSFET R<sub>DS(ON)</sub> as a current-sense component.

Feedforward ramp modulation, average-current mode control, and internal feedback compensation provide fast response to load transients. Out-of-phase operation with 180-degree phase shift reduces input current ripple. The controller can be transformed into a complete DDR memory power supply solution by activating a designated pin. In DDR Mode, one of the channels tracks the output voltage of another channel and provides output current sink and source capability — essential for proper powering of DDR chips. The buffered reference voltage required by this type of memory is also provided. The FAN5026 monitors these outputs and generates separate PGx (power good) signals when the soft-start is completed and the output is within ±10% of the set point.

Over-voltage protection prevents the output voltage from exceeding 120% of the set point. Normal operation is automatically restored when over-voltage conditions cease. Under-voltage protection latches the chip off when output drops below 75% of the set value after the soft-start sequence for this output is completed. An adjustable over-current function monitors the output current by sensing the voltage drop across the lower MOSFET. If precision current-sensing is required, an external current-sense resistor may be used.

## **Related Resources**

Application Note — AN-6002 Component Calculations and Simulation Tools

## **Ordering Information**

| Part Number | Operating<br>Temperature<br>Range | Package                                           | Packing Method |

|-------------|-----------------------------------|---------------------------------------------------|----------------|

| FAN5026MTCX | -40 to +85°C                      | 28-Lead Thin-Shrink Small-Outline Package (TSSOP) | Tape and Reel  |

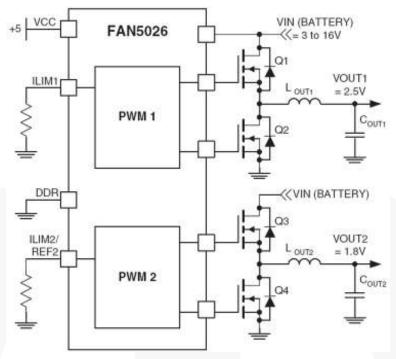

# **Block Diagrams**

Figure 1. Dual-Output Regulator

Figure 2. Typical Application

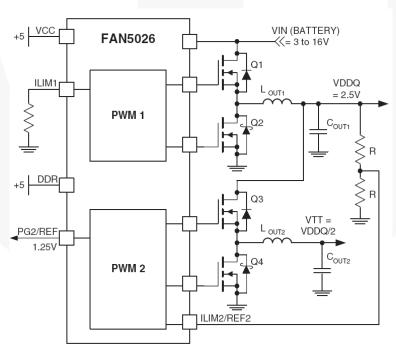

# **Pin Configuration**

Figure 3. TSSOP-28

## **Pin Definitions**

| Pin# | Name  | Description                                                                                                                                                                                     |  |  |  |  |  |  |

|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1    | AGND  | <b>Analog Ground</b> . This is the signal ground reference for the IC. All voltage levels are measured with respect to this pin                                                                 |  |  |  |  |  |  |

| 2    | LDRV1 | ow-Side Drive. The low-side (lower) MOSFET driver output. Connect to gate of low-side                                                                                                           |  |  |  |  |  |  |

| 27   | LDRV2 | MOSFET.                                                                                                                                                                                         |  |  |  |  |  |  |

| 3    | PGND1 | Power Ground. The return for the low-side MOSFET driver. Connect to source of low-side                                                                                                          |  |  |  |  |  |  |

| 26   | PGND2 | MOSFET.                                                                                                                                                                                         |  |  |  |  |  |  |

| 4    | SW1   | Switching Node. Return for the high-side MOSFET driver and a current sense input. Connect                                                                                                       |  |  |  |  |  |  |

| 25   | SW2   | to source of high-side MOSFET and low-side MOSFET drain.                                                                                                                                        |  |  |  |  |  |  |

| 5    | HDRV1 | High-Side Drive. High-side (upper) MOSFET driver output. Connect to gate of high-side                                                                                                           |  |  |  |  |  |  |

| 24   | HDRV2 | MÖSFET.                                                                                                                                                                                         |  |  |  |  |  |  |

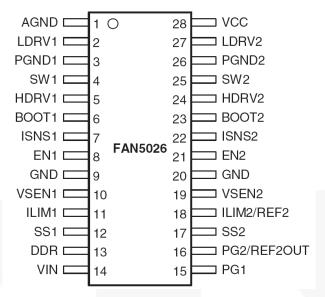

| 6    | BOOT1 | BOOT. Positive supply for the upper MOSFET driver. Connect as shown in Figure 4.                                                                                                                |  |  |  |  |  |  |

| 23   | BOOT2 |                                                                                                                                                                                                 |  |  |  |  |  |  |

| 7    | ISNS1 | Current-Sense Input. Monitors the voltage drop across the lower MOSFET or external sense                                                                                                        |  |  |  |  |  |  |

| 22   | ISNS2 | resistor for current feedback.                                                                                                                                                                  |  |  |  |  |  |  |

| 8    | EN1   | <b>Enable</b> . Enables operation when pulled to logic HIGH. Toggling EN resets the regulator after a latched fault condition. These are CMOS inputs whose state is indeterminate if left open. |  |  |  |  |  |  |

| 21   | EN2   |                                                                                                                                                                                                 |  |  |  |  |  |  |

| 9    | GND   | Ground                                                                                                                                                                                          |  |  |  |  |  |  |

| 20   | GND   | Giodila                                                                                                                                                                                         |  |  |  |  |  |  |

| 10   | VSEN1 | Output Voltage Sense. The feedback from the outputs; used for regulation as well as PG,                                                                                                         |  |  |  |  |  |  |

| 19   | VSEN2 | under-voltage, and over-voltage protection and monitoring.                                                                                                                                      |  |  |  |  |  |  |

Continued on the following page...

## **Pin Definitions**

| Pin # | Name    | Description                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 11    | ILIM1   | Current Limit 1. A resistor from this pin to GND sets the current limit.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 12    | SS1     | Soft Start. A capacitor from this pin to GND programs the slew rate of the converter during                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 17    | SS2     | initialization. During initialization, this pin is charged with a 5mA current source.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 13    | DDR     | <b>DDR Mode Control</b> . HIGH = DDR Mode. LOW = two separate regulators operating 180 degrees out of phase.                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 14    | VIN     | <b>Input Voltage</b> . Normally connected to the battery, providing voltage feedforward to set the amplitude of the internal oscillator ramp. When using the IC for two-step conversion from 5V input, connect through $100 \mathrm{K}\Omega$ resistor to ground, which sets the appropriate ramp gain and synchronizes the channels $90^\circ$ out of phase. |  |  |  |  |  |

| 15    | PG1     | <b>Power-Good Flag</b> . An open-drain output that pulls LOW when $V_{\text{SEN}}$ is outside a $\pm 10\%$ range of the 0.9V reference.                                                                                                                                                                                                                       |  |  |  |  |  |

| 16    | PG2 /   | <b>Power-Good 2</b> . When not in DDR Mode, open-drain output that pulls LOW when the V <sub>OUT</sub> is out of regulation or in a fault condition.                                                                                                                                                                                                          |  |  |  |  |  |

| 16    | REF2OUT | <b>Reference Out 2</b> . When in DDR Mode, provides a buffered output of REF2. Typically used as the V <sub>DDQ/2</sub> reference.                                                                                                                                                                                                                            |  |  |  |  |  |

| 18    | ILIM2 / | Current Limit 2. When not in DDR Mode, a resistor from this pin to GND sets the current limit.                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 10    | REF2    | Reference for reg #2 when in DDR Mode. Typically set to V <sub>OUT1/2</sub> .                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 28    | VCC     | VCC. This pin powers the chip as well as the LDRV buffers. The IC starts to operate when voltage on this pin exceeds 4.6V (UVLO rising) and shuts down when it drops below 4.3V (UVLO falling).                                                                                                                                                               |  |  |  |  |  |

# **Block Diagram**

© 2005 Fairchild Semiconductor Corporation FAN5026 • Rev. 1.0.8

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                               | Min. | Max.                 | Unit |

|------------------|-----------------------------------------|------|----------------------|------|

| V <sub>CC</sub>  | V <sub>CC</sub> Supply Voltage          |      | 6.5                  | V    |

| V <sub>IN</sub>  | V <sub>IN</sub> Supply Voltage          |      | 18                   | V    |

|                  | BOOT, SW, ISNS, HDRV                    |      | 24                   | V    |

|                  | BOOTx to SWx                            |      | 6.5                  | V    |

|                  | All Other Pins                          | -0.3 | V <sub>CC</sub> +0.3 | V    |

| TJ               | Junction Temperature                    | -40  | +150                 | °C   |

| T <sub>STG</sub> | Storage Temperature                     | -65  | +150                 | °C   |

| TL               | Lead Temperature (Soldering,10 Seconds) |      | +300                 | °C   |

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter                               | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------------------------|------|------|------|------|

| $V_{CC}$        | V <sub>CC</sub> Supply Voltage          | 4.75 | 5.00 | 5.25 | V    |

| V <sub>IN</sub> | V <sub>IN</sub> Supply Voltage          |      |      | 16   | V    |

| T <sub>A</sub>  | Ambient Temperature                     | -40  |      | +85  | °C   |

| $\Theta_{JA}$   | Thermal Resistance, Junction to Ambient |      |      | 90   | °C/W |

## **Electrical Characteristics**

Recommended operating conditions, unless otherwise noted.

| Symbol              | Parameter                         | Conditions                                                      | Min.  | Тур.  | Max.     | Units             |

|---------------------|-----------------------------------|-----------------------------------------------------------------|-------|-------|----------|-------------------|

| Power Sup           | pplies                            |                                                                 |       | •     |          |                   |

| Ivcc                | V <sub>CC</sub> Current           | LDRV, HDRV Open, V <sub>SEN</sub> Forced Above Regulation Point |       | 2.2   | 3.0      | μA                |

|                     |                                   | Shutdown (EN-0)                                                 |       |       | 30       | μA                |

| I <sub>SINK</sub>   | V <sub>IN</sub> Current, Sinking  | V <sub>IN</sub> = 15V                                           | 10    |       | 30       | μA                |

| I <sub>SOURCE</sub> | V <sub>IN</sub> Current, Sourcing | V <sub>IN</sub> = 0V                                            |       | -15   | -30      | μA                |

| I <sub>SD</sub>     | V <sub>IN</sub> Current, Shutdown |                                                                 |       |       | 1        | μA                |

| \/                  | LIVII O Threehold                 | Rising V <sub>CC</sub>                                          | 4.30  | 4.55  | 4.75     | V                 |

| $V_{UVLO}$          | UVLO Threshold                    | Falling                                                         | 4.10  | 4.25  | 4.45     | V                 |

| V <sub>UVLOH</sub>  | UVLO Hysteresis                   |                                                                 |       | 300   |          | mV                |

| Oscillator          |                                   |                                                                 |       |       |          |                   |

| f <sub>osc</sub>    | Frequency                         |                                                                 | 255   | 300   | 345      | KHz               |

|                     | - · · · · ·                       | V <sub>IN</sub> = 16V                                           |       | 2     |          | V                 |

| $V_{PP}$            | Ramp Amplitude                    | V <sub>IN</sub> = 5V                                            |       | 1.25  |          | V                 |

| V <sub>RAMP</sub>   | Ramp Offset                       |                                                                 |       | 0.5   |          | V                 |

|                     |                                   | $V_{IN} \leq 3V$                                                |       | 125   |          | mV/V              |

| G                   | Ramp / V <sub>IN</sub> Gain       | 1V < V <sub>IN</sub> < 3V                                       |       | 250   |          | mV/V              |

| Reference           | and Soft-Start                    |                                                                 |       |       |          |                   |

| V <sub>REF</sub>    | Internal Reference Voltage        |                                                                 | 0.891 | 0.900 | 0.909    | V                 |

| I <sub>SS</sub>     | Soft-Start Current                | At Startup                                                      |       | 5     |          | μA                |

| V <sub>SS</sub>     | Soft-Start Complete Threshold     |                                                                 |       | 1.5   |          | V                 |

| PWM Con             |                                   |                                                                 | 1     |       | <b>I</b> |                   |

|                     | Load Regulation                   | I <sub>OUTX</sub> from 0 to 5A, V <sub>IN</sub> from 5 to 15V   | -2    |       | +2       | %                 |

| I <sub>SEN</sub>    | V <sub>SEN</sub> Bias Current     | Tool x norm of to or s, vin morn of to to to                    | 50    | 80    | 120      | nA                |

| UVLO <sub>TSD</sub> | Under-Voltage Shutdown            | % of Set Point, 2µs Noise Filter                                | 70    | 75    | 80       | %                 |

| UVLO                | Over-Voltage Threshold            | % of Set Point, 2µs Noise Filter                                | 115   | 120   | 125      | %                 |

| I <sub>SNS</sub>    | Over-Current Threshold            | $R_{\text{ILIM}}$ = 68.5K $\Omega$ , Figure 12                  | 112   | 140   | 168      | μA                |

| TONO                | Minimum Duty Cycle                | THEIM CO.O. G. S. F. I I GATO 12                                | 10    | 1.0   | 100      | %                 |

| Output Dri          |                                   | <u> </u>                                                        | 10    |       | )<br>7   | 70                |

| Output Di           |                                   | Sourcing                                                        |       | 12    | 15       |                   |

|                     | HDRV Output Resistance            | Sinking                                                         |       | 2.4   | 4.0      | Ω                 |

|                     |                                   | Sourcing                                                        |       | 12    | 15       |                   |

|                     | LDRV Output Resistance            | Sinking                                                         |       | 1.2   | 2.0      | Ω                 |

| Power-Go            | od Output and Control Pins        | Cintally                                                        | 1     | 1.2   | 2.0      |                   |

| . 51161-50          | Lower Threshold                   | % of Set Point, 2µs Noise Filter                                | -86   |       | -94      | %                 |

|                     | Upper Threshold                   | % of Set Point, 2µs Noise Filter                                | 108   |       | 116      | %                 |

|                     | PG Output Low                     | IPG = 4mA                                                       | 100   |       | 0.5      | 70<br>V           |

|                     | Leakage Current                   | V <sub>PULLUP</sub> = 5V                                        | +     |       | 1        | μA                |

|                     | -                                 |                                                                 | +     |       |          | μA<br>%           |

|                     | PG2/REF2OUT Voltage               | DDR = 1, 0 mA < I <sub>REF2OUT</sub> ≤10mA                      | 99.00 |       | 1.01     | V <sub>REF2</sub> |

| DDR, EN I           | nputs                             | <u>,                                      </u>                  |       | 1     |          | •                 |

| $V_{INH}$           | Input High                        |                                                                 | 2     |       |          | V                 |

| $V_{INL}$           | Input Low                         |                                                                 |       |       | 8.0      | V                 |

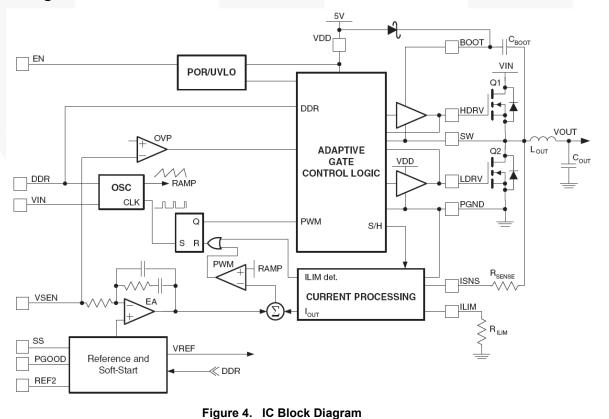

# **Typical Application**

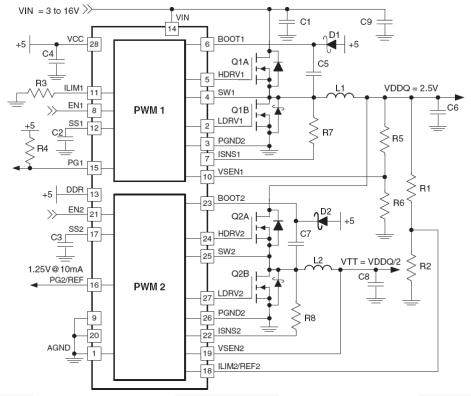

Figure 5. DDR Regulator Application

**Table 1. DDR Regulator BOM**

| Description                                      | Qty. | Ref.                    | Vendor                  | Part Number              |

|--------------------------------------------------|------|-------------------------|-------------------------|--------------------------|

| Capacitor 68μf, Tantalum, 25V, ESR 150mΩ         | 1    | C1                      | AVX                     | TPSV686*025#0150         |

| Capacitor 10nf, Ceramic                          | 2    | C2, C3                  | Any                     |                          |

| Capacitor 68μf, Tantalum, 6V, ESR 1.8Ω           | 1    | C4                      | AVX                     | TAJB686*006              |

| Capacitor 150nF, Ceramic                         | 2    | C5, C7                  | Any                     |                          |

| Capacitor 180μf, Specialty Polymer 4V, ESR 15mΩ  | 2    | C6A, C6B <sup>(1)</sup> | Panasonic               | EEFUE0G181R              |

| Capacitor 1000μf, Specialty Polymer 4V, ESR 10mΩ | 1    | C8                      | Kemet                   | T510E108(1)004AS4115     |

| Capacitor 0.1µF, Ceramic                         | 2    | C9                      | Any                     |                          |

| 1.82KΩ, 1% Resistor                              | 3    | R1, R2, R3              | Any                     |                          |

| 56.2KΩ, 1% Resistor                              | 1    | R3                      | Any                     |                          |

| 10K $\Omega$ , 5% Resistor                       | 2    | R4                      | Any                     |                          |

| 3.24KΩ, 1% Resistor                              | 1    | R5                      | Any                     |                          |

| 1.5KΩ, 1% Resistor                               | 2    | R7, R8                  | Any                     | 7 D 1                    |

| Schottky Diode 30V                               | 2    | D1, D2                  | Fairchild Semiconductor | BAT54                    |

| Inductor 6.4 $\mu$ H, 6A, 8.64 $m\Omega$         | 1    | L1                      | Panasonic               | ETQ-P6F6R4HFA            |

| Inductor 0.8μH, 6A, 2.24mΩ                       | 1    | L2                      | Panasonic               | ETQ-P6F0R8LFA            |

| Dual MOSFET with Schottky                        | 2    | Q1, Q2                  | Fairchild Semiconductor | FDS6986AS <sup>(2)</sup> |

| DDR Controller                                   | 1    | U1                      | Fairchild Semiconductor | FAN5026                  |

## Notes:

- 1.  $C6 = 2 \times 180 \mu F$  in parallel.

- 2. Suitable for typical notebook computer application of 4A continuous, 6A peak for V<sub>DDQ</sub>. If continuous operation above 6A is required, use single SO-8 packages. For more information, refer to the Power MOSFET Selection Section and use AN-6002 for design calculations.

## Typical Applications (Continued)

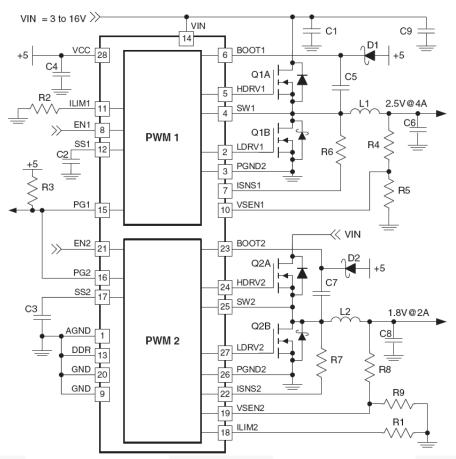

Figure 6. Dual Regulator Application

Table 2. Dual Regulator BOM

| Description                                           | Qty. | Ref.       | Vendor                  | Part Number              |

|-------------------------------------------------------|------|------------|-------------------------|--------------------------|

| Capacitor 68 $\mu$ f, Tantalum, 25V, ESR 95m $\Omega$ | 1    | C1         | AVX                     | TPSV686*025#095          |

| Capacitor 10nf, Ceramic                               | 2    | C2, C3     | Any                     |                          |

| Capacitor 68μf, Tantalum, 6V, ESR 1.8Ω                | 1    | C4         | AVX                     | TAJB686*006              |

| Capacitor 150nF, Ceramic                              | 2    | C5, C7     | Any                     |                          |

| Capacitor 330μf, Poscap, 4V, ESR 40mΩ                 | 2    | C6, C8     | Sanyo                   | 4TPB330ML                |

| Capacitor 0.1µF, Ceramic                              | 2    | C9         | Any                     |                          |

| 56.2KΩ, 1% Resistor                                   | 1    | R1, R2     | Any                     |                          |

| 10KΩ, 5% Resistor                                     | 1    | R3         | Any                     |                          |

| 3.24KΩ, 1% Resistor                                   | 1    | R4         | Any                     |                          |

| 1.82KΩ, 1% Resistor                                   | 3    | R5, R8, R9 | Any                     |                          |

| 1.5KΩ, 1% Resistor                                    | 2    | R6, R7     | Any                     |                          |

| Schottky Diode 30V                                    | 2    | D1, D2     | Fairchild Semiconductor | BAT54                    |

| Inductor 6.4μH, 6A, 8.64mΩ                            | 2    | L1, L2     | Panasonic               | ETQ-P6F6R4HFA            |

| Dual MOSFETs with Schottky                            | 1    | Q1, Q2     | Fairchild Semiconductor | FDS6986AS <sup>(3)</sup> |

| DDR Controller                                        | 1    | U1         | Fairchild Semiconductor | FAN5026                  |

## Note:

3. If currents above 4A continuous are required, use single SO-8 packages. For more information, refer to the Power MOSFET Selection Section and AN-6002 for design calculations.

## **Circuit Description**

#### Overview

The FAN5026 is a multi-mode, dual-channel PWM controller intended for graphic chipset, SDRAM, DDR DRAM, or other low-voltage power applications in modern notebook, desktop, and sub-notebook PCs. The IC integrates control circuitry for two synchronous buck converters. The output voltage of each controller can be set in the range of 0.9V to 5.5V by an external resistor divider.

The two synchronous buck converters can operate from an unregulated DC source (such as a notebook battery), with voltage ranging from 5.0V to 16V, or from a regulated system rail of 3.3V to 5.0V. In either mode, the IC is biased from a +5V source. The PWM modulators use an average current-mode control with input voltage feedforward for simplified feedback loop compensation and improved line regulation. Both PWM controllers have integrated feedback loop compensation that reduces the external components needed.

The FAN5026 can be configured to operate as a complete DDR solution. When the DDR pin is set HIGH, the second channel provides the capability to track the output voltage of the first channel. The PWM2 converter is prevented from going into Hysteretic Mode if the DDR pin is HIGH. In DDR Mode, a buffered reference voltage (buffered voltage of the REF2 pin), required by DDR memory chips, is provided by the PG2 pin.

## **Converter Modes and Synchronization**

**Table 3. Converter Modes and Synchronization**

| Mode | V <sub>IN</sub> | VIN<br>Pin      | DDR<br>Pin | PWM 2<br>w.r.t.<br>PWM1 |

|------|-----------------|-----------------|------------|-------------------------|

| DDR1 | Battery         | V <sub>IN</sub> | HIGH       | IN PHASE                |

| DDR2 | +5V             | R to<br>GND     | HIGH       | +90°                    |

| DUAL | ANY             | V <sub>IN</sub> | LOW        | +180°                   |

When used as a dual converter, as shown in Figure 6, out-of-phase operation with 180-degree phase shift reduces input current ripple.

For "two-step" conversion (where the  $V_{TT}$  is converted from  $V_{DDQ}$  as in Figure 5) used in DDR Mode, the duty cycle of the second converter is nominally 50% and the optimal phasing depends on  $V_{IN}$ . The objective is to keep noise generated from the switching transition in one converter from influencing the "decision" to switch in the other converter.

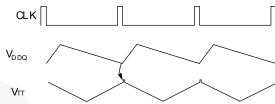

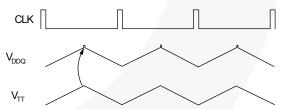

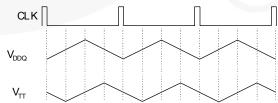

When  $V_{\text{IN}}$  is from the battery, it's typically higher than 7.5V. As shown in Figure 7, 180° operation is undesirable because the turn-on of the  $V_{\text{DDQ}}$  converter occurs very near the decision point of the  $V_{\text{TT}}$  converter.

Figure 7. Noise-Susceptible 180° Phasing for DDR1

In-phase operation is optimal to reduce inter-converter interference when  $V_{IN}$  is higher than 5V, (when  $V_{IN}$  is from a battery), as shown in Figure 8. Because the duty cycle of PWM1 (generating  $V_{DDQ}$ ) is short, the switching point occurs far away from the decision point for the  $V_{TT}$  regulator, whose duty cycle is nominally 50%.

Figure 8. Optimal In-Phase Operation for DDR1

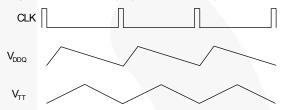

When  $V_{\text{IN}} \approx 5V$ ,  $180^{\circ}$  phase-shifted operation can be rejected for the reasons demonstrated in Figure 7.

In-phase operation with  $V_{\text{IN}}\approx 5V$  is even worse, since the switch point of either converter occurs near the switch point of the other converter, as seen in Figure 9. In this case, as  $V_{\text{IN}}$  is a little higher than 5V, it tends to cause early termination of the  $V_{TT}$  pulse width. Conversely, the  $V_{TT}$  switch point can cause early termination of the  $V_{\text{DDQ}}$  pulse width when  $V_{\text{IN}}$  is slightly lower than 5V.

Figure 9. Noise-Susceptible In-Phase Operation for DDR2

These problems are solved by delaying the second converter's clock by  $90^\circ$ , as shown in Figure 10. In this way, all switching transitions in one converter take place far away from the decision points of the other converter.

Figure 10. Optimal 90° Phasing for DDR2

## **Initialization and Soft Start**

Assuming EN is HIGH, FAN5026 is initialized when  $V_{\rm CC}$  exceeds the rising UVLO threshold. Should  $V_{\rm CC}$  drop below the UVLO threshold, an internal power-on reset function disables the chip.

The voltage at the positive input of the error amplifier is limited by the voltage at the SS pin, which is charged with a  $5\mu$ A current source. Once  $C_{SS}$  has charged to  $V_{REF}$  (0.9V) the output voltage is in regulation. The time it takes SS to reach 0.9V is:

$$t_{0.9} = \frac{0.9 \times C_{SS}}{5} \tag{1}$$

where  $t_{0.9}$  is in seconds if  $C_{SS}$  is in  $\mu F$ .

When SS reaches 1.5V, the power-good outputs are enabled and Hysteretic Mode is allowed. The converter is forced into PWM Mode during soft-start.

## **Current Processing Section**

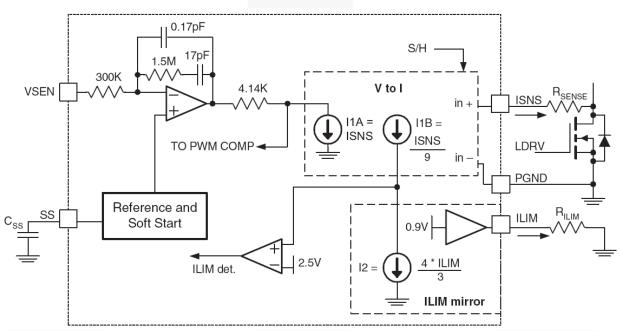

The following discussion refers to Figure 12.

The current through the  $R_{SENSE}$  resistor ( $I_{SNS}$ ) is sampled (typically 400ns) after Q2 is turned on, as shown in Figure 12. That current is held and summed with the output of the error amplifier. This effectively creates a current-mode control loop. The resistor connected to ISNSx pin ( $R_{SENSE}$ ) sets the gain in the current feedback loop. For stable operation, the voltage induced by the current feedback at the PWM comparator input should be set to 30% of the ramp amplitude at maximum load current and line voltage. The following expression estimates the recommended value of  $R_{SENSE}$  as a function of the maximum load current ( $I_{LOAD(MAX)}$ ) and the value of the MOSFET  $R_{DS(ON)}$ :

$$R_{SENSE} = \frac{I_{LOAD\,(MAX)} \cdot R_{DS\,(ON)} \cdot 4.1K}{30\% \cdot 0.125 \cdot V_{IN\,(MAX)}} - 100 \tag{2a}$$

R<sub>SENSE</sub> must, however, be kept higher than:

$$R_{SENSE} = \frac{I_{LOAD(MAX)} \cdot R_{DS(ON)}}{150 \,\mu A} - 100 \tag{2b}$$

The  $100\Omega$  is the internal resistor in series with the ISNSx pins and has  $\pm 15\%$  typical variation. Because  $R_{\text{SENSE}}$  is in series with the internal  $100\Omega$  resistor, the gain in the current feedback loop and the current limit accuracy is affected if  $R_{\text{SENSE}}$  is close to  $100\Omega$ .

## **Setting the Current Limit**

A ratio of  $I_{SNS}$  is compared to the current established when a 0.9V internal reference drives the ILIM pin. The threshold is determined as follows:

$$\frac{ISNS}{9} = \frac{4}{3}ILIM \text{ or } ISNS = 12 \cdot ILIM$$

(3a)

Since

$$ISNS = \frac{I_{LOAD} \cdot R_{DS(ON)}}{100 + R_{SENSE}}$$

(3b)

and at the ILIM 0.9V threshold:

$$ISNS = 12 \cdot \frac{0.9}{R_{ILIM}} = \frac{10.8}{R_{ILIM}}$$

(3c)

therefore:

$$I_{LOAD} = \frac{10.8}{R_{ILIM}} \cdot \frac{100 + R_{SENSE}}{R_{DS(ON)}}$$

(3d)

Current limit ( $I_{LIMIT}$ ) should be set high enough to allow inductor current to rise in response to an output load transient. Typically, a factor of 1.2 is sufficient. In addition, since  $I_{LIMIT}$  is a peak current cut-off value, multiply  $I_{LOAD(MAX)}$  by the inductor ripple current (e.g. 25%). For example, in Figure 6, the target for  $I_{LIMIT}$ :

$I_{LIMIT} > 1.2 \times 1.25 \times 1.6 \times 2A \approx 5A$

$$R_{ILIM} = \frac{10.8}{I_{LIMIT}} \cdot \frac{100 + R_{SENSE}}{R_{DS(ON)}} \tag{4}$$

Since the tolerance on the current limit is largely dependent on the ratio of the external resistors, it is fairly accurate if the voltage drop on the switching-node side of  $R_{\text{SENSE}}$  is an accurate representation of the load current. When using the MOSFET as the sensing element, the variation of  $R_{\text{DS}(\text{ON})}$  causes proportional variation in the  $l_{\text{SNS}}$ . This value varies from device to device and has a typical junction temperature coefficient of about  $0.4\%^{\circ}\text{C}$  (consult the MOSFET datasheet for actual values), so the actual current limit set point decreases proportional to increasing MOSFET die temperature. A factor of 1.6 in the current limit set point should compensate for MOSFET  $R_{\text{DS}(\text{ON})}$  variations, assuming the MOSFET heat sinking keeps its operating die temperature below 125°C.

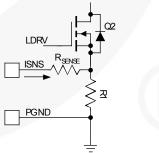

Figure 11. Improving Current-Sensing Accuracy

More accurate sensing can be achieved by using a resistor (R1) instead of the  $R_{DS(ON)}$  of the FET, as shown in Figure 11. This approach causes higher losses, but yields greater accuracy in both  $V_{DROOP}$  and  $I_{LIMIT}.\ R1$  is a low value resistor (e.g.  $10m\Omega).$

## **Duty Cycle Clamp**

During severe load increase, the error amplifier output can go to its upper limit, pushing a duty cycle to almost 100% for significant amount of time. This could cause a large increase of the inductor current and lead to a long recovery from a transient, over-current condition, or even to a failure at especially high input voltages. To prevent this, the output of the error amplifier is clamped to a fixed value after two clock cycles if severe output

voltage excursion is detected, limiting the maximum duty cycle to:

$$DC_{MAX} = \frac{V_{OUT}}{V_{IN}} + \left(\frac{2.4}{V_{IN}}\right)$$

(5)

This is designed to not interfere with normal PWM operation. When FPWM is grounded, the duty cycle clamp is disabled and the maximum duty cycle is 87%.

Figure 12. Current Limit / Summing Circuits

#### **Gate Driver Section**

The adaptive gate control logic translates the internal PWM control signal into the MOSFET gate drive signals, providing necessary amplification, level shifting, and shoot-through protection. Also, it has functions that optimize the IC performance over a wide range of operating conditions. Since MOSFET switching time can vary dramatically from type to type and with the input voltage, the gate control logic provides adaptive dead time by monitoring the gate-to-source voltages of both upper and lower MOSFETs. The lower MOSFET drive is not turned on until the gate-to-source voltage of the upper MOSFET has decreased to less than approximately 1V. Similarly, the upper MOSFET is not turned on until the gate-to-source voltage of the lower MOSFET has decreased to less than approximately 1V. This allows a wide variety of upper and lower MOSFETs to be used without a concern for simultaneous conduction or shoot-through.

There must be a low-resistance, low-inductance path between the driver pin and the MOSFET gate for the adaptive dead-time circuit to function properly. Any delay along that path subtracts from the delay generated by the adaptive dead-time circuit and shoot-through may occur.

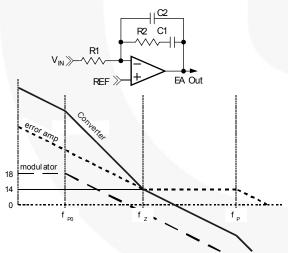

#### Frequency Loop Compensation

Due to the implemented current-mode control, the modulator has a single-pole response with -1 slope at frequency determined by load:

$$f_{PO} = \frac{1}{2\pi R_{O} C_{O}} \tag{6}$$

where R<sub>O</sub> is load resistance; C<sub>O</sub> is load capacitance.

For this type of modulator, a Type-2 compensation circuit is usually sufficient. To reduce the number of external components and simplify the design, the PWM controller has an internally compensated error amplifier. Figure 13 shows a Type-2 amplifier and its response with the responses of a current-mode modulator and the converter. The Type-2 amplifier, in addition to the pole at the origin, has a zero-pole pair that causes a flat gain region at frequencies between zero and the pole.

$$f_z = \frac{1}{2\pi R_2 C_1} = 6kHz$$

(7)

$$f_{p} = \frac{1}{2\pi R_{2}C_{2}} = 600kHz$$

(8)

This region is also associated with phase "bump" or reduced phase shift. The amount of phase-shift reduction depends on the width of the region of flat gain and has a maximum value of  $90^\circ.$  To further simplify the converter compensation, the modulator gain is kept independent of the input voltage variation by providing feedforward of  $V_{\text{IN}}$  to the oscillator ramp.

The zero frequency, the amplifier high-frequency gain, and the modulator gain are chosen to satisfy most typical applications. The crossover frequency appears at the point where the modulator attenuation equals the amplifier high-frequency gain. The system designer must specify the output filter capacitors to position the load main pole somewhere within a decade lower than the amplifier zero frequency. With this type of compensation, plenty of phase margin is achieved due to zero-pole pair phase "boost."

Figure 13. Compensation

Conditional stability may occur only when the main load pole is positioned too much to the left on the frequency axis due to excessive output filter capacitance. In this case, an ESR zero placed within the 10kHz to 50kHz range gives some additional phase boost. Fortunately, there is an opposite trend in mobile applications to keep the output capacitor as small as possible.

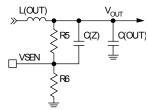

If a larger inductor value or low-ESR values are required by the application, additional phase margin can be achieved by putting a zero at the LC crossover frequency. This can be achieved with a capacitor across the feedback resistor (e.g. R5 from Figure 6), as shown in Figure 14.

Figure 14. Improving Phase Margin

The optimal value of C(Z) is:

$$C(Z) = \frac{\sqrt{L(OUT) \times C(OUT)}}{R}$$

(9)

#### **Protections**

The converter output is monitored and protected against extreme overload, short-circuit, over-voltage, and under-voltage conditions.

A sustained overload on an output sets the PGx pin LOW and latches-off the regulator on which the fault occurs. Operation can be restored by cycling the  $V_{\text{CC}}$  voltage or by toggling the EN pin.

If  $V_{\text{OUT}}$  drops below the under-voltage threshold, the regulator shuts down immediately.

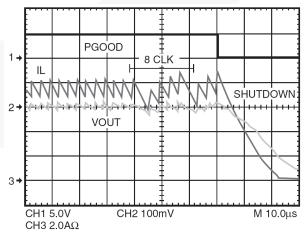

### **Over-Current Sensing**

If the circuit's current-limit signal ("ILIM det" in Figure 12) is HIGH at the beginning of a clock cycle, a pulse-skipping circuit is activated and HDRV is inhibited. The circuit continues to pulse skip in this manner for the next eight clock cycles. If, at any time from the ninth to the sixteenth clock cycle, the ILIM det is again reached; the over-current protection latch is set, disabling the regulator. If ILIM det does not occur between cycles nine and sixteen, normal operation is restored and the over-current circuit resets itself.

Figure 15. Over-Current Protection Waveforms

#### Over-Voltage / Under-Voltage Protection

Should the  $V_{\text{SNS}}$  voltage exceed 120% of  $V_{\text{REF}}$  (0.9V) due to an upper MOSFET failure or for other reasons, the over-voltage protection comparator forces LDRV HIGH. This action actively pulls down the output voltage and, in the event of the upper MOSFET failure, eventually blows the battery fuse. As soon as the output voltage drops below the threshold, the OVP comparator is disengaged.

This OVP scheme provides a "soft" crowbar function, which accommodates severe load transients and does not invert the output voltage when activated — a common problem for latched OVP schemes.

Similarly, if an output short-circuit or severe load transient causes the output to drop to less than 75% of the regulation set point, the regulator shuts down.

#### **Over-Temperature Protection**

The chip incorporates an over-temperature protection circuit that shuts the chip down if a die temperature of about 150°C is reached. Normal operation is restored at die temperature below 125°C with internal power-on reset asserted, resulting in a full soft-start cycle.

## **Design and Component Selection Guidelines**

As an initial step, define the operating input voltage range, output voltage, and minimum and maximum load currents for the controller.

## **Setting the Output Voltage**

The internal reference voltage is 0.9V. The output is divided down by a voltage divider to the VSEN pin (for example, R5 and R6 in Figure 5). The output voltage therefore is:

$$\frac{0.9V}{R6} = \frac{V_{OUT} - 0.9V}{R5}$$

(10)

To minimize noise pickup on this node, keep the resistor to GND (R6) below 2K; for example, R6 at  $1.82K\Omega$ . Then choose R5:

$$R5 = \frac{(1.82K\Omega)(V_{OUT} - 0.9)}{0.9} = 3.24K\Omega$$

(11)

For DDR applications converting from 3.3V to 2.5V or other applications requiring high duty cycles, the duty cycle clamp must be disabled by tying the converter's FPWM to GND. When converter's FPWM is at GND, the converter's maximum duty cycle is greater than 90%. When using as a DDR converter with 3.3V input, set up the converter for in-phase synchronization by tying the VIN pin to +5V.

## **Output Inductor Selection**

The minimum practical output inductor value keeps the inductor current just on the boundary of continuous conduction at some minimum load. Industry standard practice is to choose the minimum current somewhere from 15% to 35% of the nominal current. At light load, the controller can automatically switch to Hysteretic Mode to sustain high efficiency. The following equations select the proper value of the output filter inductor:

$$\Delta I = 2 \times 1_{MIN} = \frac{\Delta V_{OUT}}{ESR}$$

(12)

where  $\Delta I$  is the inductor ripple current and  $\Delta V_{\text{OUT}}$  is the maximum ripple allowed:

$$L = \frac{V_{IN} - V_{OUT}}{f_{SW} \times \Delta I} \times \frac{V_{OUT}}{V_{IN}}$$

(13)

for this example, use:

$$V_{IN} = 12, V_{OUT} = 2.5$$

$\Delta I = 25\% \cdot 6A = 1.5A$  (14)

$f_{SW} = 300 \text{KHz}$

therefore:

$$L \approx 4.4 \mu H \tag{15}$$

## **Output Capacitor Selection**

The output capacitor serves two major functions in a switching power supply. Along with the inductor, it filters the sequence of pulses produced by the switcher and it supplies the load transient currents. The requirements are usually dictated by ESR, inductor ripple current ( $\Delta I$ ), and the allowable ripple voltage ( $\Delta V$ ):

$$ESR < \frac{\Delta V}{\Delta I}$$

(16)

In addition, the capacitor's ESR must be low enough to allow the converter to stay in regulation during a load step. The ripple voltage due to ESR for the converter in Figure 6 is 120mV<sub>PP</sub>. Some additional ripple appears due to the capacitance value itself:

$$\Delta V = \frac{\Delta I}{C_{OUT} \times 8 \times f_{SW}}$$

(17)

which is only about 1.5mV for the converter in Figure 6 and can be ignored.

The capacitor must also be rated to withstand the RMS current, which is approximately  $0.3 \text{ X } (\Delta I)$ , or about 400mA, for the converter in Figure 6. High-frequency decoupling capacitors should be placed as close to the loads as physically possible.

#### **Input Capacitor Selection**

The input capacitor should be selected by its ripple current rating.

## **Two-Stage Converter Case**

In DDR Mode (Figure 5), the  $V_{TT}$  power input is powered by the  $V_{DDQ}$  output; therefore all of the input capacitor ripple current is produced by the  $V_{DDQ}$  converter. A conservative estimate of the output current required for the 2.5V regulator is:

$$I_{REGI} = I_{VDDQ} + \frac{I_{VTT}}{2}$$

(18)

As an example, if the average  $I_{VDDQ}$  is 3A and average  $I_{VTT}$  is 1A,  $I_{VDDQ}$  current is about 3.5A. If average input voltage is 16V, RMS input ripple current is:

$$I_{RMS} = I_{OUT(MAX)} \sqrt{D - D^2}$$

(19)

where D is the duty cycle of the PWM1 converter and:

$$D < \frac{V_{OUT}}{V_{IN}} = \frac{2.5}{12}$$

(20)

therefore:

$$I_{RMS} = 3.5 \sqrt{\frac{2.5}{12} - \left(\frac{2.5}{12}\right)^2} = 1.42A \tag{21}$$

## **Dual Converter 180° Phased**

In Dual Mode (shown in Figure 5), both converters contribute to the capacitor input ripple current. With each converter operating 180° out of phase, the RMS currents add in the following fashion:

$$I_{RMS} = \sqrt{I_{RMS(1)}^2 + I_{RMS(2)}^2} \text{ or}$$

(22)

$$I_{RMS} = \sqrt{(I_1)^2 (D_1 - D_1^2) + (I_2)^2 (D_2 - D_2^2)}$$

(23)

which, for the dual 3A converters of Figure 6, calculates:

$$I_{RMS} = 1.51A \tag{24}$$

#### **Power MOSFET Selection**

Losses in a MOSFET are the sum of its switching ( $P_{\text{SW}}$ ) and conduction ( $P_{\text{COND}}$ ) losses.

In typical applications, the FAN5026 converter's output voltage is low with respect to its input voltage. Therefore, the lower MOSFET (Q2) is conducting the full load current for most of the cycle. Q2 should therefore be selected to minimize conduction losses, thereby selecting a MOSFET with low  $R_{DS(ON)}$ .

In contrast, the high-side MOSFET (Q1) has a much shorter duty cycle and it's conduction loss has less impact. Q1, however, sees most of the switching losses, the primary selection criteria should be gate charge.

#### **High-Side Losses**

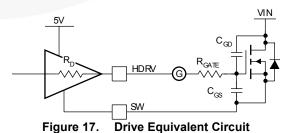

Figure 16 shows a MOSFET's switching interval, with the upper graph being the voltage and current on the drain-to-source and the lower graph detailing  $V_{\text{GS}}$  vs. time with a constant current charging the gate. The X axis, therefore, is also representative of gate charge

$(Q_{\rm G})$ .  $C_{\rm ISS}=C_{\rm GD}+C_{\rm GS}$  and it controls t1, t2, and t4 timing.  $C_{\rm GD}$  receives the current from the gate driver during t3 (as  $V_{\rm DS}$  is falling). The gate charge  $(Q_{\rm G})$  parameters on the lower graph are either specified in or can be derived from MOSFET datasheets.

Assuming switching losses are about the same for both the rising edge and falling edge, Q1's switching losses occur during the shaded time when the MOSFET has voltage across it and current through it.

These losses are given by:

$$P_{UPPER} = P_{SW} + P_{COND} \tag{25}$$

$$P_{SW} = \left(\frac{V_{DS} \times I_{L}}{2} \times 2 \times t_{S}\right) f_{SW}$$

(26)

$$P_{COND} = \frac{V_{OUT}}{V_{IN}} \times I_{OUT}^{2} \times R_{DS(ON)}$$

(27)

where:

$P_{\text{UPPER}}$  is the upper MOSFET's total losses and PsW and  $P_{\text{COND}}$  are the switching and conduction losses for a given MOSFET;

R<sub>DS(ON)</sub> is at the maximum junction temperature (T<sub>J</sub>);

and

$t_{\text{S}}$  is the switching period (rise or fall time), shown as t2 and t3 in Figure 16.

The driver's impedance and  $C_{ISS}$  determine t2, while t3's period is controlled by the driver's impedance and  $Q_{GD}$ . Since most of  $t_{S}$  occurs when  $V_{GS} = V_{SP}$ , use a constant current assumption for the driver to simplify the calculation of  $t_{S}$ :

Figure 16. Switching Losses and Q<sub>G</sub>

$$t_{s} = \frac{Q_{\text{G(SW)}}}{I_{\text{DRIVER}}} = \frac{Q_{\text{G(SW)}}}{\left(\frac{V_{\text{CC}} - V_{\text{SP}}}{R_{\text{DRIVER}} + R_{\text{GATE}}}\right)}$$

(28)

Most MOSFET vendors specify  $Q_{\text{GD}}$  and  $Q_{\text{GS.}}$   $Q_{\text{G(SW)}}$  can be determined as:

$$Q_{G(SW)} = Q_{GD} + Q_{GS} - Q_{TH}$$

(29)

where  $Q_{TH}$  is the gate charge required to get the MOSFET to it's threshold (V\_{TH}).

For the high-side MOSFET,  $V_{DS} = V_{IN}$ , which can be as high as 20V in a typical portable application. Care should be taken to include the delivery of the MOSFET's gate power (PGATE) in calculating the power dissipation required for the FAN5026:

$$P_{GATE} = Q_{G} \times V_{CC} \times f_{SW}$$

(30)

where  $Q_G$  is the total gate charge to reach  $V_{CC}$ .

## **Low-Side Losses**

Q2, however, switches on or off with its parallel Schottky diode conducting, therefore  $V_{DS} \approx 0.5V$ . Since  $P_{SW}$  is proportional to  $V_{DS}$ , Q2's switching losses are negligible and Q2 is selected based on  $R_{DS(ON)}$  only.

Conduction losses for Q2 are given by:

$$P_{COND} = (1-D) \times I_{OUT}^{2} \times R_{DS(ON)}$$

(31)

where  $R_{DS(ON)}$  is the  $R_{DS(ON)}$  of the MOSFET at the highest operating junction temperature, and:

$$D = \frac{V_{OUT}}{V_{IN}}$$

(32)

is the minimum duty cycle for the converter.

Since  $D_{\text{MIN}}$  < 20% for portable computers, (1-D)  $\approx$  1 produces a conservative result, further simplifying the calculation.

The maximum power dissipation ( $P_{D(MAX)}$ ) is a function of the maximum allowable die temperature of the low-side MOSFET; the  $\Theta_{JA}$ , and the maximum allowable ambient temperature rise:

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = \frac{\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}(\mathsf{MAX})}}{\Theta_{\mathsf{JA}}} \tag{33}$$

$\Theta_{JA}$  depends primarily on the amount of PCB area that can be devoted to heat sinking (see Application Note AN-1029, Maximum Power Enhancement Techniques for SO-8 Power MOSFETs for SO-8 MOSFET thermal information).

## **Layout Considerations**

Switching converters, even during normal operation, produce short pulses of current that could cause substantial ringing and be a source of EMI if layout constraints are not observed.

There are two sets of critical components in a DC-DC converter. The switching power components process large amounts of energy at high rates and are noise generators. The low-power components responsible for bias and feedback functions are sensitive to noise.

A multi-layer printed circuit board is recommended. Dedicate one solid layer for a ground plane. Dedicate another solid layer as a power plane and break this plane into smaller islands of common voltage levels.

Notice all the nodes that are subjected to high-dV/dt voltage swing; such as SW, HDRV, and LDRV. All surrounding circuitry tends to couple the signals from these nodes through stray capacitance. Do not oversize copper traces connected to these nodes. Do not place traces connected to the feedback components adjacent to these traces. It is not recommended to use high-density interconnect systems, or micro-vias, on these signals. The use of blind or buried vias should be limited to the low-current signals only. The use of normal thermal vias is at the discretion of the designer.

Keep the wiring traces from the IC to the MOSFET gate and source as short as possible and capable of handling peak currents of 2A. Minimize the area within the gate-source path to reduce stray inductance and eliminate parasitic ringing at the gate.

Locate small critical components, like the soft-start capacitor and current-sense resistors, as close as possible to the respective pins of the IC.

The FAN5026 utilizes advanced packaging technology with lead pitch of 0.6mm. High-performance analog semiconductors utilizing narrow lead spacing may require special considerations in design and manufacturing. It is critical to maintain proper cleanliness of the area surrounding these devices.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and h

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative