Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# FAN54040 — FAN54047 USB-OTG, 1.55 A, Li-lon Switching Charger with Power Path and 2.3 A Production Test Support

#### **Features**

- Fully Integrated, High-Efficiency Charger for Single-Cell Li-lon and Li-Polymer Battery Packs

- Pow er Path Circuit Ensures Fast System Startup with a Dead Battery when VBUS is Connected

- 1.55 A Maximum Charge Current

- Float Voltage Accuracy:

- ±0.5% at 25°C

- ±1% from 0 to 125°C

- ±5% Input and Charge Current Regulation Accuracy

- Temperature-Sense Input Prevents Auto-Charging for JETA Compliance

- Thermal Regulation and Shutdown

- 4.2 V at 2.3 A Production Test Mode

- 5 V, 500 mA Boost Mode for USB OTG

- 28 V Absolute Maximum Input Voltage

- 6 V Maximum Input Operating Voltage

- Programmable through High-Speed PC Interface (3.4 Mb/s) with Fast Mode Plus Compatibility

- Input Current

- Fast-Charge / Termination Current

- Float Voltage

- Termination Enable

- 3 MHz Synchronous Buck PWM Controller with Wide Duty Cycle Range

- Small Footprint 1 μH External Inductor

- Safety Timer with Reset Control

- Dynamic Input Voltage Control

- Very Low Battery Current when Charger Inactive

#### **Applications**

- Cell Phones, Smart Phones, PDAs

- Tablet, Portable Media Players

- Gaming Device, Digital Cameras

All trademarks are the property of their respective owners.

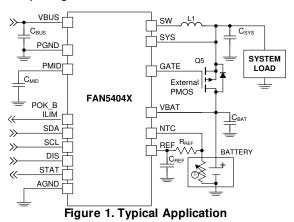

### **Description**

The FAN5404X family includes  $^{2}$ C controlled 1.55 A USB-compliant switch-mode chargers with power path operation and USB OTG boost operation. Integrated with the charger, the IC supports production test mode, which provides 4.2 V at up to 2.3 A to the system.

To facilitate fast system startup, the IC includes a power path circuit, which disconnects the battery from the system rail, ensuring that the system can power up quickly following a VBUS connection. The power path circuit ensures that the system rail stays up when the charger is plugged in, even if the battery is dead or shorted.

The charging parameters and operating modes are programmable through an  $^{\circ}C$  Interface that operates up to 3.4 Mbps. The charger and boost regulator circuits switch at 3 MHz to minimize the size of external passive components.

The FAN5404X provides battery charging in three phases: conditioning, constant current, and constant voltage. The integrated circuit automatically restarts the charge cycle when the battery falls below a voltage threshold. If the input source is removed, the IC enters a high-impedance mode blocking battery current from leaking to the input. Charge status is reported back to the host through the I<sup>2</sup>C port.

Dynamic input voltage control prevents a weak adapter's voltage from collapsing, ensuring charging capability from such adapters.

The FAN5404X is available in a 25-bump, 0.4 mm pitch, WLCSP package.

## **Ordering Information**

| Part Number                | Temperature Range | Package                                                             | PN Bits: IC_INFO[5:3] | Packing Method |

|----------------------------|-------------------|---------------------------------------------------------------------|-----------------------|----------------|

| FAN54040UCX                | -40 to 85°C       |                                                                     | 000                   |                |

| FAN54041UCX                |                   | 25-Bump, Wafer-Level<br>Chip-Scale Package<br>(WLCSP), 0.4 mm Pitch | 001                   |                |

| FAN54042UCX <sup>(1)</sup> |                   |                                                                     | 010                   | Topo and Pool  |

| FAN54045UCX <sup>(1)</sup> |                   |                                                                     | 101                   | Tape and Reel  |

| FAN54046UCX <sup>(1)</sup> |                   |                                                                     | 110                   |                |

| FAN54047UCX                |                   |                                                                     | 110                   |                |

#### Note:

1. Contact ON Semiconductor Sales for availability.

**Table 1. Feature Comparison Summary**

| Part Number | Slave Address | Automatic Charge | Battery Absent Behavior | E1 Pin |

|-------------|---------------|------------------|-------------------------|--------|

| FAN54040    | 1101011       | Yes              | Off                     | POK_B  |

| FAN54041    | 1101011       | No               | Off                     | POK_B  |

| FAN54042    | 1101011       | Yes              | On                      | POK_B  |

| FAN54045    | 1101011       | No               | Off                     | ILIM   |

| FAN54046    | 1101011       | No               | On                      | ILIM   |

| FAN54047    | 1101011       | Yes              | On                      | ILIM   |

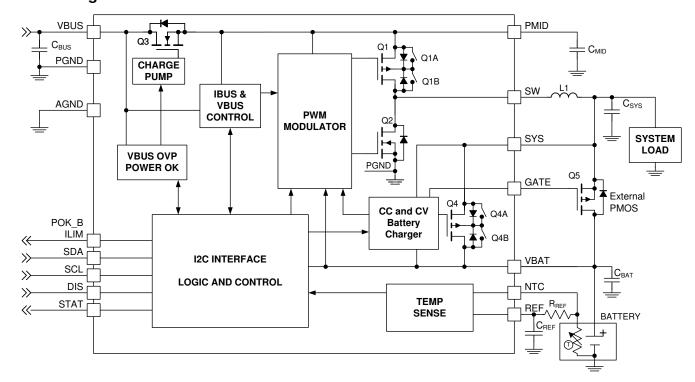

### **Block Diagram**

| PMID                          | Q1A | Q1B |

|-------------------------------|-----|-----|

| Greater than V <sub>BAT</sub> | ON  | OFF |

| Less than V <sub>BAT</sub>    | OFF | ON  |

| SYS                           | Q4A | Q4B |

|-------------------------------|-----|-----|

| Greater than V <sub>BAT</sub> | ON  | OFF |

| Less than V <sub>BAT</sub>    | OFF | ON  |

Figure 2. IC and System Block Diagram

**Table 2. Recommended External Components**

| Component                           | Description                   | Vendor                                        | Parameter           | Тур. | Unit |

|-------------------------------------|-------------------------------|-----------------------------------------------|---------------------|------|------|

| L1                                  | 1 μH, 20%, 2.2 A, 2016        | Taiyo Yuden MAKK2016T1R0M                     | L                   | 1.0  | μН   |

| L'                                  | 1 μιι, 20/6, 2.2 Α, 2010      | or Equivalent                                 | DCR (Series R)      | 75   | mΩ   |

| C <sub>BAT</sub> , C <sub>SYS</sub> | 10 μF, 20%, 6.3 V, X5R, 0603  | Murata: GRM188R60J106M<br>TDK: C1608X5R0J106M | С                   | 10   | μF   |

| Смір                                | 4.7 μF, 10%, 6.3 V, X5R, 0603 | Murata: GRM188R60J475K<br>TDK: C1608X5R0J475K | C <sup>(2)</sup>    | 4.7  | μF   |

| C <sub>BUS</sub> ,                  | 1.0 μF, 10%, 25 V, X5R, 0603  | Murata GRM188R61E105K<br>TDK:C1608X5R1E105M   | С                   | 1.0  | μF   |

| Q5                                  | PMOS,12 V, 16 mΩ, MLP2x2      | ON Semiconductor FDMA905P                     | R <sub>DS(ON)</sub> | 16   | mΩ   |

| C <sub>REF</sub>                    | 1 μF, 10%, 6.3 V, X5R, 0402   |                                               | С                   | 1.0  | μF   |

#### Note:

2. 6.3 V rating is sufficient for C<sub>MID</sub> since PMID is protected from over-voltage surges on VBUS by Q3.

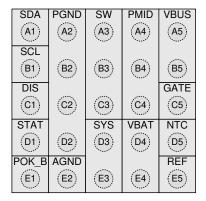

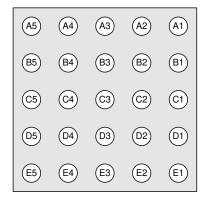

### **Pin Configuration**

Figure 3. Top View

Figure 4. Bottom View

### **Pin Definitions**

| Pin#    | Name  | Description                                                                                                                                                                                                                                                     |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | SDA   | I <sup>2</sup> C Interface Serial Data. This pin should not be left floating.                                                                                                                                                                                   |

| B1      | SCL   | I <sup>2</sup> C Interface Serial Clock. This pin should not be left floating.                                                                                                                                                                                  |

| C1      | DIS   | <b>Disable</b> . If this pin is held HIGH, Q1 and Q3 are turned off, creating a HIGH Z condition at VBUS and the PWM converter is disabled.                                                                                                                     |

| D1      | STAT  | Status. Open-drain output indicating charge status. The IC pulls this pin LOW when charge is in progress; can be used to signal the host processor when a fault condition occurs.                                                                               |

| E1      | POK_B | <b>Power OK (FAN54040-2).</b> Open-drain output that pulls LOW when VBUS is plugged in and the battery has risen above V <sub>LOWV</sub> . This signal is used to signal the host processor that it can begin to draw significant current.                      |

| E1      | ILIM  | Input Current Limit (FAN54045-7). Controls input current limit in Auto-Charge Mode. When LOW, input current is limited to 100 mA maximum. When HIGH, input current is limited to 500 mA. In 32-Second Mode, the input current limit is set by the IBUSLIM bits. |

| A2 – D2 | PGND  | <b>Power Ground</b> . Pow er return for gate drive and pow er transistors. The connection from this pin to the bottom of C <sub>MID</sub> should be as short as possible.                                                                                       |

| E2      | AGND  | Analog Ground. All IC signals are referenced to this node.                                                                                                                                                                                                      |

| A3 – C3 | SW    | Switching Node. Connect to output inductor.                                                                                                                                                                                                                     |

| D3 – E3 | SYS   | System Supply. Output voltage of the switching charger and input to the power path controller. Bypass SYS to PGND with a 10 $\mu$ F capacitor.                                                                                                                  |

| A4 – C4 | PMID  | <b>Power Input Voltage</b> . Power input to the charger regulator, bypass point for the input current sense. Bypass with a minimum of a 4.7 $\mu$ F, 6.3 V capacitor to PGND.                                                                                   |

| D4 – E4 | VBAT  | Battery Voltage. Connect to the positive (+) terminal of the battery pack. Bypass with a 10 $\mu$ F capacitor to PGND. VBAT is a power path connection.                                                                                                         |

| A5 – B5 | VBUS  | Charger Input Voltage and USB-OTG output voltage. Bypass with a 1 μF capacitor to PGND.                                                                                                                                                                         |

| C5      | GATE  | <b>External MOSFET Gate</b> . This pin controls the gate of an external P-channel MOSFET transistor used to augment the internal ideal diode. The source of the P-channel MOSFET should be connected to SYS and the drain should be connected to VBAT.          |

| D5      | NTC   | <b>Thermistor input</b> . The IC compares this node with taps on a resistor divider from REF to inhibit autocharging when the battery temperature is outside of permitted fast-charge limits.                                                                   |

| E5      | REF   | Reference Voltage. REF is a 1.8 V regulated output.                                                                                                                                                                                                             |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | F                                                                       | Parameter                      |                                 |      | Max.               | Unit  |

|-------------------|-------------------------------------------------------------------------|--------------------------------|---------------------------------|------|--------------------|-------|

| V <sub>BUS</sub>  | Continuous                                                              |                                | -0.3                            | 28.0 | V                  |       |

| V BUS             | Voltage on VBUS Pin                                                     | Pulsed, 100 ms Max             | imum Non-Repetitive             | -1.0 | 20.0               | , v   |

| Vı                | Voltage on PMID Voltage Pin                                             |                                |                                 | -0.3 | 7.0                | V     |

| V 1               | Voltage on SW, SYS, VBAT, STA                                           | T, DIS Pins                    |                                 | -0.3 | 7.0                | ] `   |

| Vo                | Voltage on Other Pins                                                   |                                |                                 | -0.3 | 6.5 <sup>(3)</sup> | V     |

| dV <sub>BUS</sub> | Maximum V <sub>BUS</sub> Slope Above 5.5 V when Boost or Charger Active |                                |                                 |      | 4                  | V/μs  |

|                   | Electrostatic Discharge Human Body Model per JESD22-A114                |                                | ıman Body Model per JESD22-A114 |      | 000                | V     |

| ESD               | Protection Level                                                        | Charged Device Mo              | del per JESD22-C101             | 5    | 00                 | ]     |

| LSD               | IEC 61000-4-2 System ESD <sup>(4)</sup>                                 | USB Connector                  | Air Gap                         |      | 15                 | kV    |

|                   | Leo 01000 4 2 Gystem Leb                                                | Pins (V <sub>BUS</sub> to GND) | Contact                         | 8    |                    | ] '`` |

| TJ                | Junction Temperature                                                    |                                |                                 | -40  | +150               | °C    |

| T <sub>STG</sub>  | Storage Temperature                                                     |                                | -65                             | +150 | °C                 |       |

| TL                | Lead Soldering Temperature, 10                                          | Seconds                        |                                 |      | +260               | °C    |

#### Note:

- Lesser of 6.5 V or V<sub>1</sub> + 0.3 V.

- 4. Guaranteed if  $C_{BUS} \ge 1 \mu F$  and  $C_{MID} \ge 4.7 \mu F$ .

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. ON Semiconductor does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol                 | Parameter                                                            |                       | Min. | Max.                      | Unit                 |

|------------------------|----------------------------------------------------------------------|-----------------------|------|---------------------------|----------------------|

| V <sub>BUS</sub>       | Supply Voltage                                                       |                       | 4    | 6                         | V                    |

| V <sub>BAT(MAX)</sub>  | Maximum Battery Voltage when Boost enabled                           |                       |      | 4.5                       | V                    |

| $-\frac{dV_{BUS}}{dt}$ | dV <sub>BUS</sub> Negative VBUS Slew Rate during VBUS Short Circuit, | T <sub>A</sub> ≤ 60°C |      | 4                         | V/us                 |

| - dt                   | C <sub>MID</sub> ≤ 4.7 μF, see VBUS Short While Charging             | T <sub>A</sub> ≥ 60°C |      | 6<br>4.5<br>4<br>2<br>+85 | <b>v</b> /μ <b>s</b> |

| TA                     | Ambient Temperature                                                  |                       | -30  | +85                       | °C                   |

| TJ                     | Junction Temperature (see Thermal Regulation and Prote               | ection section)       | -30  | +120                      | °C                   |

### **Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperature  $T_{A}$ . For measured data, see Table 18.

| Symbol | Parameter                                                   | Typical | Unit |

|--------|-------------------------------------------------------------|---------|------|

| θЈА    | Junction-to-Ambient Thermal Resistance (see also Figure 18) | 50      | °C/W |

| θЈВ    | Junction-to-PCB Thermal Resistance                          | 20      | °C/W |

### **Electrical Specifications**

Unless otherwise specified: according to the circuit of Figure 1; recommended operating temperature range for  $T_J$  and  $T_A$ ;  $V_{BUS}=5.0 \text{ V}$ ;  $HZ\_MODE$ ;  $OPA\_MODE=0$ ; (Charge Mode); SCL, SDA=0 or 1.8 V; and typical values are for  $T_J=25^{\circ}C$ .

| Symbol                | Parameter                                                          | Conditi                                                                                    | ons                                 | Min.       | Тур.                                             | Max.                                             | Unit     |

|-----------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------|------------|--------------------------------------------------|--------------------------------------------------|----------|

| Power Supp            | lies                                                               |                                                                                            |                                     |            | I                                                |                                                  | I        |

|                       |                                                                    | V <sub>BUS</sub> > V <sub>BUS(min)</sub> , PWM                                             | Sw itching                          |            | 10                                               |                                                  | mA       |

| l <sub>VBUS</sub>     | VBUS Current                                                       | V <sub>BUS</sub> > V <sub>BUS(min)</sub> ; V <sub>BAT</sub><br>I <sub>BUSLIM</sub> =100 mA | > V <sub>OREG</sub>                 |            | 2.5                                              |                                                  | mA       |

|                       |                                                                    | 0°C < T <sub>J</sub> < 85°C, HZ_<br>V <sub>BAT</sub> < V <sub>LOWV</sub> , 32S Mo          |                                     |            |                                                  | 280                                              | μΑ       |

| BAT_HZ                | Battery Discharge Current in High-<br>Impedance Mode               |                                                                                            |                                     |            | <1                                               | 10                                               | μΑ       |

| l <sub>BUS_HZ</sub>   | Battery Leakage Current to V <sub>BUS</sub> in High-Impedance Mode |                                                                                            |                                     | -5.0       | -0.2                                             |                                                  | μΑ       |

| Charger Vol           | tage Regulation                                                    |                                                                                            |                                     |            | <u>l</u>                                         | <u> </u>                                         |          |

|                       | Charge Voltage Range                                               |                                                                                            |                                     | 3.5        |                                                  | 4.4                                              | V        |

| $V_{OREG}$            |                                                                    | T <sub>A</sub> =25°C                                                                       |                                     | -0.5       |                                                  | +0.5                                             | %        |

|                       | Charge Voltage Accuracy                                            | T <sub>J</sub> =0 to 125°C                                                                 |                                     | -1         |                                                  | +1                                               | %        |

| Charging Cu           | ırrent Regulation                                                  | I                                                                                          |                                     | 1          |                                                  |                                                  | <u>I</u> |

|                       |                                                                    | ., ,, ,,                                                                                   | IO_LEVEL=0                          | 550        |                                                  | 1550                                             | mA       |

| lochrg                | Output Charge Current Range                                        | VLOWV < VBAT < VOREG                                                                       | IO_LEVEL=1                          | 290        | 340                                              | 390                                              | mA       |

|                       | Charge Current Accuracy                                            | IO_LEVEL=0                                                                                 |                                     | <b>-</b> 5 |                                                  | +5                                               | %        |

| Weak Batter           | y Detection                                                        | l                                                                                          |                                     | 1          | ı                                                |                                                  |          |

| $V_{LOWV}$            | Weak Battery Threshold Range                                       |                                                                                            |                                     | 3.4        |                                                  | 3.7                                              | V        |

|                       | Weak Battery Threshold Accuracy                                    |                                                                                            | <b>-</b> 5                          |            | +5                                               | %                                                |          |

|                       | Weak Battery Deglitch Time                                         | Rising Voltage, 2 mV                                                                       |                                     | 30         |                                                  | ms                                               |          |

| Logic Levels          | s : DIS, SDA, SCL                                                  |                                                                                            |                                     |            | <u>l</u>                                         | <u> </u>                                         |          |

| V <sub>IH</sub>       | High-Level Input Voltage                                           |                                                                                            |                                     | 1.05       |                                                  |                                                  | V        |

| VıL                   | Low-Level Input Voltage                                            |                                                                                            |                                     |            |                                                  | 0.4                                              | V        |

| I <sub>IN</sub>       | Input Bias Current                                                 | Input Tied to GND or                                                                       | V <sub>BUS</sub>                    |            | 0.01                                             | 1.00                                             | μΑ       |

| Charge Terr           | nination Detection                                                 |                                                                                            |                                     |            | <u>l</u>                                         | <u> </u>                                         |          |

|                       | Termination Current Range                                          | V <sub>BAT</sub> > V <sub>OREG</sub> - V <sub>RCH</sub> ,                                  | V <sub>BUS</sub> > V <sub>SLP</sub> | 50         |                                                  | 400                                              | mA       |

|                       | Tamaia dia 2                                                       | lτERM Setting ≤ 100 m                                                                      | 4                                   | -15        |                                                  | +15                                              | 0/       |

| I(TERM)               | Termination Current Accuracy                                       | DIS=1, or HZ_MODE=1,                                                                       | %                                   |            |                                                  |                                                  |          |

|                       | Termination Current Deglitch Time                                  |                                                                                            |                                     |            | 30                                               |                                                  | ms       |

| Power Path            | (Q4) Control                                                       |                                                                                            |                                     |            | <u>I</u>                                         |                                                  |          |

|                       |                                                                    |                                                                                            | IO_LEVEL=1                          | 290        | 340                                              | 390                                              | mA       |

| ILIN                  | Power Path Max. Charge Current                                     |                                                                                            | IO_LEVEL=0                          | 400        | 450                                              | 510                                              | mA       |

|                       |                                                                    |                                                                                            | IO_LEVEL=0                          | 650        | 725                                              | 800                                              | mA       |

| V                     | VBAT to SYS Threshold for Q4 and                                   | (SYS-VBAT) Falling                                                                         |                                     | -6         | <b>–</b> 5                                       | -3                                               | mV       |

| V <sub>THSYS</sub>    | Gate Transition While Charging                                     | (SYS-VBAT) Rising                                                                          |                                     | -1         | +1                                               | 2                                                | mV       |

| Production            | Test Mode                                                          |                                                                                            |                                     |            |                                                  |                                                  |          |

| V <sub>BAT(PTM)</sub> | Production Test Output Voltage                                     | 1 mA < l <sub>BAT</sub> < 2 A, V <sub>BUS</sub> =5.5 V                                     |                                     | 4.116      | 4.200                                            | 4.284                                            | V        |

|                       | Production Test Output Current                                     | 20% Duty with Max. Period 10 ms                                                            |                                     | 2.3        | <del>                                     </del> | <del>                                     </del> | Α        |

Continued on the following page...

## **Electrical Specifications** (Continued)

Unless otherwise specified: according to the circuit of Figure 1; recommended operating temperature range for  $T_J$  and  $T_A$ ;  $V_{BUS}=5.0 \text{ V}$ ;  $HZ\_MODE$ ;  $OPA\_MODE=0$ ; (Charge Mode); SCL, SDA=0 or 1.8 V; and typical values are for  $T_J=25^{\circ}C$ .

| Symbol                   | Parameter                                                                  | Conditions                                                              | Min. | Тур. | Max.       | Unit      |

|--------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------------|-----------|

| Input Power              | Source Detection                                                           | •                                                                       |      | 1    | 1          |           |

| T1                       | T1 (0°C) Temperature Threshold                                             |                                                                         | 71.9 | 73.9 | 75.9       |           |

| T2                       | T1 (10°C) Temperature Threshold                                            |                                                                         | 62.6 | 64.6 | 66.6       | % of      |

| T3                       | T1 (45°C) Temperature Threshold                                            |                                                                         | 31.9 | 32.9 | 34.9       | $V_{REF}$ |

| T4                       | T1 (60°C) Temperature Threshold                                            |                                                                         | 21.3 | 23.3 | 25.3       |           |

| Input Power              | Source Detection                                                           |                                                                         |      |      |            |           |

| V <sub>IN(MIN)1</sub>    | VBUS Input Voltage Rising                                                  | To Initiate and Pass VBUS Validation                                    |      | 4.29 | 4.42       | V         |

| V <sub>IN(MIN)2</sub>    | Minimum VBUS during Charge                                                 | During Charging                                                         |      | 3.71 | 3.94       | V         |

| tvbus_valid              | VBUS Validation Time                                                       |                                                                         |      | 30   |            | ms        |

| V <sub>BUS</sub> Contro  | lLoop                                                                      | •                                                                       | •    |      | •          | •         |

| V <sub>BUSLIM</sub>      | VBUS Loop Setpoint Accuracy                                                |                                                                         | -3   |      | +3         | %         |

| Input Currer             | nt Limit                                                                   | •                                                                       | •    | •    | •          |           |

| L                        | Charger Input Current Limit                                                | IBUSLIM Set to 100 mA                                                   | 88   | 93   | 98         | m A       |

| <b>I</b> BUSLIM          | Threshold                                                                  | IBUSLIM Set to 500 mA                                                   | 450  | 475  | 500        | - mA      |

| V <sub>REF</sub> Bias Ge | nerator                                                                    |                                                                         |      | 1    | _ <b>L</b> |           |

| \/                       | Bias Regulator Voltage                                                     | V <sub>BUS</sub> > V <sub>IN(MIN)</sub>                                 |      | 1.8  |            | V         |

| $V_{REF}$                | Short-Circuit Current Limit                                                |                                                                         |      | 2.5  |            | mA        |

| Battery Rech             | narge Threshold                                                            |                                                                         | •    | •    | •          | •         |

| Van                      | Recharge Threshold                                                         | Below V <sub>(OREG)</sub>                                               | 100  | 120  | 150        | mV        |

| $V_{RCH}$                | Deglitch Time                                                              | V <sub>BAT</sub> Falling Below V <sub>RCH</sub> Threshold               |      | 130  |            | ms        |

| STAT, POK_I              | B Output                                                                   | •                                                                       | •    | •    | •          |           |

| V <sub>STAT(OL)</sub>    | STAT Output Low                                                            | I <sub>STAT</sub> =10 mA                                                |      |      | 0.4        | V         |

| ISTAT(OH)                | STAT High Leakage Current                                                  | V <sub>STAT</sub> =5 V                                                  |      |      | 1          | μΑ        |

| Battery Dete             | ction                                                                      | •                                                                       |      |      | 1          |           |

| Претест                  | Battery Detection Current before Charge Done (Sink Current) (5)            | Begins after Termination Detected                                       |      | -0.8 |            | mA        |

| tdetect                  | Battery Detection Time                                                     | and V <sub>BAT</sub> ≤ V <sub>OREG</sub> −V <sub>RCH</sub>              |      | 262  |            | ms        |

| Sleep Comp               | arator                                                                     |                                                                         |      |      | _ <b>I</b> |           |

| $V_{SLP}$                | Sleep-Mode Entry Threshold, V <sub>BUS</sub> – V <sub>BAT</sub>            | 2.3 V ≤ V <sub>BAT</sub> ≤ V <sub>OREG</sub> , V <sub>BUS</sub> Falling | 0    | 0.04 | 0.10       | ٧         |

| Power Switch             | ches (see Figure 2)                                                        | •                                                                       | •    | •    |            |           |

|                          | Q3 On Resistance (VBUS to PMID)                                            | I <sub>IN(LIMIT)</sub> =500 mA                                          |      | 180  | 250        |           |

| D- « · - · · ·           | Q1 On Resistance (PMID to SW)                                              |                                                                         |      | 130  | 225        | mΩ        |

| R <sub>DS(ON)</sub>      | Q2 On Resistance (SW to GND)                                               |                                                                         | 1    | 150  | 225        |           |

|                          | Q4 On Resistance (SYS to VBAT)                                             | V <sub>BAT</sub> =4.2 V                                                 |      | 70   | 100        | mΩ        |

| ISYNC                    | Synchronous to Non-Synchronous<br>Current Cut-Off Threshold <sup>(6)</sup> | Low-Side MOSFET (Q2) Cycle-by-<br>Cycle Current Limit                   |      | 140  |            | mA        |

Continued on the following page...

### **Electrical Specifications** (Continued)

Unless otherwise specified: according to the circuit of Figure 1; recommended operating temperature range for  $T_J$  and  $T_A$ ;  $V_{BUS}=5.0~V$ ;  $HZ_MODE$ ;  $OPA_MODE=0$ ; (Charge Mode); SCL, SDA=0 or 1.8 V; and typical values are for  $T_J=25^{\circ}C$ .

| Symbol               | Parameter                                   | Conditions                                                                                     | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| Charger PW           | M Modulator                                 | •                                                                                              |      | ı    |      |      |

| fsw                  | Oscillator Frequency                        |                                                                                                | 2.7  | 3.0  | 3.3  | MHz  |

| D <sub>MAX</sub>     | Maximum Duty Cycle                          |                                                                                                |      |      | 100  | %    |

| D <sub>MIN</sub>     | Minimum Duty Cycle                          |                                                                                                |      | 0    |      | %    |

| Boost Mode           | Operation (OPA_MODE=1, HZ_MOD               | DE=0)                                                                                          |      |      |      | 1    |

| V                    | Boost Output Voltage at VBUS                | $2.5~\text{V} < \text{V}_{\text{BAT}} < 4.5~\text{V},~\text{I}_{\text{LOAD}}$ from 0 to 200 mA | 4.80 | 5.07 | 5.20 | V    |

| V <sub>BOOST</sub>   | boost Output Voltage at VBOS                | $3.0~\text{V} < \text{V}_{\text{BAT}} < 4.5~\text{V},~\text{I}_{\text{LOAD}}$ from 0 to 500 mA | 4.77 | 5.07 | 5.20 |      |

| BAT(BOOST)           | Boost Mode Quiescent Current                | PFM Mode, V <sub>BAT</sub> =3.6 V, I <sub>LOAD</sub> =0                                        |      | 250  | 350  | μА   |

| ILIMPK(BST)          | Q2 Peak Current Limit                       |                                                                                                | 1350 | 1550 | 1950 | mA   |

| UVLO <sub>BST</sub>  | Minimum Battery Voltage for Boost           | While Boost Active                                                                             |      | 2.32 |      | V    |

| UVLOBST              | Operation                                   | To Start Boost Regulator                                                                       |      | 2.48 | 2.70 | 1 °  |

| VBUS Load            | Resistance                                  | -                                                                                              |      |      | · ·  |      |

| Б                    | VIDLIC to DOND, Decistance                  | Normal Operation                                                                               |      | 500  |      | kΩ   |

| R <sub>VBUS</sub>    | VBUS to PGND Resistance                     | VBUS Validation                                                                                |      | 100  |      | Ω    |

| Protection a         | ind Timers                                  | •                                                                                              |      |      |      | I .  |

| V/DLIC               | VBUS Over-Voltage Shutdown                  | V <sub>BUS</sub> Rising                                                                        | 6.09 | 6.29 | 6.49 | V    |

| VBUS <sub>OVP</sub>  | Hysteresis                                  | V <sub>BUS</sub> Falling                                                                       |      | 100  |      | mV   |

| LIMPK(CHG)           | Q1 Cycle-by-Cycle Peak Current<br>Limit     | Charge Mode                                                                                    |      | 3    |      | Α    |

| M                    | Battery Short-Circuit Threshold             | V <sub>BAT</sub> Rising                                                                        | 1.95 | 2.00 | 2.05 | V    |

| V <sub>SHORT</sub>   | Hysteresis                                  |                                                                                                |      | 100  |      | mV   |

| I                    | Linear Charging Current                     | V <sub>BAT</sub> < V <sub>SHORT</sub>                                                          |      | 13   |      | mA   |

| ISHORT               | Linear Charging Current                     | Linear                                                                                         |      | 30   |      | IIIA |

| Ta                   | Thermal Shutdown Threshold (7)              | T <sub>J</sub> Rising                                                                          |      | 145  |      | °C   |

| T <sub>SHUTDWN</sub> | Hysteresis <sup>(7)</sup>                   | T <sub>J</sub> Falling                                                                         |      | 25   |      | 1 ~  |

| T <sub>CF</sub>      | Thermal Regulation Threshold <sup>(7)</sup> | Charge Current Reduction Begins                                                                |      | 120  |      | °C   |

| tint                 | Detection Interval                          |                                                                                                |      | 2.1  |      | S    |

| tono                 | 32-Second Timer <sup>(8)</sup>              | Charger Enabled                                                                                | 20.5 | 25.2 | 28.0 | _    |

| t <sub>32</sub> s    | 52-Second Timer                             | Charger Disabled                                                                               | 18.0 | 25.2 | 34.0 | - s  |

| t <sub>15MIN</sub>   | 15-Minute Timer                             | 15-Minute Mode (FAN54040,<br>FAN54042, FAN54046, FAN54047)                                     | 12.0 | 13.5 | 15.0 | min  |

| $\Delta t_{LF}$      | Low-Frequency Timer Accuracy                | Charger Inactive                                                                               | -25  |      | 25   | %    |

#### Notes:

- 5. Negative current is current flowing from the battery to VBUS (discharging the battery).

- 6. Q2 alw ays turns on for 60 ns, then turns off if current is below ISYNC.

- 7. Guaranteed by design; not tested in production.

- 8. This tolerance (%) applies to all timers on the IC, including soft-start and deglitching timers.

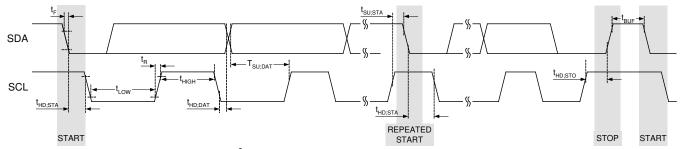

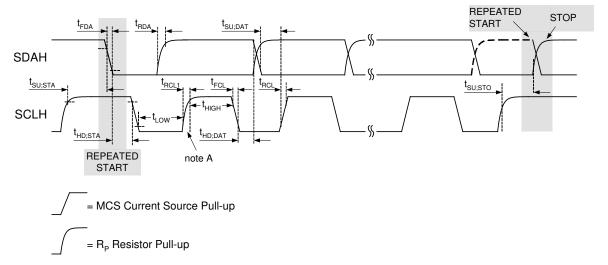

# I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol            | Parameter                                       | Conditions                                | Min. | Typ.             | Max. | Unit |  |

|-------------------|-------------------------------------------------|-------------------------------------------|------|------------------|------|------|--|

|                   |                                                 | Standard Mode                             |      |                  | 100  |      |  |

|                   |                                                 | Fast Mode                                 |      |                  | 400  |      |  |

| f <sub>SCL</sub>  | SCL Clock Frequency                             | Fast Mode Plus                            |      |                  | 1000 | kHz  |  |

|                   |                                                 | High-Speed Mode, $C_B \le 100 \text{ pF}$ |      |                  | 3400 |      |  |

|                   |                                                 | High-Speed Mode, $C_B \le 400 \text{ pF}$ |      |                  | 1700 |      |  |

|                   |                                                 | Standard Mode                             |      | 4.7              |      |      |  |

| t <sub>BUF</sub>  | BUS-free Time between STOP and START Conditions | Fast Mode                                 |      | 1.3              |      | μS   |  |

|                   | OTATA CONCINOUS                                 | Fast Mode Plus                            |      | 0.5              |      |      |  |

|                   |                                                 | Standard Mode                             |      | 4                |      | μS   |  |

|                   | START or Repeated START Hold                    | Fast Mode                                 |      | 600              |      | ns   |  |

| thd;sta           | Time                                            | Fast Mode Plus                            |      | 260              |      | ns   |  |

|                   |                                                 | High-Speed Mode                           |      | 160              |      | ns   |  |

|                   |                                                 | Standard Mode                             |      | 4.7              |      | μS   |  |

|                   |                                                 | Fast Mode                                 |      | 1.3              |      | μS   |  |

| tLOW              | SCL LOW Period                                  | Fast Mode Plus                            |      | 0.5              |      | μS   |  |

|                   |                                                 | High-Speed Mode, C <sub>B</sub> ≤ 100 pF  |      | 160              |      | ns   |  |

|                   |                                                 | High-Speed Mode, C <sub>B</sub> ≤ 400 pF  |      | 320              |      | ns   |  |

|                   |                                                 | Standard Mode                             |      | 4                |      | μS   |  |

|                   |                                                 | Fast Mode                                 |      | 600              |      | ns   |  |

| t <sub>HIGH</sub> | SCL HIGH Period                                 | Fast Mode Plus                            |      | 260              |      | ns   |  |

|                   |                                                 | High-Speed Mode, C <sub>B</sub> ≤ 100 pF  |      | 60               |      | ns   |  |

|                   |                                                 | High-Speed Mode, $C_B \le 400 \text{ pF}$ |      | 120              |      | ns   |  |

|                   |                                                 | Standard Mode                             |      | 4.7              |      | μS   |  |

|                   |                                                 | Fast Mode                                 |      | 600              |      | ns   |  |

| tsu;sta           | Repeated START Setup Time                       | Fast Mode Plus                            |      | 260              |      | ns   |  |

|                   |                                                 | High-Speed Mode                           |      | 160              |      | ns   |  |

|                   |                                                 | Standard Mode                             |      | 250              |      |      |  |

|                   |                                                 | Fast Mode                                 |      | 100              |      |      |  |

| tsu;dat           | Data Setup Time                                 | Fast Mode Plus                            |      | 50               |      | ns   |  |

|                   |                                                 | High-Speed Mode                           |      | 10               |      |      |  |

|                   |                                                 | Standard Mode                             | 0    |                  | 3.45 | μS   |  |

|                   |                                                 | Fast Mode                                 | 0    |                  | 900  | ns   |  |

| thd;dat           | Data Hold Time                                  | Fast Mode Plus                            | 0    |                  | 450  | ns   |  |

| •                 |                                                 | High-Speed Mode, C <sub>B</sub> ≤ 100 pF  | 0    |                  | 70   | ns   |  |

|                   |                                                 | High-Speed Mode, C <sub>B</sub> ≤ 400 pF  | 0    |                  | 150  | ns   |  |

|                   |                                                 | Standard Mode                             | 20+0 | .1C <sub>B</sub> | 1000 |      |  |

|                   |                                                 | Fast Mode                                 | 20+0 | .1C <sub>B</sub> | 300  | ns   |  |

| t <sub>RCL</sub>  | SCL Rise Time                                   | Fast Mode Plus                            | 20+0 |                  | 120  |      |  |

| -                 |                                                 | High-Speed Mode, $C_B \le 100 \text{ pF}$ |      | 10               | 80   | -    |  |

|                   |                                                 | High-Speed Mode, $C_B \le 400 \text{ pF}$ |      | 20               | 160  |      |  |

Continued on the following page...

## $I^2C$ Timing Specifications (Continued)

Guaranteed by design.

| Symbol            | Parameter                         | Conditions                                | Min.                 | Тур.                 | Max. | Unit |

|-------------------|-----------------------------------|-------------------------------------------|----------------------|----------------------|------|------|

|                   |                                   | Standard Mode                             | 20+0                 | .1C <sub>B</sub>     | 300  |      |

|                   | SCL Fall Time                     | Fast Mode                                 | 20+0.1C <sub>B</sub> |                      | 300  | ns   |

| t <sub>FCL</sub>  |                                   | Fast Mode Plus                            | 20+0                 | 20+0.1C <sub>B</sub> |      |      |

|                   |                                   | High-Speed Mode, $C_B \le 100 \text{ pF}$ |                      | 10                   | 40   |      |

|                   |                                   | High-Speed Mode, $C_B \le 400 \text{ pF}$ |                      | 20                   | 80   |      |

| t <sub>RCL1</sub> | Rise Time of SCL after a Repeated | High-Speed Mode, $C_B \le 100 \text{ pF}$ |                      | 10                   | 80   | ns   |

| IRCL1             | START Condition and after ACK Bit | High-Speed Mode, $C_B \le 400 \text{ pF}$ |                      | 20                   | 160  | 115  |

|                   |                                   | Standard Mode                             | 20+0                 | .1C <sub>B</sub>     | 1000 |      |

|                   | SDA Rise Time                     | Fast Mode                                 | 20+0.1C <sub>B</sub> |                      | 300  | ns   |

| t <sub>RDA</sub>  |                                   | Fast Mode Plus                            | 20+0.1C <sub>B</sub> |                      | 120  |      |

|                   |                                   | High-Speed Mode, $C_B \le 100 \text{ pF}$ |                      | 10                   | 80   |      |

|                   |                                   | High-Speed Mode, $C_B \le 400 \text{ pF}$ |                      | 20                   | 160  |      |

|                   |                                   | Standard Mode                             | 20+0.1C <sub>B</sub> |                      | 300  |      |

|                   |                                   | Fast Mode                                 | 20+0                 | .1 <b>C</b> B        | 300  |      |

| t <sub>FDA</sub>  | SDA Fall Time                     | Fast Mode Plus                            | 20+0.1C <sub>B</sub> |                      | 120  | ns   |

|                   |                                   | High-Speed Mode, $C_B \le 100 \text{ pF}$ |                      | 10                   | 80   |      |

|                   |                                   | High-Speed Mode, $C_B \le 400 \text{ pF}$ |                      | 20                   | 160  | ı    |

|                   |                                   | Standard Mode                             |                      | 4                    |      | μS   |

|                   | Stan Candition Satura Time        | Fast Mode                                 |                      | 600                  |      | ns   |

| tsu;sto           | Stop Condition Setup Time         | Fast Mode Plus                            |                      | 120                  |      | ns   |

|                   |                                   | High-Speed Mode                           |                      | 160                  |      | ns   |

| C <sub>B</sub>    | Capacitive Load for SDA and SCL   |                                           |                      |                      | 400  | pF   |

### **Timing Diagrams**

Figure 5. I<sup>2</sup>C Interface Timing for Fast and Slow Modes

Note A: First rising edge of SCLH after Repeated Start and after each ACK bit.

Figure 6. I<sup>2</sup>C Interface Timing for High-Speed Mode

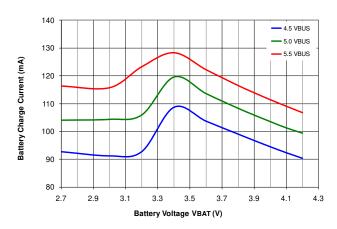

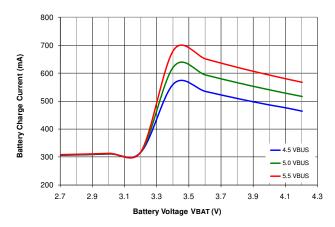

### **Charge Mode Typical Characteristics**

Figure 7. Battery Charge Current vs.  $V_{BUS}$  with  $I_{BUSLIM}$ =100 mA

Figure 8. Battery Charge Current vs. V<sub>BUS</sub> with I<sub>BUSLIM</sub>=500 m A

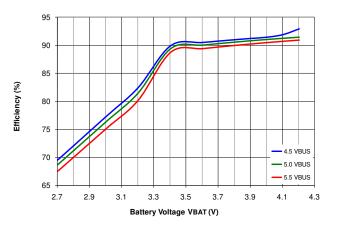

Figure 9. Efficiency vs. V<sub>BUS</sub>, I<sub>BUSLIM</sub>=500 mA, I<sub>SYS</sub>=0

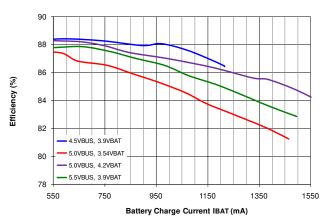

Figure 10. Efficiency vs. Charging Current, IBUSLIM=No Limit

### **Charge Mode Typical Characteristics**

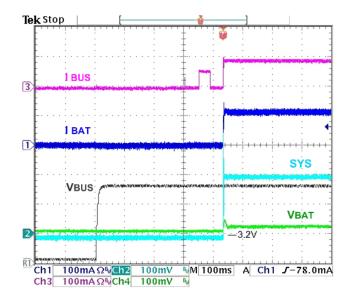

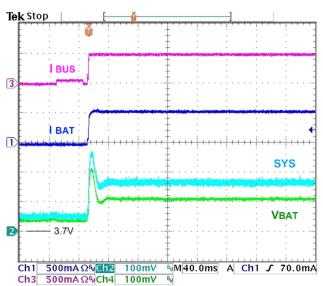

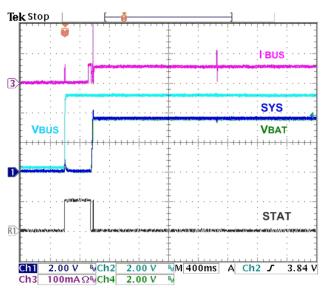

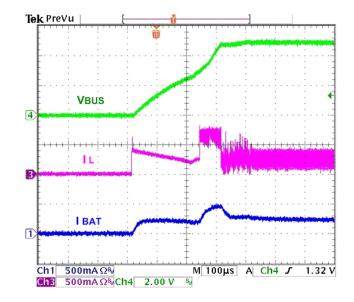

Figure 11. Charger Startup at V<sub>BUS</sub> Plug-In, 100 m A I<sub>BUSLIM</sub>, 3.2 V<sub>BAT</sub>, 100  $\Omega$  SYS Load

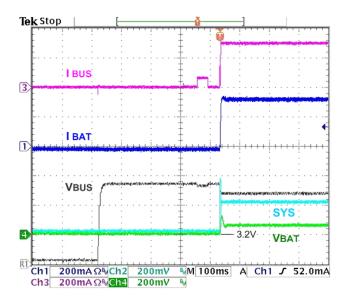

Figure 12. Charger Startup at V  $_{BUS}$  Plug-In, 500 m A  $I_{INBUSLIM},$  3.2 V  $_{BAT},$  100  $\Omega$  SYS Load

Figure 13. Charger Startup at V<sub>BUS</sub> Plug-In Using 300 mA Current Limited Source, 500 mA I<sub>BUSLIM</sub>, 3.2 V<sub>BAT</sub>, 50  $\Omega$  SYS Load

Figure 14. Charger Startup with HZ Bit Reset, 500 m A  $_{\rm IBUSLIM},$  950 m A  $_{\rm ICHARGE},$  50  $\Omega$  SYS Load

### **Charge Mode Typical Characteristics**

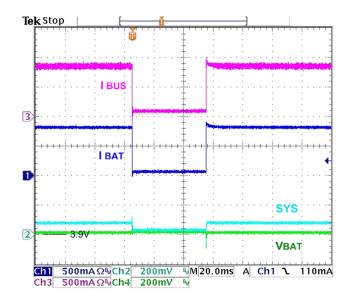

Figure 15. Battery Removal / Insertion while Charging, TE=0, 3.9  $V_{BAT}, I_{CHRG}\!=\!950$  mA,  $I_{BUSLIM}\!=\!No$  Limit, 50  $\Omega$  SYS Load

Figure 16. Battery Removal / Insertion when Charging, TE=1, 3.9 V<sub>BAT</sub>, I<sub>CHRG</sub>=950 mA, I<sub>BUSLIM</sub>=No Limit, 50 Ω SYS Load

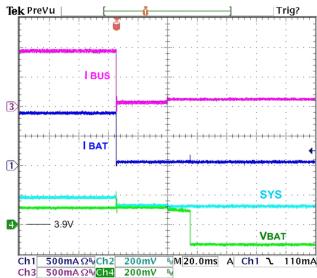

Figure 17. No Battery at V  $_{BUS}$  Power-Up, FAN54040, 100  $\Omega$  SYS Load, 1  $k\Omega$  V  $_{BAT}$  Load

Figure 18. No Battery at  $V_{BUS}$  Power-Up, FAN54042, 100  $\Omega$  SYS Load, 1 k $\Omega$   $V_{BAT}$  Load

SYS

**V**BAT

### **Charge Mode Typical Characteristics**

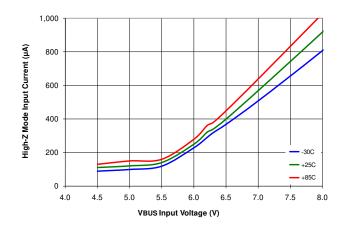

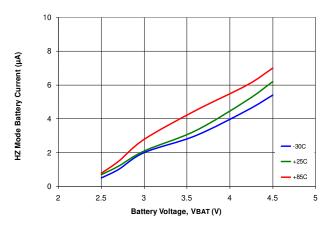

Figure 19. HZ Mode VBUS Current vs. Temperature, 3.7 V<sub>BAT</sub>

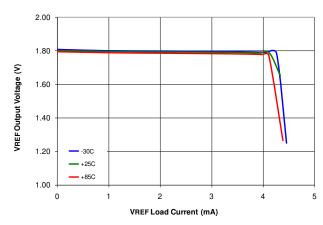

Figure 20. V<sub>REF</sub> vs. Load Current, Over-Temperature, 5.0 V<sub>BUS</sub>

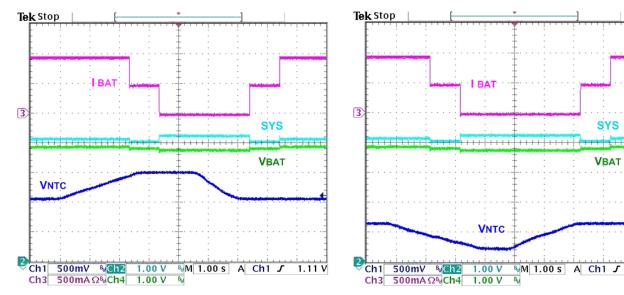

Figure 21. Charging vs. Temperature (NTC), +30°C to -10°CFigure 22 Charging vs. Temperature (NTC), +30°C to +70°C 3.7 V<sub>BAT</sub>, I<sub>CHRG</sub>=950 m A, No I<sub>BUSLIM</sub>, 100 Ω SYS Load 3.7 V<sub>BAT</sub>, I<sub>CHRG</sub>=950 m A, No I<sub>BUSLIM</sub>, 100 Ω SYS Load

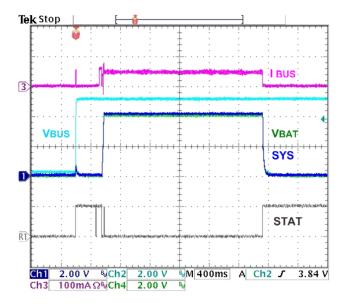

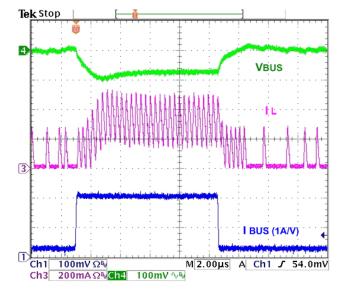

### **GSM Typical Characteristics**

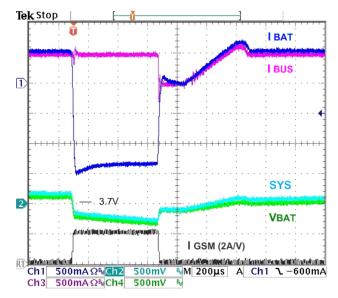

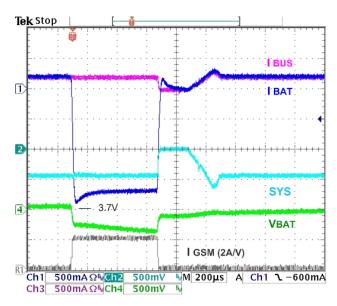

A 2.0 A GSM pulse applied at VBAT with 5  $\mu$ s rise / fall time. Simultaneous to GSM pulse, 50  $\Omega$  additional load applied at SYS.

Figure 23. 2.0 A GSM Pulse Response, I<sub>BUSLIM</sub>=500 m A Control, I<sub>CHRG</sub>=950 m A, 3.7 V<sub>BAT</sub>, OREG=4.2 V

Figure 24. 2.0 A GSM Pulse Response, I<sub>BUSLIM</sub>=500 mA, I<sub>CHRG</sub>=950 mA, 3.7 V<sub>BAT</sub>, OREG=4.2 V, 200 mA Source Current Limit

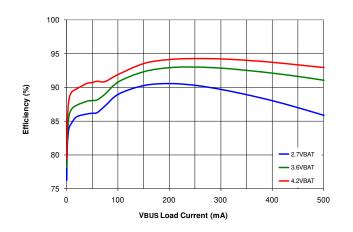

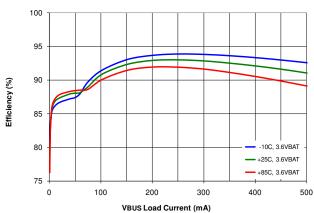

### **Boost Mode Typical Characteristics**

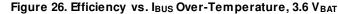

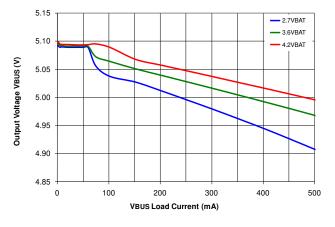

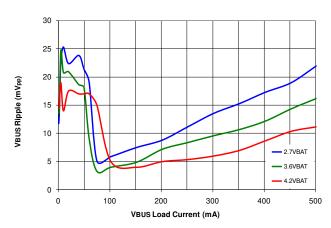

Unless otherwise specified, using circuit of Figure 1, VBAT=3.6 V, TA=25°C.

Figure 25. Efficiency vs. I<sub>BUS</sub> Over V<sub>BAT</sub>

Figure 27. Regulation vs. I<sub>BUS</sub> Over V<sub>BAT</sub>

Figure 28. Output Ripple vs. I<sub>BUS</sub> Over V<sub>BAT</sub>

Figure 29. Quiescent Current (IQ) vs. V<sub>BAT</sub> Over-Temperature

Figure 30. Battery Discharge Current vs. V<sub>BAT</sub>, HZ / Sleep Mode

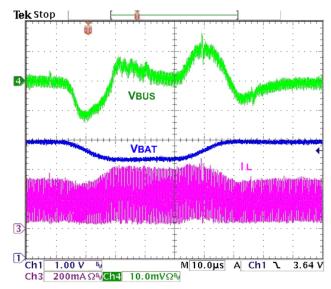

### **Boost Mode Typical Characteristics**

Unless otherwise specified, using circuit of Figure 1, VBAT=3.6 V, TA=25°C.

Tek PreVu

VBUS

VBUS

SW

Chi 5.00 V M M2.00μS A Ch4 \ 3.68 V

Chi 2.00 A Ω% Ch4 \ 2.00 V %

Figure 31. OTG Startup, 50  $\Omega$  Load, 3.6  $V_{BAT}$  External / Additional 10  $\mu f$  on VBUS

Figure 32. OTG V<sub>BUS</sub> Overload Response

Figure 33. Load Transient, 20-200-20 mA  $I_{BUS}$ ,  $t_{RISE/FALL}$ =100 ns

Figure 34. Line Transient, 50  $\Omega$  Load, 3.9-3.3-3.9 V<sub>BAT</sub>, t<sub>RISE/FALL</sub>=10  $\mu$ s

### **Circuit Description / Overview**

When charging batteries with a current-limited input source, such as USB, a switching charger's high efficiency over a wide range of output voltages minimizes charging time.

FAN5404X combines a highly integrated synchronous buck regulator for charging with a synchronous boost regulator, which can supply 5 V to USB On-The-Go (OTG) peripherals. The FAN5404X employs synchronous rectification for both the charger and boost regulators to maintain high efficiency over a wide range of battery voltages and charge states.

The FAN5404X has four operating modes:

- Charge Mode: Charges a single-cell Li-ion or Li-polymer battery.

- Boost Mode: Provides 5 V power to USB-OTG with an integrated synchronous rectification boost regulator, using the battery as input.

- High-Impedance Mode:

Both the boost and charging circuits are OFF in this mode. Current flow from VBUS to the battery or from the battery to VBUS is blocked in this mode. This mode consumes very little current from VBUS or the battery.

- Production Test Mode

This mode provides 4.2 V output on VBAT and supplies a load current of up to 2.3 A.

### **Charge Mode**

In Charge Mode, FAN5404X employs six regulation loops:

- Input Current: Limits the amount of current drawn from VBUS. This current is sensed internally and can be programmed through the I<sup>2</sup>C interface.

- Charging Current: Limits the maximum charging current. This current is sensed using an internal sense MOSFET.

- 3. VBUS Voltage: This loop is designed to prevent the input supply from being dragged below V<sub>BUSLIM</sub> (typically 4.5 V) when the input power source is current limited. An example of this would be a travel charger. This loop cuts back the current when V<sub>BUS</sub> approaches V<sub>BUSLIM</sub>, allowing the input source to run in current limit.

- 4. Charge Voltage: The regulator is restricted from exceeding this voltage. As the internal battery voltage rises, the battery's internal impedance works in conjunction with the charge voltage regulation to decrease the amount of current flowing to the battery. Battery charging is completed when the current through Q4 drops below the ITERM threshold.

- 5. Power Path: When  $V_{BAT}$  is below  $V_{BATMIN}$ , Q4 operates as a linear current source and modulates its current to ensure that the voltage on SYS stays above 3.4 V.

- Temperature: If the IC's junction temperature reaches 120°C, charge current is reduced until the IC's temperature is below 120°C.

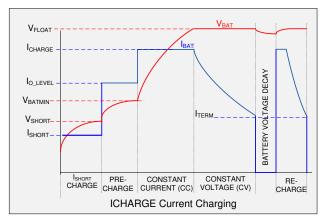

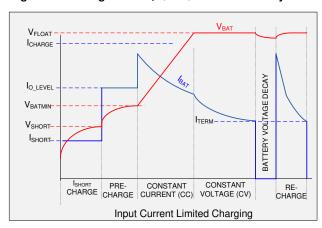

#### **Battery Charging Curve**

If the battery voltage is below  $V_{SHORT}$ , a linear current source pre-charges the battery until  $V_{BAT}$  reaches  $V_{SHORT}$ . The PWM charging circuit is then started and the battery is charged with a constant current if sufficient input power is available. The current slew rate is limited to prevent overshoot.

The FAN5404X is designed to work with a current-limited input source at VBUS. During the current regulation phase of charging, IBUSLIM or the programmed charging current limits the amount of current available to charge the battery and power the system. The effect of IBUSLIM on ICHARGE can be seen in Figure 36.

Figure 35. Charge Curve, ICHARGE Not Limited by IINLIM

Figure 36. Charge Curve, IBUSLIM Limits ICHARGE

Assuming that  $V_{OREG}$  is programmed to the cell's fully charged "float" voltage, the current that the battery accepts with the PWM regulator limiting its output (sensed at VBAT) to  $V_{OREG}$  declines and the charger enters the voltage regulation phase of charging. When the current declines to the programmed  $I_{TERM}$  value, the charge cycle is complete. Charge current termination can be disabled by resetting the TE bit (REG1[3]).

The charger output or "float" voltage can be programmed by the OREG bits from 3.5~V to 4.44~V in 20~mV increments, as shown in Table 4.

The following charging parameters can be programmed by the host through  $^{\circ}\text{C}$ :

**Table 3. Programmable Charging Parameters**

| Parameter                      | Name               | Register  |

|--------------------------------|--------------------|-----------|

| Output Voltage Regulation      | Voreg              | REG2[7:2] |

| Battery Charging Current Limit | lochrg             | REG4[6:3] |

| Input Current Limit            | I <sub>INLIM</sub> | REG1[7:6] |

| Charge Termination Limit       | ITERM              | REG4[2:0] |

| Weak Battery Voltage           | $V_{LOWV}$         | REG1[5:4] |

Table 4. OREG Bits (OREG[7:2]) vs. Charger  $V_{OUT}$  ( $V_{OREG}$ ) Float Voltage

| (VOREG) FIDAL VOILAGE |     |       |  |  |  |

|-----------------------|-----|-------|--|--|--|

| Decimal               | Hex | VOREG |  |  |  |

| 0                     | 00  | 3.50  |  |  |  |

| 1                     | 01  | 3.52  |  |  |  |

| 2                     | 02  | 3.54  |  |  |  |

| 3                     | 03  | 3.56  |  |  |  |

| 4                     | 04  | 3.58  |  |  |  |

| 5                     | 05  | 3.60  |  |  |  |

| 6                     | 06  | 3.62  |  |  |  |

| 7                     | 07  | 3.64  |  |  |  |

| 8                     | 80  | 3.66  |  |  |  |

| 9                     | 09  | 3.68  |  |  |  |

| 10                    | 0A  | 3.70  |  |  |  |

| 11                    | 0B  | 3.72  |  |  |  |

| 12                    | 0C  | 3.74  |  |  |  |

| 13                    | 0D  | 3.76  |  |  |  |

| 14                    | 0E  | 3.78  |  |  |  |

| 15                    | 0F  | 3.80  |  |  |  |

| 16                    | 10  | 3.82  |  |  |  |

| 17                    | 11  | 3.84  |  |  |  |

| 18                    | 12  | 3.86  |  |  |  |

| 19                    | 13  | 3.88  |  |  |  |

| 20                    | 14  | 3.90  |  |  |  |

| 21                    | 15  | 3.92  |  |  |  |

| 22                    | 16  | 3.94  |  |  |  |

| 23                    | 17  | 3.96  |  |  |  |

| Decimal | Hex   | VOREG |

|---------|-------|-------|

| 24      | 18    | 3.98  |

| 25      | 19    | 4.00  |

| 26      | 1A    | 4.02  |

| 27      | 1B    | 4.04  |

| 28      | 1C    | 4.06  |

| 29      | 1D    | 4.08  |

| 30      | 1E    | 4.10  |

| 31      | 1F    | 4.12  |

| 32      | 20    | 4.14  |

| 33      | 21    | 4.16  |

| 34      | 22    | 4.18  |

| 35      | 23    | 4.20  |

| 36      | 24    | 4.22  |

| 37      | 25    | 4.24  |

| 38      | 26    | 4.26  |

| 39      | 27    | 4.28  |

| 40      | 28    | 4.30  |

| 41      | 29    | 4.32  |

| 42      | 2A    | 4.34  |

| 43      | 2B    | 4.36  |

| 44      | 2C    | 4.38  |

| 45      | 2D    | 4.40  |

| 46      | 2E    | 4.42  |

| 47 - 63 | 2F-3F | 4.44  |

#### Note:

- 9. Default settings are denoted by **bold** typeface. Provided DIS, CE# and HZ\_MODE are LOW, a new charge cycle begins when one of the following occurs:

- The battery voltage falls below V<sub>OREG</sub> V<sub>RCH</sub> after charge termination has occurred.

- 2. Any IC write occurs causing the T32 s timer to run.

Products that include the auto-charge feature also begin charging if:

3. VBUS Power-on-Reset (POR) occurs and the battery voltage is below the weak battery threshold (VLOWV).

### Charge Current Limit (I<sub>OCHARGE</sub>)

Table 5. I<sub>OCHARGE</sub> Current as Function of I<sub>OCHARGE</sub> Bits (REG4 [6:3])

| DEC   | BIN       | HEX | I <sub>OCHARGE</sub> (mA) |

|-------|-----------|-----|---------------------------|

| 0     | 0000      | 0   | 550                       |

| 1     | 0001      | 1   | 650                       |

| 2     | 0010      | 2   | 750                       |

| 3     | 0011      | 3   | 850                       |

| 4     | 0100      | 4   | 950                       |

| 5     | 0101      | 5   | 1,050                     |

| 6     | 0110      | 6   | 1,150                     |

| 7     | 0111      | 7   | 1,250                     |

| 8     | 1000      | 8   | 1,350                     |

| 9     | 1001      | 9   | 1,450                     |

| 10-15 | 1010-1111 | A-F | 1,550                     |

When the IO\_LEVEL bit is set (default), the locharge bits are ignored and charge current is set to 340 mA.

#### **PWM Controller in Charge Mode**

The IC uses a current-mode PWM controller to regulate the output voltage and battery charge currents. The synchronous rectifier (Q2) has a negative current limit that turns off Q2 at 140 mA to prevent current flow from the battery.

#### **Termination Current Limit**

Current charge termination is enabled when TE (REG1[3])=1. Typical termination current values are given in Table 6.

Table 6. Termination Current as Function of ITERM Bits (REG4[2:0]) or PC\_IT Bits (REG7[2:0]

| ITERM Bits or PC_IT Bits | Termination Current (mA) |

|--------------------------|--------------------------|

| 0                        | 50                       |

| 1                        | 100                      |

| 2                        | 150                      |

| 3                        | 200                      |

| 4                        | 250                      |

| 5                        | 300                      |

| 6                        | 350                      |

| 7                        | 400                      |

When the charge current falls below I<sub>TERM</sub>; PWM charging stops, but the STAT pin remains LOW. The STAT pin then goes HIGH and the STATUS bits change to CHARGE DONE (10), provided the battery and charger are still connected.

A post-charging feature, "top-off" charging, is available to continue the battery charging to a lower charge current to maximize battery capacity. The PC\_EN bit must be set to 1 before the battery charging current reaches the termination current ITERM for normal charging. The post-charging termination current is set by the PC\_IT[2:0] bits, as shown in Table 6. If PC\_EN is set to 1; right after the normal charging is ended as described above, post charging is started with PC\_ON monitor bit set to 1. Once the current reaches the

threshold for post-charging completion, PWM charging stops and PC  $\,$  ON  $\,$  bit changes back to  $\,$ 0.

During post-charging, the STAT pin is HIGH, indicating that the charge current is below the  $I_{TERM}$  level. To exit post-charging, one of the following must occur: a  $V_{BUS}$  POR, the POK\_B cycled when  $V_{BAT}$  <3.0 V, or the CE# or HZ\_Mode bit cycled.

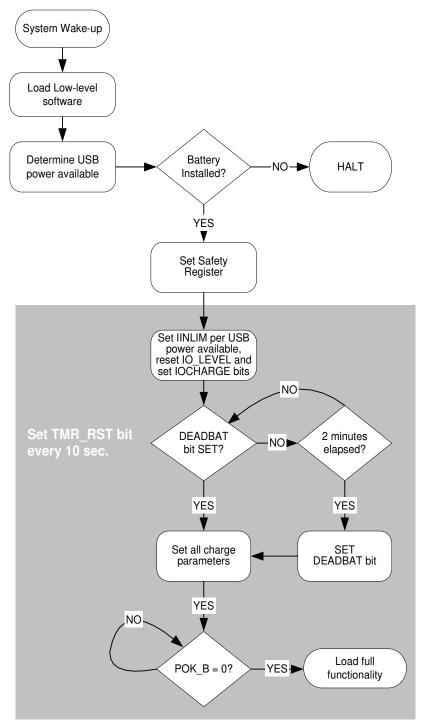

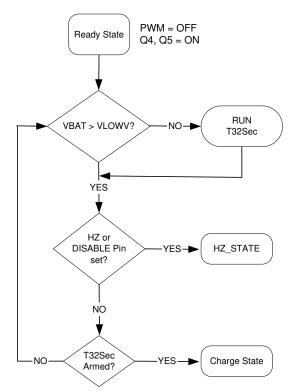

#### Safety Timer

At the beginning of charging, the IC starts a 15-minute timer ( $t_{15\text{MIN}}$ ). When this timer times out, charging is terminated. Writing to any register through I^C stops and resets the  $t_{15\text{MIN}}$  timer, which in turn starts a 32-second timer ( $t_{328}$ ). Setting the TMR\_RST bit (REG0[7]) resets the  $t_{328}$  timer. If the  $t_{328}$  timer times out; charging is terminated, the registers are set to their default values, and charging resumes using the default values with the  $t_{15\text{MIN}}$  timer running.

Normal charging is controlled by the host with the  $t_{32S}$  timer running to ensure that the host is alive. Charging with the  $t_{15\text{MIN}}$  timer running is used for charging unattended by the host. If the  $t_{15\text{MIN}}$  timer expires, the IC turns off the charger and indicates a timer fault (110) on the FAULT bits (REG0[2:0]). This sequence prevents overcharge if the host fails to reset the  $t_{32S}$  timer.

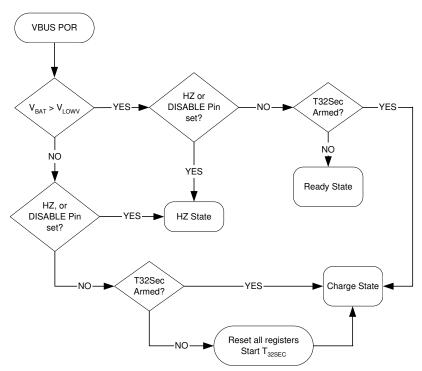

### **V<sub>BUS</sub> POR / Non-Compliant Charger Rejection**

256 ms after VBUS is connected, the IC pulses the STAT pin and sets the VBUS\_CON bit. Before starting to supply current, the IC applies a 110  $\Omega$  load from VBUS to GND. V\_BUS must remain above V\_IN(MIN)1 and below VBUS\_OVP for t\_VBUS\_VALID (32 ms) before the IC initiates charging or supplies power to SYS. The V\_BUS validation sequence alw ays occurs before significant current is drawn from VBUS (for example, after a VBUS OVP fault or a V\_RCH recharge initiation). t\_VBUS\_VALID ensures that unfiltered 50/60 Hz chargers and other non-compliant chargers are rejected.

#### **USB-Friendly Boot Sequence**

At  $V_{BUS}$  POR, when the battery voltage is above the weak battery threshold ( $V_{LOW}$ ); the IC operates in accordance with its  $^{\circ}$ C register settings. If  $V_{BAT}$  <  $V_{LOW}$  and  $t_{32s}$  is not running, the IC sets all registers to their default values and begins to deliver power to SYS.

FAN54040, FAN54042, and FAN54047 feature auto-charge, which allow these parts to deliver charge to the battery prior to receiving host commands.

FAN54041 does not automatically initiate charging at  $V_{BUS}$  POR. Instead, it waits in IDLE state for the host to initiate charging through  $\Gamma^{C}C$  commands. While in IDLE state, Q4 and Q5 are on. This allows the system to run through a separate power path without requiring an additional disconnection MOSFET.

#### **Power Path Operation**

As long as  $V_{BAT} < V_{BATMIN}$ , Q4 operates as a linear current source, (Pow er Path Mode) with its current limited to 340 mA. The IC then regulates SYS to 3.54 V and attempts to charge the battery with as much current as possible with the available  $I_{BUSLIM}$  input current, without allowing SYS to drop below 3.4 V. This ensures that system power always receives first priority from a limited input supply. During this

time, POK\_B is HIGH. If  $V_{BAT} < V_{SHORT}$ , Q4's current is further reduced to about 13 mA ( $I_{SHORT}$ ) when  $I_{BUSLIM}$  is set to 100 or 500 mA. For all other input current limits,  $I_{SHORT}$  current is approximately 30 mA.

The POK\_B signal can be used to keep the system in a low-power state, preventing excessive loading from the system while attempting to charge a depleted battery.

Table 7. VBATMIN Thresholds to Exit Power Path Mode

| I <sub>BUSLIM</sub> (mA) | V <sub>BATMIN</sub> (V) |

|--------------------------|-------------------------|

| 100                      | 3.4                     |

| 500                      | 3.3                     |

| 800                      | 3.2                     |

| No Limit                 | 3.2                     |