# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Is Now Part of

## **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconduc

August 2013

# FAN54300 — USB-Compliant, Dual-Power Input, Single-Cell, Li-Ion Switching Charger with USB-OTG Boost Regulator

### Features

- Fully Integrated, High-Efficiency Charger for Single-Cell Li-Ion and Li-Polymer Battery Packs

- Accepts USB or Dedicated Power Input Source

- 5 V, 300 mA Boost Mode for USB OTG from 2.5 to 4.5 V Battery Input

- Charge Voltage Accuracy:  $\pm 0.5\%$  at T<sub>A</sub>=25°C  $\pm 1\%$  from T<sub>A</sub>=0 to 125°C

- ±5% USB Input Current Regulation Accuracy

- ±5% Charge Current Regulation Accuracy

- 20 V Absolute Maximum Input Voltage

- 9.5 V Maximum Input Operating Voltage on VIN Pin,

6.5 V Maximum on VBUS Pin

- Up to 1.5 A Maximum Charge Rate

- Programmable Charge and Mode through High-Speed I<sup>2</sup>C Interface (3.4 Mb/s) with Fast Mode Plus Compatibility

- Input Current

- Fast-Charge / Termination Current

- Charger Voltage

- Safety Timer

- Termination Enable

- 3 MHz Synchronous Buck PWM Controller with Wide Duty Cycle Range

- Small Footprint, 1 μH, External Inductors

- Safety Timer with Reset Control

- Weak Input Sources Accommodated by Reducing Charging Current to Maintain Minimum V<sub>BUS</sub> Voltage

- Low Reverse Leakage from Battery Drain to VBUS or VIN

- Programmable LED Drive for Charge Indication

- Register and Slave Addresses Compatible with FAN540X and FAN542X Families

## Description

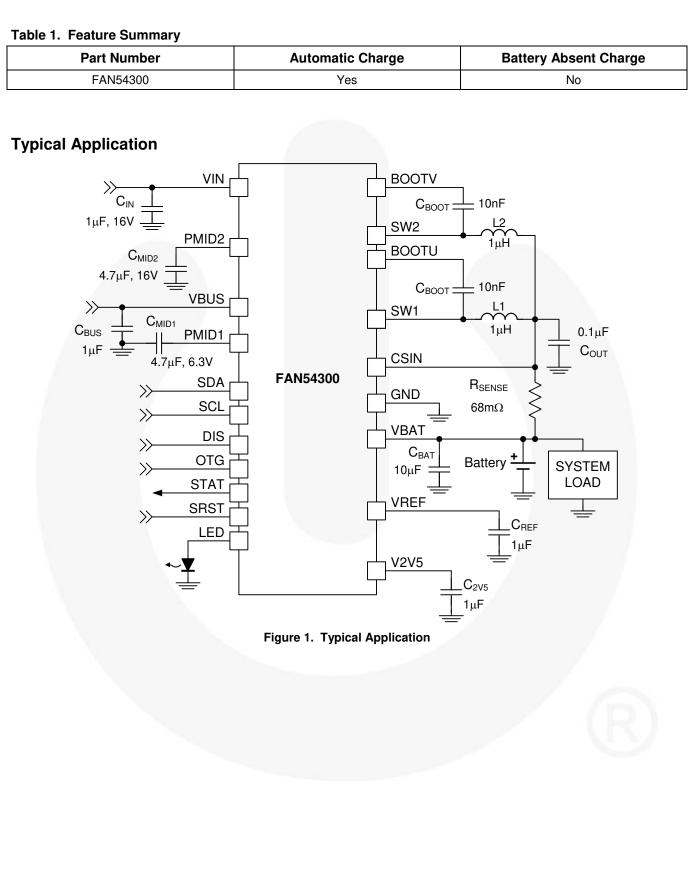

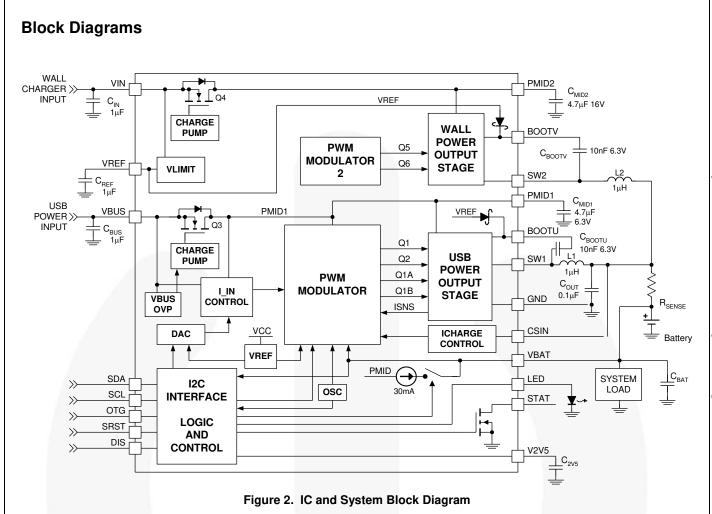

The FAN54300 combines two highly integrated switch-mode chargers and a boost regulator to minimize single-cell Li-Ion charging time from a USB and/or auxiliary power source.

Charging parameters and operating modes are programmable through an I<sup>2</sup>C Bus® interface that operates up to 3.4 Mbps. The charger and boost regulator circuits switch at 3 MHz to minimize the size of the external passive components.

The FAN54300 provides battery charging in three phases: conditioning, constant current, and constant voltage.

To ensure USB compliance and minimize charging time, the USB input current is limited to the value set through the  $l^2C$  host. Charge termination is determined by a programmable minimum current level. A safety timer with reset control provides a safety backup for the  $l^2C$  host.

The IC automatically restarts the charge cycle when the battery falls below an internal threshold. If the input source is removed, the IC enters a high-impedance mode, with leakage from the battery to the input prevented. Charge status is reported back to the host through the  $I^2C$  port. Charge current is reduced when the die temperature reaches 120°C.

The FAN54300 can operate as a boost regulator on command from the system. The boost regulator includes a soft-start that limits inrush current from the battery.

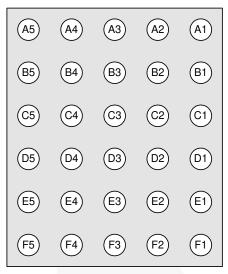

The FAN54300 is available in a 30-bump, 0.4 mm pitch, wafer-level, chip-scale package (WLCSP).

### **Applications**

- Cell Phones, Smart Phones, PDAs

- Digital Cameras

- Portable Media Players

| eracing ine |                   |                                                                  |               |

|-------------|-------------------|------------------------------------------------------------------|---------------|

| Part Number | Temperature Range | Package                                                          | Packing       |

| FAN54300UCX | -40 to 85°C       | 30-Ball, WLCSP, 5x6 Array, 0.4mm Pitch,<br>586 μm Package Height | Tape and Reel |

**Ordering Information**

Table 2. Recommended External Components

| Component                          | Description                   | Vendor                 | Parameter | Тур. | Units |

|------------------------------------|-------------------------------|------------------------|-----------|------|-------|

|                                    | Charge Currents to 1 A:       | Murata: LQM2MPN1R0M    | L         | 1.0  | μH    |

| L1, L2:                            | 1 μH, 20%, 1.3 A, 2016        |                        | DCR       | 85   | mΩ    |

|                                    | Charge Currents Above 1 A:    |                        |           | 1.0  | μH    |

|                                    | 1 μH, 20%, 1.6 A, 2520        | Murata: LQM2HPN1R0M    | DCR       | 55   | mΩ    |

| C <sub>BAT</sub>                   | 10 μF, 20%, 6.3 V, X5R, 0603  | Murata: GRM188R60J106M | С         | 10   | μF    |

| C <sub>MID1,2</sub>                | 4.7 μF, 10%, 16 V, X5R, 0805  | Murata: GRM21BR61C475K | С         | 4.7  | μF    |

| C <sub>IN</sub> , C <sub>BUS</sub> | 1.0 μF, 10%, 16 V, X5R, 0603  | Murata GRM188R61E105K  | С         | 1.0  | μF    |

| C <sub>BOOT</sub>                  | 10 nF, 10%, 6.3 V, X5R, 0201  | Murata GRM033R70J103K  | С         | 10   | nF    |

| C <sub>OUT</sub>                   | 0.1 μF, 10%, 6.3 V, X5R, 0201 | Murata GRM033R60J104K  | С         | 0.1  | μF    |

| $C_{2V5}, C_{REF}$                 | 1μF, 10%, 6.3 V, X5R, 0402    | Murata GRM155R60J105M  | С         | 1.0  | μF    |

## **Pin Configuration**

| BOOTV | VREF | V2V5 | SDA  | BOOTU |

|-------|------|------|------|-------|

| (A1)  | (A2) | (A3) | (A4) | (A5)  |

| V     | N    | SCL  | VB   | US    |

| (B1)  | (B2) | (B3) | (B4) | (B5)  |

| PM    | ID2  | SRST | PM   | ID1   |

| (C1)  | (C2) | (C3) | (C4) | (C5)  |

| SV    | V2   | DIS  | SV   | V1    |

| (D1)  | (D2) | (D3) | (D4) | (D5)  |

|       |      | GND  |      |       |

| E1)   | (E2) | (E3) | (E4) | (E5)  |

| LED   | OTG  | CSIN | VBAT | STAT  |

| (F1)  | (F2) | (F3) | (F4) | (F5)  |

Figure 4. Pin Assignments (Top View)

## **Pin Definitions**

| Pin #  | Name  | Description                                                                                                                                                                                                                                                                                                                                   |

|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |       | •                                                                                                                                                                                                                                                                                                                                             |

| A1     | BOOTV | <b>BOOT</b> . High-side NMOS driver supply. Connect a 10nF capacitor from SW2 to this pin.                                                                                                                                                                                                                                                    |

| A2     | VREF  | <b>Bias Regulator Output</b> . Connect to a 1 $\mu$ F capacitor to PGND. This pin supplies the internal gate drive and power supply to the IC while charging. Up to 5 mA of current can be provided from this pin to drive external circuits. This pin is active when either V <sub>IN</sub> or V <sub>BUS</sub> are above V <sub>BAT</sub> . |

| A3     | V2V5  | <b>2.5 V Regulator</b> . Connect to a 1 $\mu$ F capacitor to PGND. Up to 5 mA can be provided from this pin to drive external circuits. This regulator is powered only when VIN is connected.                                                                                                                                                 |

| A4     | SDA   | I <sup>2</sup> C Interface Serial Data. This pin should not be left floating.                                                                                                                                                                                                                                                                 |

| A5     | BOOTU | BOOT. High-side NMOS driver supply. Connect a 10 nF capacitor from SW1 to this pin.                                                                                                                                                                                                                                                           |

| B1, B2 | VIN   | Charger Input Voltage. Bypass with a minimum of 1 µF, 16 V capacitor to GND.                                                                                                                                                                                                                                                                  |

| B3     | SCL   | I <sup>2</sup> C Interface Serial Clock. This pin should not be left floating.                                                                                                                                                                                                                                                                |

| B4, B5 | VBUS  | USB Input Voltage. Bypass with a 1 $\mu$ F, 16 V capacitor to GND.                                                                                                                                                                                                                                                                            |

| C1, C2 | PMID2 | <b>Power Input Voltage for VIN Power Source</b> . Power input to the charger regulator, bypass point for the VIN input current sense, and high-voltage input switch. Bypass with a minimum of 4.7 $\mu$ F, 16 V capacitor to PGND.                                                                                                            |

| C3     | SRST  | Safety Reset. When LOW, both safety registers are reset to their default values. When HIGH, the safety registers reset when $V_{BAT}$ drops below $V_{SHORT}$ .                                                                                                                                                                               |

| C4, C5 | PMID1 | <b>Power Input Voltage for VBUS Power Source</b> . Power input to the VBUS switching charger regulator, bypass point for the VBUS input current sense, and high-voltage input switch. Bypass with a minimum of 4.7 $\mu$ F, 6.3 V capacitor to PGND.                                                                                          |

| D1, D2 | SW2   | Switching Node for VIN Charger. Connect to the output inductor.                                                                                                                                                                                                                                                                               |

| D3     | DIS   | <b>Charge Disable</b> . When this pin is HIGH, charging is disabled and no timers are reset. When LOW, charging is controlled by the I <sup>2</sup> C registers. This pin does not affect the 32-second timer.                                                                                                                                |

| D4, D5 | SW1   | Switching Node for VBUS Charger and OTG Boost. Connect to the output inductor.                                                                                                                                                                                                                                                                |

| E1–E5  | GND   | <b>Ground</b> . Power return for gate drive and power transistors as well as IC signal ground. The connection from this pin to the bottoms of the $C_{PMID}$ capacitors should be as short as possible.                                                                                                                                       |

| F1     | LED   | Light Emitting Diode Output. Up to 5 mA current source drive from the active PMID indicates the battery is charging.                                                                                                                                                                                                                          |

Figure 5. Pin Assignments (Bottom View)

| Т         |

|-----------|

| ≥         |

| Ž         |

| 154300    |

| μ         |

| õ         |

| 0         |

|           |

|           |

|           |

| S         |

| USB-C     |

| Ь         |

| ŏ         |

| ň         |

| ц<br>Ц    |

| Ĭ         |

| a         |

| 3         |

|           |

|           |

| ual-P     |

| <u>e</u>  |

| ΰ         |

| ŏ         |

| 0W0       |

| e         |

| Ť         |

| F         |

| ď         |

| Ž         |

| ţ,        |

| ഗ         |

| Ť         |

| õ         |

|           |

| ľ         |

| S<br>S    |

| E E       |

| ļ,        |

|           |

| l, Li-lon |

| 9         |

|           |

| S         |

| S         |

| itc       |

| 2         |

| l≓        |

| ЗС        |

| 2         |

| <u>Ω</u>  |

| ۲<br>۲    |

| ar        |

| Ö.        |

| e         |

|           |

| ≤.        |

| İŧ        |

|           |

| C         |

| S         |

| φ         |

| В-O       |

| Ĭ         |

| TG B      |

|           |

| 3         |

| ŏ         |

| Š         |

| t t       |

| Ъ         |

| Э.        |

| Ľ         |

| 8         |

| Ĩť        |

| <u> </u>  |

| _         |

| Pin # | Name | Description                                                                                                                                                                                       |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F2    | OTG  | <b>On The Go</b> . When unattended charging is indicated, the level on this pin sets the $I_{BUS}$ current limit. This pin is also used to put the IC into Boost Mode.                            |

| F3    | CSIN | <b>Current-Sense Input</b> . Connect to sense resistor in series with the battery. The IC uses this node to sense current into the battery. Bypass this pin with a 0.1 $\mu$ F capacitor to PGND. |

| F4    | VBAT | <b>Battery Voltage</b> . Connect to the positive (+) terminal of the battery pack. Bypass with a 10 $\mu$ F capacitor to PGND.                                                                    |

| F5    | STAT | Status. Open-drain output indicating charge status. The IC pulls this pin LOW when charging is in process.                                                                                        |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                                     |                                            | Parameter                             | Min. | Max.               | Unit |

|--------------------------------------------|--------------------------------------------|---------------------------------------|------|--------------------|------|

| N/                                         |                                            | Continuous                            | -1.4 | 00.0               | V    |

| V <sub>BUS</sub>                           | VBUS Voltage                               | Pulsed, 100 ms Maximum Non-Repetitive | -2.0 | 20.0               | V    |

| V <sub>IN</sub>                            | VIN Voltage                                |                                       | -2.0 | 20.0               | V    |

| V <sub>BOOTU</sub>                         | BOOTU Voltage                              |                                       | -0.7 | 20.0               | V    |

| V <sub>BOOTV</sub>                         | BOOTV Voltage                              |                                       | -0.7 | 20.0               | V    |

| $V_{PMID1}$                                | PMID1 Voltage                              |                                       | -1.0 | 20.0               | V    |

| V <sub>SW1</sub>                           | SW1 Voltage                                |                                       | -0.7 | 6.5                | V    |

| V <sub>PMID2</sub>                         | PMID2 Voltage                              | 1                                     | -1.0 | 20.0               | V    |

| V <sub>SW2</sub>                           | SW2 Voltage                                |                                       | -0.7 | 12.0               | V    |

| Vo                                         | Other Pins                                 |                                       | -0.3 | 6.5 <sup>(1)</sup> | V    |

| $\frac{\text{dV}_{\text{BUS}}}{\text{dt}}$ | Maximum Rate of V <sub>BUS</sub> Increase  | Above 5.5 V when IC Enabled           |      | 4                  | V/µs |

| dV <sub>IN</sub><br>dt                     | Maximum Rate of V <sub>IN</sub> Increase A | Above 9.5 V when IC Enabled           |      | 4                  | V/µs |

| ESD                                        | Electrostatic Discharge                    | Human Body Model per JESD22-A114      | 2    | .0                 | kV   |

| ESD                                        | Protection Level                           | Charged Device Model per JESD22-C101  | 1.5  |                    | kV   |

| TJ                                         | Junction Temperature                       |                                       | -40  | +150               | °C   |

| T <sub>STG</sub>                           | Storage Temperature                        |                                       | -65  | +150               | °C   |

| TL                                         | Lead Soldering Temperature, 10             | ) Seconds                             |      | +260               | °C   |

Note:

1. Lesser of 6.5 V or  $V_{REF}$  + 0.3 V.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol           | Parameter            | Min. | Max. | Units |

|------------------|----------------------|------|------|-------|

| V <sub>BUS</sub> | VBUS Supply Voltage  | 4    | 6    | V     |

| V <sub>IN</sub>  | VIN Supply Voltage   | 4.0  | 9.5  | V     |

| TA               | Ambient Temperature  | -30  | +85  | °C    |

| TJ               | Junction Temperature | 0    | +125 | °C    |

## **Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperate  $T_A$ .

| ; | Symbol        | Parameter                              | Typical | Unit |

|---|---------------|----------------------------------------|---------|------|

|   | $\theta_{JA}$ | Junction-to-Ambient Thermal Resistance | 60      | °C/W |

|   | $\theta_{JB}$ | Junction-to-PCB Thermal Resistance     |         | °C/W |

## **Electrical Specifications**

Unless otherwise specified: circuit of Figure 1, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS}$  or  $V_{IN} = 5.0$  V, HZ1, HZ2, OPA\_MODE = 0, (Charger Mode). SCL, SDA, OTG = 0 or 1.8 V. Typical values are for  $T_J = 25^{\circ}$ C.

| Symbol              | Parameter                                   | Conditions                                                                                                                                                                                        | Min. | Тур. | Max. | Units   |

|---------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------|

| Power Su            | pplies                                      |                                                                                                                                                                                                   |      |      |      |         |

|                     |                                             | PWM Switching, Open Battery, TE=0                                                                                                                                                                 |      | 33   |      | mA      |

|                     |                                             | PWM Not Switching (V <sub>BAT</sub> > V <sub>OREG</sub> )                                                                                                                                         |      | 3.6  |      | mA      |

| I <sub>VBUS</sub>   | VBUS Current                                | $0^{\circ}C < T_J < 85^{\circ}C, \ HZ1 = 1, \ V_{BAT} > V_{LOWV}$                                                                                                                                 |      | 350  | 500  | μΑ      |

|                     |                                             | $0^{\circ}C < T_J < 85^{\circ}C,  HZ1$ = 1, $V_{BAT} < V_{LOWV},  32S$ Mode                                                                                                                       |      | 350  | 500  | μA      |

|                     |                                             | PWM Switching, Open Battery, TE=0                                                                                                                                                                 |      | 33   |      | mA      |

|                     |                                             | PWM Not Switching (VBAT>VOREG)                                                                                                                                                                    | 100  | 2.6  |      | mA      |

| I <sub>VIN</sub>    | VIN Current                                 | $0^{\circ}C < T_J < 85^{\circ}C, \ HZ2 = 1, \ V_{IN} > V_{LOWV}$                                                                                                                                  | 1    | 350  | 500  | μΑ      |

|                     |                                             | $\begin{array}{l} 0^{\circ}C < T_{J} < 85^{\circ}C,  HZ2 = 1,  V_{IN} < V_{LOWV}, \\ 32S \; Mode \end{array}$                                                                                     |      | 350  | 500  | μA      |

|                     | Detter Discharze Current in                 | $0^{\circ}C < T_J < 85^{\circ}C,  HZ1 = HZ2 = 1 \text{ or} \\ DIS=1,  V_{BAT} = 4.2 \text{ V}$                                                                                                    |      |      | 20   | μA      |

| I <sub>BAT</sub>    | Battery Discharge Current in<br>High-Z Mode | $\begin{array}{l} 0^{\circ}C < T_{J} < 85^{\circ}C, \ V_{BAT} = 4.2 \ V, \ V_{IN} = \\ V_{BUS} = \ Open \ or \ GND, \ HZ1 = HZ2 = 1, \\ SDA = SCL = 1.8 \ V, \ No \ I^{2}C \ Traffic \end{array}$ |      |      | 30   | μΑ      |

| Charger \           | oltage Regulation                           |                                                                                                                                                                                                   |      |      |      |         |

|                     | Charge Voltage Range                        |                                                                                                                                                                                                   | 3.5  |      | 4.4  | V       |

| V <sub>OREG</sub>   | Charge Voltage Accuracy                     | $T_A = 25^{\circ}C$                                                                                                                                                                               | -0.5 |      | +0.5 | %       |

|                     |                                             | $T_J = 0$ to 125°C                                                                                                                                                                                | -1   |      | +1   | %       |

| Charging            | Current Regulation                          |                                                                                                                                                                                                   |      |      |      |         |

|                     | Output Charge Current Range                 | $V_{LOWV} < V_{BAT} < V_{OREG},$<br>$V_{BUS} > V_{SLP}, R_{SENSE} = 68 m\Omega$                                                                                                                   | 550  |      | 1500 | mA      |

| IOCHRG              | Charge Current Accuracy                     | $20 \text{ mV} \leq V_{IREG} \leq 40 \text{ mV}$                                                                                                                                                  | 92   | 97   | 102  | % of    |

|                     | Across R <sub>SENSE</sub>                   | $V_{IREG} > 40 \text{ mV}$                                                                                                                                                                        | 94   | 97   | 100  | Setting |

| Weak-Bat            | Itery Detection                             |                                                                                                                                                                                                   | 1    |      |      |         |

| V <sub>LOWV</sub>   | Weak-Battery Threshold<br>Accuracy          | $3.4 \le V_{LOWV} \le 3.7$                                                                                                                                                                        | -5   |      | +5   | %       |

|                     | Weak Battery Deglitch Time                  | Rising Voltage, 2 mV Overdrive                                                                                                                                                                    |      | 30   |      | ms      |

| Logic Lev           | vels: DIS, SDA, SCL, OTG                    |                                                                                                                                                                                                   |      |      |      | •       |

| V <sub>IH</sub>     | HIGH-Level Input Voltage                    |                                                                                                                                                                                                   | 1.05 |      |      | V       |

| VIL                 | LOW-Level Input Voltage                     |                                                                                                                                                                                                   |      |      | 0.4  | V       |

| I <sub>IN</sub>     | Input Bias Current                          | Input Tied to GND or V <sub>BAT</sub>                                                                                                                                                             |      | 0.01 | 1.00 | μA      |

| Charge T            | ermination Detection                        |                                                                                                                                                                                                   |      |      |      |         |

|                     | Termination Current Range                   | $\label{eq:VBAT} \begin{split} V_{\text{BAT}} &> V_{\text{OREG}} - V_{\text{RCH}},  V_{\text{BUS}} > V_{\text{SLP}}, \\ R_{\text{SENSE}} &= 68 \ \text{m}\Omega \end{split}$                      | 50   |      | 400  | mA      |

| L                   | Termination Current Assures                 | $[V_{CSIN}-V_{BAT}]$ from 3 mV to 20 mV                                                                                                                                                           | -25% |      | +25% |         |

| I <sub>(TERM)</sub> | Termination Current Accuracy                | $[V_{CSIN}-V_{BAT}]$ from 20 mV to 40 mV                                                                                                                                                          | -5%  |      | +5%  |         |

|                     | Termination Current Deglitch<br>Time        | 2 mV Overdrive                                                                                                                                                                                    |      | 30   |      | ms      |

## Electrical Specifications (Continued)

Unless otherwise specified: circuit of Figure 1, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS}$  or  $V_{IN} = 5.0$  V, HZ1, HZ2, OPA\_MODE = 0, (Charger Mode). SCL, SDA, OTG = 0 or 1.8V. Typical values are for  $T_J = 25^{\circ}$ C.

| Symbol                      | Parameter                                                                            | Conditions                                                                          | Min. | Тур.  | Max. | Units |

|-----------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|-------|------|-------|

| VBUS Inp                    | ut Power Source Detection                                                            |                                                                                     |      |       |      |       |

| V <sub>BUS(MIN)1</sub>      | V <sub>BUS</sub> Input Voltage Rising                                                | To Start VBUS Validation                                                            | 4.20 | 4.30  | 4.40 | V     |

| V <sub>BUS(MIN)2</sub>      | Min. V <sub>BUS</sub> to Pass Validation                                             | During V <sub>BUS</sub> Validation Period                                           | 4.00 | 4.08  | 4.15 | V     |

| V <sub>BUS(MIN)3</sub>      | Min. V <sub>BUS</sub> During Charge                                                  | During Charging                                                                     | 3.64 | 3.71  | 3.78 | V     |

| tvbus_valid                 | V <sub>BUS</sub> Validation Time                                                     |                                                                                     |      | 30    |      | ms    |

| VBUSLOAD                    | V <sub>BUS</sub> Load                                                                | $V_{BUS} = 5 V$ , Applied at $V_{BUS}$ Validation                                   |      | 50    |      | mA    |

| VIN Input                   | Power Source Detection                                                               |                                                                                     |      |       | I.   |       |

| V <sub>IN(MIN)1</sub>       | VIN Input Voltage Rising                                                             | To Start VIN Validation                                                             | 4.20 | 4.30  | 4.40 | V     |

| V <sub>IN(MIN)2</sub>       | Min. V <sub>IN</sub> to Pass Validation                                              | During VIN Validation Period                                                        | 4.00 | 4.08  | 4.15 | V     |

| V <sub>IN(MIN)3</sub>       | Min. V <sub>IN</sub> During Charge                                                   | During Charging                                                                     | 3.64 | 3.71  | 3.78 | V     |

| t <sub>VBUS_VALID</sub>     | V <sub>IN</sub> Validation Time                                                      |                                                                                     |      | 30    |      | ms    |

| VINLOAD                     | V <sub>IN</sub> Load                                                                 | $V_{IN} = 5 V$ , Applied at $V_{IN}$ Validation                                     |      | 50    |      | mA    |

| Input Curr                  | ent Limit                                                                            |                                                                                     |      |       |      |       |

|                             | VBUS Input Current-Limit                                                             | I <sub>BUS</sub> set to 100 mA                                                      | 88   | 93    | 98   |       |

| BUSLIM                      | Threshold                                                                            | I <sub>BUS</sub> set to 500 mA                                                      | 450  | 475   | 500  | - mA  |

| V <sub>2V5</sub> 2.5V I     | inear Regulator                                                                      |                                                                                     |      |       |      |       |

| M                           | 2.5 V Regulator Output                                                               | $I_{2V5}$ from 0 to 5 mA, $V_{IN} > 4.75$ V                                         | 2.35 | 2.50  | 2.65 | V     |

| V <sub>2V5</sub>            | Current Limit                                                                        |                                                                                     | 6    | 8     |      | mA    |

| V <sub>REF</sub> Bias       | Generator                                                                            |                                                                                     |      |       |      |       |

| M                           | Bias regulator voltage                                                               | $V_{IN} > V_{IN(MIN)}$                                                              | 3.5  |       | 6.0  | V     |

| $V_{REF}$                   | current limit                                                                        |                                                                                     | 10   | 15    |      | mA    |

| Battery Re                  | echarge Threshold                                                                    |                                                                                     |      |       |      |       |

| V                           | Recharge Threshold                                                                   | Below V <sub>(OREG)</sub>                                                           | 100  | 120   | 150  | mV    |

| V <sub>RCH</sub>            | Deglitch Time                                                                        | VBAT falling below V <sub>RCH</sub> threshold                                       |      | 130   |      | ms    |

| STAT Out                    | put                                                                                  |                                                                                     |      |       |      |       |

| V <sub>STAT(OL)</sub>       | STAT Output LOW                                                                      | I <sub>STAT</sub> = 10 mA                                                           |      |       | 0.4  | V     |

| I <sub>STAT(OH)</sub>       | STAT High Leakage Current                                                            | V <sub>STAT</sub> = 5 V                                                             |      |       | 1    | μA    |

| LED Outp                    | ut                                                                                   |                                                                                     |      | 1     |      |       |

| $I_{\text{LED}(\text{ON})}$ | LED Output Current Accuracy                                                          | $V_{LED}$ from 1.5 to 3.5 V,<br>Max. ( $V_{REF}$ , $V_{BAT}$ ) – $V_{LED}$ > 100 mV | -30  |       | +30  | %     |

| I <sub>LED(OFF)</sub>       | LED Off-State Leakage Current                                                        | V <sub>LED</sub> = 0 V                                                              |      |       | 1    | μA    |

| Battery De                  | etection                                                                             |                                                                                     |      |       |      | 1     |

| I <sub>DETECT</sub>         | Battery Detection Current Before<br>Charge Complete<br>(Sink Current) <sup>(2)</sup> | Begins After Termination Detected and $V_{BAT} \leq V_{OREG} - V_{RCH}$             |      | -0.45 |      | mA    |

| <b>t</b> DETECT             | Battery Detection time                                                               |                                                                                     |      | 262   |      | ms    |

Continued on the following page ...

## Electrical Specifications (Continued)

Unless otherwise specified: circuit of Figure 1, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS}$  or  $V_{IN} = 5.0$  V, HZ1, HZ2, OPA\_MODE = 0, (Charger Mode). SCL, SDA, OTG = 0 or 1.8 V. Typical values are for  $T_J = 25^{\circ}$ C.

| Symbol                | Parameter                                                                              | Conditions                                                                                 | Min. | Тур. | Max. | Units |

|-----------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|-------|

| Sleep Cor             | nparator                                                                               | •                                                                                          |      |      | •    |       |

| $V_{\text{SLP}}$      | $      Sleep Mode Entry Threshold, \\ V_{BUS} - V_{BAT} \mbox{ or } V_{IN} - V_{BAT} $ | $2.3 \text{ V} \leq \text{V}_{BAT} \leq \text{V}_{OREG}, \text{V}_{PWRIN} \text{ Falling}$ | 0    | 90   | 160  | mV    |

|                       | Sleep Mode Exit Hysteresis                                                             | 2.3 V ≤ V <sub>BAT</sub> ≤ V <sub>OREG</sub>                                               |      | 40   |      | mV    |

| $V_{\text{SLP}}$ EXIT | Deglitch Time for $V_{BUS}$ Rising Above $V_{SLP} + V_{SLP\_EXIT}$                     | Rising Voltage                                                                             |      | 30   |      | ms    |

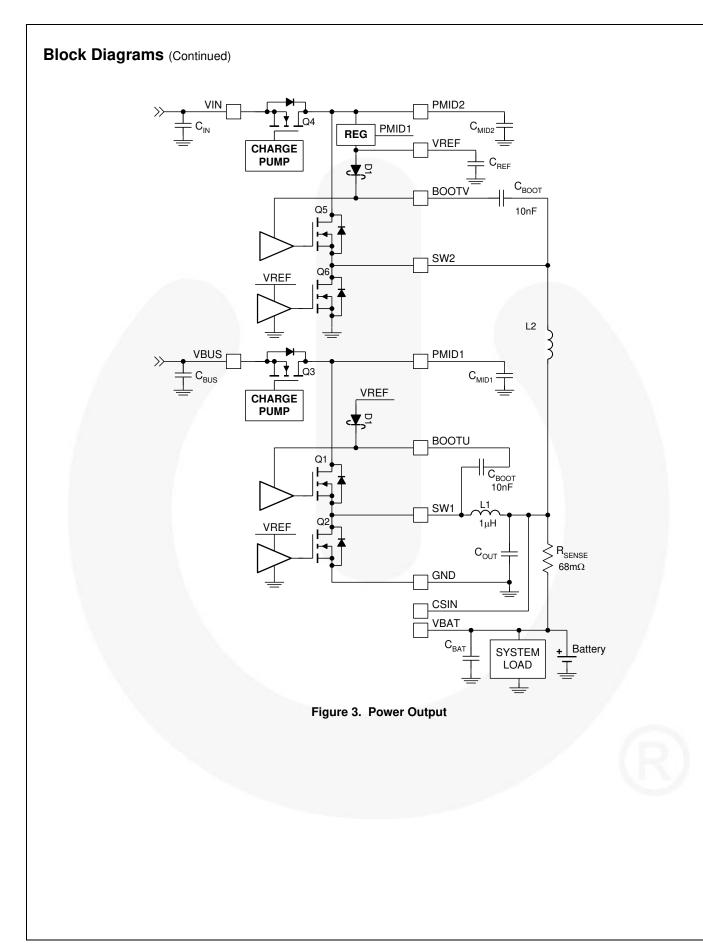

| Power Sw              | itches (see Figure 3)                                                                  |                                                                                            |      |      |      |       |

|                       | Q3 On Resistance<br>(VBUS to PMID1)                                                    | $ BUS_{(LIMIT)} \ge 500 \text{ mA}$                                                        |      | 210  | 300  |       |

| -                     | Q1 On Resistance<br>(PMID1 to SW1)                                                     |                                                                                            |      | 110  | 225  |       |

| P                     | Q2 On Resistance<br>(SW1 to GND)                                                       |                                                                                            |      | 130  | 225  |       |

| R <sub>DS(ON)</sub>   | Q4 On Resistance<br>(VIN to PMID2)                                                     |                                                                                            |      | 160  | 225  | mΩ    |

|                       | Q5 On Resistance<br>(PMID2 to SW2)                                                     |                                                                                            |      | 110  | 225  |       |

|                       | Q6 On Resistance<br>(SW2 to GND)                                                       |                                                                                            |      | 190  | 350  |       |

| Charger F             | WM Modulator                                                                           |                                                                                            |      |      |      |       |

| f <sub>SW</sub>       | Oscillator Frequency                                                                   |                                                                                            | 2.7  | 3.0  | 3.3  | MHz   |

| D <sub>MAX</sub>      | Maximum Duty Cycle                                                                     |                                                                                            |      |      | 100  | %     |

| D <sub>MIN</sub>      | Minimum Duty Cycle                                                                     |                                                                                            |      | 0    |      | %     |

| I <sub>SYNC</sub>     | Synchronous to Non-<br>Synchronous Current<br>Threshold <sup>(3)</sup>                 | Low-Side MOSFET Cycle-by-Cycle<br>Current Limit                                            |      | -120 |      | mA    |

| Boost Mo              | de Operation (OPA_MODE = 1,                                                            | HZ1 = 0)                                                                                   |      | 1    |      |       |

| N                     |                                                                                        | $2.5 \text{ V} < \text{V}_{BAT} < 4.5 \text{ V}, 0-200 \text{ mA Load}$                    | 4.80 | 5.05 | 5.17 | V     |

| V <sub>BOOST</sub>    | Boost Output Voltage at VBUS                                                           | $2.7 \text{ V} < \text{V}_{\text{BAT}} < 4.5 \text{ V}, 0-300 \text{ mA Load}$             | 4.77 | 5.05 | 5.17 | v     |

| BAT(BOOST)            | Boost Mode Quiescent Current                                                           | PFM Mode, $V_{IN} = 3.6 \text{ V}$ , $I_{OUT} = 0$                                         |      | 300  | 400  | μA    |

| ILIMPK(BST)           | Q2-Peak Current Limit                                                                  |                                                                                            | 1160 | 1380 | 1550 | mA    |

| V <sub>BAT(MAX)</sub> | Maximum Battery Input for<br>Boost Operation                                           | V <sub>BAT</sub> Rising                                                                    | 4.7  | 1    |      | V     |

|                       | Hysteresis                                                                             | V <sub>BAT</sub> Falling                                                                   |      | 125  |      | mV    |

| UVLO <sub>BST</sub>   | Minimum Battery Voltage for                                                            | While Boost Active                                                                         |      | 2.42 |      | v     |

| OVLOBSI               | Boost Operation                                                                        | To Start Boost Regulator                                                                   |      | 2.58 | 2.70 | v     |

| VBUS, VII             | Load Resistance                                                                        |                                                                                            |      |      |      |       |

| R <sub>VBUS</sub>     | VBUS to GND Resistance                                                                 | Normal Operation                                                                           | 500  | 1000 | 1500 | Ω     |

| IVBUS                 |                                                                                        | V <sub>BUS</sub> Validation                                                                | 50   | 110  | 175  | Ω     |

| D.                    |                                                                                        | Normal Operation                                                                           | 500  | 1000 | 1500 | Ω     |

| R <sub>VIN</sub>      | VIN to GND Resistance                                                                  | V <sub>IN</sub> Validation                                                                 | 50   | 110  | 175  | Ω     |

Continued on the following page ...

## Electrical Specifications (Continued)

Unless otherwise specified: circuit of Figure 1, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS}$  or  $V_{IN} = 5.0$  V, HZ1, HZ2, OPA\_MODE = 0, (Charger Mode). SCL, SDA, OTG = 0 or 1.8 V. Typical values are for  $T_J = 25^{\circ}$ C.

| Symbol               | Parameter                                   | Conditions                            | Min. | Тур. | Max. | Units |  |

|----------------------|---------------------------------------------|---------------------------------------|------|------|------|-------|--|

| Protection           | and Timers                                  | •                                     | ·    |      |      | •     |  |

| VBUSOVP              | VBUS Over-Voltage Shutdown                  | V <sub>BUS</sub> Rising               | 6.12 | 6.31 | 6.50 | V     |  |

|                      | Hysteresis                                  | V <sub>BUS</sub> Falling              |      | 100  |      | mV    |  |

| VINOVP               | VIN Over-Voltage Shutdown                   | V <sub>IN</sub> Rising                | 9.5  | 10.0 | 10.5 | V     |  |

|                      | Hysteresis                                  | V <sub>IN</sub> Falling               |      | 100  |      | mV    |  |

| V <sub>SHORT</sub>   | Battery Short-Circuit Threshold             | V <sub>BAT</sub> Rising               | 2.00 | 2.05 | 2.10 | V     |  |

|                      | Hysteresis                                  | V <sub>BAT</sub> Falling              |      | 100  |      | V     |  |

| I <sub>SHORT</sub>   | Short-Circuit Current                       | V <sub>BAT</sub> < V <sub>SHORT</sub> | 30   | 40   | 50   | mA    |  |

| Ŧ                    | Thermal Shutdown Threshold <sup>(4)</sup>   | T <sub>J</sub> Rising                 |      | 165  |      |       |  |

| T <sub>SHUTDWN</sub> | Hysteresis <sup>(4)</sup>                   | T <sub>J</sub> Falling                | 6    | 10   |      | °C    |  |

| $T_{CF}$             | Thermal Regulation Threshold <sup>(4)</sup> | Charge Current Reduction Begins       |      | 120  |      | °C    |  |

| t <sub>INT</sub>     | Detection Interval                          |                                       |      | 2.1  |      | S     |  |

| t <sub>32SEC</sub>   | 32-Second Timer <sup>(5)</sup>              | 32-Second Mode                        | 21.0 |      | 31.5 | S     |  |

| t <sub>15MIN</sub>   | 15-Minute Timer                             | 15-Minute Mode                        | 12.0 | 13.5 | 15.0 | min   |  |

| $\Delta t_{LF}$      | Low Frequency Timer Accuracy                | Charger Inactive                      | -25  |      | 25   | %     |  |

#### Notes:

2. Refers to negative inductor current. At lower battery charging current, of about 20 mA, non-synchronous switching operation commences.

3. Q2 and Q6 always turn on for »60 ns and then turn off if the current is below I<sub>SYNC</sub>.

4. Guaranteed by design.

5. This tolerance applies to all timers on the IC, including soft-start and deglitching timers.

FAN54300

Ī

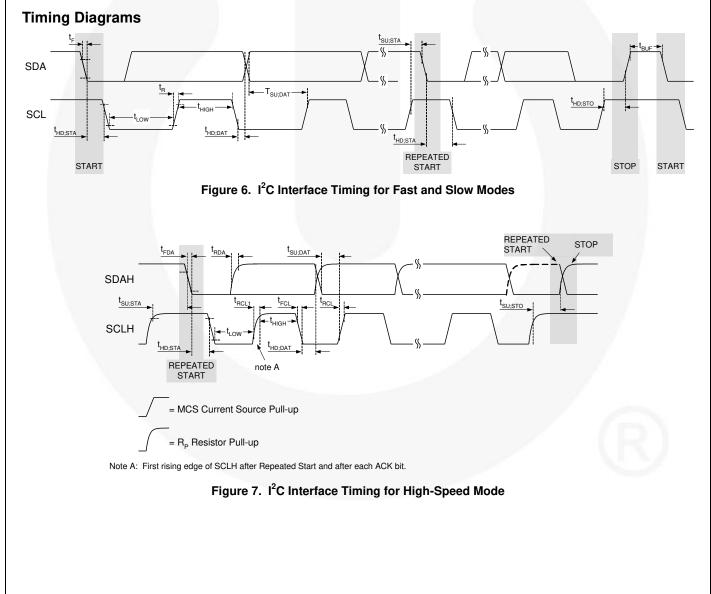

## I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol              | Parameter                                          | Conditions                                 | Min. | Тур.                 | Max. | Uni      |  |

|---------------------|----------------------------------------------------|--------------------------------------------|------|----------------------|------|----------|--|

| f <sub>SCL</sub>    |                                                    | Standard Mode                              |      |                      | 100  |          |  |

|                     |                                                    | Fast Mode                                  |      |                      | 400  |          |  |

|                     | SCL Clock Frequency                                | High-Speed Mode, C <sub>B</sub> ≤ 100 pF   |      |                      | 3400 | kH:      |  |

|                     |                                                    | High-Speed Mode, C <sub>B</sub> ≤ 400 pF   |      |                      | 1700 |          |  |

| t <sub>BUF</sub>    | Bus-Free Time between STOP<br>and START Conditions | Standard Mode                              |      | 4.7                  |      |          |  |

|                     |                                                    | Fast Mode                                  |      | 1.3                  |      | μS       |  |

|                     | START or Repeated START<br>Hold Time               | Standard Mode                              |      | 4                    |      | μS       |  |

| t <sub>HD;STA</sub> |                                                    | Fast Mode                                  |      | 600                  |      | ns       |  |

| 412,017             |                                                    | High-Speed Mode                            |      | 160                  |      | ns       |  |

|                     |                                                    | Standard Mode                              |      | 4.7                  |      | μ        |  |

|                     |                                                    | Fast Mode                                  |      | 1.3                  |      | μ        |  |

| t <sub>LOW</sub>    | SCL LOW Period                                     | High-Speed Mode, $C_B \leq 100 \text{ pF}$ |      | 160                  |      | ns       |  |

|                     |                                                    | High-Speed Mode, $C_B \leq 400 \text{ pF}$ |      | 320                  |      | n        |  |

|                     |                                                    | Standard Mode                              |      | 4                    |      | μ        |  |

|                     | SCL HIGH Period                                    | Fast Mode                                  |      | 600                  |      | n:       |  |

| t <sub>HIGH</sub>   |                                                    | High-Speed Mode, $C_B \le 100 \text{ pF}$  |      | 60                   |      | n        |  |

|                     |                                                    | High-Speed Mode, $C_B \leq 400 \text{ pF}$ |      | 120                  |      | n        |  |

|                     | Repeated START Setup Time                          | Standard Mode                              |      | 4.7                  |      |          |  |

|                     |                                                    | Fast Mode                                  |      | 600                  |      | μ        |  |

| tsu;sta             |                                                    | High-Speed Mode                            |      | 160                  |      | n:<br>n: |  |

|                     |                                                    | Standard Mode                              |      | 250                  |      | 11       |  |

|                     | Data Catur Time                                    |                                            |      | 100                  |      | n        |  |

| tsu;dat             | Data Setup Time                                    | Fast Mode                                  |      |                      |      |          |  |

|                     |                                                    | High-Speed Mode                            | 0    | 10                   | 0.45 |          |  |

|                     | Data Hold Time                                     | Standard Mode                              | 0    |                      | 3.45 | μ        |  |

| t <sub>HD;DAT</sub> |                                                    | Fast Mode                                  | 0    |                      | 900  | n        |  |

|                     |                                                    | High-Speed Mode, $C_B \leq 100 \text{ pF}$ | 0    |                      | 70   | n        |  |

|                     |                                                    | High-Speed Mode, $C_B \leq 400 \text{ pF}$ | 0    |                      | 150  | n        |  |

|                     | SCL Rise Time                                      | Standard Mode                              |      | ).1C <sub>B</sub>    | 1000 |          |  |

| t <sub>RCL</sub>    |                                                    | Fast Mode                                  | 20+0 | ).1C <sub>B</sub>    | 300  | n        |  |

|                     |                                                    | High-Speed Mode, $C_B \leq 100 \text{ pF}$ |      | 10                   | 80   |          |  |

|                     |                                                    | High-Speed Mode, $C_B \leq 400 \text{ pF}$ |      | 20                   | 160  |          |  |

|                     | SCL Fall Time                                      | Standard Mode                              |      | ).1C <sub>B</sub>    | 300  |          |  |

| t <sub>FCL</sub>    |                                                    | Fast Mode                                  | 20+0 | ).1C <sub>B</sub>    | 300  | n        |  |

| чғс                 |                                                    | High-Speed Mode, $C_B \leq 100 \text{ pF}$ |      | 10                   | 40   |          |  |

|                     |                                                    | High-Speed Mode, $C_B \leq 400 \text{ pF}$ |      | 20                   | 80   |          |  |

|                     | SDA Rise Time<br>Rise Time of SCL after a          | Standard Mode                              | 20+0 | 20+0.1C <sub>B</sub> |      |          |  |

| t <sub>RDA</sub>    |                                                    | Fast Mode                                  | 20+0 | ).1C <sub>B</sub>    | 300  | ns       |  |

| t <sub>RCL1</sub>   | Repeated START Condition<br>and after ACK Bit      | High-Speed Mode, $C_B \leq 100 \text{ pF}$ |      | 10                   | 80   |          |  |

|                     |                                                    | High-Speed Mode, $C_B \leq 400 \text{ pF}$ |      | 20                   | 160  | 1        |  |

## I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol           | Parameter                    | Conditions                                 | Min. | Тур.                 | Max. | Unit |  |

|------------------|------------------------------|--------------------------------------------|------|----------------------|------|------|--|

| t <sub>FDA</sub> | SDA Fall Time                | Standard Mode                              |      | 20+0.1C <sub>B</sub> |      | -    |  |

|                  |                              | Fast Mode                                  |      | 20+0.1C <sub>B</sub> |      |      |  |

|                  |                              | High-Speed Mode, $C_B \leq 100 \text{ pF}$ |      | 10                   | 80   | ns   |  |

|                  |                              | High-Speed Mode, $C_B \leq 400 \text{ pF}$ |      | 20                   | 160  |      |  |

| tsu;sto          | Stop Condition Setup Time    | Standard Mode                              |      | 4                    |      | μS   |  |

|                  |                              | Fast Mode                                  |      | 600                  |      | ns   |  |

|                  |                              | High-Speed Mode                            |      | 160                  |      | ns   |  |

| CB               | Capacitive Load for SDA, SCL |                                            |      |                      | 400  | pF   |  |

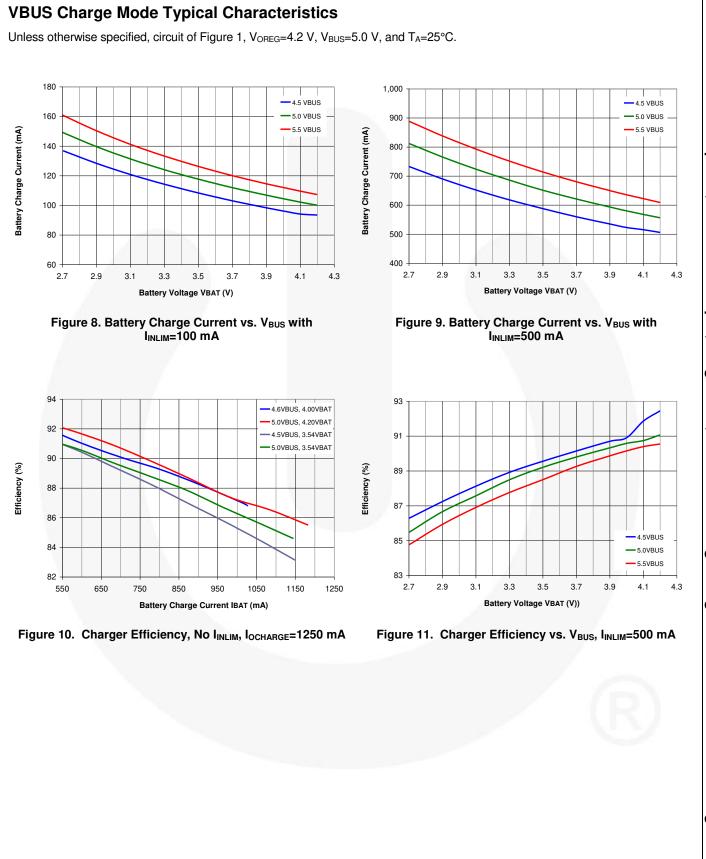

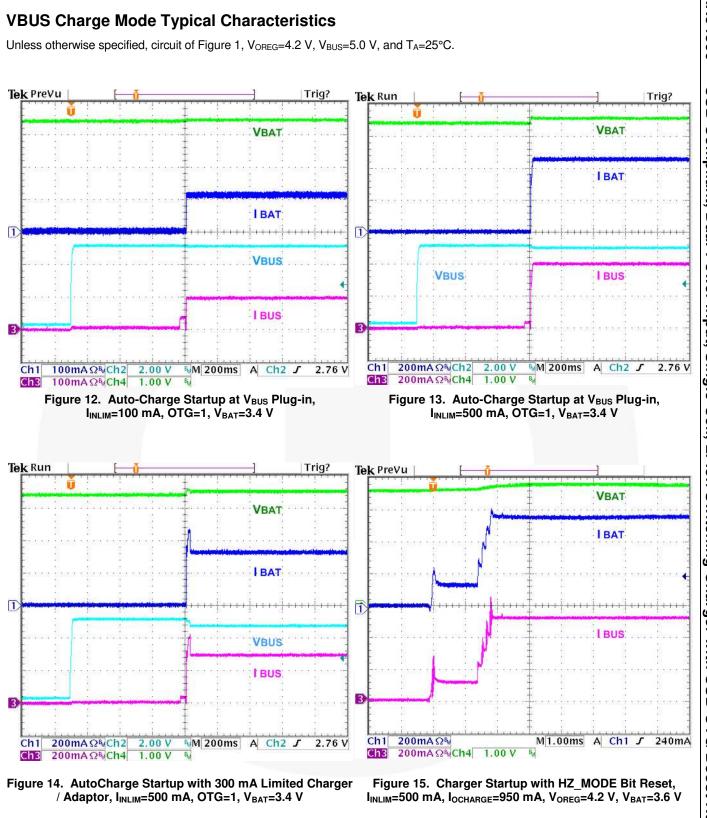

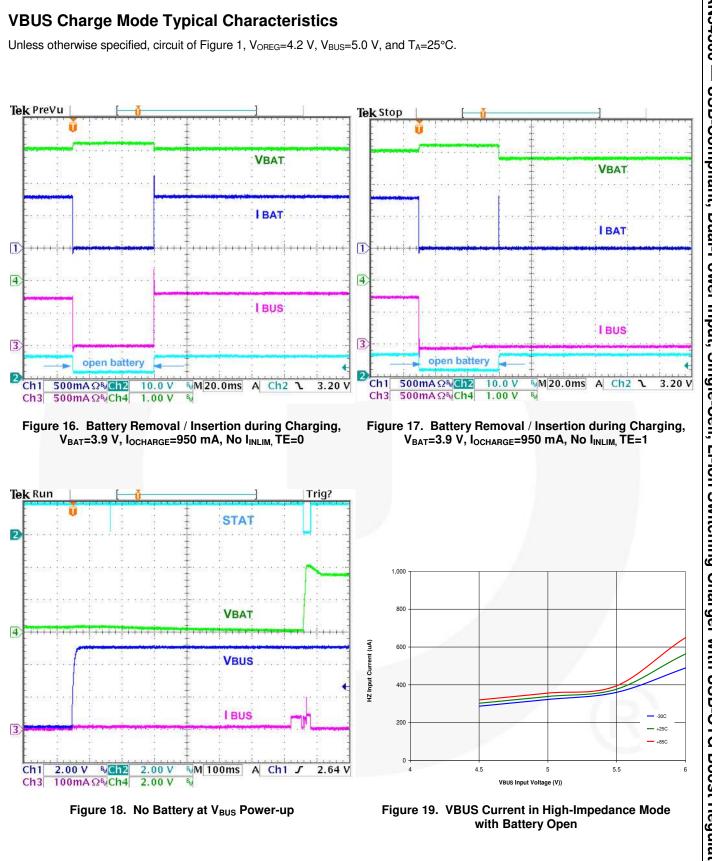

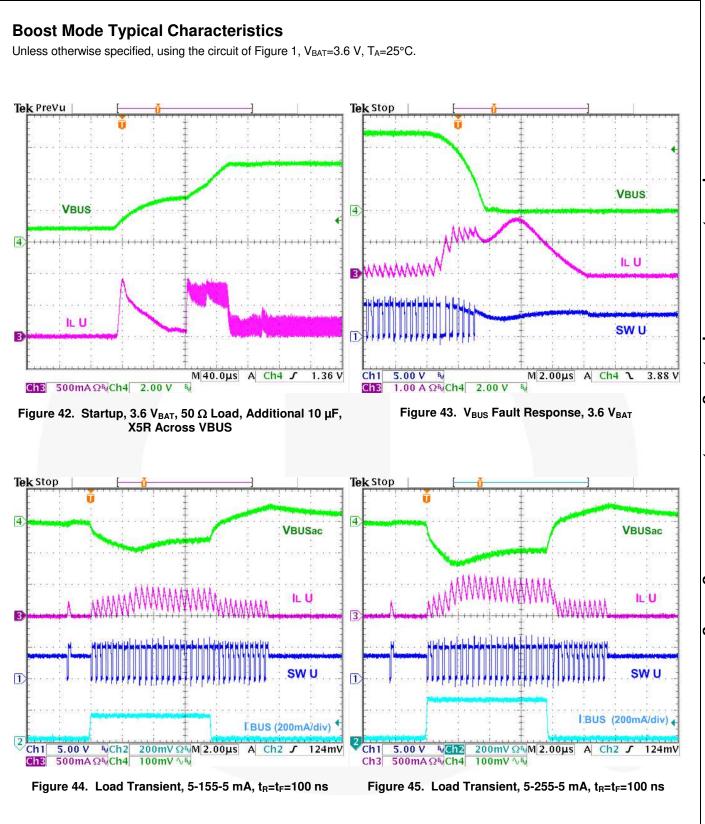

Unless otherwise specified, circuit of Figure 1,  $V_{OREG}$  = 4.2 V,  $V_{IN}$  = 5.0 V, and  $T_A$ =25°C.

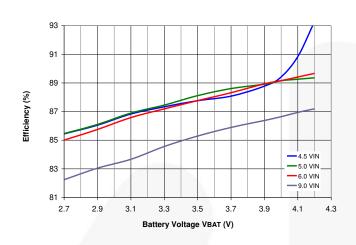

Figure 20. Charger Efficiency, Iocharge=950 mA

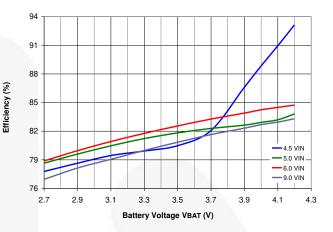

Figure 21. Charger Efficiency, Iocharge=1550 mA

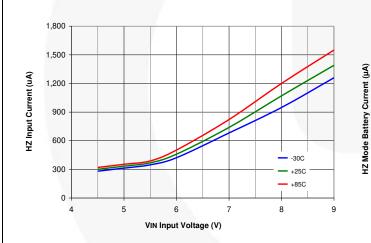

Figure 22. V<sub>IN</sub> Current in High-Impedance Mode, V<sub>BAT</sub>=3.6 V

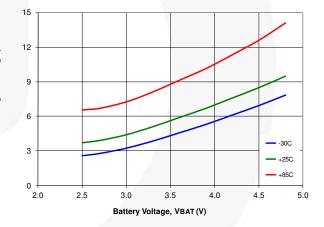

Figure 23. Battery Current in High-Impedance Mode, VBUS=Open, V<sub>IN</sub>=Open

FAN54300 ---

USB-Compliant, Dual-Power Input, Single-Cell, Li-Ion Switching Charger with USB-OTG Boost Regulator

## **Circuit Description / Overview**

When charging batteries with a current-limited input source, such as USB, a switching charger's high efficiency over a wide range of output voltages minimizes charging time.

The FAN54300 combines two highly integrated synchronous buck regulators for charging from two separate power sources. The IC also includes a synchronous boost regulator, which can supply 5 V to USB On-The-Go (OTG) peripherals. The regulator employs synchronous rectification for both the charger and boost regulators to maintain high efficiency over a wide range of battery voltages and charge states.

In addition to its USB (VBUS) input, the FAN54300 allows a second power source (VIN) to be used for charging. This input source is typically a "wall wart" and can be up to 9.5 V input.

The FAN54300 has three operating modes:

Charge Mode:

Charges a single-cell Li-lon or Li-polymer battery.

Boost Mode:

Provides 5 V power to USB-OTG with an integrated synchronous rectification boost regulator using the battery as input.

#### High-Impedance Mode:

Both the boost and charging circuits are off in this mode. Current flow from PWRIN (the charging power source) to the battery, or from the battery to PWRIN, are blocked in this mode. This mode consumes very little current from PWRIN or the battery.

When the IC is charging the battery from VIN, the boost regulator may be simultaneously enabled to supply 5 V for OTG peripherals.

#### **Charge Mode**

In Charge Mode, FAN54300 employs five regulation loops:

- 1. VBUS input current: Limits the amount of current drawn from VBUS. This current is sensed internally and can be programmed through the I<sup>2</sup>C interface

- Charging current: Limits the maximum charging current. This current is sensed using an external R<sub>SENSE</sub> resistor.

- 3. Charge voltage: The regulator is restricted from exceeding this voltage. As the internal battery voltage rises, the battery's internal impedance and R<sub>SENSE</sub> works in conjunction with the charge voltage regulation to decrease the amount of current flowing to the battery. Battery charging is completed when the voltage across R<sub>SENSE</sub> drops below the I<sub>TERM</sub> threshold.

- 4. Temperature: If the IC's junction temperature reaches 120°C, charge current is continuously reduced until the IC's temperature stabilizes at 120°C.

- An additional loop limits the amount of drop on VBUS or VIN to a programmable voltage (V<sub>SP</sub>) to accommodate current-limited wall chargers.

#### **Input Source Selection**

The FAN54300 selects the power source (PWRIN) for charging according to the following criteria.

Table 3. PWRIN: Charging Power Input Source Selection

| V <sub>IN</sub> | V <sub>BUS</sub> | PWRIN            |

|-----------------|------------------|------------------|

| VALID           | INVALID          | V <sub>IN</sub>  |

| INVALID         | VALID            | V <sub>BUS</sub> |

| VALID           | VALID            | V <sub>IN</sub>  |

If charging is in progress with V<sub>BUS</sub> and V<sub>IN</sub> becomes valid, charging from VBUS stops and charging continues from V<sub>IN</sub>. Charging stops if HZ\_VIN is set when V<sub>IN</sub> becomes valid while charging with V<sub>BUS</sub>.

If VIN and VBUS are both connected and  $t_{15MIN}$  expires, both CE# bits are set. To reinitiate  $t_{15MIN}$  charging (autocharge) with a weak battery, both power sources must be unplugged, then a valid power source plugged in. If only one of the two connected sources are removed then connected with a weak battery, both CE# bits remain set.

#### **Fault Reporting and Register Reset**

All faults that occur during charging or boost are reported only in the STATUS register (R0) associated with the active charging source at the time of the fault. Any register reset that occurs due to  $t_{32SEC}$  overflow resets only the associated with the active charging source.

For example: Assume the IC is charging in 32-Second Mode with V<sub>IN</sub> as a source. The processor stops setting TMR\_RST, so  $t_{32SEC}$  expires. The IC then resets only the \_V registers and goes into 15-Minute Mode charging with V<sub>IN</sub>. A timer fault is enunciated, but reported in the CONTROL0\_V register. CONTROL0\_U is unaffected by this event. When the  $t_{15MIN}$  timer expires, the IC sets the CE#\_V bit, but leaves the CE#\_U bit unchanged.

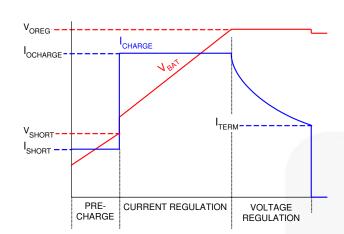

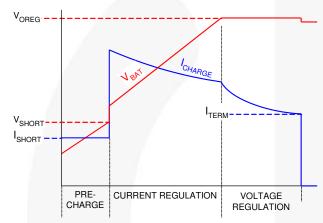

#### **Battery Charging Curve**

If the battery voltage is below  $V_{SHORT}$ , a linear current source "pre-charges" the battery until  $V_{BAT}$  reaches  $V_{SHORT}$ . The PWM charging circuits are then started and the battery is charged with a constant current if sufficient input power is available. The current slew rate is limited to prevent overshoot.

The FAN54300 is designed to work with a current-limited input source at PWRIN. During the current regulation phase of charging, PWRIN current limitations or the programmed charging current limit the amount of current available to charge the battery and power the system. The effect of input power limitations on  $I_{CHARGE}$  can be seen in Figure 47.

Figure 46. Charge Curve when PWRIN Limitations Don't Limit ICHARGE

#### Figure 47. Charge Curve when PWRIN Limits I<sub>CHARGE</sub>

PWRIN limitations are controlled either by:

- IBUSLIM: These bits set the maximum amount of current that the charger draws from VBUS; OR

- SP CHARGER: For power-limited chargers. the FAN54300 limits current draw when the charging source drops to the voltage programmed by the SP CHARGER bits. This allows "travel adapters" to be accommodated without host software overhead. The SP CHARGER control loop applies to both VIN and VBUS.

Assuming VOREG is programmed to the cell's fully charged "float" voltage, the current the battery accepts with the PWM regulator limiting its output (sensed at VBAT) to VOREG declines and the charger enters the voltage regulation phase of charging. When the current declines to the programmed ITERM value, the charge cycle is complete. Charge current termination can be disabled by resetting the TE bit.

#### **Charger Programmability**

Throughout this document, any parameter that ends in "U" applies when charging from V<sub>BUS</sub> and any parameter ending in "V" applies when charging from VIN. Parameters set with slave address D6 are applied when charging from V<sub>BUS</sub>. Parameters set with slave address D4 are applied when charging from VIN.

The following charging and input power control parameters can be programmed by the host through  $I^2C$ .

#### **Table 4. Programmable Charging Parameters**

| Parameter                          | Charging<br>Source | Name    | Register  |  |

|------------------------------------|--------------------|---------|-----------|--|

| Output Voltage<br>Regulation       | Either             | OREG    | REG2[7:2] |  |

| Battery Charging                   | V <sub>BUS</sub>   | ICHGU   | REG4[6:4] |  |

| Current Limit                      | V <sub>IN</sub>    | ICHGV   | REG4[6:3] |  |

| Input Current Limit                | V <sub>BUS</sub>   | IBUSLIM | REG1[7:6] |  |

| Charge<br>Termination Limit        | Either             | ITERM   | REG4[2:0] |  |

| Special Charger<br>Minimum Voltage | Either             | VSP     | REG5[2:0] |  |

The charger output or "float" voltage can be programmed by the OREG bits from 3.5 V to 4.44 V in 20 mV increments.

#### Table 5. OREG Bits (REG2 [7:2]) vs. Charger Vout (V<sub>OBEG</sub>) Float Voltage

| Decimal | Hex | VOREG | Decimal | Hex | VOREG |  |

|---------|-----|-------|---------|-----|-------|--|

| 0       | 00  | 3.50  | 32      | 20  | 4.14  |  |

| 1       | 01  | 3.52  | 33      | 21  | 4.16  |  |

| 2       | 02  | 3.54  | 34      | 22  | 4.18  |  |

| 3       | 03  | 3.56  | 35      | 23  | 4.20  |  |

| 4       | 04  | 3.58  | 36      | 24  | 4.22  |  |

| 5       | 05  | 3.60  | 37      | 25  | 4.24  |  |

| 6       | 06  | 3.62  | 38      | 26  | 4.26  |  |

| 7       | 07  | 3.64  | 39      | 27  | 4.28  |  |

| 8       | 08  | 3.66  | 40      | 28  | 4.30  |  |

| 9       | 09  | 3.68  | 41      | 29  | 4.32  |  |

| 10      | 0A  | 3.70  | 42      | 2A  | 4.34  |  |

| 11      | 0B  | 3.72  | 43      | 2B  | 4.36  |  |

| 12      | 0C  | 3.74  | 44      | 2C  | 4.38  |  |

| 13      | 0D  | 3.76  | 45      | 2D  | 4.40  |  |

| 14      | 0E  | 3.78  | 46      | 2E  | 4.42  |  |

| 15      | 0F  | 3.80  | 47      | 2F  | 4.44  |  |

| 16      | 10  | 3.82  | 48      | 30  | 4.44  |  |

| 17      | 11  | 3.84  | 49      | 31  | 4.44  |  |

| 18      | 12  | 3.86  | 50      | 32  | 4.44  |  |

| 19      | 13  | 3.88  | 51      | 33  | 4.44  |  |

| 20      | 14  | 3.90  | 52      | 34  | 4.44  |  |

| 21      | 15  | 3.92  | 53      | 35  | 4.44  |  |

| 22      | 16  | 3.94  | 54      | 36  | 4.44  |  |

| 23      | 17  | 3.96  | 55      | 37  | 4.44  |  |

| 24      | 18  | 3.98  | 56      | 38  | 4.44  |  |

| 25      | 19  | 4.00  | 57      | 39  | 4.44  |  |

| 26      | 1A  | 4.02  | 58      | ЗA  | 4.44  |  |

| 27      | 1B  | 4.04  | 59      | 3B  | 4.44  |  |

| 28      | 1C  | 4.06  | 60      | 3C  | 4.44  |  |

| 29      | 1D  | 4.08  | 61      | 3D  | 4.44  |  |

| 30      | 1E  | 4.10  | 62      | 3E  | 4.44  |  |

| 31      | 1F  | 4.12  | 63      | 3F  | 4.44  |  |

| Note:   |     |       |         |     |       |  |

#### Note:

6. All register default settings are noted by **bold typeface**.