# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

July 2013

# FAN7093 High-Current PN Half-Bridge Driver

#### **Features**

- Path Resistance for a Full-Bridge Configuration: Max. 30.5 mΩ at 150°C

- PWM Capability: > 60 kHz<sup>1</sup> Combined with Active Free Wheeling

- Switched-Mode Current Limitation for Reduced Power Dissipation In Over-Current Condition

- Current Limit Protection: Typ. 46 A

- Independent Current-Sense Output and Diagnostic Flag for High and Low Sides

- Over-Temperature Protection (OTP) with Latch

- Shorted-Load Protection with Latch Behavior

- Over-Voltage Protection (OVP) with Lockout

- Under-Voltage Protection (UVP)

- Logic Level Control Inputs

- Adjustable Slew Rates for Optimized EMI

- Typical Slew Rate of 1 V/µs with Open Slew Rate Pin

### Description

The FAN7093 is an integrated high-current half-bridge driver for electric motor drive applications. It contains one P-channel high-side MOSFET and one N-channel low-side MOSFET with an integrated control IC in one package. With the P-channel high-side switch, the need for a charge pump is eliminated, which minimizes EMI.

Pins IN and /INH are logic-level inputs and control the half-bridge output. The diagnostic and current sense IS pin outputs a current that is proportional to the current flowing through the half-bridge MOSFETs. The IS pin output represents current for the P-channel or the N-channel, depending on which is active.

The part is protected against a short to battery or ground of the out pin, over-current, over-temperature, over-voltage, and under-voltage conditions. The FAN7093 provides a cost- and space-optimized solution for protected high-current PWM motor drives.

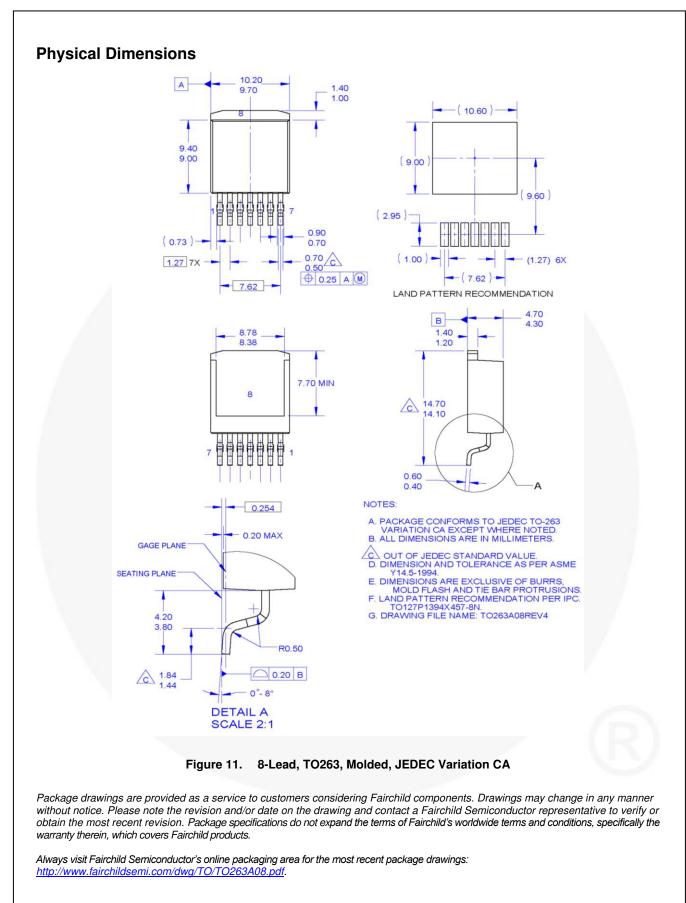

Figure 1. TO263-7L

$<sup>^1</sup>$  The *minimum* duty cycle is 34% when  $V_{\text{BATT}}{=}14$  V,  $R_{\text{SR}}$  is shorted, and the following parameters are at their typical values:  $t_{d(\text{ON})\text{HS}}, t_{slew(on)\text{HS}}, \text{ and } t_{slew(on)\text{LS}}.$

### **Ordering Information**

| Part Number  | Operating<br>Temperature Range | Package                                   | Packing<br>Method |

|--------------|--------------------------------|-------------------------------------------|-------------------|

| FAN7093_F085 | -40 to +150°C                  | 8-Lead, TO263, Molded, JEDEC Variation CA | Tape & Reel       |

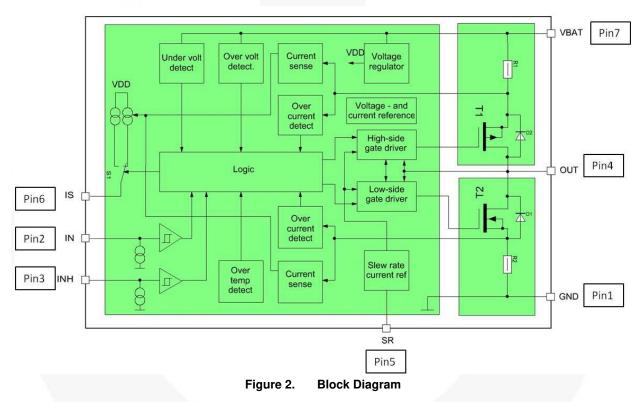

# **Block Diagram**

The FAN7093 is a high-current half-bridge that contains three separate chips in one package: one P-channel high-side MOSFET, one N-channel low-side MOSFET, and with a control IC. All three chips are mounted on one common lead frame, using chip-on-chip and chipby-chip technologies. The power MOSFETs are vertical MOS transistors to ensure minimum on-state resistance.

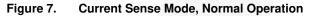

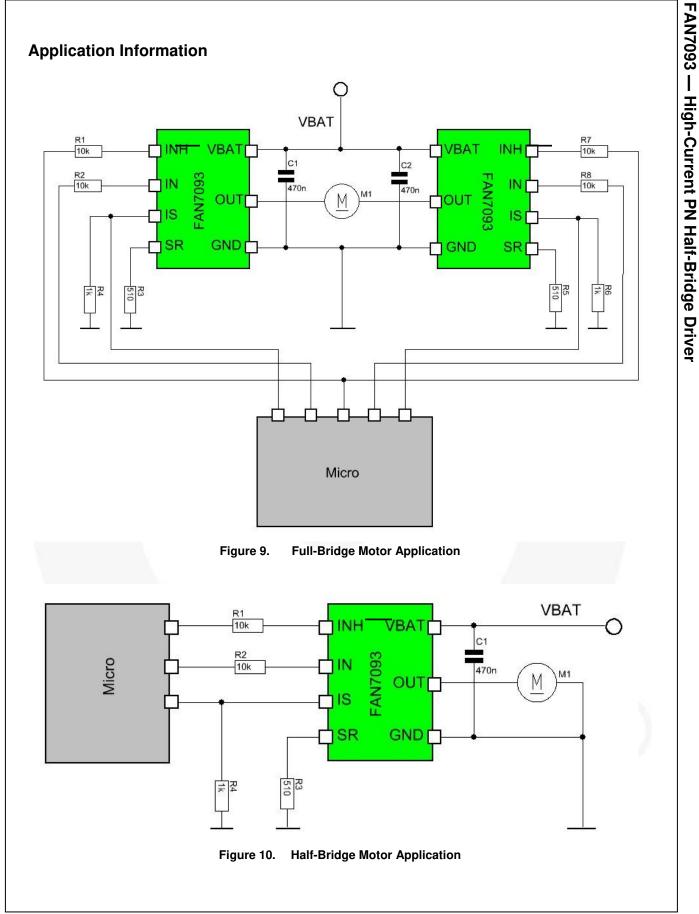

Using a P-channel high-side switch eliminates a charge pump and reduces EMI. A microcontroller is able to control the logic level inputs of IN and /INH of the halfbridge. The diagnostic pin IS is a current output stage that delivers a proportional current through the Pchannel and N-channel MOSFETS, depending on which is being activated, with the IN or /INH pin forcing conditions. In case of a short to VBATT or ground, the IS pin acts as an error flag. The error flag can be detected as a logic HIGH level through an attached microcontroller. In an over-current situation, the control IC turns off the MOSFETs and tries to turn them back on after a cool down time of 140 µs (typical). The control IC protects the MOSFETs against over-voltage, under-voltage, and over-temperature conditions. The dead time, to prevent shoot-through between the P- and N-channel MOSFET, is also generated by the control IC. The slew rate of the outputs can be adjusted through an external resistor connected to the SR pin. The FAN7093 can be combined with another FAN7093 to form a full-bridge drive. Multiple FAN7093 can be combined in full-or half-bridge three-phase drive configurations.

# **Pin Configuration**

Figure 3. **Pin Assignments**

# **Pin Definitions**

| Pin  | Symbol                           | I/O | Function                                                                                                                            |  |  |

|------|----------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | GND <sup>(1)</sup>               |     | Ground                                                                                                                              |  |  |

| 2    | IN                               | Ι   | Input. Defines whether the high-side (HS) or low-side (LS) switch is activated.                                                     |  |  |

| 3    | /INH                             | I.  | hibit. When set to LOW, the device enters Sleep Mode and resets Over-<br>emperature Protection (OTP) and the HS and LS short latch. |  |  |

| 4, 8 | OUT <sup>(1)</sup>               | 0   | Power output of the bridge                                                                                                          |  |  |

| 5    | SR                               | 1   | Slew rate. The slew rate of the power switches can be adjusted by connecting a resistor between the SR and GND pins.                |  |  |

| 6    | IS                               | 0   | Current sense and diagnostics                                                                                                       |  |  |

| 7    | V <sub>BATT</sub> <sup>(1)</sup> |     | Supply                                                                                                                              |  |  |

Note:

1. This pin needs power wiring.

#### Table 1. Truth Table

| Device State                                       | /INH | IN   | HS  | LS  | IS   | Mode                                                                                                        |

|----------------------------------------------------|------|------|-----|-----|------|-------------------------------------------------------------------------------------------------------------|

|                                                    | LOW  | Х    | OFF | OFF | LOW  | Standby Mode                                                                                                |

| Normal Operation                                   | HIGH | LOW  | OFF | ON  | CS   | LS Active                                                                                                   |

|                                                    | HIGH | HIGH | ON  | OFF | CS   | HS Active                                                                                                   |

| Over-Voltage<br>I <sub>OUT</sub> ≤ I <sub>CP</sub> | Х    | х    | ON  | OFF | HIGH | Shutdown of LS, HS Activated, Error Detected                                                                |

| Over-Voltage<br>I <sub>OUT</sub> > I <sub>CP</sub> | х    | х    | OFF | OFF | HIGH | Shutdown of LS, HS Error Detected<br>Reset with /INH HIGH to LOW to HIGH when<br>condition no longer exists |

| Under-Voltage                                      | Х    | Х    | OFF | OFF | LOW  | UV Lockout                                                                                                  |

| Over-Temperature or<br>Shorted LS or HS            | LOW  | х    | OFF | OFF | LOW  | Standby Mode, Reset of Latch                                                                                |

| Over-Temperature<br>or Shorted LS or HS            | HIGH | х    | OFF | OFF | HIGH | Shutdown with Latch, Error Detected                                                                         |

| Current Limit                                      | HIGH | HIGH | OFF | ON  | HIGH | Switched Mode, Error Detected <sup>(2)</sup>                                                                |

|                                                    | HIGH | LOW  | ON  | OFF | HIGH | Switched Mode, Error Detected <sup>(2)</sup>                                                                |

#### Notes:

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_J = -40$ °C to +150°C; all voltages with respect to ground, and positive current flowing into pin (unless otherwise specified).

| Symbol                                     | Parameter                                       | Condition                                 | Min. | Тур.   | Max. | Unit |

|--------------------------------------------|-------------------------------------------------|-------------------------------------------|------|--------|------|------|

| $V_{BATT}$                                 | Supply Voltage <sup>(4)</sup>                   |                                           | -0.3 |        | 45   | V    |

| $V_{\rm IN}$ / $V_{\rm INH}$               | Logic Input Voltage <sup>(4)</sup>              |                                           | -0.3 |        | 45   | V    |

| $V_{SR}$                                   | Voltage at SR Pin <sup>(4)</sup>                |                                           | -0.3 |        | 1.5  | V    |

| VIS                                        | Voltage at IS Pin <sup>(4)</sup>                |                                           | -0.3 |        | 7.5  | V    |

| I <sub>D(HS)</sub> ,<br>I <sub>D(LS)</sub> | HS/LS Continuous Drain Current <sup>(4,5)</sup> | T <sub>C</sub> < 85°C                     | 1    | -46/46 |      | А    |

| $I_{D(HS),} \\ I_{D(LS)}$                  | HS/LS Pulsed Drain Current <sup>(4,5)</sup>     | $T_{C}$ < 85°C Single Pulse < 5 $\mu$ s   |      | -90/90 |      | А    |

| I <sub>D(HS),</sub><br>I <sub>D(LS)</sub>  | HS/LS PWM Current <sup>(4,5)</sup>              | T <sub>C</sub> < 125°C f=1 kHz,<br>DC=50% |      | -55/55 |      | А    |

| Temperat                                   | ures                                            |                                           |      |        |      |      |

| TJ                                         | Junction Temperature <sup>(4)</sup>             |                                           | -40  |        | 150  | °C   |

| T <sub>STG</sub>                           | Storage Temperature <sup>(4)</sup>              |                                           | -55  |        | 150  | °C   |

| Electrosta                                 | atic Discharge Capability (ESD)                 |                                           | ·    |        |      |      |

| FOD                                        | Liveran Dady Madel JECD00 4114 <sup>(6)</sup>   | IN, /INH, SR, IS                          | -2   |        | 2    | IM   |

| ESD                                        | Human Body Model, JESD22-A114 <sup>(6)</sup>    | OUT, GND, VBATT                           | -6   |        | 6    | kV   |

Notes:

4. Not subject to production testing, specified by design.

5. Maximum reachable current may be smaller, depending on current-limit level.

6. ESD susceptibility, HBM according to AEC\_Q100-0042 / JESD22-A114-B (1.5 kΩ, 100 pF).

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                        | Parameter                                                                                                                  | Condition                                                   | Min. | Тур. | Max. | Unit |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| $V_{\text{BATT}(\text{NOM})}$ | Supply Voltage Range for Nominal Operation                                                                                 |                                                             | 7    |      | 18   | V    |

| $V_{\text{BATT}(\text{EXT})}$ | Supply Voltage Range for Extended Operation                                                                                | Parameter<br>Deviations Possible                            | 5.5  |      | 28.0 | V    |

| TJ                            | Junction Temperature                                                                                                       |                                                             | -40  |      | 150  | °C   |

| $\Theta_{JC(LS)}$             | Thermal Resistance, Junction-Case, Low-Side Switch $\Theta_{JC(LS)}=\Delta T_J (LS) / P_V (LS)^{(7)}$                      |                                                             |      | 0.8  | 7    | °C/W |

| $\Theta_{JC(\text{HS})}$      | Thermal Resistance, Junction-Case, High-Side Switch $\Theta_{JC(HS)}=\Delta T_J$ (HS) / P <sub>V</sub> (HS) <sup>(7)</sup> |                                                             |      | 0.45 |      | °C/W |

| Θ <sub>JA</sub>               | Thermal Resistance, Junction-Ambient <sup>(7)</sup>                                                                        | Using Pad Area of<br>One Square Inch of<br>Two-Ounce Copper |      | 40   |      | °C/W |

#### Note:

7. Not subject to production test; specified by design.

# **Electrical Characteristics**

Unless otherwise specified,  $V_{BATT} = 7 V$  to 18 V,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ ,  $I_L = 0 A$ , all voltages with respect to ground, and positive current flowing into pin.

| Symbol                  | Parameter         | Condition                                                                         | Min. | Тур. | Max. | Unit |

|-------------------------|-------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| IV <sub>BATT(ON)</sub>  | Supply Current    | $V_{INH}$ =5 V, $V_{IN}$ =5 V, $R_{SR}$ =0 $\Omega$ , DC-Mode, No Fault Condition |      |      | 5.0  | mA   |

| IV <sub>BATT(OFF)</sub> | Quiescent Current | V <sub>INH</sub> =0 V, V <sub>IN</sub> =0 V                                       |      |      | 450  | μA   |

# **Power Stage Characteristics**

The power stages of the FAN7093 consist of a P-channel vertical DMOS transistor for the high-side switch and an N-channel vertical DMOS transistor for the low-side switch. All protection and diagnostic functions are located in the control die. Both switches can be operated up to 60 kHz<sup>2</sup>, allowing active freewheeling and minimizing power dissipation in the forward operation of the integrated diodes.

The on-state resistance, R<sub>DS(ON)</sub>, is dependent on the supply voltage V<sub>BATT</sub> as well as on the junction temperature, T<sub>J</sub>.

#### Power Stages — Static Characteristics

Unless otherwise specified,  $V_{BATT}=7$  V to 18 V,  $T_{J}=-40^{\circ}$ C to +150°C, all voltages with respect to ground, and positive current flowing into pin.

| Symbol                       | Parameter                                    | Condition M                                                    | /lin. Typ. | Max. | Unit |

|------------------------------|----------------------------------------------|----------------------------------------------------------------|------------|------|------|

| High-Side S                  | witch                                        |                                                                |            |      |      |

| R <sub>DS(ON)_HS</sub>       | On-State High-Side Resistance                | $I_{OUT}$ =-20 A; $V_{BATT}$ =14 V <sup>(8)</sup>              |            | 12.3 | mΩ   |

| I <sub>LEAK(HS)</sub>        | Leakage Current                              | V <sub>INH</sub> =0 V, V <sub>OUT</sub> =0 V                   |            | 50   | μA   |

| V <sub>RDF</sub>             | Reverse Diode Forward-Voltage <sup>(9)</sup> | I <sub>OUT</sub> =-9 A                                         |            | 1.5  | V    |

| Low-Side S                   | witch                                        |                                                                |            |      |      |

| R <sub>DS(ON)_LS</sub>       | On-State Low-Side Resistance                 | I <sub>OUT</sub> =20 A; V <sub>BATT</sub> =14 V <sup>(8)</sup> |            | 18.2 | mΩ   |

| $I_{\text{Leak}(\text{LS})}$ | Leakage Current                              | V <sub>INH</sub> =0 V, V <sub>OUT</sub> =V <sub>BATT</sub>     | 6          | 10   | μA   |

|                              | Reverse Diode Forward-Voltage <sup>(9)</sup> | I <sub>OUT</sub> =9 A                                          | 1.         | -1.5 | V    |

Notes:

Specified R<sub>DS(ON)</sub> value is related to normal soldering points; R<sub>DS(ON)</sub> values are specified for FAN7093\_F085: pin 1,7 to pin 8 (tab, backside).

9. Due to active freewheeling, the diode is conducting only for a few  $\mu$ s, depending on the value of the external R<sub>SR</sub> resistor.

$<sup>^2</sup>$  The minimum duty cycle is 34% when  $V_{\text{BATT}}$ =14 V,  $R_{\text{SR}}$  is shorted and the following parameters are at their typical values:  $t_{d(\text{ON})\text{LS}}, t_{\text{Slew(on)}\text{HS}}$ , and  $t_{\text{Slew(on)}\text{LS}}$ .

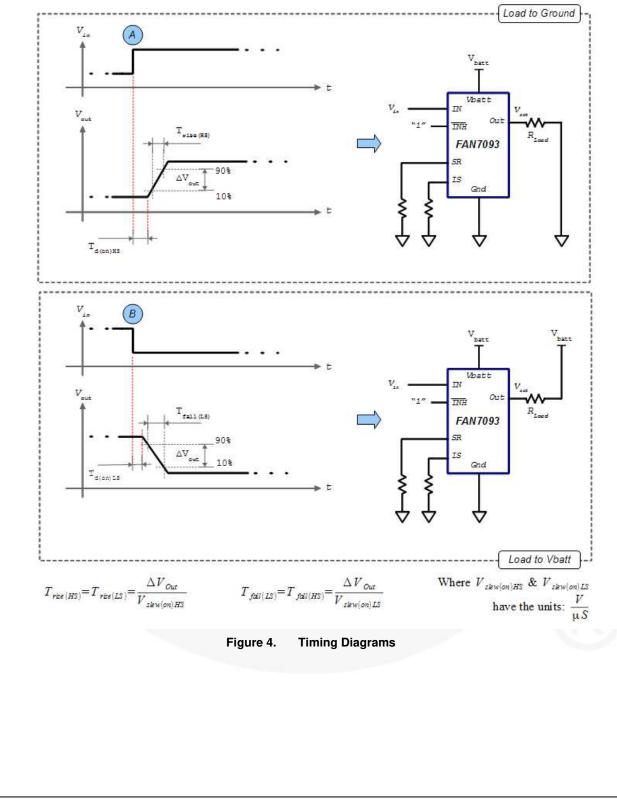

# **Switching Times**

Due to the timing differences for the rising and the falling edges, there is a slight difference between the length of the input pulse and the length of the output pulse, as shown in Figure 4.

### Power Stages - Dynamic Characteristics

Unless otherwise specified;  $V_{BATT}=7 V - 14 V$ ,  $T_{J}=-40^{\circ}C$  to  $+150^{\circ}C$ ,  $R_{L}=2 \Omega$ , /INH HIGH, all voltages with respect to ground, and positive current flowing into pin.

| Symbol                  | Parameter                 | Condition                                                                               | Min. | Тур. | Max. | Unit |  |

|-------------------------|---------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|--|

| High-Side Swi           | itch Dynamic Characte     | ristics                                                                                 |      |      |      |      |  |

|                         |                           | R <sub>SR</sub> =0Ω                                                                     | 15   | 19   | 24   |      |  |

| N                       | Slew Rate <sup>(10)</sup> | R <sub>SR</sub> =5.1 kΩ                                                                 | 12   | 15   | 17   |      |  |

| V <sub>Slew(ON)HS</sub> | Siew Rale                 | R <sub>SR</sub> =51 kΩ                                                                  | 5    | 6    | 7    | V/µs |  |

|                         |                           | R <sub>SR</sub> =Open, R <sub>L</sub> to GND                                            | 0.8  | 1.0  | 1.2  |      |  |

| t <sub>d(ON)</sub> HS   | Turn-On Delay             | /INH High; IN LOW to HIGH;<br>OUT with RL to GND (see Figure<br>4 top)                  | 0.45 | 2.10 | 4.20 | μs   |  |

| Low-Side Swit           | tch Dynamic Character     | ristics                                                                                 |      |      |      |      |  |

|                         |                           | $R_{SR}=0\Omega$                                                                        | 18   | 21   | 24   |      |  |

| V                       | Slew Rate <sup>(10)</sup> | R <sub>SR</sub> =5.1 kΩ                                                                 | 13   | 17   | 19   |      |  |

| V <sub>Slew(ON)LS</sub> | Siew Rale                 | R <sub>SR</sub> =51 kΩ                                                                  | 5    | 7    | 7    | V/µs |  |

|                         |                           | R <sub>SR</sub> =Open, R <sub>L</sub> to VBATT                                          | 0.8  | 1.2  | 1.2  |      |  |

| t <sub>d(ON)LS</sub>    | Turn-On Delay             | /INH HIGH; IN HIGH to LOW;<br>OUT with RL to V <sub>BATT</sub> (see<br>Figure 4 bottom) | 0.45 | 2.10 | 4.20 | μs   |  |

Note:

10. Not production tested.

### **Protection Functions**

The device provides several integrated protection functions designed to prevent IC damage in fault conditions. Fault conditions are considered as "outside" the normal operating range. Protection functions are not for continuous or repetitive operation, with the exception of current-limit protection. In a fault condition, the FAN7093 applies the highest slew rate possible, independent of the connected slew rate resistor ( $R_{SR}$ ). Over-voltage, over-temperature, and over-current situations are indicated by a fault current flag  $I_{IS(LIM)}$  at the IS pin. The following describes the protection functions in order of priority. Over-voltage protection overrides all other protections.

#### **Over-Voltage Protection (OVP)**

To ensure a high immunity against over-voltage conditions like load dump, the device turns off the low-side MOSFET and turns on the high-side MOSFET when the supply voltage exceeds the over-voltage protection level  $V_{OV(OFF)}$ . The control IC returns to normal operation  $t_{lock}$ =140  $\mu$ s (Typ.) after the supply voltage decreases below the over-voltage lockout level,  $V_{OV(ON)}$ . In H-bridge configurations, this behavior leads to freewheeling in the high side during over-voltage lockout, the IC turns off the high-side driver and latches this state. See Table 1, which shows the condition of the IS pin flag. This state can be reset (if the conditions no longer exist) when /INH goes from HIGH to LOW to HIGH again.

#### **Under-Voltage Protection (UVP)**

To avoid uncontrolled motion; for example, a driven motor at low voltages; the control IC turns off all MOSFETS when the supply voltage drops below the turn-off voltage,  $V_{UV(OFF)}$ . The control IC resumes to normal operation when the supply voltage rises above the turn-on voltage  $V_{UV(ON)}$ . Notice that the IS pin does NOT flag this fault condition.

#### **Over-Temperature Protection (OTP)**

The FAN7093 is protected against over-temperature by an integrated temperature sensor in the control IC. Over-temperature protection turns off both output stages. This state is latched until the device is reset by a LOW signal with a minimum pulse length of  $t_{reset}$  at the /INH pin, assuming the control IC temperature decreased by at least the thermal hysteresis. Repetitive use of the over-temperature protection decreases product life.

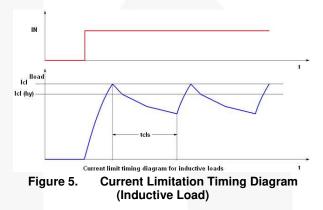

#### **Current Limitation**

The current is measured in both MOSFETS. As soon as the current reaches the limit  $I_{CL}$ , the low-side or highside MOSFET is deactivated and the other MOSFET activated for  $t_{CLS}$ . During that time, changes at the IN pin are ignored. The /INH pin can still be used to turn off both MOSFETs. After  $t_{CLS}$ , the MOSFETS return to their initial setting. The error signal at the IS pin is reset after 2 x  $t_{CLS}$ . Unintentional triggering of the current-limit circuitry through short current spikes (e.g. inflicted by EMI coming from a motor) is suppressed by an internal filter. Reaction delay of the filter circuitry affects the current limit level  $I_{CL}$ , depending on slew rate of the load current dI/dt.

In combination with a typical inductive load, such as a motor, this results in a switched-mode current limitation. This method of limiting current has the advantage of greatly reduced power dissipation compared to driving the MOSFET in linear mode. Therefore, it is possible to use the current limitation for a short time without exceeding the maximum allowed junction temperature (e.g. for limiting the inrush current during motor startup). However, regular use of the current limitation is only allowed as long as the specified maximum junction temperature is not exceeded. Exceeding this temperature reduces the life of the device.

#### **Short-Circuit Protection (SCP)**

The device is short-circuit protected against:

- Output Shorted to Ground

- Output Shorted to Battery Voltage

- Short-Circuit between the Load Connections

The short-circuit protection is a combination of current limit and over-temperature shutdown of the device.

# **Electrical Characteristics - Protection Functions**

Unless otherwise specified;  $V_{BATT}=7$  V to 18 V,  $T_{J}=-40^{\circ}C$  to  $+150^{\circ}C$ , all voltages with respect to ground, and positive current flowing into pin.

| 0                           | Demonster                                                                | O a se all'il a se           | Liı  | s    |      |      |

|-----------------------------|--------------------------------------------------------------------------|------------------------------|------|------|------|------|

| Symbol                      | Parameter                                                                | Condition                    | Min. | Тур. | Max. | Unit |

| Under-Voltage               | e Shutdown                                                               |                              |      |      |      | I    |

| V <sub>UV(ON)</sub>         | Turn-Off Voltage                                                         | VBATT Increasing             |      |      | 5.6  | V    |

| $V_{\text{UV}(\text{OFF})}$ | Turn-On Voltage                                                          | V <sub>BATT</sub> Decreasing | 4.9  |      |      | V    |

| $V_{UV(HY)}$                | Hysteresis                                                               |                              |      | 0.15 |      | V    |

| Over-Voltage                | Lockout                                                                  |                              |      |      |      |      |

| V <sub>OV(ON)</sub>         | Turn-Off Voltage                                                         | V <sub>BATT</sub> Decreasing | 28   |      |      | V    |

| $V_{\text{OV}(\text{OFF})}$ | Turn-On Voltage                                                          | V <sub>BATT</sub> Increasing | 27   |      | 35   | V    |

| V <sub>OV(HY)</sub>         | Hysteresis                                                               |                              |      | 1.0  |      | V    |

| t <sub>lock</sub>           | Lockout Time                                                             |                              |      | 140  |      | μs   |

| Current Limita              | ation                                                                    |                              |      |      |      |      |

| I <sub>CL</sub>             | Current Limit Detection Level High-<br>and Low-Side                      |                              | 39   | 50   | 61   | А    |

| I <sub>CP</sub>             | Peak Current Limit Detection Level<br>High- and Low-Side <sup>(11)</sup> |                              | 72   | 88   | 105  | A    |

| Current Limita              | ation Timing                                                             |                              |      |      |      |      |

| t <sub>CLS</sub>            | Shut-Off Time for HS and LS                                              |                              | 100  | 150  | 200  | μs   |

| Thermal Shute               | down                                                                     |                              |      |      |      |      |

| T <sub>SD(SENSE)</sub>      | Turn-Off Temperature Sense                                               |                              | 170  |      | 190  | °C   |

| T <sub>SD(SENSE)</sub>      | Turn-On Temperature Sense                                                |                              | 150  |      | 170  | °C   |

| T <sub>SD(HYS)</sub>        | Thermal Hysteresis                                                       |                              |      | 15   |      | K    |

| t <sub>reset</sub>          | Reset Pulse at /INH Pin (/INH LOW)                                       |                              | 4    |      |      | μs   |

Note:

11. Not production tested; specified by design.

### **Control and Diagnostics**

#### **Input Circuit**

The internal gate drivers for the MOSFETS are controlled through inputs IN and /INH and are TTL / CMOS-compatible Schmitt triggers with hysteresis. Setting the /INH pin to HIGH enables the device. In this condition, one of the two power MOSFETS turn on, depending on the input level of the IN pin. To deactivate both switches, the /INH pin must be set LOW. No external driver is needed. The FAN7093 can interface directly with a microcontroller as long as the maximum ratings are not exceeded.

#### **Dead-Time Generation**

The dead time is generated on the control IC to prevent shoot-through between the power MOSFETS. The dead-time is independent of the selected slew rate to reach a high PWM frequency of 60 kHz.

#### **Adjustable Slew Rate**

To optimize electromagnetic emission (EMI), the switching speed of the MOSFETs is adjustable by an external resistor. The slew rate pin, SR, allows designers to optimize the balance between emission and power dissipation within the application by connecting an external resistor  $R_{SR}$  to GND. If the SR pin is open by design or if intermittent disconnect occurs, the slew rate is set to the value shown in the Power Stages - Dynamic Characteristics table.

# Status Flag Diagnostic with Current-Sense Capability

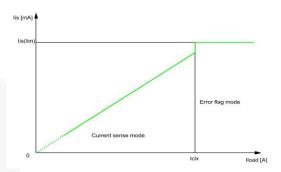

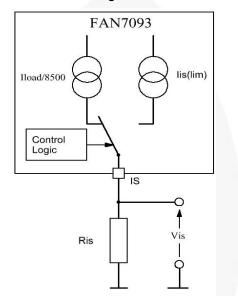

The status pin, IS, is used as a combined current sense and error flag output. In normal operation (Current-Sense Mode), a current source in the control IC is connected to the status pin, which delivers a current proportional to the forward load current flowing through the active high-side or low-side MOSFET. Current flow in the reverse direction cannot be detected except for a marginal leakage current I<sub>IS(LK)</sub>. External resistor R<sub>IS</sub> determines the voltage per output current. The current-sense ratio value is shown in the Electrical Characteristics - Control and Diagnostics table. In case of a fault condition, the status output is connected to a current source independent of the load current and provides IIS(lim). The maximum voltage at the IS pin is determined by the choice of the external resistor and the supply voltage. When in a current-limit condition, I<sub>IS(lim)</sub>, is active for a time 2 x t<sub>CLS</sub>; the flag indicates the error for time t<sub>CL</sub> after the condition no longer exists, but constantly stays active as long as the current-limit condition exists.

Figure 6. Sense Current vs. Load Current and Flag Current

Figure 8. Error Flag Mode, Fault Condition

# **Electrical Characteristics - Control and Diagnostics**

Unless otherwise specified,  $V_{BATT}=7V$  to 18V,  $T_{J}=-40$  °C to +150 °C, all voltages with respect to ground, positive current flowing into pin.

| Symbol                 | Parameter                                                                            | Condition                                                                                | Min. | Тур. | Max. | Unit            |

|------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|-----------------|

| V <sub>INXL</sub>      | Low Level Voltage, /INH, IN                                                          |                                                                                          | 1.5  |      |      | V               |

| V <sub>INXH</sub>      | High Level Voltage, /INH, IN                                                         |                                                                                          |      |      | 3.5  | V               |

| V <sub>INXH(HYS)</sub> | Input Voltage Hysteresis                                                             |                                                                                          | 500  |      |      | mV              |

| I <sub>INXH</sub>      | Input Current High Level                                                             | V <sub>INH</sub> =V <sub>IN</sub> =0.4 V to 5.3 V                                        | 20   |      | 80   | μA              |

|                        |                                                                                      | R <sub>IS</sub> =800 Ω                                                                   | 4.5  | 8.5  | 13.5 |                 |

| KILIS                  | Current Sense Ratio in Static on-<br>Condition KILIS=I <sub>1</sub> /I <sub>1S</sub> | I <sub>L</sub> =8 A to 50 A                                                              |      |      |      | 10 <sup>3</sup> |

|                        |                                                                                      | I <sub>L</sub> =1.1 A to 8 A                                                             | 3.5  |      |      |                 |

| I <sub>IS(LIM)</sub>   | Maximum Analog Sense Current                                                         | R <sub>IS</sub> =800 Ω                                                                   | 4.5  |      | 5.5  | mA              |

| I <sub>IS(FAULT)</sub> | Sense Current in Fault Condition <sup>(12)</sup>                                     | R <sub>IS</sub> =800 Ω                                                                   | 5.5  |      | 7.0  | mA              |

| VIS(FAULT)             | Maximum IS Output Voltage                                                            | R <sub>IS</sub> ≥ 3 kΩ                                                                   |      |      | 7.5  | V               |

| IISLEAK                | I <sub>SENSE</sub> Leakage Current                                                   | /INH HIGH, IN=X, IL=0 A                                                                  |      |      | 300  | μA              |

| tset                   | Settling time <sup>(12,13)</sup>                                                     | Resistive Load,<br>V <sub>BATT</sub> =14 V, I <sub>L</sub> =3 A, /INH<br>HIGH, SR to GND |      |      | 4    | μs              |

#### Notes:

12. Not subject to production test; specified by design.

The settling time is from when IN transitions 0 to 1 (the low-side goes OFF and the high-side goes ON) and 1 to 0 (the high-side goes OFF and the low-side goes ON) to when V<sub>(IS)</sub> reaches 90% of its final value.

LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                          |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make<br>changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |

Rev. 164