Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

February 2008

# FMS6403 Triple Video Drivers with Selectable HD/PS/SD Bypass Filters for RGB and YPbPr Signals

### **Features**

- Three Video Anti-aliasing or Reconstruction Filters

- 2:1 MUX Inputs for YPbPr and RGB Inputs

- Supports D1, D2, D3, and D4 Video D-connector (EIAJ CP-4120)

- Selectable 8MHz/15MHz/30MHz 6th-order Filters, Plus Bypass

- Works with SD (480i), Progressive (480p), and HD (1080i/ 720p)

- AC-coupled Inputs Include DC Restore / Bias Circuitry

- All Outputs Can Drive AC- or DC-Coupled

75Ω Loads and Provide Either 0dB or 6dB of Gain

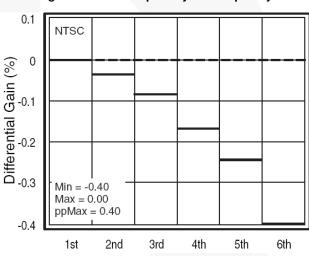

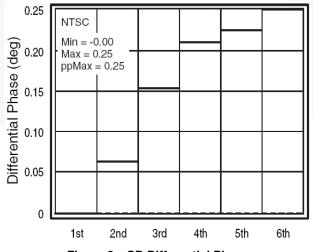

- 0.40% Differential Gain, 0.25° Differential Phase

- TSSOP-20 Packaging

# **Applications**

- Progressive Scan

- Cable Set-top Boxes

- Home Theaters

- Satellite Set-top Boxes

- DVD Players

- HDTV

- Personal Video Recorders (PVR)

- Video On Demand (VOD)

# Description

The FMS6403 offers comprehensive filtering for TV, set-top box, or DVD applications. This part consists of a triple, sixth-order filter with selectable 30MHz, 15MHz, or 8MHz cutoff frequency. The filters may also be bypassed so that the bandwidth is limited only by the output amplifiers.

A 2:1 multiplexer is provided on each filter channel. The triple filters are intended for YPbPr and RGB signals. The DC clamp levels are set according to the RGB\_SEL control input. YPbPr sync tips are clamped to 250mV, 1.125V, and 1.125V, respectively; while RGB sync tips are all clamped to 250mV. Sync clamp timing can be derived from the Y/G inputs or from the external SYNC\_IN pin. The 8MHz and 15MHz filter settings support bi-level sync, while the 30MHz filter setting and bypass mode support tri-level sync.

All channels nominally accept AC-coupled 1V<sub>PP</sub> signals. Selectable 0dB or 6dB gain allows the outputs to drive 1V<sub>PP</sub> or 2V<sub>PP</sub> signals into AC- or DC-coupled terminated loads with a 1V<sub>PP</sub> input. Input signals cannot exceed  $1.5V_{PP}$  and outputs cannot exceed  $2.5V_{PP}$ .

# **Ordering Information**

| Part Number             | Operating<br>Temperature<br>Range | Package                                            | Packing Method             |

|-------------------------|-----------------------------------|----------------------------------------------------|----------------------------|

| FSM6403MTC              | 0 to 70°C                         | 20-Lead, Thin Shrink Small Outline Package (TSSOP) | 94 Units in Tubes          |

| FSM6403MTC20X 0 to 70°C |                                   | 20-Lead, Thin Shrink Small Outline Package (TSSOP) | 2500 Unit Tape and<br>Reel |

All packages are lead free per JEDEC: J-STD-020B standard.

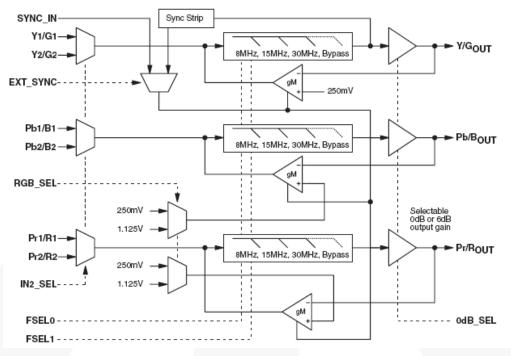

# **Functional Block Diagram**

Figure 1. Block Diagram

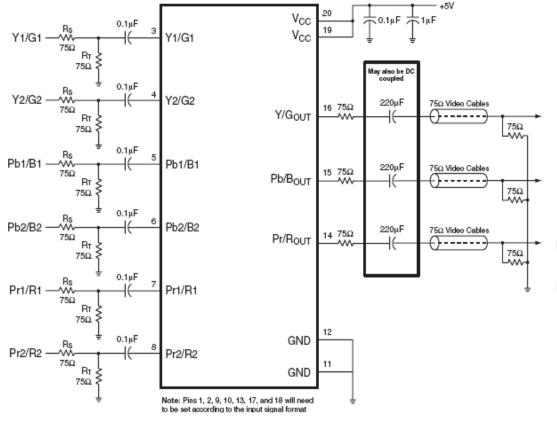

# **Typical Application**

Figure 2. Typical Application Circuit

# **Pin Configuration**

Figure 3. Pin Configuration

### **Pin Definitions**

| Pin# | Name                | Туре   | Description                                                                                                           |  |  |  |

|------|---------------------|--------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | EXT_SYNC            | Input  | Selects the external SYNC_IN signal when set to logic 1; do not float.                                                |  |  |  |

| 2    | RGB_SEL             | Input  | Selects RGB clamp levels when set to logic 1. YPbPr clamps levels when set to logic 0; do not float.                  |  |  |  |

| 3    | Y1/G1               | Input  | Y or G input 1 - may be connected to a signal that includes sync.                                                     |  |  |  |

| 4    | Y2/G2               | Input  | Y or G input 2 - may be connected to a signal that includes sync.                                                     |  |  |  |

| 5    | Pb1/B1              | Input  | Pb or B input 1.                                                                                                      |  |  |  |

| 6    | Pb2/B2              | Input  | Pb or B input 2.                                                                                                      |  |  |  |

| 7    | Pr1/R1              | Input  | Pr or R input 1.                                                                                                      |  |  |  |

| 8    | Pr2/R2              | Input  | Pr or R input 2.                                                                                                      |  |  |  |

| 9    | F <sub>SEL0</sub>   | Input  | Selects filter corner frequency or bypass, see Table 2. Do not float.                                                 |  |  |  |

| 10   | F <sub>SEL1</sub>   | Input  | Selects filter corner frequency or bypass, see Table 2. Do not float.                                                 |  |  |  |

| 11   | GND                 | Input  | Must be tied to ground, do not float.                                                                                 |  |  |  |

| 12   | GND                 | Input  | Must be tired to ground, do not float.                                                                                |  |  |  |

| 13   | 0dB_SEL             | Input  | Selects output gain of 0dB when set to logic 1; 6dB when set to logic 0. Do not float.                                |  |  |  |

| 14   | Pr/R <sub>out</sub> | Output | Pr or R output.                                                                                                       |  |  |  |

| 15   | Pb/B <sub>OUT</sub> | Output | Pb or B output.                                                                                                       |  |  |  |

| 16   | Y/G <sub>OUT</sub>  | Output | Y or G output.                                                                                                        |  |  |  |

| 17   | In2_SEL             | Input  | Selects MUX input 2 when set to logic 1; MUX input 1 when set to logic 0. Do not float.                               |  |  |  |

| 18   | SYNC_IN             | Input  | External sync inputs signal, square wave crossing $V_{\text{IL}}$ and $V_{\text{IN}}$ input thresholds. Do not float. |  |  |  |

| 19   | V <sub>CC</sub>     | Input  | +5V supply. Do not float.                                                                                             |  |  |  |

| 20   | V <sub>CC</sub>     | Input  | +5V supply. Do not float.                                                                                             |  |  |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                      | Min. | Max.                  | Unit |

|------------------|------------------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage                              | -0.3 | +6.6                  | V    |

| V <sub>IO</sub>  | Analog and Digital I/O                         | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| I <sub>OUT</sub> | Output Current, Any One Channel, Do Not Exceed |      | 60                    | mA   |

### Note:

1. Functional operation under any of these conditions is not implied.

# **Reliability Information**

| Symbol           | Parameter                                                             | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------------------------------------|------|------|------|------|

| TJ               | Junction Temperature                                                  |      |      | +150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                             | +150 | °C   |      |      |

| TL               | Lead Temperature, Soldering 10 seconds                                |      |      | +300 | °C   |

| $\Theta_{JA}$    | Thermal Resistance, JEDEC Standard Multi-layer Test Boards, Still Air |      | 74   |      | °C/W |

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol              | Parameter                   | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------|------|------|------|------|

| T <sub>A</sub>      | Operating Temperature Range | 0    | /    | 70   | °C   |

| V <sub>CC</sub>     | V <sub>CC</sub> Range       | 4.75 | 5.00 | 5.25 | V    |

| R <sub>SOURCE</sub> | Input Source Resistance     |      | _    | 150  | Ω    |

# **DC Electrical Specifications**

$T_A=25^{\circ}C$ ,  $V_I=1V_{PP}$ ,  $V_{CC}=5.0V$ ; all inputs AC coupled with  $0.1\mu F$ ; all outputs AC coupled into  $150\Omega$ ; referenced to 400kHz; unless otherwise noted.

| Symbol              | Parameter                         | Conditions                                                                           | Min. | Тур.  | Max.            | Units    |

|---------------------|-----------------------------------|--------------------------------------------------------------------------------------|------|-------|-----------------|----------|

| Icc                 | Supply Current <sup>(2)</sup>     | V <sub>CC</sub> , no load                                                            |      | 90    | 130             | mA       |

| VI                  | Input Voltage Maximum             |                                                                                      |      | 1.5   |                 | $V_{PP}$ |

| V <sub>IL</sub>     | Digital Input Low <sup>(2)</sup>  | F <sub>SELO</sub> , F <sub>SEL1</sub> , RGB_SEL, 0dB_SEL, EXT_SYNC, IN2_SEL, SYNC_IN | 0    |       | 0.8             | ٧        |

| V <sub>IH</sub>     | Digital Input High <sup>(2)</sup> | F <sub>SELO</sub> , F <sub>SEL1</sub> , RGB_SEL, 0dB_SEL, EXT_SYNC, IN2_SEL, SYNC_IN | 2.4  |       | V <sub>CC</sub> | ٧        |

| V <sub>CLAMP1</sub> | Output Clamp Voltage              | R,G,B,Y                                                                              |      | 250   |                 | mV       |

| V <sub>CLAMP2</sub> | Output Clamp Voltage              | Pb and Pr                                                                            |      | 1.125 |                 | V        |

| PSRR                | Power Supply Rejection Ratio      | DC, All Channels                                                                     |      | -40   |                 | dB       |

### Note:

2. 100% tested at 25°C.

# **Standard-Definition Electrical Specifications**

$T_A=25^{\circ}C$ ,  $V_I=1V_{PP}$ ,  $V_{CC}=5.0V$ ,  $F_{SEL0}=0$ ,  $F_{SEL1}=0$ ,  $0dB\_SEL=0$  (gain=6dB),  $R_{SOURCE}=37.5\Omega$ ; all inputs AC coupled with  $0.1\mu F$ ; all outputs AC coupled with  $220\mu F$  into  $150\Omega$  referenced to 400kHz; unless otherwise noted.

| Symbol               | Parameter                                            | Conditions                                                     | Min. | Тур. | Max. | Units |

|----------------------|------------------------------------------------------|----------------------------------------------------------------|------|------|------|-------|

| ۸۱/                  | SD Gain, 0dB_SEL=0 <sup>(3)</sup>                    | All Channels CD Made                                           | 5.6  | 6.0  | 6.4  | dD    |

| AV <sub>SD</sub>     | SD Gain, 0dB_SEL=1 <sup>(3)</sup>                    | All Channels, SD Mode                                          | -0.4 | 0    | 0.4  | dB    |

| f <sub>1dBSD</sub>   | -1dB Bandwidth for SD                                | All Channels                                                   | 5.5  | 7.6  |      | MHz   |

| f <sub>CSD</sub>     | -3dB Bandwidth for SD                                | All Channels                                                   |      | 8.5  |      | MHz   |

| f <sub>SBSD</sub>    | Attenuation: SD (Stop-band Rejection) <sup>(3)</sup> | All Channels at f=27MHz                                        | 40   | 56   |      | dB    |

| dG                   | Differential Gain                                    | All Channels                                                   | 1    | 0.40 |      | %     |

| dφ                   | Differential Phase                                   | All Channels                                                   |      | 0.25 |      | ٥     |

| THD                  | Output Distortion,<br>All Channels                   | V <sub>OUT</sub> =1.8V <sub>PP</sub> at 1MHz                   |      | 0.4  |      | %     |

| X <sub>TALK</sub>    | Crosstalk, Channel-to-channel                        | At 1.0MHz                                                      |      | -68  |      | dB    |

| IN <sub>MUXISO</sub> | INMUX Isolation                                      | At 1.0MHz                                                      |      | -70  |      | dB    |

| SNR                  | Signal-to-Noise Ratio                                | All Channels, NTC-7 Weighting, 4.2MHz Lowpass, 100Khz Highpass |      | 74   |      | dB    |

| t <sub>pdSD</sub>    | Propagation Delay for SD                             | Delay from Input to Output at 4.5MHz                           |      | 80   |      | ns    |

| T1                   | SYNC to SYNC_IN Delay                                |                                                                |      | 10   |      | ns    |

| T2                   | SYNC_IN Minimum Pulse<br>Width                       |                                                                |      | 4    | 1    | μs    |

### Note:

3. 100% tested at 25°C.

# **Progressive Scan (PS) Electrical Specifications**

$T_A$ =25°C,  $V_I$ =1 $V_{PP}$ ,  $V_{CC}$ =5.0V,  $F_{SEL0}$ =1,  $F_{SEL1}$ =0, 0dB\_SEL=0 (gain=6dB),  $R_{SOURCE}$ =37.5 $\Omega$ ; all inputs AC coupled with 0.1 $\mu$ F; all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  referenced to 400kHz; unless otherwise noted.

| Symbol             | Parameter                                         | Conditions                          | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------------------------|-------------------------------------|------|------|------|-------|

| ۸۱/                | PS Gain, 0dB_SEL=0 <sup>(4)</sup>                 | All Channels PS Mode                | 5.6  | 6.0  | 6.4  | dB    |

| AV <sub>PS</sub>   | PS Gain, 0dB_SEL=1 <sup>(4)</sup>                 | All Channels PS Mode                | -0.4 | 0    | 0.4  | dB    |

| f <sub>1dBPS</sub> | -1dB Bandwidth for PS <sup>(4)</sup>              | All Channels                        | 10   | 15   |      | MHz   |

| f <sub>CPS</sub>   | -3dB Bandwidth for PS                             | All Channels                        |      | 17   |      | MHz   |

| f <sub>SBPS</sub>  | Attenuation, PS (Stop-band Reject) <sup>(4)</sup> | All Channels at f=54MHz             | 40   | 48   |      | dB    |

| t <sub>pdPS</sub>  | Propagation Delay for PS                          | Delay from Input to Output at 10MHz |      | 45   |      | ns    |

| T1                 | SYNC to SYNC_IN Delay                             |                                     |      | 10   |      | ns    |

| T2                 | SYNC_IN Minimum Pulse<br>Width                    |                                     |      | 2    |      | μs    |

### Note:

# **High-Definition Electrical Specifications**

$T_A$ =25°C,  $V_I$ =1 $V_{PP}$ ,  $V_{CC}$ =5.0 $V_I$ ,  $F_{SEL0}$ =0,  $F_{SEL1}$ =1, 0dB\_SEL=0 (gain=6dB),  $R_{SOURCE}$ =37.5 $\Omega$ ; all inputs AC coupled with 0.1 $\mu$ F; all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  referenced to 400kHz; unless otherwise noted.

| Symbol             | Parameter                                         | Conditions                          | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------------------------|-------------------------------------|------|------|------|-------|

| AV <sub>HD</sub>   | HD Gain, 0dB_SEL=0 <sup>(5)</sup>                 | All Channels HD Mode                | 5.6  | 6.0  | 6.4  | dB    |

| AVHD               | HD Gain, 0dB_SEL=1 <sup>(5)</sup>                 | All Channels HD Mode                | -0.4 | 0    | 0.4  | dB    |

| f <sub>1dBHD</sub> | -1dB Bandwidth for HD <sup>(5)</sup>              | All Channels                        | 20   | 29   |      | MHz   |

| f <sub>CHD</sub>   | -3dB Bandwidth for HD                             | All Channels                        |      | 33   |      | MHz   |

| f <sub>SBHD</sub>  | Attenuation, HD (Stop-band Reject) <sup>(5)</sup> | All Channels at f=74.25MHz          | 30   | 40   |      | dB    |

| t <sub>pdHD</sub>  | Propagation Delay for HD                          | Delay from Input to Output at 20MHz | - /  | 26   |      | ns    |

| T1                 | SYNC to SYNC_IN Delay                             |                                     | 4    | 10   |      | ns    |

| T2                 | SYNC_IN Minimum Pulse<br>Width                    |                                     |      | 1.5  |      | μs    |

### Note:

# Unfiltered 1080p Bypass (Wide Bandwidth) Electrical Specifications

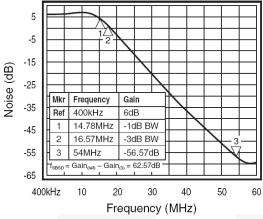

$T_A$ =25°C,  $V_I$ =1 $V_{PP}$ ,  $V_{CC}$ =5.0 $V_I$ ,  $F_{SEL0}$ =1,  $F_{SEL1}$ =1, 0dB\_SEL=0 (gain=6dB),  $R_{SOURCE}$ =37.5 $\Omega$ ; all inputs AC coupled with 0.1 $\mu$ F; all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  referenced to 400kHz; unless otherwise noted.

| Symbol             | Parameter                      | Conditions                          | Min. | Тур. | Max. | Units |

|--------------------|--------------------------------|-------------------------------------|------|------|------|-------|

| ۸۱/                | Gain, 0dB_SEL=0 <sup>(6)</sup> | All Channels Bypass Mode            | 5.6  | 6.0  | 6.4  | dB    |

| $AV_{WB}$          | Gain, 0dB_SEL=1 <sup>(6)</sup> | All Channels Bypass Mode            | -0.4 | 0    | 0.4  | dB    |

| f <sub>1dBWB</sub> | -1dB Bandwidth                 | All Channels                        |      | 63   |      | MHz   |

| f <sub>CWB</sub>   | -3dB Bandwidth                 | All Channels                        |      | 91   |      | MHz   |

| t <sub>pdWB</sub>  | Propagation Delay              | Delay from Input to Output at 20MHz |      | 10   |      | ns    |

### Note:

6. 100% tested at 25°C.

<sup>4. 100%</sup> tested at 25°C.

<sup>5. 100%</sup> tested at 25°C.

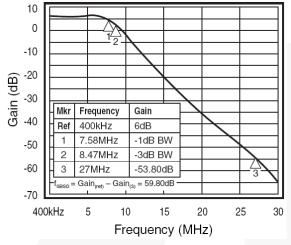

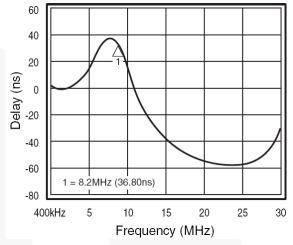

# **Typical Performance Characteristics**

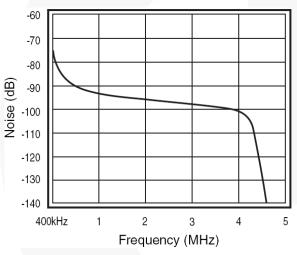

$T_A$ =25°C,  $V_I$ =1 $V_{PP}$ ,  $V_{CC}$ =5.0V,  $F_{SEL0}$ =0,  $F_{SEL1}$ =0, 0dB\_SEL=0 (gain=6dB),  $R_{SOURCE}$ =37.5 $\Omega$ ; all inputs AC coupled with 0.1 $\mu$ F; all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$ , referenced to 400kHz; unless otherwise noted.

Figure 4. SD Frequency Response

Figure 5. SD Group Delay vs. Frequency

Figure 6. SD Noise vs. Frequency

Figure 7. SD Differential Gain

Figure 8. SD Differential Phase

### **Progressive Scan (PS) Typical Performance Characteristics**

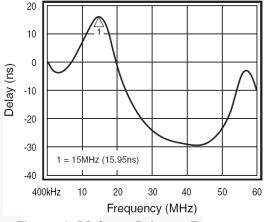

$T_A$ =25°C,  $V_I$ =1 $V_{PP}$ ,  $V_{CC}$ =5.0V,  $F_{SEL0}$ =1,  $F_{SEL1}$ =0, 0dB\_SEL=0 (gain=6dB),  $R_{SOURCE}$ =37.5 $\Omega$ ; all inputs AC coupled with 0.1 $\mu$ F; all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$ , referenced to 400kHz; unless otherwise noted.

Figure 9. PS Frequency Response

Figure 10. PS Group Delay vs. Frequency

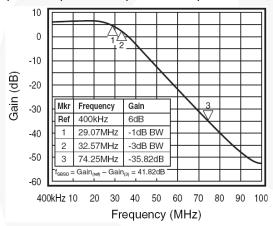

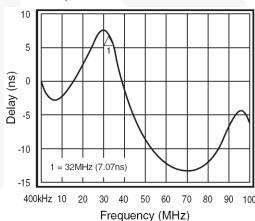

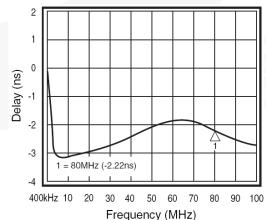

# **High-Definition Typical Performance Characteristics**

$T_A$ =25°C,  $V_I$ =1 $V_{PP}$ ,  $V_{CC}$  = 5.0V,  $F_{SEL0}$ =0,  $F_{SEL1}$ =1, 0dB\_SEL=0 (gain=6dB),  $R_{SOURCE}$ =37.5 $\Omega$ ; all inputs AC coupled with 0.1 $\mu$ F; all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$ , referenced to 400kHz; unless otherwise noted.

Figure 11. HD Frequency Response

Figure 12. HD Group Delay vs. Frequency

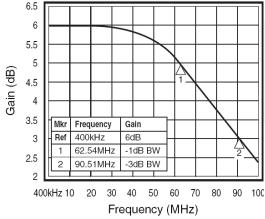

### Unfiltered 1080p Bypass (WB) Typical Performance Characteristics

$T_A$ =25°C,  $V_I$ =1 $V_{PP}$ ,  $V_{CC}$ =5.0V,  $F_{SEL0}$ =1,  $F_{SEL1}$ =1, 0dB\_SEL=0 (gain=6dB),  $R_{SOURCE}$ =37.5 $\Omega$ ; all inputs AC coupled with 0.1 $\mu$ F; all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$ , referenced to 400kHz: unless otherwise noted.

Frequency (MHz)

Figure 13. Bypass Mode Frequency Response

Figure 14. Bypass Mode Group Delay vs. Frequency

### **Functional Description**

### Introduction

The FMS6403 is a next-generation filter solution from Fairchild Semiconductor addressing the expanding filtering needs for televisions, set-top boxes, and DVD players, including progressive scan capability. The product provides selectable filtering with cutoff frequencies of 30MHz, 15MHz, and 8MHz for all three channels. In addition, the filters can be bypassed for wider bandwidth applications. The FMS6403 allows consumer devices to support a variety of resolution standards with the same hardware.

Multiplexers on the channel inputs are controlled by the IN2\_SEL pin. The RGB\_SEL pin can be used to set the sync tip clamp voltages for YPbPr or RGB applications. All three channels are set for 250mV sync tips to reduce DC-coupled power dissipation for RGB inputs. The lower output bias voltage is not suitable for the PbPr outputs: so for YPbPr inputs, these signals are clamped to 1.125V, while Y is still clamped to 250mV. Sync tip clamping voltages are set by forcing the desired DC bias level during the active sync period. For systems without sync on Y/G, an external sync input is provided. If sync exists on one input Y/G signal, but not on the other Y/G input signal, the IN2 SEL and EXT SYNC control inputs may be wired together on the PCB to switch the sync source with the input source. Both standard-definition (bi-level) and high-definition (trilevel) sync are supported at the Y/G inputs and SYNC IN depending on the FSEL[1:0] inputs. See the Sync Processing section for further details.

Standard-definition (480i) and progressive (480p) signals are clamped by forcing the signal to the desired voltage during the sync pulse. For signals with sync, the sync tip itself is forced to the clamp voltage (typically 250mV). When high-definition (HD) sync is present (trilevel sync) the sync tip duration is too short to allow this approach. To accurately clamp HD signals, the sync pulse starts a timer and the actual clamping is done at the blanking level right after the sync pulse. The sync tip is typically placed at 250mV if its amplitude is 300mV.

All three outputs are driven by amplifiers with selectable gains of 0dB or +6dB. The gain is set with the 0dB\_SEL pin. These amplifiers can drive two terminated video loads  $(75\Omega)$  to  $2V_{PP}$  with a  $1V_{PP}$  input when set to 6dB gain. The input range is limited to  $1.5V_{PP}$  and the output range is limited to  $2.5V_{PP}$ .

All control inputs must be driven high or low. Do not leave them floating.

### **External SYNC Mode**

The FMS6403 can properly recover sync timing from video signals that include sync. If the Y-input video signals do not include sync, the FMS6403 can be used in sxternal SYNC mode. In external sync mode, (EXT\_SYNC pin is high), a pulsed input must be applied to the SYNC\_IN pin. If there is no video signal present, therefore no sync signal present, there must be an input

applied to the SYNC\_IN pin. When there is no video signal on the video inputs, SYNC\_IN can be a sync pulse every 60µs to mimic the slowest sync in a regular video signal. The following two sections discuss the sync processing and timing required in more detail.

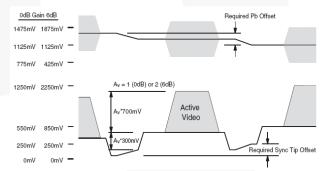

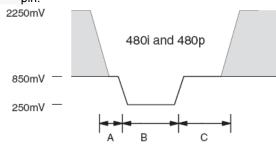

# SD and Progressive Scan Video Sync Processing

The FMS6403 must control the DC offset of AC-coupled input signals since the average DC level of video varies with image content. If the input offset is allowed to wander, the common-mode input range of the amplifiers can be exceeded, leading to signal distortion. DC offset adjustment is referred to as "clamping" or, in some cases, biasing, and must be done at the correct time during each video line. The optimum time is during the sync pulse, since it is the lowest input voltage. This approach works well for 480i and 480p signals since the sync tip duration is long enough to allow the DC-offset errors to be compensated from line to line. The DCoffset of the sync tip is adjusted as illustrated in Figure 15 by forcing a current on the input during the sync pulse. The sync tip is clamped to approximately 250mV. Signals like Pb and Pr with a symmetric voltage range (±350mV) are clamped to approximately 1.125V. Note that the following diagrams illustrate DC restore functionality and indicate output voltage levels for both 0dB and 6dB gain (1V<sub>PP</sub> and 2V<sub>PP</sub> video signals at the output pin).

Figure 15. Bi-level Sync Tip Clamping and Bias

In some cases, the sync voltage may be compressed to less than the nominal 300mV value. The FMS6403 can successfully recover SD and progressive scan sync greater than 100mV (compressed to 33% of nominal).

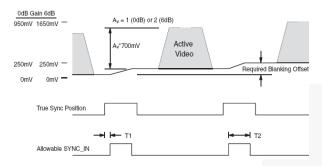

The FMS6403 can properly recover sync timing from luma and green, which include sync. If none of the video signals includes sync, the EXT\_SYNC control input can be set high and an external sync signal must be input on the SYNC\_IN pin. *Refer to the External Sync section for more details*. The timing required for this operating mode is shown in Figure 16. SYNC timings, T1 and T2, are defined in the SD Electrical Specifications section.

Figure 16. Bi-level External Sync Clamping and Bias

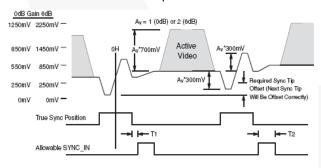

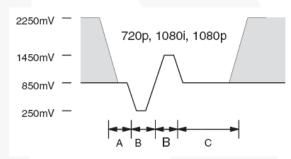

# HD and Bypass Mode Video Sync Processing

When the input signal is a high-definition signal, the trilevel sync pulse is too short to allow proper clamp operation. Rather than clamp during the sync pulse, the sync pulse is located and the signal is clamped to the blanking level. This is done such that the sync tip is set to approximately 250mV for signals with 300mV sync tip amplitude. The EXT\_SYNC control input selects the sync stripper output or the SYNC\_IN pin for use by the clamp circuit.

### Note:

The SYNC\_IN timing for HD signals is different from the timing for SD or PS signals.

For HD signals, the SYNC\_IN signal must be high when the clamp must be active. This is during the time immediately after the sync pulse while the signal is at the blanking level. This operation is shown in Figure 17. Note that the following diagrams illustrate DC restore functionality and indicate output voltage levels for both 0dB and 6dB gain (1V<sub>PP</sub> and 2V<sub>PP</sub> video signals at the FMS6403 output pin). SYNC timings, T1 and T2, are defined in the HD Electrical Specifications table section.

Figure 17. Tri-level Blanking Clamp

### Note:

Tri-level sync may only be compressed 5%. If HD sync is compressed more than 5%, it may not be properly located.

### **Sync Timing**

Normally, the FMS6403 responds to bi-level sync and clamps the sync tip during period 'B' in Figure 19. When the filters are switched to high-definition mode (30MHz) or bypass mode, the sync processing responds to trilevel sync and clamps to the blanking level during period 'C' in Figure 19.

### Note:

The diagram indicates SYNC timings at the output pin.

Figure 18. Sync Timing Bi-level

Figure 19. Sync Timing Tri-level

The tri-level sync pulse is located such that the broad pulses in the vertical interval do not trigger the clamp. To improve the system settling at turn-on, the broad pulses are clamped to just above ground. Once the broad pulses (and tri-level sync tips) are above ground, the normal clamping process takes over and clamps to the blanking level during period 'C' in Figure 19.

FMS6403 is supports the video standards and associated sync timings shown in Table 1, (additional standards, such as 483p59.94, also work correctly).

### **Table 1. Sync Timings**

| Format | Refresh | Sample<br>Rate | Period (T) | Α         | В          | С           | H-Rate   |

|--------|---------|----------------|------------|-----------|------------|-------------|----------|

| 480i   | 30Hz    | 13.5MHz        | 74ns       | 20T=1.5μs | 64T=4.7µs  | 61T=4.5µs   | 15.75kHz |

| 480p   | 60Hz    | 27 MHz         | 37ns       | 20T=750ns | 64T=2.35µs | 61T=2.25µs  | 31.5kHz  |

| 720p   | 60Hz    | 74.25 MHz      | 13.4ns     | 70T=938ns | 40T=536ns  | 220T=2.95ns | 45kHz    |

| 1080i  | 30Hz    | 74.25 MHz      | 13.4ns     | 20T=589ns | 44T=589ns  | 148T=1.98ns | 33.75kHz |

| 1080p  | 60Hz    | 148.5 MHz      | 6.7ns      | 20T=596ns | 44T=296ns  | 148T=996ns  | 67.5kHz  |

### Note:

10. Timing values are approximate for 30Hz/60Hz refresh rates.

**Table 2. Filter Settings**

| FSEL1, Pin 10 | FSEL0, Pin 9 | Filter -3db Frequency | Video Format     | Sync Format                  |

|---------------|--------------|-----------------------|------------------|------------------------------|

| 0             | 0            | 8MHz                  | SD, 480i         | Bi-level, 4.7µs pulse width  |

| 0             | 1            | 15MHz                 | PS, 480p         | Bi-level, 2.35µs pulse width |

| 1             | 0            | 32MHz                 | HD, 1080i, 720p  | Tri-level, 589ns pulse width |

| 1             | 1            | Filter Bypass         | Unfiltered 1080p | Tri-level, 290ns pulse width |

### **Table 3. Gain Settings Tables**

| 0dB_SEL, Pin 13 | Gain (dB) | V <sub>IN/</sub> <sup>(11)</sup> | V <sub>OUT</sub> <sup>(11)</sup> |

|-----------------|-----------|----------------------------------|----------------------------------|

| 0               | 6         | 1V <sub>PP</sub>                 | 2V <sub>PP</sub>                 |

| 1               | 0         | 1V <sub>PP</sub>                 | 1V <sub>PP</sub>                 |

### Note:

11. Video level does not include damp voltage, which offsets the input above ground.

### **Table 4. Sync Settings**

| EXT_SYNC, Pin 1 | Sync Source          |

|-----------------|----------------------|

| 0               | Y/G Input, Pin 3/4   |

| 1               | SYNC_IN Input, Pin 2 |

### **Table 5. Clamp Settings**

| RGB_SEL, Pin 2 | Input      | Output     | Clamp Voltage |

|----------------|------------|------------|---------------|

|                | Y1, Pin 3  | Y, Pin 16  | 250mV         |

| 0              | Pb1, Pin 5 | Pb, Pin 15 | 1.125V        |

|                | Pr1, Pin 7 | Pr, Pin 14 | 1.125V        |

|                | G1, Pin 3  | G, Pin 16  | 250mV         |

| 1              | B1, Pin 5  | B, Pin 15  | 250mV         |

|                | R1, Pin 7  | R, Pin 14  | 250mV         |

# **Applications Information**

# **Input Circuitry**

The DC restore circuit requires a source impedance ( $R_{SOURCE} = R_S \mid\mid R_T$ ) of less than or equal to 150 $\Omega$  for correct operation. Driving the FMS6403 with a high-impedance source (e.g. a DAC loaded with 330 $\Omega$ ) does not yield optimum results. *Refer Figure 2 for details*.

### **Output Drive**

The FMS6403 is specified to operate with output currents typically less than 60mA, more than sufficient for a dual  $(75\Omega)$  video load. Internal amplifiers are current limited to approximately 100mA and should withstand brief-duration, short-circuit conditions; however, this capability is not guaranteed.

The maximum specified input voltage of  $1.5V_{PP}$  can be sustained for all inputs. When the input is clamped to 1.125V, this does not result in a meaningful output signal. With a gain of 6dB, the output should be 1.125V  $\pm 1.5V$ , which is not possible since the output cannot drive below ground. This condition will not damage the part; however, the output will be clipped. For signals clamped to 250mV, this does not occur.

Signals at mid-scale during SYNC (Pb and Pr) must be clamped to 1.125V. Signals that are at their lowest during SYNC (Y, R, G, B) must be clamped to 250mV for proper operation. Clamping a Pr signal to 250mV results in clipping the bottom of the signal.

The  $220\mu F$  capacitor coupled with the  $150\Omega$  termination, as shown in the Figure 2, forms a high-pass filter that blocks the DC while passing the video frequencies and avoiding tilt. Any value lower than  $220\mu F$  creates problems, such as video tilt. Higher values, such as  $470\mu F$  -  $1000\mu F$ , are the most optimal output coupling capacitor. By AC coupling, the average DC level is zero and the output voltages of all channels is centered ~zero.

### Sync Recovery

The FMS6403 typically recovers bi-level sync with amplitude greater than 100mV (33% compressed relative to the nominal 300mV amplitude). The FMS6403 looks for the lowest signal voltage and clamps this to approximately 250mV at the output.

Tri-level sync may not be compressed more than 5% (15mV) for correct operation. Tri-level sync is located by finding the edges of the tri-level pulse and running a timer to operate the clamp during the back porch interval.

The selection of the 8MHz or 15MHz filters enables bilevel sync recovery. Selection of the 30MHz filter or bypass mode enables tri-level sync recovery. Bi-level and tri-level sync recovery are not interchangeable. See the Sync Processing section for more information.

### **Power Dissipation**

The output drive configuration must be considered when calculating overall power dissipation. Care must be taken not to exceed the maximum die junction temperature. The following example can be used to

calculate the FMS6403's power dissipation and internal temperature rise:

$$T_{J} = T_{A} + Pd \Theta_{JA}$$

where:

$$P_{D} = P_{CH1} + P_{CH2} + P_{CH3}$$

and:

$$PCHx = V_{S} \cdot I_{CH} - (V_{O}^{2}/R_{L})$$

$V_0 = 2V_{IN} + 0.280V$

$I_{CH} = (I_{CC} / 3) + (V_0 / R_L)$

V<sub>IN</sub> = RMS value of input signal

$I_{CC} = 90 \text{mA}$

$V_S = 5V$

where:

R<sub>L</sub> = channel load resistance

Board layout can also affect thermal characteristics. Refer to the *Layout Considerations Section for more information*. The FMS6403 is specified to operate with output currents typically less than 60mA, more than sufficient for a single (150 $\Omega$ ) video load. Internal amplifiers are current limited to a maximum of 100mA and should withstand brief duration short circuit conditions, however this capability is not guaranteed.

### **Layout Considerations**

General layout and supply bypassing play major roles in high-frequency performance and thermal characteristics. Fairchild offers an evaluation board, FMS6403DEMO, to guide layout and aid device testing and characterization. The FMS6403DEMO is a four-layer board with a full power and ground planes. For optimum results, follow the steps below as a basis for high-frequency layout:

- Include 10µF and 0.1µF ceramic bypass capacitors.

- Place the 10µF capacitor within 0.75 inches of the power pin.

- Place the 0.1µF capacitor within 0.1 inches of the power pin.

- Connect all external ground pins as tightly as possible, preferably with a large ground plane under the package.

- Layout channel connections to reduce mutual trace inductance.

- Minimize all trace lengths to reduce series inductances. If routing across a board, place devise such that longer traces are at the inputs rather than the outputs.

If using multiple, low-impedance DC-coupled outputs; special layout techniques can help dissipate heat. For dual-layer boards, place a 0.5-inch to 1-inch (1.27cm to 2.54cm) square ground plane directly under the device and on the bottom side of the board. Use multiple vias to connect the ground planes. For multi-layer boards, additional planes (connected with vias) can be used for additional thermal improvements.

Worst-case additional die power due to DC loading can be estimated at  $({\rm V_{CC}}^2/4{\rm R_{load}})$  per output channel. This assumes a constant DC output voltage of  ${\rm V_{CC}}^2$ . For 5V  ${\rm V_{CC}}$  with a dual DC video load, add 25/(4•75) = 83mW, per channel.

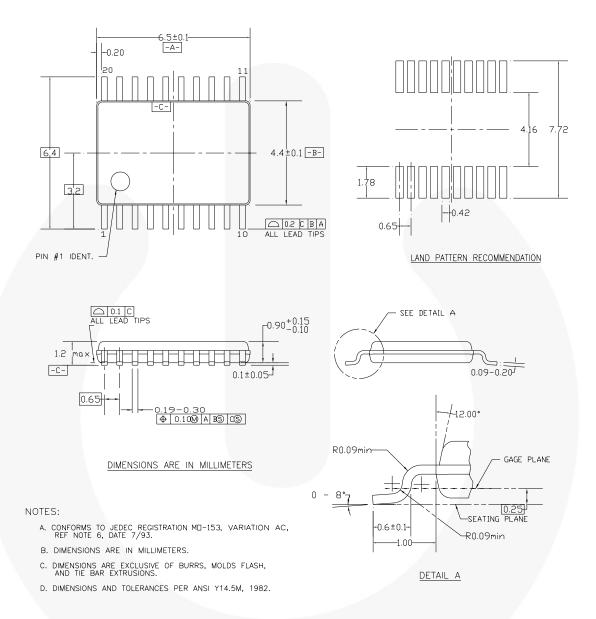

# **Physical Dimensions**

MTC20REVD1

Figure 20. 20-lead Thin Shrink Small Outline Package (TSSOP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>

### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

ACE Y® Build it Now™ CorePLUS™ CROSSVOLT™ CTL TM

Current Transfer Logic™ EcoSPARK<sup>®</sup> EZSWITCH™ \*

Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT®

FAST® FastvCore™ FlashWriter<sup>®</sup>\* FPS™ FRFET®

Global Power Resources

Green FPS™

Green FPS™e-Series™

GTO™ i-Lo™ IntelliMAX™ ISOPLANAR™ MegaBuck™ MICROCOUPLER™

MicroFET™ MicroPak™ MillerDrive™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR®

PDP-SPM™ Power220® POWEREDGE® Power-SPM™ PowerTrench®

Programmable Active Droop™ QFÉT®

QSTM QT Optoelectronics™ Quiet Series™

RapidConfigure™ SMART STÅRT™ SPM<sup>®</sup>

STEALTH TM SuperFET™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8

SupreMOS™ SvncFET™ SYSTEM®

GENERAL

The Power Franchise®

wer franchise TinyBoost™ TinyBuck<u>™</u> TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ uSerDes™ UHC® Ultra FRFET™

UniFET™ VCX™

### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

### As used herein:

- 1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support, which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness

### PRODUCT STATUS DEFINITIONS

### Definition of Terms

| Datasheet Identification | Product Status                                                                                                                                     | Definition                                                                                                                                                                                               |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Advance Information      | Formative or In Design                                                                                                                             | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |

| Preliminary              | First Production                                                                                                                                   | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |

| No Identification Needed | Full Production                                                                                                                                    | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to imprithe design.                                                  |  |

| Obsolete                 | This datasheet contains specifications on a product that has be discontinued by Fairchild Semiconductor. The datasheet is prince information only. |                                                                                                                                                                                                          |  |

Rev. 133

<sup>\*</sup> EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative