Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **FMS7401L**

## **Digital Power Controller**

## **General Description**

The FMS7401L is a Digital Power Controller designed for applications requiring ease of digital based control over analog based implementations. The FMS7401L is an ideal solution to implement ballast control, motor control and battery management functions. It integrates a wide variety of analog blocks with an 8-bit microcontroller core to offer a complementary feature set with high performance, low power and small size in a single chip.

The FMS7401L is intended for applications using a supply voltage in the 2.7V to 3.6V range. It is fabricated using CMOS technology and is fully static offering a significant power savings. The FMS7401L is available in both 8-pin and 14-pin PDIP, SOIC and TSSOP packages.

### **Features**

- 8-bit Microcontroller Core

- · 1K bytes on-board code EEPROM

- 64 bytes data EEPROM

- · 64 bytes SRAM

- · Watchdog Reset

- Multi-input Wakeup on all general purpose I/O pins

- Fast 12-bit PWM timer with dead time control and halfbridge output drive

- Input Capture Mode

- 5-Ch 8-bit Analog-to-Digital Converter

- 20 uS conversion time

- Sample and Hold

- Internal Voltage Reference (1.21V)

- Gated Auto-sampling Mode

- Auto-zero Amplifier (gain 16)

- · Uncommitted Amplifier

- Internal Current Source Generator (1mA)

- On-chip Oscillator

- No external components

- 1µs instruction cycle time

- · On-chip Power-on Reset

- · Programmable read and write disable functions

- Memory Mapped I/O

- Programmable Comparator (63 Levels)

- · Brown-out Reset

- Software selectable I/O option

- Push-pull outputs with tri-state option

- · Weak pull-up or high impedance inputs

- Fully static CMOS

- Power Saving Halt Mode

- < 1.3 $\mu$ A @ 3.3V

- Power Saving Idle Mode

- $-<180\mu A @ 3.3V$

- · Single supply operation

- -2.7V 3.6V

- 40 years data retention

- 100,000 data changes

- 8-/14-pin PDIP, SOIC, and TSSOP packages

- In-circuit programming

- Fast Page-write Programming Mode

|          |                | Program        | Data Mem | ory (bytes) |     |           |

|----------|----------------|----------------|----------|-------------|-----|-----------|

| Device   | Supply Voltage | Memory (bytes) | SRAM     | Data EEPROM | I/O | Pin Count |

| FMS7401L | 2.7V - 3.6V    | 1K             | 64       | 64          | 6   | 8         |

| FMS7401L | 2.7V - 3.6V    | 1K             | 64       | 64          | 8   | 14        |

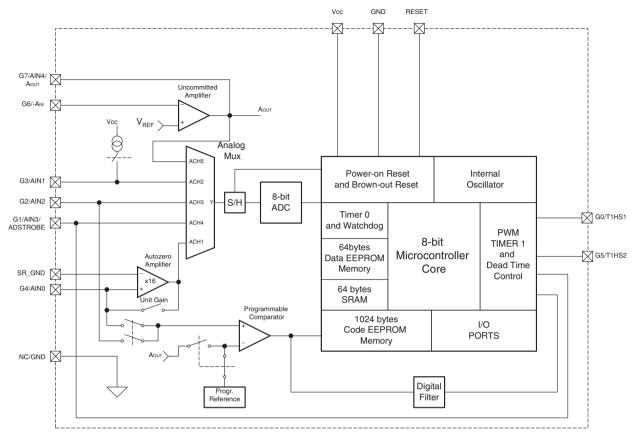

## **Block Diagram**

Figure 1. FMS7401L Block and Connection Diagram

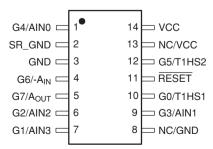

## **Pin Configurations**

FMS7401L 14-Pin PDIP/SOIC/TSSOP

## **FMS7401L Pin Definitions**

| Pin Number   |       |                       |                     |                                                                                                                                      |  |

|--------------|-------|-----------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| 8-1          | Pin   | 14-Pin                |                     |                                                                                                                                      |  |

| PDIP<br>SOIC | TSSOP | PDIP<br>SOIC<br>TSSOP | Pin Name            | Pin Function Description                                                                                                             |  |

| 1            | 3     | 1                     | G4/AIN0             | General purpose I/O port (bit 4 of the I/O configuration registers).                                                                 |  |

|              |       |                       |                     | AIN0 analog input of the ADC (autozero amplifier's positive terminal).                                                               |  |

|              |       |                       |                     | Programmable Comparator non-inverting input, if COMPSEL=0.                                                                           |  |

| 2            | 4     | 3                     | GND                 | Digital ground pin.                                                                                                                  |  |

| 3            | 5     | 6                     | G2/AIN2             | General purpose I/O port (bit 2 of the I/O configuration registers).                                                                 |  |

|              |       |                       |                     | AIN2 analog input of the ADC.                                                                                                        |  |

|              |       |                       |                     | Programmable Comparator non-inverting input, if COMPSEL=1.                                                                           |  |

| 4            | 6     | 7                     | G1/AIN3/            | General purpose I/O port (bit 1 of the I/O configuration registers).                                                                 |  |

|              |       |                       | ADSTROBE            | AIN3 analog input of the ADC.                                                                                                        |  |

|              |       |                       |                     | External digital clock input.                                                                                                        |  |

|              |       |                       |                     | PWM Timer 1's ADSTROBE output.                                                                                                       |  |

| 5            | 7     | 9                     | G3/AIN1             | General purpose I/O port (bit 3 of the I/O configuration registers).                                                                 |  |

|              |       |                       |                     | AIN1 analog input of the ADC.                                                                                                        |  |

|              |       |                       |                     | Internal current source generator pin.                                                                                               |  |

| 6            | 8     | 10                    | G0/                 | General purpose I/O port (bit 0 of the I/O configuration registers).                                                                 |  |

|              |       |                       | T1HS1               | PWM Timer 1's T1HS1 output.                                                                                                          |  |

| 7            | 1     | 12                    | G5/                 | General purpose I/O port (bit 5 of the I/O configuration registers).                                                                 |  |

|              |       |                       | T1HS2               | PWM Timer 1's T1HS2 output.                                                                                                          |  |

| 8            | 2     | 14                    | VCC                 | Supply voltage input.                                                                                                                |  |

| _            | _     | 2                     | SR_GND              | AIN0 analog input of the ADC (autozero amplifier's negative terminal). SR_GND is internally connected to GND in the 8-pin FMS7401L.  |  |

| _            | _     | 4                     | G6/-A <sub>IN</sub> | General purpose I/O port (bit 6 of the I/O configuration registers).                                                                 |  |

|              |       |                       |                     | Uncommitted amplifier negative analog input.                                                                                         |  |

| _            | _     | 5                     | G7/AIN4/            | General purpose I/O port (bit 7 of the I/O configuration registers).                                                                 |  |

|              |       |                       | Аоит                | AIN4 analog input of the ADC.                                                                                                        |  |

|              |       |                       |                     | Uncommitted amplifier analog output.                                                                                                 |  |

| _            | _     | 8                     | NC/GND              | In the FMS7401L, pin 8 is internally connected to GND. Externally, pin 8 should be le unconnected or connected to GND.               |  |

| _            | _     | 11                    | RESET               | Active low external reset input.                                                                                                     |  |

| -            | _     | 13                    | NC/VCC              | In the FMS7401L, VCC is internally connected to pin 13. Externally, pin 13 should either be left unconnected or connected to pin 13. |  |

## **Table of Contents**

| <u>FMS7401L</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1  |

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| <u>Pin Configurations</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| FMS7401L Pin Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3  |

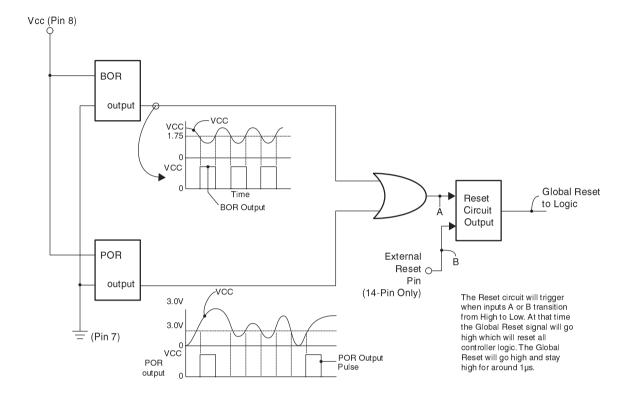

| 1 Reset Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8  |

| 1.1 Power-on Reset Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8  |

| 1.2 External Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 1.3 Brown-out Reset Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

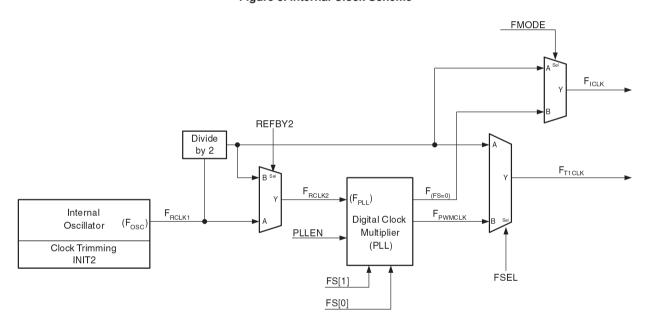

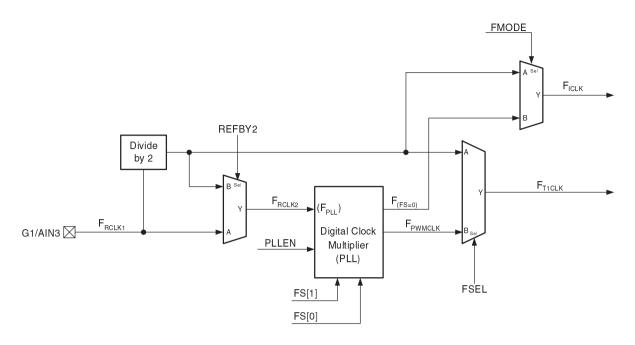

| 2 Clock Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

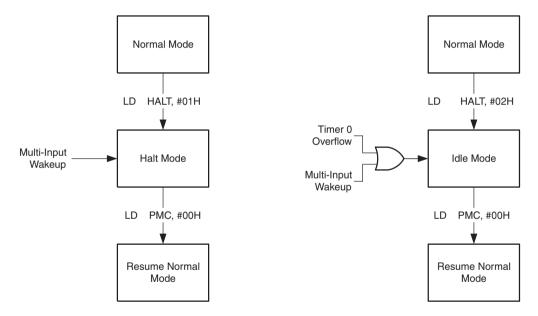

| 3 Power Saving Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 3.1 Halt Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 3.1.1 PLL Steps for Halt Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 3.2 Idle Mode 3.2.1 PLL Steps for Id |    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

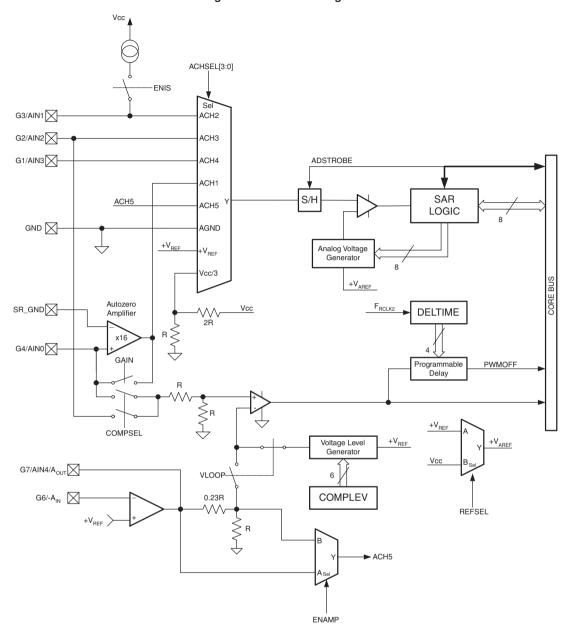

| 4 ADC Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |

| 4.1 ADC Circuit Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |

| 4.1.1 ADCNTRL1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 4.1.2 ADCNTRL2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 4.2 ADC Conversion Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 4.2.1 Analog Input Voltage and its 8-bit Digital Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 4.2.2 ADC Gated Auto-sampling Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4.2.3 ADC Conversion Clock Configuration 4.3 Autozero Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4.4 Uncommitted Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

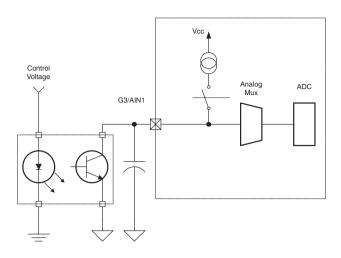

| 4.5 Current Source Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 5 Programmable Comparator Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 5.1 Programmable Comparator's Voltage Threshold Levels (VLOOP=0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 5.2 Hardware Voltage and Current Loop Control (VLOOP=1) 5.3 Digital Delay Filter with PWMOFF Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |