Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

August 2010

# FOD2200 Low Input Current Logic Gate Optocouplers

#### **Features**

- 1kV/µs minimum common mode rejection

- Compatible with LSTTL, TTL, and CMOS logic

- Wide V<sub>CC</sub> range (4.5V to 20V)

- 2.5Mbd guaranteed over temperature

- Low input current (1.6mA)

- Three state output (no pullup resistor required)

- Guaranteed performance from 0°C to 85°C

- Hysteresis

- Safety and regulatory approved

- UL1577, 5000 V<sub>RMS</sub> for 1 min.

- IEC60747-5-2

- >8.0mm clearance and creepage distance (option 'T' or 'TS')

- 1,414V Peak Working Insulation Voltage (V<sub>IORM</sub>)

#### **Applications**

- Isolation of high speed logic systems

- Computer peripheral interfaces

- Microprocessor system interfaces

- Ground loop elimination

- Pulse transformer replacement

- Isolated bus driver

- High speed line receiver

#### **Description**

The FOD2200 is an optically coupled logic gate that combine an AlGaAs LED and an integrated high gain photo detector. The detector has a three state output stage and has a detector threshold with hysteresis. The three state output eliminates the need for a pullup resistor and allows for direct drive of data busses. The hysteresis provides differential mode noise immunity and eliminates the potential for output signal chatter.

The Electrical and Switching Characteristics of the FOD2200 are guaranteed over the temperature range of  $0^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  and a  $V_{CC}$  range of 4.5V to 20V. Low  $I_{F}$  and wide  $V_{CC}$  range allow compatibility with TTL, LSTTL, and CMOS logic and result in lower power consumption compared to other high speed opto-couplers. Logic signals are transmitted with a maximum propagation delay of 300ns. The FOD2200 is useful for isolating high speed logic interfaces, buffering of input and output lines, and implementing isolated line receivers in high noise environments.

#### Truth Table (Positive Logic)

| LED | Enable | Output |

|-----|--------|--------|

| On  | Н      | Z      |

| Off | Н      | Z      |

| On  | L      | Н      |

| Off | L      | L      |

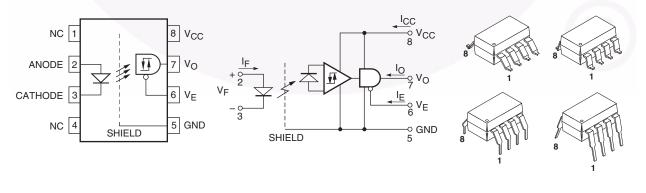

#### **Functional Block Diagram and Schematic**

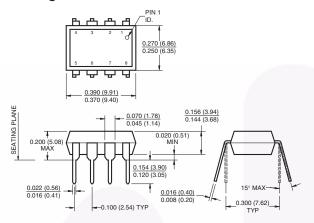

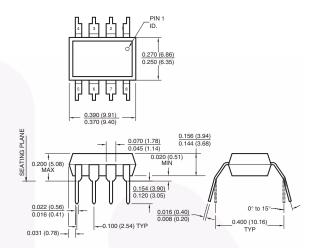

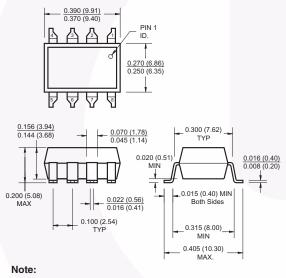

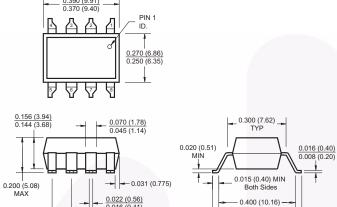

### Package Outlines

### **Safety and Insulation Ratings**

As per IEC 60747-5-2. This optocoupler is suitable for "safe electrical insulation" only within the safety limit data. Compliance with the safety ratings shall be ensured by means of protective circuits.

| Symbol                | Parameter                                                                                                                                             | Min.            | Тур.     | Max. | Unit              |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|------|-------------------|

|                       | Installation Classifications per DIN VDE 0110/1.89 Table 1                                                                                            |                 |          |      |                   |

|                       | For Rated Mains Voltage < 150Vrms                                                                                                                     |                 | I–IV     |      |                   |

|                       | For Rated Mains Voltage < 300Vrms                                                                                                                     |                 | I–IV     |      |                   |

|                       | For Rated Mains Voltage < 450Vrms                                                                                                                     |                 | I–III    |      |                   |

|                       | For Rated Mains Voltage < 600Vrms                                                                                                                     |                 | I–III    |      |                   |

|                       | For Rated Mains Voltage < 1000Vrms (Option T, TS)                                                                                                     |                 | I–III    |      |                   |

|                       | Climatic Classification                                                                                                                               |                 | 40/85/21 |      |                   |

|                       | Pollution Degree (DIN VDE 0110/1.89)                                                                                                                  |                 | 2        |      |                   |

| CTI                   | Comparative Tracking Index                                                                                                                            | 175             |          |      |                   |

| V <sub>PR</sub>       | Input to Output Test Voltage, Method b,  V <sub>IORM</sub> x 1.875 = V <sub>PR</sub> , 100% Production Test with tm = 1 sec., Partial Discharge < 5pC | 2651            |          |      |                   |

|                       | Input to Output Test Voltage, Method a, V <sub>IORM</sub> x 1.5 = V <sub>PR</sub> , Type and Sample Test with tm = 60 sec.,Partial Discharge < 5 pC   | 2121            |          |      |                   |

| V <sub>IORM</sub>     | Max Working Insulation Voltage                                                                                                                        | 1,414           |          |      | V <sub>peak</sub> |

| V <sub>IOTM</sub>     | Highest Allowable Over Voltage                                                                                                                        | 6000            |          |      | V <sub>peak</sub> |

|                       | External Creepage                                                                                                                                     | 8               |          |      | mm                |

|                       | External Clearance                                                                                                                                    | 7.4             |          |      | mm                |

|                       | External Clearance (for Option T or TS - 0.4" Lead Spacing)                                                                                           | 10.16           |          |      | mm                |

|                       | Insulation Thickness                                                                                                                                  | 0.5             |          |      | mm                |

|                       | Safety Limit Values – Maximum Values Allowed in the Event of a Failure                                                                                |                 |          |      |                   |

| T <sub>Case</sub>     | Case Temperature                                                                                                                                      | 150             |          |      | °C                |

| I <sub>S,INPUT</sub>  | Input Current                                                                                                                                         | 10              |          |      | mA                |

| P <sub>S,OUTPUT</sub> | Output Power (Duty Factor ≤ 2.7%)                                                                                                                     | 150             |          |      | mW                |

| R <sub>IO</sub>       | Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500V                                                                                      | 10 <sup>9</sup> |          |      | Ω                 |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C unless otherwise specified)

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol              | Parameter                                                  | Value          | Units |

|---------------------|------------------------------------------------------------|----------------|-------|

| T <sub>STG</sub>    | Storage Temperature                                        | -40 to +125    | °C    |

| T <sub>OPR</sub>    | Operating Temperature                                      | -40 to +85     | °C    |

| T <sub>SOL</sub>    | Lead Solder Temperature (1.6mm below seating plane)        | 260 for 10 sec | °C    |

| EMITTER             |                                                            |                |       |

| I <sub>F (PK)</sub> | Peak Transient Input Current (≤1µs PW, 300pps)             | 1.0            | А     |

| I <sub>F</sub>      | Average Forward Input Current                              | 10             | mA    |

| V <sub>R</sub>      | Reverse Input Voltage                                      | 5.0            | V     |

| P <sub>D</sub>      | Output Power Dissipation (No derating required up to 85°C) | 45             | mW    |

| DETECTOR            |                                                            |                |       |

| V <sub>CC</sub>     | Supply Voltage                                             | 0 to 20        | V     |

| Io                  | Average Output Current                                     | 25             | mA    |

| VE                  | Three State Enable Voltage                                 | -0.5 to 20     | V     |

| Vo                  | Output Voltage                                             | -0.5 to 20     | V     |

| $P_{D}$             | Output Power Dissipation (No derating required up to 85°C) | 150            | mW    |

#### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol              | Parameter                  | Min. | Max. | Units |

|---------------------|----------------------------|------|------|-------|

| I <sub>F(ON)</sub>  | Forward Input Current      | 1.6* | 5    | mA    |

| I <sub>F(OFF)</sub> | Forward Input Current      |      | 0.1  | mA    |

| V <sub>CC</sub>     | Supply Voltage, Output     | 4.5  | 20   | V     |

| V <sub>EL</sub>     | Enable Voltage, LOW Level  | 0    | 0.8  | V     |

| V <sub>EH</sub>     | Enable Voltage, HIGH Level | 2.0  | 20   | V     |

| T <sub>A</sub>      | Operating Temperature      | 0    | +85  | °C    |

| N                   | Fan Out (TTL Load)         |      | 4    |       |

<sup>\*</sup>The initial switching threshold is 1.6mA or less. It is recommended that 2.2mA be used to permit at least a 20% CTR degradation guardband.

**Electrical Characteristics** ( $T_A = 0$ °C to +85°C,  $V_{CC} = 4.5$ V to 20V,  $I_{F(ON)} = 1.6$ mA to 5mA,  $V_{EH} = 2$ V to 20V,  $V_{EL} = 0$ V to 0.8V,  $I_{F(OFF)} = 0$  mA to 0.1mA unless otherwise specified.)<sup>(1)</sup>

#### **Individual Component Characteristics**

| Symbol           | Parameter                              | Test Condit                         | ions                  | Min. | Тур.* | Max.  | Unit  |

|------------------|----------------------------------------|-------------------------------------|-----------------------|------|-------|-------|-------|

| EMITTER          |                                        |                                     |                       |      |       |       | 1     |

| V <sub>F</sub>   | Input Forward Voltage                  | I <sub>F</sub> = 5mA                |                       |      |       | 1.75  | V     |

|                  |                                        |                                     | $T_A = 25^{\circ}C$   |      | 1.40  | 1.7   |       |

| B <sub>VR</sub>  | Input Reverse Breakdown<br>Voltage     | I <sub>R</sub> = 10μA               |                       | 5.0  |       |       | V     |

| C <sub>IN</sub>  | Input Capacitance                      | Pins 2 & 3, V <sub>F</sub> = 0, f = | 1MHz                  |      | 60    |       | pF    |

| ΔVF/ΔΤΑ          | Input Diode Temperature<br>Coefficient | I <sub>F</sub> = 5mA                |                       |      | -1.4  |       | mV/°C |

| DETECTO          | DR                                     |                                     |                       |      | '     |       | •     |

| Іссн             | High Level Supply                      | $I_F = 5mA$ , $I_O = Open$ ,        | $V_{CC} = 5.5V$       |      | 3.5   | 4.5   | mA    |

|                  | Current                                | V <sub>E</sub> = Don't Care         | V <sub>CC</sub> = 20V |      | 4.0   | 6.0   |       |

| I <sub>CCL</sub> | Low Level Supply Current               | $I_F = 0$ , $I_O = Open$ ,          | $V_{CC} = 5.5V$       |      | 4.4   | 6.0   | mA    |

|                  |                                        | V <sub>E</sub> = Don't care         | V <sub>CC</sub> = 20V |      | 5.2   | 7.5   |       |

| I <sub>EL</sub>  | Low Level Enable Current               | V <sub>E</sub> = 0.4V               |                       |      | -0.1  | -0.32 | mA    |

| I <sub>EH</sub>  | High Level Enable Current              | V <sub>E</sub> = 2.7V               |                       |      |       | 20    | μΑ    |

|                  |                                        | $V_{E} = 5.5V$                      |                       |      |       | 100   |       |

|                  |                                        | V <sub>E</sub> = 20V                |                       |      | 0.005 | 250   |       |

| V <sub>EH</sub>  | High Level Enable Voltage              |                                     |                       | 2.0  |       |       | V     |

| V <sub>EL</sub>  | Low Level Enable Voltage               |                                     |                       |      |       | 0.8   | V     |

**Switching Characteristics** ( $T_A = 0$ °C to +85°C,  $I_{F(ON)} = 1.6$ mA to 5mA,  $I_{F(OFF)} = 0$  to 0.1mA,  $V_{CC} = 4.5$ V to 20V unless otherwise specified.)

| Symbol             | AC Characteristics                                    | Test Con                                                          | ditions                                             | Min.   | Тур.* | Max. | Unit |

|--------------------|-------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------|--------|-------|------|------|

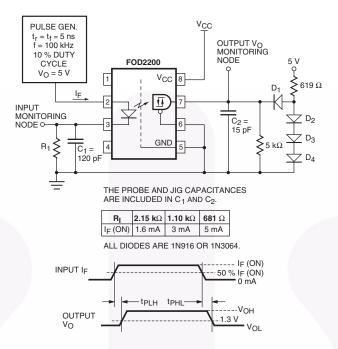

| T <sub>PLH</sub>   | Propagation Delay Time<br>to Output High Level        | With Peaking Capaci                                               | tor <sup>(2)(4)</sup> (Fig. 1)                      |        | 120   | 300  | ns   |

| T <sub>PHL</sub>   | Propagation Delay Time to Output Low Level            | With Peaking Capaci                                               | tor <sup>(3)(4)</sup> (Fig. 1)                      |        | 180   | 300  | ns   |

| t <sub>r</sub>     | Output Rise Time (10% to 90%)                         | <sup>(5)</sup> (Fig. 1)                                           |                                                     |        | 80    |      | ns   |

| t <sub>f</sub>     | Output Fall Time (90% to 10%)                         | <sup>(6)</sup> (Fig. 1)                                           |                                                     |        | 25    |      | ns   |

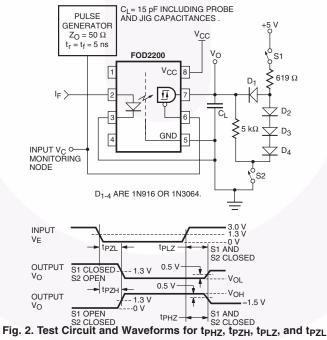

| t <sub>PZH</sub>   | Enable Propagation Delay Time to Output High Level    | (Fig. 2)                                                          |                                                     |        | 40    |      | ns   |

| t <sub>PZL</sub>   | Enable Propagation Delay Time to Output Low Level     | (Fig. 2)                                                          |                                                     |        | 50    |      | ns   |

| T <sub>PHZ</sub>   | Disable Propagation Delay Time from Output High Level | (Fig. 2)                                                          |                                                     |        | 95    |      | ns   |

| T <sub>PLZ</sub>   | Disable Propagation Delay Time from Output Low Level  | (Fig. 2)                                                          |                                                     |        | 80    | 1    | ns   |

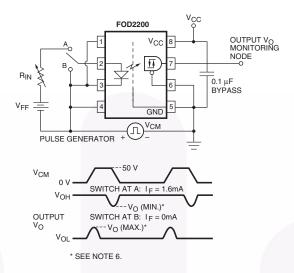

| ICM <sub>H</sub> I | Common Mode Transient Immunity (at Output High Level) | T <sub>A</sub> =25°C,<br>V <sub>OH</sub> (Min.) = 2.0V,           | I <sub>F</sub> = 1.6mA,<br> V <sub>CM</sub>   = 50V | 1,000  |       |      | V/µs |

|                    |                                                       | $V_{CC} = 5V^{(7)}$ (Fig. 3)                                      | $I_F = 5mA,$<br>$ V_{CM}  = 1,000V$                 | 10,000 |       |      |      |

| ICM <sub>L</sub> I | Common Mode                                           | $T_A = 25$ °C, $I_F = 0$ mA                                       | IV <sub>CM</sub> I = 50V                            | 1,000  | _     |      | V/µs |

|                    | Transient Immunity (at Output Low Level)              | $V_{OL}$ (Max.) = 0.8 V,<br>$V_{CC}$ = 5V <sup>(8)</sup> (Fig. 3) | IV <sub>CM</sub>   = 1,000V                         | 10,000 |       |      |      |

<sup>\*</sup>Typical values at  $T_A$  = 25°C,  $V_{CC}$  = 5V,  $I_{F(ON)}$  = 3mA unless otherwise specified.

#### **Electrical Characteristics** (Continued)

**Transfer Characteristics** ( $T_A = 0$ °C to +85°C,  $V_{CC} = 4.5V$  to 20V,  $I_{F(ON)} = 1.6$ mA to 5mA,  $V_{EH} = 2V$  to 20V,  $V_{EL} = 0V$  to 0.8V,  $I_{F(OFF)} = 0$ mA to 0.1mA unless otherwise specified.)<sup>(1)</sup>

| Symbol           | DC Characteristics                  | Test Condition                                                            | ons                      | Min. | Тур.*                 | Max. | Unit |

|------------------|-------------------------------------|---------------------------------------------------------------------------|--------------------------|------|-----------------------|------|------|

| I <sub>OHH</sub> | Output Leakage Current              | $V_{CC} = 4.5V, I_F = 5mA$                                                | $V_{O} = 5.5V$           |      | 2.0                   | 100  | μΑ   |

|                  | $(V_{OUT} > V_{CC})$                |                                                                           | V <sub>O</sub> = 20V     |      | 2.5                   | 500  |      |

| V <sub>OL</sub>  | Low Level Output Voltage            | $V_{CC} = 4.5 \text{ V}, I_F = 0 \text{mA}, V_{OL} = 6.4 \text{mA}^{(2)}$ | $V_{\rm E} = 0.4  \rm V$ |      | 0.33                  | 0.5  | V    |

| I <sub>FT</sub>  | Input Threshold Current             | $V_{CC} = 4.5V, V_{O} = 0.5V, V_{OL} = 6.4mA$                             | $V_E = 0.4V$ ,           |      |                       | 1.6  | mA   |

| V <sub>OH</sub>  | Logic High Output Voltage           | I <sub>OH</sub> = -2.6mA                                                  |                          | 2.4  | V <sub>CC</sub> – 1.8 |      | V    |

| l <sub>OZL</sub> | High Impedance State Output Current | $V_{O} = 0.4V, V_{EN} = 2V, I_{F}$                                        | = 5mA                    |      |                       | -20  | μΑ   |

| I <sub>OZH</sub> | High Impedance State                | $V_{O} = 2.4 \text{ V}, V_{EN} = 2 \text{ V}, I_{F}$                      | = 5mA                    |      |                       | 20   | μΑ   |

|                  | Output Current                      | $V_{O} = 5.5 \text{ V}, V_{EN} = 2 \text{ V}, I_{F}$                      | = 5mA                    |      |                       | 100  |      |

|                  |                                     | $V_{O} = 20 \text{ V}, V_{EN} = 2 \text{ V}, I_{F}$                       | = 5mA                    |      |                       | 500  |      |

| I <sub>OSL</sub> | Logic Low Short Circuit             | $V_{O} = V_{CC} = 5.5V, I_{F} = 00$                                       | mA                       | 25   |                       | \    | mA   |

|                  | Output Current <sup>(10)</sup>      | $V_{O} = V_{CC} = 20V, I_{F} = 0n$                                        | nA                       | 40   |                       |      |      |

| I <sub>OSH</sub> | Logic High Short Circuit            | $V_{CC} = 5.5V, I_F = 5mA, V$                                             | o = GND                  | -10  | \                     |      | mA   |

|                  | Output Current <sup>(10)</sup>      | $V_{CC} = 20V$ , $I_F = 5mA$ , $V_O = GND$                                |                          | -25  |                       |      |      |

| I <sub>HYS</sub> | Input Current Hysteresis            | V <sub>CC</sub> = 4.5V                                                    |                          |      | 0.03                  |      | mA   |

#### **Isolation Characteristics** (T<sub>A</sub> = 0°C to +85°C unless otherwise specified)

| Symbol           | Characteristics                   | Test Conditions                                          | Min. | Тур.*            | Max. | Unit             |

|------------------|-----------------------------------|----------------------------------------------------------|------|------------------|------|------------------|

| V <sub>ISO</sub> | Withstand Insulation Test Voltage | $R_H < 50\%$ , $T_A = 25$ °C, $t = 1 \text{ min.}^{(9)}$ | 5000 |                  |      | V <sub>RMS</sub> |

| R <sub>I-O</sub> | Resistance (Input to Output)      | $V_{I-O} = 500  VDC^{(9)}$                               |      | 10 <sup>12</sup> |      | Ω                |

| C <sub>I-O</sub> | Capacitance (Input to Output)     | $V_{I-O} = 0V, f = 1MHz^{(9)}$                           |      | 0.6              |      | pF               |

<sup>\*</sup>Typical values at  $T_A$  = 25°C,  $V_{CC}$  = 5V,  $I_{F(ON)}$  = 3mA unless otherwise stated.

#### Notes:

- The V<sub>CC</sub> supply to each optoisolator must be bypassed by a 0.1µF capacitor or larger. This can be either a ceramic

or solid tantalum capacitor with good high frequency characteristic and should be connected as close as possible

to the package V<sub>CC</sub> and GND pins of each device.

- t<sub>PLH</sub> Propagation delay is measured from the 50% level on the LOW to HIGH transition of the input current pulse

to the 1.3V level on the LOW to HIGH transition of the output voltage pulse.

- 3. t<sub>PHL</sub> Propagation delay is measured from the 50% level on the HIGH to LOW transition of the input current pulse to the 1.3V level on the HIGH to LOW transition of the output voltage pulse.

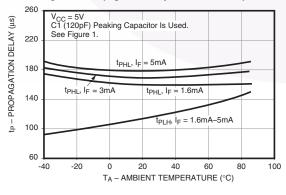

- 4. When the peaking capacitor is omitted, propagation delay times may increase by 100ns.

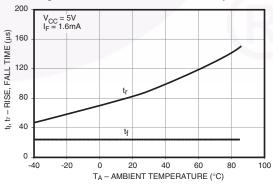

- 5.  $t_r$  Rise time is measured from the 10% to the 90% levels on the LOW to HIGH transition of the output pulse.

- 6.  $t_f$  Fall time is measured from the 90% to the 10% levels on the HIGH to LOW transition of the output pulse.

- CM<sub>H</sub> The maximum tolerable rate of fall of the common mode voltage to ensure the output will remain in the high state (i.e., V<sub>OLIT</sub> > 2.0V).

- 8.  $CM_L$  The maximum tolerable rate of rise of the common mode voltage to ensure the output will remain in the low state (i.e.,  $V_{OUT} < 0.8V$ ).

- 9. Device considered a two-terminal device: Pins 1, 2, 3 and 4 shorted together, and Pins 5, 6, 7 and 8 shorted together.

- 10. Duration of output short circuit time should not exceed 10ms.

#### **Test Circuits**

Fig. 1. Test Circuit and Waveforms for  $t_{\text{PLH}},\,t_{\text{PHL}},\,t_{\text{r}}$  and  $t_{\text{f}}$

#### Test Circuits (Continued)

Fig. 3. Test Circuit and Typical Waveforms for Common Mode Transient Immunity

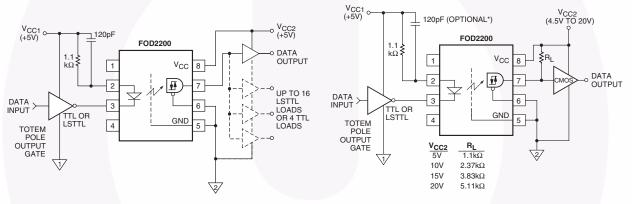

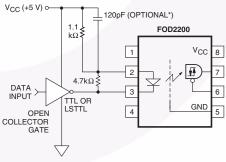

Figure 4. Recommended LSTTL to LSTTL Circuit

Figure 5. LSTTL to CMOS Interface Circuit

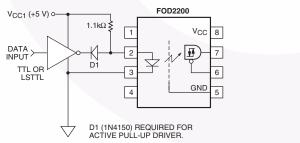

Figure 6. Recommended LED Drive Circuit

Figure 7. Series LED Drive with Open Collector Gate (4.7k $\Omega$  Resistor Shunts IOH from the LED)

<sup>\*</sup>The 120pF capacitor may be omitted in applications where 500ns propagation delay is sufficient.

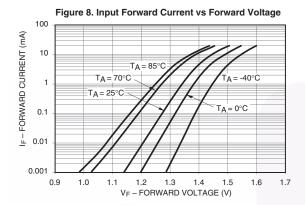

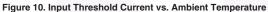

#### **Typical Performance Curves**

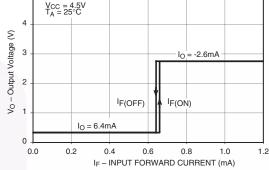

$V_{CC} = 4.5V$  $T_A = 25^{\circ}C$

Figure 9. Output Voltage vs. Input Forward Current

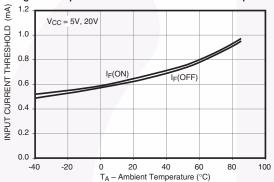

Figure 11. Logic Low Output Voltage vs. Ambient Temperature

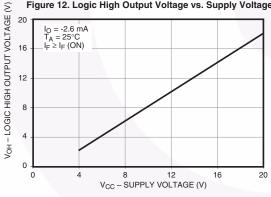

Figure 12. Logic High Output Voltage vs. Supply Voltage

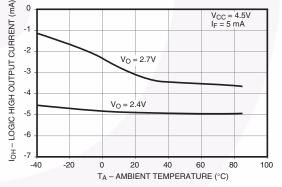

Figure 13. Logic High Output Current vs. Ambient Temperature

Figure 14. Propagation Delay vs Ambient Temperature

Figure 15. Rise, Fall Time vs Ambient Temperature

#### **Package Dimensions**

#### **Through Hole**

#### 0.4" Lead Spacing (Option T)

#### Surface Mount - 0.3" Lead Spacing (Option S)

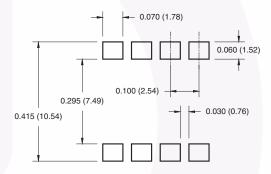

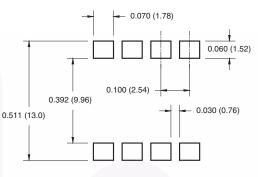

## 8-Pin Surface Mount DIP – Land Pattern (Option S)

All dimensions are in inches (millimeters)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>

#### Package Dimensions (Continued)

#### **Surface Mount – 0.4" Lead Spacing (Option TS)**

## 8-Pin Surface Mount DIP – Land Pattern (Option TS)

#### Note:

All dimensions are in inches (millimeters)

0.100 (2.54) TYP

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>

0.497 (12.6) MAX.

## **Ordering Information**

| Part Number  | Package                                           | Packing Method                       |

|--------------|---------------------------------------------------|--------------------------------------|

| FOD2200      | DIP 8-Pin                                         | Tube (50 units per tube)             |

| FOD2200S     | SMT 8-Pin (Lead Bend)                             | Tube (50 units per tube)             |

| FOD2200SD    | SMT 8-Pin (Lead Bend)                             | Tape and Reel (1,000 units per reel) |

| FOD2200V     | DIP 8-Pin, IEC60747-5-2 option                    | Tube (50 units per tube)             |

| FOD2200SV    | SMT 8-Pin (Lead Bend), IEC60747-5-2 option        | Tube (50 units per tube)             |

| FOD2200SDV   | SMT 8-Pin (Lead Bend), IEC60747-5-2 option        | Tape and Reel (1,000 units per reel) |

| FOD2200TV    | DIP 8-Pin, 0.4" Lead Spacing, IEC60747-5-2 option | Tube (50 units per tube)             |

| FOD2200TSV   | SMT 8-Pin, 0.4" Lead Spacing, IEC60747-5-2 option | Tube (50 units per tube)             |

| FOD2200TSR2V | SMT 8-Pin, 0.4" Lead Spacing, IEC60747-5-2 option | Tape and Reel (700 units per reel)   |

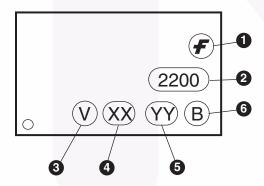

## **Marking Information**

| Defini | Definitions                                                                                 |  |  |  |  |

|--------|---------------------------------------------------------------------------------------------|--|--|--|--|

| 1      | Fairchild logo                                                                              |  |  |  |  |

| 2      | Device number                                                                               |  |  |  |  |

| 3      | IEC60747-5-2 Option (only appears on component ordered with this option) (Pending approval) |  |  |  |  |

| 4      | Two digit year code, e.g., '08'                                                             |  |  |  |  |

| 5      | Two digit work week ranging from '01' to '53'                                               |  |  |  |  |

| 6      | Assembly package code                                                                       |  |  |  |  |

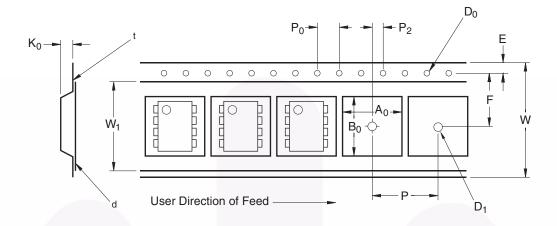

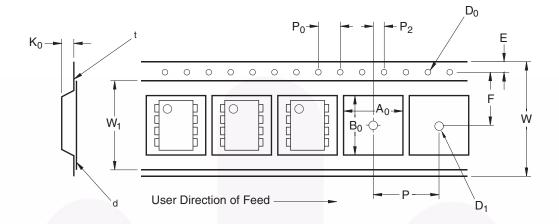

## **Carrier Tape Specifications (Option SD)**

| Symbol         | Description                     | Dimension in mm |

|----------------|---------------------------------|-----------------|

| W              | Tape Width                      | 16.0 ± 0.3      |

| t              | Tape Thickness                  | 0.30 ± 0.05     |

| P <sub>0</sub> | Sprocket Hole Pitch             | 4.0 ± 0.1       |

| D <sub>0</sub> | Sprocket Hole Diameter          | 1.55 ± 0.05     |

| E              | Sprocket Hole Location          | 1.75 ± 0.10     |

| F              | Pocket Location                 | 7.5 ± 0.1       |

| P <sub>2</sub> |                                 | 2.0 ± 0.1       |

| Р              | Pocket Pitch                    | 12.0 ± 0.1      |

| A <sub>0</sub> | Pocket Dimensions               | 10.30 ±0.20     |

| B <sub>0</sub> |                                 | 10.30 ±0.20     |

| K <sub>0</sub> |                                 | 4.90 ±0.20      |

| W <sub>1</sub> | Cover Tape Width                | 13.2 ± 0.2      |

| d              | Cover Tape Thickness            | 0.1 max         |

|                | Max. Component Rotation or Tilt | 10°             |

| R              | Min. Bending Radius             | 30              |

## **Carrier Tape Specifications (Option TSR2V)**

| Symbol         | Description                     | Dimension in mm |

|----------------|---------------------------------|-----------------|

| W              | Tape Width                      | 24.0 ± 0.3      |

| t              | Tape Thickness                  | 0.40 ± 0.1      |

| P <sub>0</sub> | Sprocket Hole Pitch             | 4.0 ± 0.1       |

| D <sub>0</sub> | Sprocket Hole Diameter          | 1.55 ± 0.05     |

| Е              | Sprocket Hole Location          | 1.75 ± 0.10     |

| F              | Pocket Location                 | 11.5 ± 0.1      |

| P <sub>2</sub> |                                 | 2.0 ± 0.1       |

| Р              | Pocket Pitch                    | 16.0 ± 0.1      |

| A <sub>0</sub> | Pocket Dimensions               | 12.80 ± 0.1     |

| B <sub>0</sub> |                                 | 10.35 ± 0.1     |

| K <sub>0</sub> |                                 | 5.7 ±0.1        |

| W <sub>1</sub> | Cover Tape Width                | 21.0 ± 0.1      |

| d              | Cover Tape Thickness            | 0.1 max         |

|                | Max. Component Rotation or Tilt | 10°             |

| R              | Min. Bending Radius             | 30              |

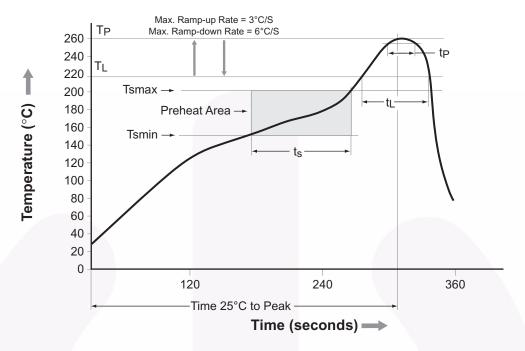

#### **Reflow Profile**

| Profile Freature                                          | Pb-Free Assembly Profile |  |

|-----------------------------------------------------------|--------------------------|--|

| Temperature Min. (Tsmin)                                  | 150°C                    |  |

| Temperature Max. (Tsmax)                                  | 200°C                    |  |

| Time (t <sub>S</sub> ) from (Tsmin to Tsmax)              | 60-120 seconds           |  |

| Ramp-up Rate (t <sub>L</sub> to t <sub>P</sub> )          | 3°C/second max.          |  |

| Liquidous Temperature (T <sub>L</sub> )                   | 217°C                    |  |

| Time (t <sub>L</sub> ) Maintained Above (T <sub>L</sub> ) | 60-150 seconds           |  |

| Peak Body Package Temperature                             | 260°C +0°C / -5°C        |  |

| Time (t <sub>P</sub> ) within 5°C of 260°C                | 30 seconds               |  |

| Ramp-down Rate (T <sub>P</sub> to T <sub>L</sub> )        | 6°C/second max.          |  |

| Time 25°C to Peak Temperature                             | 8 minutes max.           |  |

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its gbbal subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ FRFFT<sup>®</sup> Auto-SPM™

Global Power Resource SM Build it Now™ CorePLUS™ Green FPS™

Green FPS™ e-Series™ CorePOWER™

CROSSVOLT™ Gmax™ CTI TM GTO™

IntelliMAX™ Current Transfer Logic™ **DEUXPEED**® ISOPLANAR™ Dual Cool™ MegaBuck™ EcoSPARK<sup>®</sup> MICROCOUPLER™ EfficientMax™ MicroFET™ MicroPak™ ESBC™

MicroPak2™ MillerDrive™ Fairchild® MotionMax™ Fairchild Semiconductor® Motion-SPM™ FACT Quiet Series™ OptoHiT™ FACT OPTOLOGIC® FAST®

FastvCore™ FETBench™ FlashWriter®\*

PDP SPM™

Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™

OFFT QS<sup>TM</sup> Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™ SPM® STEALTH™ SuperFET™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8

SupreMOS® SyncFET™ Sync-Lock™

SYSTEM ®\* The Power Franchise® wer franchise TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ TriFault Detect™ TRUECURRENT™\* ' SerDes™

LIHC Ultra FRFET™ UniFET™ **VCX™** VisualMax™ XS™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

**OPTOPLANAR®**

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Definition of Terms         |                       |                                                                                                                                                                                                     |

|-----------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet<br>Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information         | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary                 | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed    | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                    | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 149