Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Freedom FRDM-K66F Development Platform User's Guide

#### 1. Introduction

The NXP Freedom development platform is a set of software and hardware tools for evaluation and development. It is ideal for rapid prototyping of microcontroller-based applications. The NXP Freedom K66F hardware, FRDM-K66F, is a simple, yet sophisticated design featuring a Kinetis K series microcontroller, built on the ARM© Cortex®-M4 core.

FRDM-K66F can be used to evaluate the K66 and K26 Kinetis K series devices. It features a MK66FN2M0VMD18, which boast a maximum operation frequency of 180MHz, 2MB of flash, 256KB RAM, a high-speed USB controller, Ethernet controller, Secure Digital Host controller, and loads of analog and digital peripherals. The FRDM-K66F hardware is formfactor compatible with the ArduinoTM R3 pin layout, providing a broad range of expansion board options. The onboard interface includes a digital accelerometer & magnetometer, gyroscope, audio codec, digital MEMS mic, tricolor LED, SDHC, Bluetooth Add-on module, RF Add-on module (for use over SPI), and Ethernet.

The FRDM-K66F platform features OpenSDAv2.1, the NXP open-source hardware embedded serial and debug adapter running an open-source bootloader. This circuit offers several options for serial communication, flash programming and run-control debugging. The openSDAv2.1 is loaded with JLink firmware for rapid

#### **Contents**

| 1. Introduction                             | 1  |

|---------------------------------------------|----|

| 2. FRDM-K66F Hardware Overview              |    |

| 3. FRDM-K66F Hardware Description           |    |

| 3.1. Power supply                           |    |

| 3.2. Series and debug adapter (OpenSDAv2.1) |    |

| 4. Microcontroller                          | 7  |

| 5. Clocking                                 |    |

| 6. Universal Serial Bus (USB)               |    |

| 7. Secure Digital Card                      |    |

| 8. Ethernet                                 |    |

| 9. Accelerometer and Magnetometer           |    |

| 10. Gyroscope                               |    |

| 11. RGB LED                                 |    |

| 12. Serial Port                             | 16 |

| 13. Reset                                   | 16 |

| 14. Push Button Switches                    | 16 |

| 15. Debug                                   | 17 |

| 16. Audio                                   |    |

| 16.1. Audio codec                           | 17 |

| 16.2. Digital MEMS microphone               | 18 |

| 16.3. I/O connectors                        | 19 |

| 17. Add-on Modules                          | 21 |

| 17.1. RF module                             | 21 |

| 17.2. Bluetooth module                      | 22 |

| 18. Input/Output connectors                 | 22 |

| 19. Arduino Compatibility                   |    |

| 20. Miscellaneous                           | 23 |

| 21. References                              | 23 |

| 22. Revision History                        | 24 |

prototyping and product development, with a focus on connected Internet of Things devices.

#### 2. FRDM-K66F Hardware Overview

The features of the FRDM-K66F hardware are as follows:

- MK66FN2M0VMD18 MCU (180 MHz, 2MB Flash, 256KB RAM, 144MBGA package)

- Dual role High-speed USB interface with micro-B USB connector

- RGB LED

- FXOS8700CQ Accelerometer and Magnetometer

- FXAS21002 Gyroscope

- Two user push buttons

- Flexible power supply options OpenSDAv2.1 USB, K66F USB, and external sources

- Easy access to MCU I/O via Arduino R3TM compatible I/O connectors

- Programmable OpenSDAv2.1 debug interface with multiple applications available including:

- SWD debug interface over a USB HID connection providing run-control debugging and compatibility with IDE tools

- Virtual serial port interface

- Ethernet

- Micro SD

2

- Audio features

- Digital MEMS microphone

- Auxiliary input jack

- Headset/Analog microphone jack

- Two optional input for analogue microphone

- Optional header for add-on RF module: RF24L01+ Nordic 2.4 GHz Radio

- Optional header for add-on Bluetooth module: JY-MCU BT Board V1.05 BT

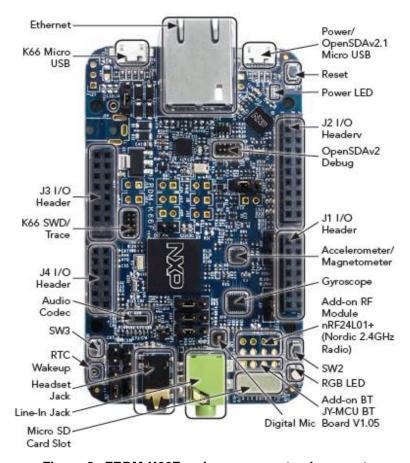

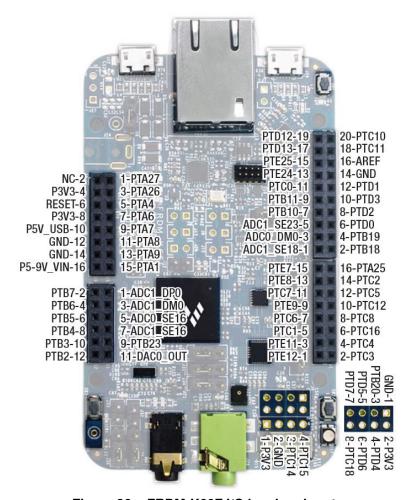

*Figure 1* shows a block diagram of the FRDM-K66F design. *Figure 2* explains the primary components and their placement on the hardware assembly.

#### Headers for Arduino R3 + FSL I2S Extension User Dig MEMS Jumpers select mic outputs to MCU or to codec **LEDs** Mic RMII Enet **RJ-45** PDM Data / Clk PHY HS USB OTG Micro-AB USB 3.5mm TRRS SWD, RESET B Headphone / Mic K66 K20 I2C Micro-B USB MIC / GND Input PK20KX128VFMS between Ring 2 / Sleeve 2MB / 256KB / 180 MHz 128 Mic JTAG / SWD OpenSDA MIC Dig SWD/ Trace Analog SDHC MIC Standard SD Mic Dialog DA7212 Card Slot CODEC MIC Analog Mic I2C Accel/Mag Gyro FXOS8700CQ FXAS21002 AUX in 3.5mm Line-in External Interface Freescale External Memory Device Connector Circuits

Figure 1. FRDM-K66F block diagram

Figure 2. FRDM-K66F main components placement

## 3. FRDM-K66F Hardware Description

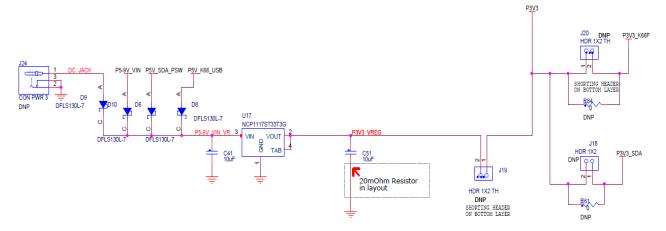

## 3.1. Power supply

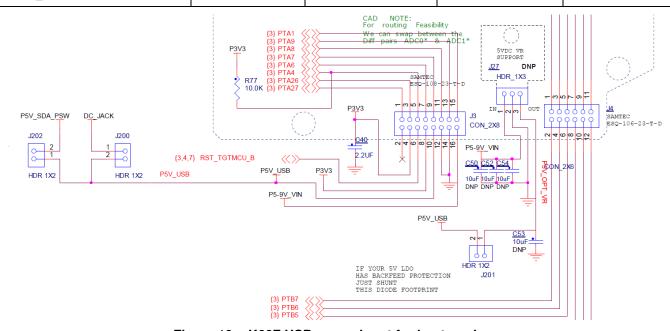

There are multiple power supply options on the FRDM-K66F. It can be powered from either of the USB connectors, the  $V_{\rm IN}$  pin on the J3 I/O header, DC Jack (Not populated), or an off-board 1.71-3.6 V supply from the 3.3 V pin on the J20 header. The USB, DC Jack, and  $V_{\rm IN}$  supplies are regulated onboard using a 3.3 V linear regulator to produce the main power supply. The 3.3 V Header (J20) is not regulated onboard. *Table 1* provides the operational details and requirements for the power supplies.

| Table 1. Thom-Root power requirements |             |                          |                    |

|---------------------------------------|-------------|--------------------------|--------------------|

| Supply Source                         | Valid Range | OpenSDAv2.1 Operational? | Regulated onboard? |

| OpenSDAv2.1 USB                       | 5V          | Yes                      | Yes                |

| K66F USB                              | 5V          | No                       | Yes                |

| V <sub>IN</sub> Pin                   | 5V – 9V     | No                       | Yes                |

| 3.3V Header (J20)                     | 1.71 – 3.6V | No                       | No                 |

| DC Jack (Not Populated)               | 5V          | No                       | No                 |

Table 1. FRDM-K66F power requirements

Freedom FRDM-K66F Development Platform User's Guide, User's Guide, Rev. 0, 02/2016

#### NOTE

The OpenSDAv2.1 circuit is only operational when a USB cable is connected and supplying power to OpenSDAv2.1 USB. However, protection circuitry is in place to allow multiple sources to be powered at once.

Figure 3. Power supply schematic

| Table 2. F | FRDM-K66F | power | supplies |

|------------|-----------|-------|----------|

|------------|-----------|-------|----------|

| Power supply name | Description                                                                                                |

|-------------------|------------------------------------------------------------------------------------------------------------|

| P5-9V_VIN         | Power supplied from the V <sub>IN</sub> pin of the I/O headers (J3 pin 16). A Schottky diode provides back |

|                   | drive protection <sup>1</sup> .                                                                            |

| P5V_SDA_PSW       | Power supplied from the <b>OpenSDA USB</b> connector. A Schottky diode provides back drive protection      |

| P5V_K66_USB       | Power supplied from the <b>K66F USB</b> connector. A Schottky diode provides back drive protection         |

| DC_JACK           | Power supplied from the <b>DC Jack</b> (Not populated) connector. A Schottky diode provides back drive     |

|                   | protection. (Note: Must use 5V supply)                                                                     |

| P3V3_VREG         | Regulated 3.3V supply. Sources power to the P3V3 supply rail through a back drive protection               |

|                   | Schottky diode <sup>2</sup> .                                                                              |

| P3V3_K66          | K66F MCU supply. Header J20 provides a convenient means for energy consumption                             |

|                   | measurements <sup>3</sup> .                                                                                |

| P3V3_SDA          | OpenSDA circuit supply. Header J18 provides a convenient means for energy consumption                      |

|                   | measurements <sup>2</sup> .                                                                                |

| P5V_USB           | Nominal 5V supplied to the I/O headers (J3 pin 10)                                                         |

- A 5 VDC regulator is required at J27 when USB Host mode is used. The USB host mode requires a 5 V supply to USB device.

- By default the linear regulator, U17, is a 3.3 V output regulator. This is common footprint that would allow the user to

modify the assembly to utilize an alternative device such as 1.8V. The K66F microcontroller has an operating range of

1.71 V to 3.6 V.

- 3. J18 and J20 are not populated by default. P3V3\_K66 rail is connected by shorting trace at bottom layer of J20. To measure the energy consumption of the K66F MCU, the trace between J20 pins 1 and 2 must first be cut. A current probe or shunt resistor and voltage meter can then be applied to measure the energy consumption on these rails.

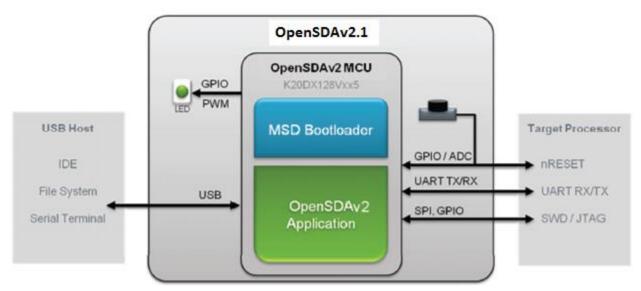

## 3.2. Series and debug adapter (OpenSDAv2.1)

OpenSDAv2.1 is a serial and debug adapter circuit which includes an open-source hardware design, and open-source bootloader, and debug interface software. It bridges serial and debug communications between a USB host and an embedded target processor as shown in *Figure 4*. The hardware circuit is

#### FRDM-K66F Hardware Description

based on a NXP Kinetis K20 family microcontroller (MCU) with 128 KB of embedded flash and an integrated USB controller. OpenSDAv2.1 comes preloaded with the CMSIS-DAP bootloader—an open-source mass storage device (MSD) bootloader, and the JLink interface firmware, which provides a virtual serial port interface, and a JLink debug protocol interface. For more information on the OpenSDAv2.1 software, see mbed.org and <a href="https://github.com/mbedmicro/CMSIS-DAP">https://github.com/mbedmicro/CMSIS-DAP</a> and <a href="https://www.segger.com/opensda.html">https://www.segger.com/opensda.html</a>.

Figure 4. OpenSDA high-level block diagram

OpenSDAv2.1 is managed by a Kinetis K20 MCU built on the ARM® Cortex™-M4 core. The OpenSDA circuit includes a status LED (D2) and a pushbutton (SW1). The pushbutton asserts the Reset signal to the K66F target MCU. It can also be used to place the OpenSDAv2.1 into Bootloader mode. SPI and GPIO signals provide an interface to either the SWD debug port of the K20. Additionally, signal connections are available to implement a UART serial channel. The OpenSDA circuit receives power when the USB connector J26 is plugged into a USB host.

#### **Debug Interface**

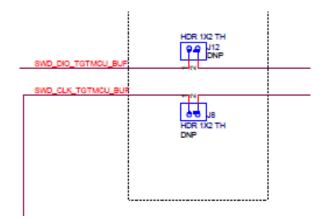

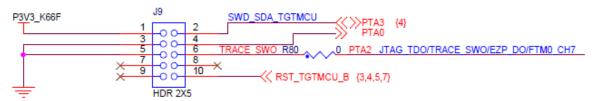

Signals with SPI and GPIO capability are used to connect directly to the SWD of the K66F. These signals are also brought out to a standard 10-pin (0.05") Cortex Debug connector (J9). It is possible to isolate the K66F MCU from the OpenSDAv2.1 circuit and use J9 to connect to an off-board MCU. To accomplish this, cut the trace on the bottom side of the PCB that connects pin 1 & 2 of J8 and pin 1 & 2 of J12. These will disconnect the SWD\_CLK & SWD\_DIO pins to the K66F so that it will not interfere with the communications to an off-board MCU connected to J9 when OpenSDA circuit is powered.

Figure 5. SWD signals isolation

#### SWD CONNECTOR

Figure 6. SWD connector

J9 is populated by default. A mating cable, such as a Samtec FFSD IDC cable, can then be used to connect from the OpenSDAv2.1 of the FRDM-K66F to an off-board SWD connector.

#### **Virtual Serial Port**

A serial port connection is available between the OpenSDAv2.1 MCU and pins PTB16 and PTB17 of the K66F.

## 4. Microcontroller

The FRDM-K66F features the MK66FN2M0VMD18 MCU. This 180 MHz microcontroller is part of the Kinetis K6x family and is implemented in a 144 MBGA package. The following table notes some of the features of the MK66FN2M0VMD18 MCU.

Table 3. Features of MK66FN2M0VMD18

| Feature         | Description                                                                                                                                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ultra low power | 11 low-power modes with power and clock gating for optimal peripheral activity and recovery times                                                          |

|                 | Full memory and analog operation down to 1.71V for extended battery life                                                                                   |

|                 | Low-leakage wake-up unit with up to six internal modules and sixteen pins as wake-up sources in low-leakage stop (LLS)/very low-leakage stop (VLLSx) modes |

|                 | Low-power timer for continual system operation in reduced power states                                                                                     |

Table 3. Features of MK66FN2M0VMD18

| Feature            | Description                                                                                                                                                                       |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash and SRAM     | <ul> <li>2048-KB flash featuring fast access times, high reliability, and four levels of security<br/>protection</li> </ul>                                                       |

|                    | 256 KB of SRAM                                                                                                                                                                    |

|                    | <ul> <li>No user or system intervention to complete programming and erase functions and full<br/>operation down to 1.71 V</li> </ul>                                              |

|                    | Flash access control                                                                                                                                                              |

| Mixed-signal       | High-speed 16-bit ADC with configurable resolution                                                                                                                                |

| capability         | Single or differential output modes for improved noise rejection                                                                                                                  |

|                    | 500-ns conversion time achievable with programmable delay block triggering                                                                                                        |

|                    | Three high-speed comparators providing fast and accurate motor overcurrent                                                                                                        |

|                    | protection by driving PWMs to a safe state                                                                                                                                        |

|                    | Optional analog voltage reference provides an accurate reference to analog blocks                                                                                                 |

|                    | Two 12-bit DACs                                                                                                                                                                   |

| Performance        | 180-MHz ARM Cortex-M4 core with DSP instruction set, single cycle MAC, and single instruction multiple data (SIMD) extensions                                                     |

|                    | <ul> <li>Up to 32 channels DMA for peripheral and memory servicing with reduced CPU loading and<br/>faster system throughput</li> </ul>                                           |

|                    | Cross bar switch enables concurrent multi-master bus accesses, increasing bus bandwidth                                                                                           |

|                    | <ul> <li>Independent flash banks allowing concurrent code execution and firmware updating with no<br/>performance degradation or complex coding routines</li> </ul>               |

| Timing and Control | Four Flex Timers with a total of 20 channels                                                                                                                                      |

|                    | Hardware dead-time insertion and quadrature decoding for motor control                                                                                                            |

|                    | Carrier modulator timer for infrared waveform generation in remote control applications                                                                                           |

|                    | <ul> <li>Four-channel 32-bit periodic interrupt timer provides time base for RTOS task scheduler or<br/>trigger source for ADC conversion and programmable delay block</li> </ul> |

|                    | One Low power Timer                                                                                                                                                               |

|                    | One independent real time clock                                                                                                                                                   |

| Connectivity and   | High-Speed USB Device/Host                                                                                                                                                        |

| Communications     | Full-Speed USB Device/Host/On-The-Go with device charge detect capability                                                                                                         |

|                    | Optimized charging current/time for portable USB devices, enabling longer battery life                                                                                            |

|                    | <ul> <li>USB low-voltage regulator supplies up to 120 mA off chip at 3.3 volts to power external<br/>components from 5-volt input</li> </ul>                                      |

|                    | Five UARTs:                                                                                                                                                                       |

|                    | <ul> <li>One UART supports RS232 with flow control, RS485, and ISO7816</li> </ul>                                                                                                 |

|                    | <ul> <li>Four UARTs support RS232 with flow control and RS485</li> </ul>                                                                                                          |

|                    | One low-power UART (LPUART)                                                                                                                                                       |

|                    | One Inter-IC Sound (I2S) serial interface for audio system interfacing                                                                                                            |

Table 3. Features of MK66FN2M0VMD18

| Feature                                | Description                                                                                                                                                                                                                                                                                        |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | Three DSPI modules and three I2C modules                                                                                                                                                                                                                                                           |

|                                        | Secured digital host controller (SDHC)                                                                                                                                                                                                                                                             |

|                                        | One FlexCAN module                                                                                                                                                                                                                                                                                 |

|                                        | One Ethernet module with 1588                                                                                                                                                                                                                                                                      |

|                                        | <ul> <li>A multi-function external bus interface (FlexBUS) controller capable of interfacing to slave-<br/>only devices.</li> </ul>                                                                                                                                                                |

| Reliability, Safety<br>and<br>Security | <ul> <li>Hardware Encryption co-processor for secure data transfer and storage. Faster than software<br/>implementations and with minimal CPU loading. Supports a wide variety of algorithms - DES,<br/>3DES, AES, MD5, SHA-1, SHA-256</li> </ul>                                                  |

|                                        | <ul> <li>System security and tamper detection with secure real-time clock (RTC) and independent<br/>battery supply. Secure key storage with internal/external tamper detection for unsecured<br/>flash, temperature, clock, and supply voltage variations and physical attack detection</li> </ul> |

|                                        | <ul> <li>Memory protection unit provides memory protection for all masters on the cross bar switch,<br/>increasing software reliability</li> </ul>                                                                                                                                                 |

|                                        | <ul> <li>Cyclic redundancy check (CRC) engine validates memory contents and communication data,<br/>increasing system reliability</li> </ul>                                                                                                                                                       |

|                                        | <ul> <li>Independently-clocked COP guards against clock skew or code runaway for fail-safe<br/>applications such as the IEC 60730 safety standard for household appliances</li> </ul>                                                                                                              |

|                                        | <ul> <li>External watchdog monitor drives output pin to safe state for external components in the<br/>event that a watchdog timeout occurs</li> </ul>                                                                                                                                              |

|                                        | <ul> <li>Included in NXP's product longevity program, with assured supply for a minimum of 10 years<br/>after launch</li> </ul>                                                                                                                                                                    |

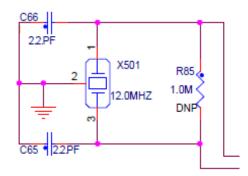

# 5. Clocking

#### **WARNING**

Resonator is NOT recommended when HS USB is used.

The Kinetis MCUs start up from an internal digitally-controlled oscillator (DCO). Software can enable the main external oscillator (EXTAL0/XTAL0) if desired. The external oscillator/resonator can range from 32.768 KHz up to a 50 MHz. The default external source for the MCG input is a 12 MHz crystal. The 12 MHz reference clock is suitable for both audio codec and HS USB features.

Figure 7. 12 MHz crystal clock source for MCU

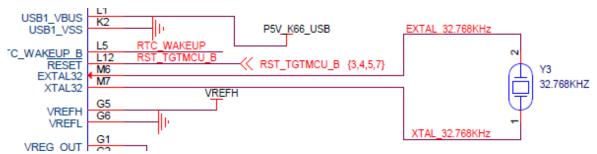

By default, the 32.768 KHz crystal is connected to the RTC oscillator inputs.

Figure 8. 32.768 KHz crystal for RTC

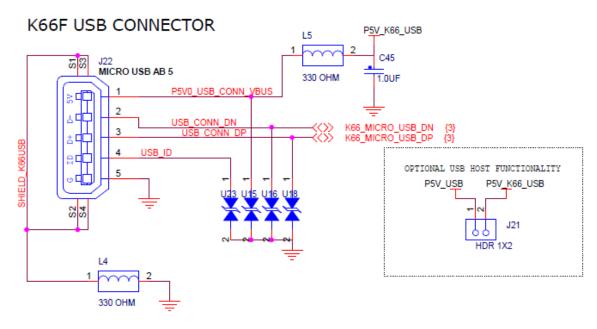

# 6. Universal Serial Bus (USB)

The MK66FN2M0VMD18 features an HS USB with Host/Device capability and built-in transceiver. The FRDM-K66F routes the USB1 D+ and D- signals from the MK66FN2M0VMD18 MCU directly to the onboard micro USB connector (J22).

Figure 9. K66F USB port

When the FRDM-K66F is operating in USB Host mode, a 5 V power must be supplied to VBUS of J22 and J21 must be shunt. The 5 V power can be sourced from either OpenSDAv2.1 USB port (J26), pin 10 of J3 I/O header, 5V DC\_Jack, and P5-9V\_VIN DC-DC converter of J27.

#### **NOTE**

DC\_Jack (J24) and 5 V regulator (J27) are not populated by default. J200 and J201 are not populated by default.

| Tuble 4. COD Host power source tuble |         |       |       |       |

|--------------------------------------|---------|-------|-------|-------|

| Power source                         | Voltage | J202  | J200  | J201  |

| OpenSDAv2.1 USB Port (J26)           | 5V      | Shunt | Off   | Off   |

| DC_Jack (5V only)                    | 5V      | Off   | Shunt | Off   |

| P5-9V_VIN                            | 9V      | Off   | Off   | Shunt |

Table 4. USB host power source table

Figure 10. K66F USB power input for host mode

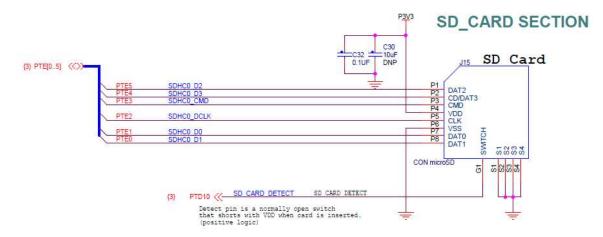

# 7. Secure Digital Card

A micro Secure Digital (SD) card slot is available on the FRDM-K66F connected to the SD Host Controller (SDHC) signals of the MCU. This slot will accept micro format SD memory cards. The SD card detect pin is an open switch that shorts with VDD when card is inserted. *Table 5* shows the SDHC signal connection details.

Figure 11. Micro SD interface

Table 5. Micro SD card socket connection

| Pin   | Function       | FRDM-K66F connection                                                                    |

|-------|----------------|-----------------------------------------------------------------------------------------|

| 1     | DAT2           | PTE5/SPI1_PCS2/UART3_RX/ <b>SDHC0_D2</b> /FTM3_CH0                                      |

| 2     | CD/DAT3        | PTE4/LLWU_P2/SPI1_PCS0/UART3_TX/ <b>SDHC0_D3</b> /TRACE_D0                              |

| 3     | CMD            | PTE3/ADC1_SE7A/SPI1_SIN/UART1_RTS/ <b>SDHC0_CMD</b> /TRACE_D1/SPI1_SOUT                 |

| 4     | VDD            | 3.3 V Board supply (V_BRD)                                                              |

| 5     | CLK            | PTE2/LLWU_P1/ADC1_SE6A/SPI1_SCK/UART1_CTS/ <b>SDHC0_DCLK</b> /TRACE_D2                  |

| 6     | VSS            | Ground                                                                                  |

| 7     | DAT0           | PTE1/LLWU_P0/ADC1_SE5A/SPI1_SOUT/UART1_RX/ <b>SDHC0_D0</b> /TRACE_D3/I2C1_SCL/SPI 1_SIN |

| 8     | DAT1           | PTE0/ADC1_SE4A/SPI1_PCS1/UART1_TX/ <b>SDHC0_D1</b> /TRACE_CLKOUT/I2C1_SDA/RTC_CLKOUT    |

| G1    | SWITCH         | PTD10/LPUART0_RTS/FB_A18                                                                |

| S1-S4 | S1, S2, S3, S4 | Shield Ground                                                                           |

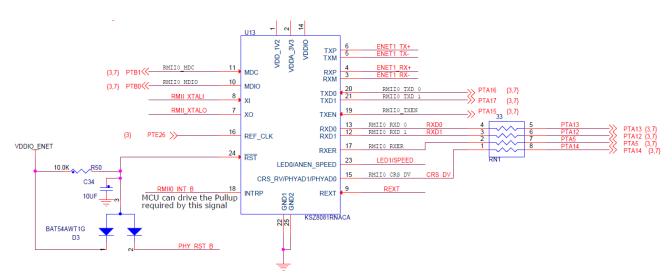

## 8. Ethernet

The MK66FN2M0VMD18 features a 10/100 Mbps Ethernet MAC with MII and RMII interfaces. The FRDM-K66F routes RMII interface signals from the K66F MCU to onboard Micrel 32-pin Ethernet PHY.

When the K66F Ethernet MAC is operating in RMII mode, synchronization of the MCU clock and the 50 MHz RMII transfer clock is important. The MCU input clock must be kept in phase with external PHY. The 32-pin Micrel Ethernet PHY has the ability to provide 50 MHz clock to MK66FN2M0VMD18 MCU PTE26 (ENET\_1588\_CLKIN) and Ethernet PHY itself.

Figure 12. RMII to Ethernet PHY

There is no external pull up on MDIO signal when MK66FN2M0VMD18 is requesting status of the Ethernet link connection. Internal pull is required when enabled in port configuration for MDIO signal.

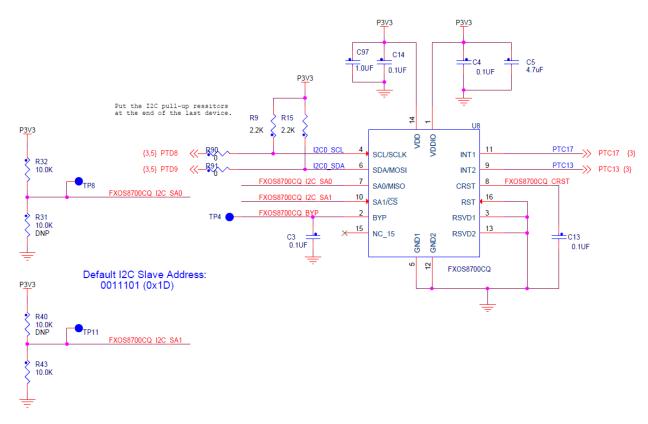

## 9. Accelerometer and Magnetometer

An NXP FXOS8700CQ low-power, 6-axis Xtrinsic sensor combines 14-bit accelerometer and 16-bit magnetometer sensors is interfaced through an  $I^2C$  bus and two GPIO signals, as shown in *Table 6* below. By default, the  $I^2C$  address is 0x1D (SA0 pulled high and SA1 pulled low).

| FXOS8700CQ | K66F Connection                                                                      |

|------------|--------------------------------------------------------------------------------------|

| SCL        | PTD8/LLWU_P24/ <b>I2C0_SCL</b> /LPUART0_RX/FB_A16                                    |

| SDA        | PTD9/ <b>I2C0_SDA</b> /LPUART0_TX/FB_A17                                             |

| INT1       | PTC17/CAN1_TX/UART3_TX/ENET0_1588_TMR1/FB_CS4/FB_TSIZ0/FB_BE31_24_BLS7_0/SDRAM _DQM3 |

| INT2       | PTC13/UART4_CTS/FTM_CLKIN1/FB_AD26/SDRAM_D26/TPM_CLKIN1                              |

Table 6. Accelerometer and magnetometer signals connection

Figure 13. Accelerometer and magnetometer

# 10. Gyroscope

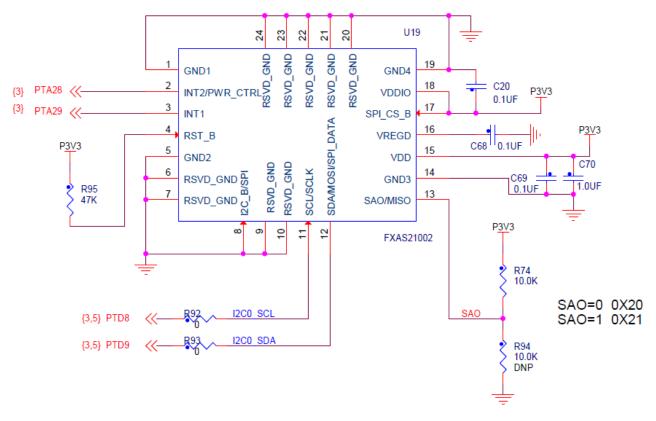

An NXP FXAS21002 low-power, 3-axis gyroscope with 16-bit ADC resolution is interfaced through an I2C bus and two GPIO signals, as shown in *Table 7*. By default, the I2C address is 0x21 (SA0 pulled high). The I2C signals is also shared with FXOS8700CQ sensor.

| FXOS8700CQ | K66F Connection                                   |

|------------|---------------------------------------------------|

| SCL        | PTD8/LLWU_P24/ <b>I2C0_SCL</b> /LPUART0_RX/FB_A16 |

| SDA        | PTD9/ <b>I2C0_SDA</b> /LPUART0_TX/FB_A17          |

| INT1       | PTA29/MII0_COL/FB_A24                             |

| INT2       | PTA28/MII0_TXER/FB_A25                            |

Table 7. Gyroscope signals connection

15

Figure 14. Gyroscope

## 11. RGB LED

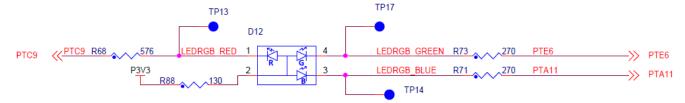

An RGB LED is connected through GPIO. *Table 8* shows the signal connections.

Table 8. LED signal connections

| LED   | K66F Connection                                                         |

|-------|-------------------------------------------------------------------------|

| RED   | PTC9/ADC1_SE5B/CMP0_IN3/FTM3_CH5/I2S0_RX_BCLK/FB_AD6/SDRAM_A14/FTM_FLT0 |

| GREEN | PTE6/LLWU_P16/SPI1_PCS3/UART3_CTS/I2S0_MCLK/FTM3_CH1/USB0_SOF_OUT       |

| BLUE  | PTA11/LLWU_P23/FTM2_CH1/MII0_RXCLK/I2C2_SDA/FTM2_QD_PHB/TPM2_CH1        |

Figure 15. Tri-color LED

## 12. Serial Port

The primary serial port interface signals are PTB16 UART1\_RX and PTB17 UART1\_TX. These signals are connected to the OpenSDAv2.1.

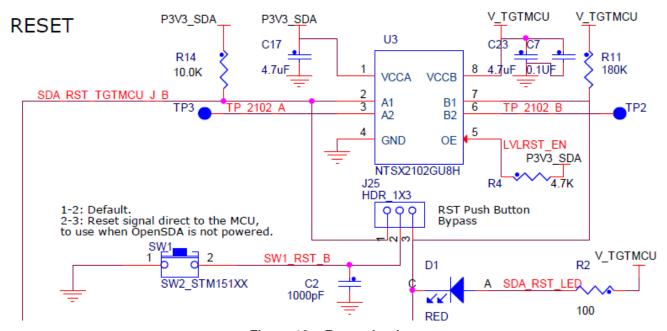

#### 13. Reset

The RESET signal on the K20 is connected externally to a pushbutton, SW1, and also to the OpenSDAv2.1 circuit. The reset button can be used to force an external reset event in the target MCU. The reset button can also be used to force the OpenSDAv2.1 circuit into bootloader mode. For more details, see *Series and debug adapter (OpenSDAv2.1)*.

When using other power source and OpenSDAv2.1 is not powered, J25 2-3 must be shunt for proper reset operation.

Figure 16. Reset circuit

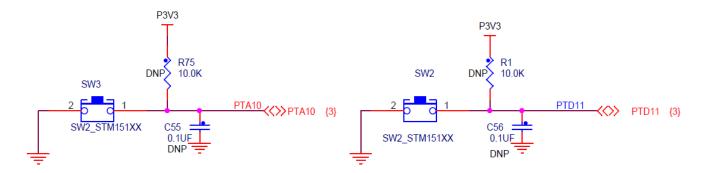

#### 14. Push Button Switches

Two push button switches, SW2 and SW3, are available on the FRDM-K66F board. SW2 is connected to PTD11 and SW3 is connected to PTA10. Beside the general purpose IO function, both SW2 and SW3 can be used as a low-leakage wakeup (LLWU) source.

| Switch | K66F switches connection                                        |  |  |

|--------|-----------------------------------------------------------------|--|--|

| SW2    | PTD11/LLWU_P25/SPI2_PCS0/SDHC0_CLKIN/LPUART0_CTS/FB_A19         |  |  |

| SW3    | PTA10/LLWU_P22/FTM2_CH0/MII0_RXD2/FTM2_QD_PHA/TPM2_CH0/TRACE_D0 |  |  |

Table 9. Push button GPIO function

17

Figure 17. Push button switches

## 15. Debug

The debug interface on MK66FN2M0VMD18 is a Serial Wire Debug (SWD) port with trace output capability. There are two debug interfaces on the FRDM-K66F – an onboard OpenSDAv2.1 circuit (J22) and K66F direct SWD connection (J9) via a 10-pin header. To use an external debugger, such as J-Link on J9, you may need to disconnect the OpenSDAv2.1 SWD circuit from the K66F by cut trace at the bottom of the J8 and J12.

## 16. Audio

#### 16.1. Audio codec

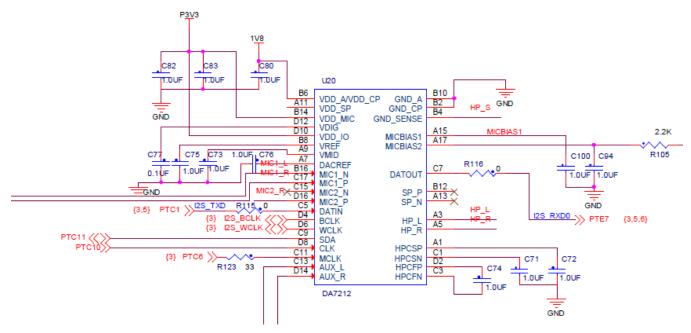

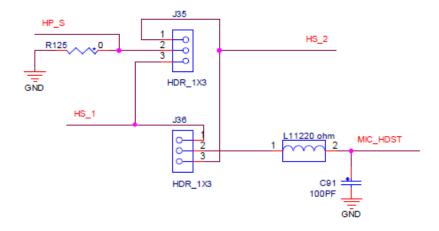

FRDM-K66F board features a Dialog DA7212 ultra-low power audio codec processor with four analogue (or two analogues and two digitals) microphones with two independent microphone biases, headphone output a true-ground Class G with integrated charge pump, stereo auxiliary input, flexible analogue and digital mixing path, and DSP for ALC, 5-band EQ, noise gate, beep generator.

The Dialog audio codec (DA7212) connects to the FRDM-K66F over I2C serial communication for control, and over I2S for digital audio data. By default, the I2C address is 0x1A (Write address: 0x34 and Read address: 0x35).

The maximum I2C clock rate that the DA7212 is capable of is 1 MHz, whereas the K66F is capable of 1 MHz. However, due to FRDM board configuration, the maximum I2C clock that the FRDM can support is 400 KHz.

Digital audio data is transported between the DA7212 and the MCU over I2S data lines. The master/slave configuration is defined by software drivers. When DA7212 is in slave mode, DA7212 receives BCLK and WCLK. When DA7212 is in master mode, DA7212 generates BCLK and WCLK.

Figure 18. FRDM-K66F Audio Codec DA7212

Clock source – MCU vs DA7212

## 16.2. Digital MEMS microphone

An Akustica AKU242 high definition onboard Micro-Electrical Mechanical System (MEMS) microphone (U22) is interfaced through a Pulse Density Modulated (PDM). There are two available options either for K66F direct PDM communication which requires additional software protocol and CPU cycles to handle PDM protocol or uses DA7212 to convert PDM on the fly to Pulse-code modulation (PCM) for K66F communication. By default, J30 and J31 are shunt 1-2 to DA7212.

Figure 19. Digital Mic connection

#### 16.3. I/O connectors

#### 16.3.1. Headset

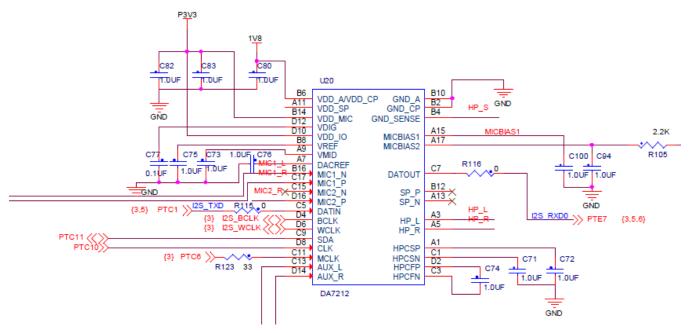

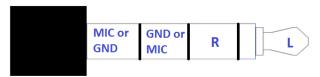

A standard headset with microphone can be attached to the FRDM-K66F via a 3.5 mm 4-pole socket J28. There are two configurations on headset depending on the headset manufacturer. J35 1-2 and J36 1-2 (Default setup) or J35 2-3 and J36 2-3 can be used to route the MIC and GND signals for the two configurations. Headphone left and right channel remain fixed.

Figure 20. Headset Jack diagram

Figure 21. FRDM-K66F headset configuration

The DC bias for the headset microphone is sourced from MICBIAS2. The microphone signal is input to the DA7212 on MIC2\_R.

Table 10. Headset Jack configurations

| Jumper configuration J35 & J36 | FRDM-K66F headset configurations |  |  |

|--------------------------------|----------------------------------|--|--|

| Shunt 1-2                      | L/R/GND/MIC (default)            |  |  |

| Shunt 2-3                      | L/R/MIC/GND                      |  |  |

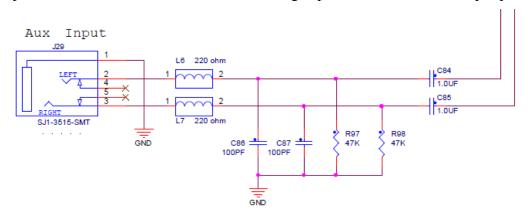

#### 16.3.2. Auxiliary audio input (AUX\_IN)

Analogue signals can be connected to auxiliary input AUX\_L/AUX\_R via a 3.5 mm jack socket J29. The analog inputs are DC biased and a series DC blocking capacitor is added to the input path.

Figure 22. FRDM-K66F AUX\_IN

## 16.3.3. Analog microphone

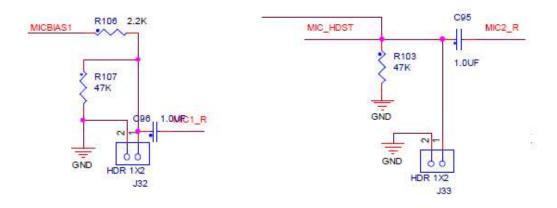

Two external analog microphones can be attached to the board via jumper header 1x2 J32 and J33. J32 pin 1 is routed to MIC1\_R and J33 pin 1 is routed to MIC2\_R. Both J32 and J33 pin 2 is ground. MIC2\_R is too connected to 3.5 mm dual role headset J28. The DC bias for MIC1\_R is sourced from MICBIAS1 and MIC2\_R is sourced from MICBIAS2.

Figure 23. Analog microphone

#### 17. Add-on Modules

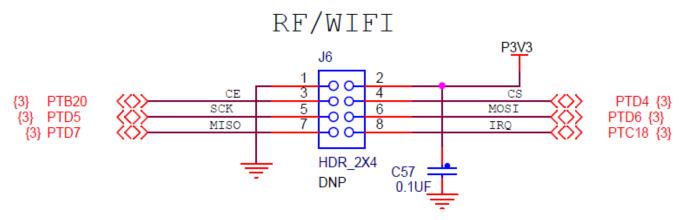

#### 17.1. RF module

IRQ

An optional header (J6) on the FRDM-K66F supports communication with a 2.4 GHz nRF24L01+ Nordic Radio module over SPI. Alternatively, any SPI-based device or module can be used with this header.

Pin **Function** FRDM-K66F RF connection GND Ground P3V3 3.3 V Board supply 3 PTB20/SPI2 PCS0/FB AD31/SDRAM D31/CMP0 OUT CE PTD4/LLWU P14/SPI0 PCS1/UART0 RTS/FTM0 CH4/FB AD2/SDRAM A10/EWM IN/SPI1 PCS0 4 CS 5 SCK PTD5/ADC0 SE6B/SPI0 PCS2/UART0 CTS/UART0 COL/FTM0 CH5/FB AD1/SDRAM A9/EWM O UT/SPI1 SCK MOSI PTD6/LLWU P15/ADC0 SE7B/SPI0 PCS3/UART0 RX/FTM0 CH6/FB AD0/FTM0 FLT0/SPI1 SOUT 6 MISO PTD7/CMT\_IRO/UART0\_TX/FTM0\_CH7/SDRAM\_CKE/FTM0\_FLT1/SPI1\_SIN

PTC18/UART3 RTS/ENET0 1588 TMR2/FB TBST/FB CS2/FB BE15 8 BLS23 16/SDRAM DQM1

Table 11. RF connection

Figure 24. Optional add-on RF/SPI module

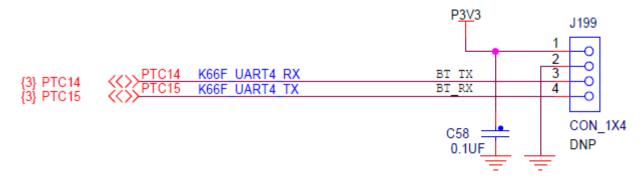

#### 17.2. Bluetooth module

An optional header (J199) on the FRDM-K66F supports communication with add-on Bluetooth, such as the JY-MCU BT Board V1.05 BT wireless Bluetooth module, over an UART.

Alternatively, and serial (SCI) module can be used with this connector. Note that the serials are 3 V levels and do not conform to RS-232 logic levels, so a level shifter such as Maxim DS3232 should be used with RS-232 devices.

Figure 25. Optional add-on bluetooth/SCI module

# 18. Input/Output connectors

The MK66FN2M0VMD18 microcontroller is packaged in a 144-pin MapBGA. Some pins are used in onboard circuitry, but some are directly connected to one of four I/O headers (J1, J2, J3 and J4).

The pins on the K66F microcontroller are named for their general purpose input/output port pin function. For example, the 1<sup>st</sup> pin on Port A is referred to as PTA1. The name assigned to the I/O connector pin corresponds to the GPIO pin of the K66F.

Figure 26. FRDM-K66F I/O header pinout

# 19. Arduino Compatibility

The I/O headers on the FRDM-K66F are arranged to allow compatibility with peripheral boards (known as shields) that connect to Arduino and Arduino-compatible microcontroller boards. The outer rows of pins (Even numbered pins) on the headers share the same mechanical spacing and placement as the I/O headers on the Arduino Revision 3 (R3) standard.

## 20. Miscellaneous

PTA4

## 21. References

The following references are available on www.NXP.com/FRDM-K66F

- FRDM-K66F Quick Start Guide

- FRDM-K66F Schematic, FRDM-K66F-SCH

- FRDM-K66F Design Package

#### **Revision History**

#### Other references:

- DA7212 (http://www.dialog-semiconductor.com/products/audio/audio-codecs/da7212)

- AKU240 (http://www.akustica.com/Digital HD voice mic.asp)

# 22. Revision History

Table 12. Revision history

| Revision number | Date    | Substantial changes |  |

|-----------------|---------|---------------------|--|

| 0               | 02/2016 | Initial release     |  |