# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## FSA9480 — USB 2.0 Accessory Switch

#### Features

- Automatically Detects USB Accessories:

- USB OTG Mode

- CEA-936-A Car Kit and Chargers

- Headsets

SEMICONDUCTOR

- Video Cable

- Factory Mode Cables

- UART

- TTY Converter

- USB Data Cable

- Chargers

- Auto-configures Connections with Independent Override Capability

- Integrated Audio Amplifier Generates Required Bias for CEA-936-A Car Kit Audio

- Automatic Low-Power Mode When No Accessory is Attached

- Integrated Over-Voltage and Over Current Protection FET on V<sub>BUS</sub> for Fault Isolation

- Negative-Swing-Capable Audio Channel

## Applications

Cell Phones

## Description

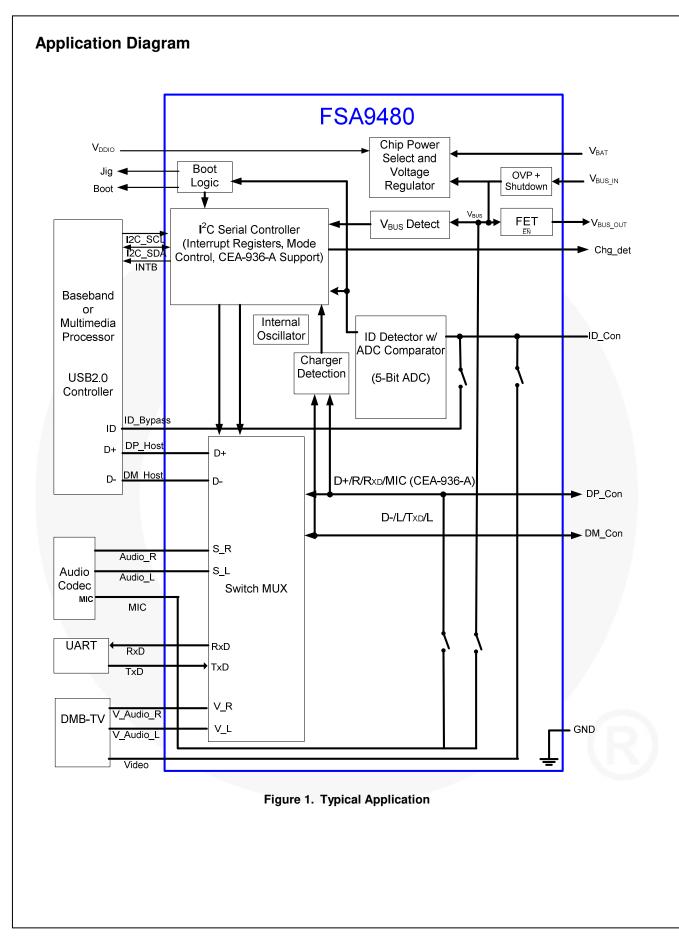

The FSA9480 is a USB port accessory detector and switch. The FSA9480 is fully controlled using  $I^2C^{TM}$  and enables USB data, stereo and mono audio, video, microphone, and UART data to use a common connector port. It is designed for compatibility with CEA-936-A car kit adapters, USB 2.0 signaling, and USB OTG (on-the-go). The architecture is designed to allow audio signals to swing below ground so a common USB and headphone jack can be used for personal media players and portable peripheral devices.

The FSA9480 meets USB specification Rev. 2.0, micro-USB specification, and CEA-936-A.

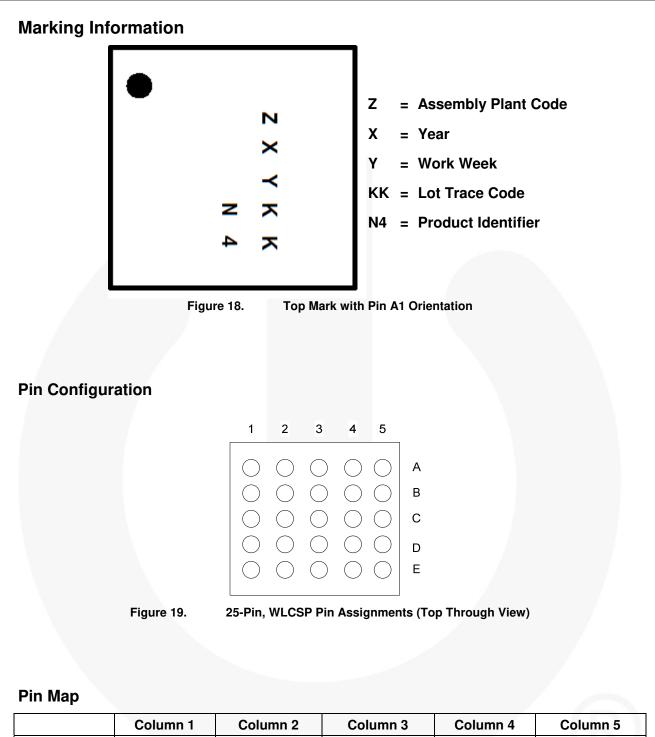

#### **Ordering Information**

| Part Number | Operating<br>Temperature Range | Top Mark | Package                                |

|-------------|--------------------------------|----------|----------------------------------------|

| FSA9480UCX  | -40 to +85°C                   | N4       | 25-Lead, 2.1x2.1x0.625mm WLCSP Package |

$I^2C^{TM}$  is a trademark of NXP B.V. Corporation.

## **Block Descriptions**

This block is used for factory-mode test and debug as described in Table 1.

#### Table 1. Boot Table

| Factory Mode    | ID Resistor | JIG  | BOOT | Switch Connections                           |

|-----------------|-------------|------|------|----------------------------------------------|

| UART, Boot Off  | 523KΩ       | LOW  | LOW  | Table 3 - Accessory Auto Configuration Table |

| USB, Boot On    | 301KΩ       | LOW  | HIGH | Table 3 - Accessory Auto Configuration Table |

| USB, Boot Off   | 255KΩ       | LOW  | LOW  | Table 3 - Accessory Auto Configuration Table |

| UART, Boot On   | 619KΩ       | LOW  | HIGH | Table 3 - Accessory Auto Configuration Table |

| No Factory Mode | N/A         | Hi-Z | LOW  | See Notes 1 and 2                            |

#### Notes:

1. JIG pin description: Low signals the phone to power up. When disabled this open drain floats and the pin is Hi-Z

2. BOOT pin description: This boot pin level directs the baseband processor which mode to boot in when the JIG box is attached, the JIG pin has been driven LOW, and the phone is powered up.

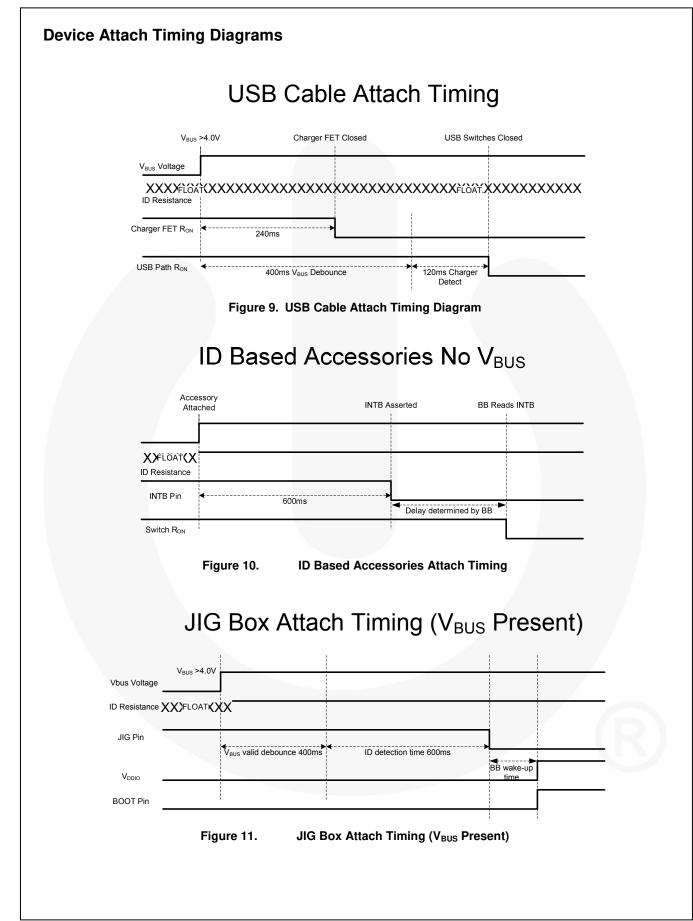

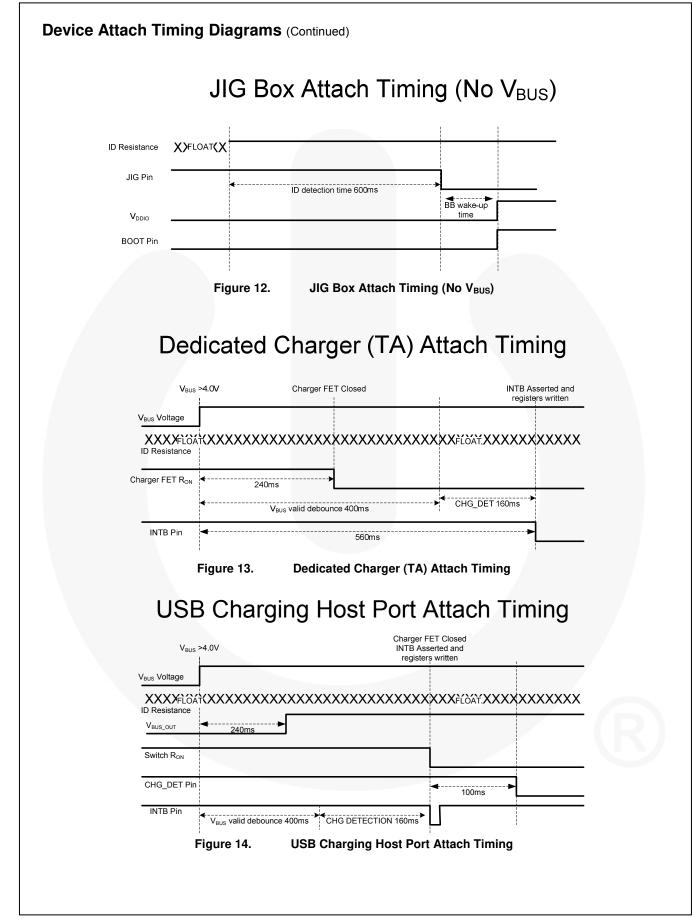

#### D+, D- Charger Detection

This block monitors D+ and D- to determine when a USB charger or dedicated charger is attached to the phone. The detection scheme follows the dedicated charger-detect algorithm as defined in the USB Implementers Forum Battery Charging Specification and as described in the CEA-936-A USB car kit specification. The FSA9480 distinguishes between a dedicated charger and USB charger and reports the appropriate type in the Device Type 1 Register. Whenever either type of charger is detected, the CHG\_DET (I<sub>SET</sub>) pin is pulled LOW.

#### **Chip Power Select and Voltage Regulator**

This block independently selects  $V_{BUS_IN}$  or  $V_{BAT}$  to power the FSA9480 and includes necessary LDO voltage regulators to provide stable power.

Valid ranges (for detecting and accepting supply) for:  $V_{\text{BAT}}$ : 3.0V to 4.4V  $V_{\text{BUS}}$ : 4.4V to 5.5V.

Voltage reference selection criteria:

- If V<sub>BUS</sub> is present and in the valid range, the device takes its power from V<sub>BUS</sub>. Otherwise, the device takes its power from V<sub>BAT</sub> (if in valid range).

- If the device is operating on V<sub>BAT</sub> and a valid V<sub>BUS</sub> becomes available, the device switches to the V<sub>BUS</sub> reference.

This block also accepts a  $V_{\text{DDIO}}$  voltage reference for baseband interface I/O signals.

#### **OVP / OCP Shutdown Block**

When  $V_{BUS}$  is less than 6.8V, this block allows the  $V_{BUS}$  supply to enter the chip power select voltage regulator block. For  $V_{BUS}$  greater than 7.2V, the input is disconnected, protecting the FSA9480 from excess voltage. This block is capable of withstanding continuous 28V in shutdown mode. Upon entering shutdown, the OVP\_EN bit in the Interrupt 1 Register is set HIGH and an interrupt is sent to the baseband. The Over-Current Protection (OCP) feature limits current through the charger FET to  $\leq 1.5A$  maximum. The FSA9480 automatically senses an over-current event,

clamps the current, and reports to the baseband by asserting OCP\_EN in the Interrupt 1 Register. OCP mode is only implemented when  $V_{BUS}$  is provided by the attached accessory. In PPD Mode *(see below)*, the FSA9480 does not limit current supplied by the phone.

#### **V<sub>BUS</sub> Detect and FET Blocks**

This block monitors the status of the V<sub>BUS</sub> pin. A valid V<sub>BUS</sub> level is defined as V<sub>BUS</sub> greater than 4.4V and less than 5.5V. When V<sub>BUS</sub> is determined to be valid, the internal NMOS charging FET is enabled, allowing battery charging whenever a valid V<sub>BUS</sub> is present. The charging FET is designed to limit inrush current to 100mA during enable to allow the voltage levels to stabilize during initial connection. This current limiting is automatic and designed per the requirements outlined in the USB Battery Charging Specification.

#### I<sup>2</sup>C<sup>™</sup> and Digital Core Block

This block includes a full  $I^2C$  slave controller. The  $I^2C$  slave fully complies with the  $I^2C$  specification version 2.1 requirements. This block also includes the FSA9480 chip master controller. The chip controller monitors commands sent to the FSA9480 via  $I^2C$  from the baseband and takes action. The FSA9480 digital core takes inputs from the various functional blocks within the FSA9480 and the  $I^2C$  commands received from the phone baseband and relays relevant status updates to the phone.

## ID Detector with Analog Digital Converter (ADC) Block

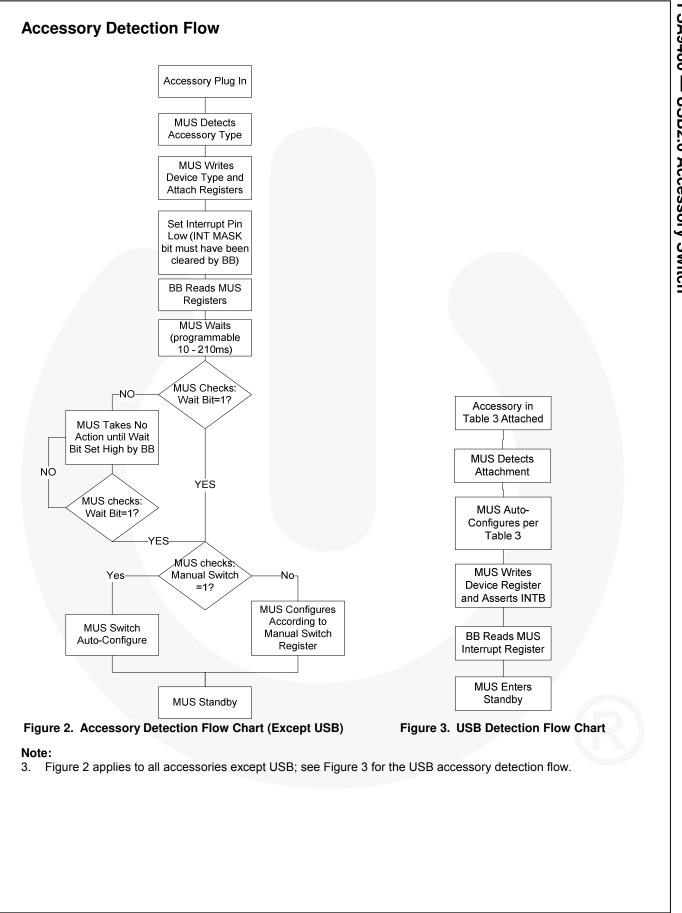

This block monitors the ID pin for accessory attach and detach. After determining which accessory has been attached, the detector block reports this back to the digital core, which sends an interrupt to the baseband. Upon detecting changes in the ID pin voltage, the ADC also writes the ADC value bits in the ADC Register. The baseband processor can then read the  $I^2C$  registers and determine the appropriate action. The programmable wait time does not begin until after the baseband acknowledges the interrupt read. Figure 2 outlines the high-level accessory detection flow sequence for Samsung-specific accessories.

| Bit Number |   |   |   | Equivalent R <sub>ID</sub> | Description |                                                    |

|------------|---|---|---|----------------------------|-------------|----------------------------------------------------|

| 4          | 3 | 2 | 1 | 0                          | (ΚΩ)        | Description                                        |

| )          | 0 | 0 | 0 | 0                          | GND         | USB OTG Mode                                       |

| )          | 0 | 0 | 0 | 1                          | 2.000       | Audio Send_End Button                              |

| )          | 0 | 0 | 1 | 0                          | 2.604       | Audio Remote S1 Button                             |

| )          | 0 | 0 | 1 | 1                          | 3.208       | Audio Remote S2 Button                             |

| )          | 0 | 1 | 0 | 0                          | 4.014       | Audio Remote S3 Button                             |

| )          | 0 | 1 | 0 | 1                          | 4.820       | Audio Remote S4 Button                             |

| )          | 0 | 1 | 1 | 0                          | 6.030       | Audio Remote S5 Button                             |

| )          | 0 | 1 | 1 | 1                          | 8.030       | Audio Remote S6 Button                             |

| )          | 1 | 0 | 0 | 0                          | 10.030      | Audio Remote S7 Button                             |

| )          | 1 | 0 | 0 | 1                          | 12.030      | Audio Remote S8 Button                             |

| )          | 1 | 0 | 1 | 0                          | 14.460      | Audio Remote S9 Button                             |

| C          | 1 | 0 | 1 | 1                          | 17.260      | Audio Remote S10 Button                            |

| C          | 1 | 1 | 0 | 0                          | 20.500      | Audio Remote S11 Button                            |

| )          | 1 | 1 | 0 | 1                          | 24.070      | Audio Remote S12 Button                            |

| )          | 1 | 1 | 1 | 0                          | 28.700      | Reserved Accessory #1                              |

| C          | 1 | 1 | 1 | 1                          | 34.000      | Reserved Accessory #2                              |

| 1          | 0 | 0 | 0 | 0                          | 40.200      | Reserved Accessory #3                              |

| 1          | 0 | 0 | 0 | 1                          | 49.900      | Reserved Accessory #4                              |

| 1          | 0 | 0 | 1 | 0                          | 64.900      | Reserved Accessory #5                              |

| 1          | 0 | 0 | 1 | 1                          | 80.070      | Audio Device Type 2                                |

| 1          | 0 | 1 | 0 | 0                          | 102.000     | Phone Powered Device                               |

| 1          | 0 | 1 | 0 | 1                          | 121.000     | TTY Converter                                      |

| 1          | 0 | 1 | 1 | 0                          | 150.000     | UART Cable                                         |

| 1          | 0 | 1 | 1 | 1                          | 200.000     | CEA-936-A Type-1 Charger <sup>(4)</sup>            |

| 1          | 1 | 0 | 0 | 0                          | 255.000     | Factory Mode Boot OFF-USB                          |

| 1          | 1 | 0 | 0 | 1                          | 301.000     | Factory Mode Boot ON-USB                           |

| 1          | 1 | 0 | 1 | 0                          | 365.000     | Audio/Video Cable                                  |

| 1          | 1 | 0 | 1 | 1                          | 442.000     | CEA-936-A Type-2 Charger <sup>(4)</sup>            |

|            | 1 | 1 | 0 | 0                          | 523.000     | Factory Mode Boot OFF-UART                         |

|            | 1 | 1 | 0 | 1                          | 619.000     | Factory Mode Boot ON-UART                          |

|            | 4 | 4 | 4 | 0                          | 1000.070    | Audio Device Type 1 with Remote <sup>(4)</sup>     |

| 1          | 1 | 1 | 1 | U                          | 1002.000    | Audio Device Type 1 / Only Send-End <sup>(5)</sup> |

Chargers must provide a valid V<sub>BUS</sub> for the FSA9480 to report them to the phone baseband.

Audio devices with remote and audio device / only send end are reported as audio in the Device Type 1 Register. The FSA9480 auto-configures in Audio Mode, as described in Table 3.

#### Switch MUX Block

The switch MUX block contains an  $I^2C$  controlled DP4T multiplexer with dedicated paths for high-speed USB, audio R/L, TV R/L, and UART signaling. A summary of

the switch auto configuration connections for the various states is shown in Table 3.

| Configurati                        | ion Type | V <sub>BUS</sub>  | DP        | DM        | ID                      | воот | JIG  | CHG_DET<br>(I <sub>SET</sub> ) |

|------------------------------------|----------|-------------------|-----------|-----------|-------------------------|------|------|--------------------------------|

| Audio Type 1                       |          | MIC               | Audio_R   | Audio_L   | Key<br>Press<br>Monitor | LOW  | Hi-Z | Hi-Z                           |

| Audio Type 2                       |          | Chg FET<br>Closed | RxD       | TxD       | (7)                     | LOW  | Hi-Z | Hi-Z                           |

| TTY                                |          | MIC               | Audio_R   |           | (7)                     | LOW  | Hi-Z | Hi-Z                           |

| UART                               |          | (6)               | RxD       | TxD       | (7)                     | LOW  | Hi-Z | Hi-Z                           |

| USB                                |          | Chg FET<br>Closed | DP_Host   | DM_Host   | IDBP                    | LOW  | Hi-Z | Hi-Z                           |

| USB Charger                        |          | Chg FET<br>Closed | DP_Host   | DM_Host   | IDBP                    | LOW  | Hi-Z | Low                            |

| A/V Cable                          |          | (6)               | V_Audio_R | V_Audio_L | Video                   | LOW  | Hi-Z | Hi-Z <sup>(8)</sup>            |

| Dedicated Char<br>Type I & II Char |          | Chg FET<br>Closed | Open      | Open      | NA                      | LOW  | Hi-Z | Low                            |

| Phone Power<br>(PPE                |          | Chg FET<br>Closed | Audio_R   | Audio_L   | (7)                     | LOW  | Hi-Z | Hi-Z                           |

| Factory Mode                       | Boot_On  | Chg FET<br>Open   | RxD       | TxD       | (7)                     | HIGH | LOW  | Hi-Z                           |

| Jig: UÁRT                          | Boot_Off | Chg FET<br>Open   | RxD       | TxD       | (7)                     | LOW  | LOW  | Hi-Z                           |

| Factory Mode                       | Boot_On  | Chg FET<br>closed | DP_Host   | DM_Host   | (7)                     | HIGH | LOW  | Hi-Z                           |

| Jig: UŠB                           | Boot_Off | Chg FET<br>closed | DP_Host   | DM_Host   | (7)                     | LOW  | LOW  | Hi-Z                           |

Table 3.

Accessory Auto Configuration Table

#### Notes:

6. If V<sub>BUS</sub> is valid, the charger FET is closed; otherwise, the charger FET is open.

7. ID is monitored by ADC for change of state.

8. Unless V<sub>BUS</sub> is valid, in which case, a charger adapter has been added and CHG\_DET is enabled.

## **Mode Descriptions**

#### Initialization

On initial power up, all register bits are initialized to their default condition, as defined in the I<sup>2</sup>C register map. During initialization, all switch paths are open. Immediately after initializing, all registers transition to Standby/IDLE Mode.

#### V<sub>DDIO</sub> Reset Mode

While in active mode, the FSA9480 is reset by the falling edge of the  $V_{DDIO}$  signal pin as the  $V_{DDIO}$  level transitions from HIGH to LOW. In this case, the FSA9480 automatically resets to its initialization state. All register bits are initialized to their default condition, as defined in the  $I^2C$  register map. Immediately following  $V_{DDIO}$  reset all switch paths are open and the FSA9480 transitions to Standby/IDLE Mode. The FSA9480 enters Standby/Idle Mode after the initial reset, while the  $V_{DDIO}$  pin remains LOW. Immediately after the  $V_{DDIO}$  level returns to a High and the Interrupt Mask is cleared the FSA9480 reports any activity detected while in Standby/Idle Mode.

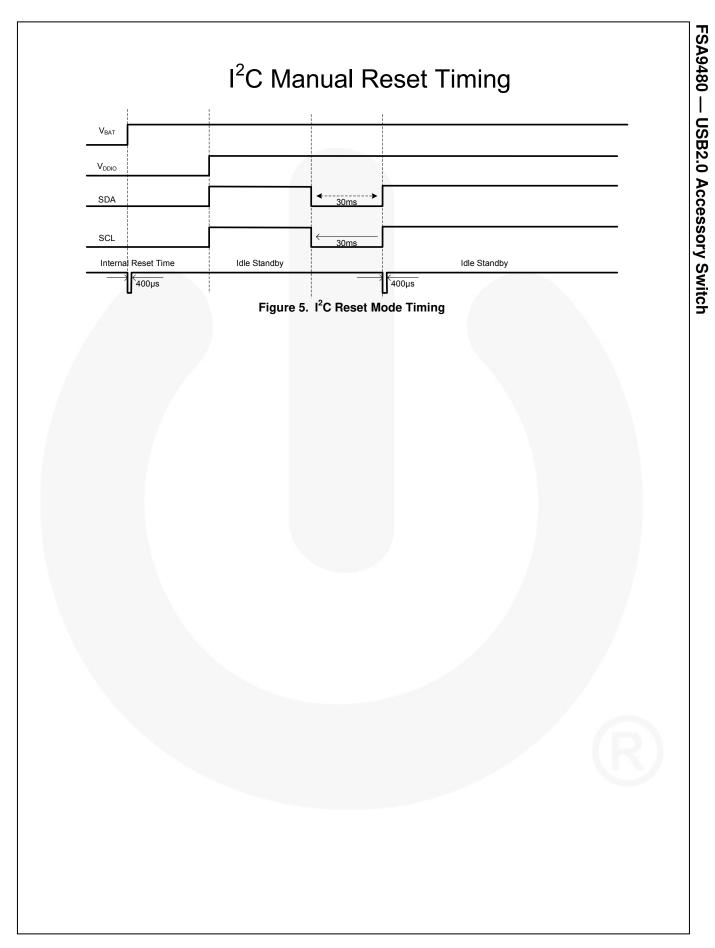

## I<sup>2</sup>C Reset Mode

The FSA9480 can also be reset by driving both the SDA and SCL signal lines LOW for 30ms. In this case, the FSA9480 automatically resets all registers to default condition, as defined in the  $I^2C$  register map. Immediately following  $I^2C$  reset, all switch paths are open and FSA9480 transitions to Standby/IDLE mode. See Figure 5 for detailed timing for  $I^2C$  Reset Mode.

## Standby / IDLE

In this state, no accessory is attached. This state is connected to all other states. During this state, the device is in a power-down mode with a minimal set of functions running. The ID detector continuously monitors the ID pin for accessory attach. Upon accessory attach, the FSA9480 transitions to the appropriate mode based on the accessory.

## Charger Mode

When any of the possible charger types are attached, the FSA9480 closes the FET switch and CHG\_DET ( $I_{SET}$ ) is asserted LOW. When CHG\_DET is asserted LOW this signals the phones charger IC to enable high-current mode. When CHG\_DET is Hi-Z, the charger IC defaults to low-current charge mode.

#### USB 2.0 and USB OTG Modes

When USB2.0 cable is attached, the FSA9480 configures the switch MUX block according to Table 3. The charger FET is closed.

## Dead Battery / No Battery Mode

When no battery or a dead battery is present, the FSA9480 disables the following pins to Hi-Z: INTB,  $I^2C\_SDA$ ,  $I^2C\_SCL$ , Jig, Boot, R<sub>XD</sub>, T<sub>XD</sub>, and CHG\_DET.

## CEA-936-A Car Kit

Upon initial detection of a CEA-936-A car kit accessory, the FSA9480 detects and reports a car kit accessory attachment. The FSA9480 then initiates the car kit signaling protocol, as described in the CEA-936-A specification. Accordingly, the FSA9480 initializes in UART mode, as described section 7.2.2 of the CEA-936-A specification. The FSA9480 implements the fourwire protocol required for state transitions within the CEA-936-A specification. The baseband processor directs the FSA9480, using the mode bits in the Car Kit Register, to signal the FSA9480 to change modes within the car kit protocol. The phone generates the USB, UART, and audio signals and the FSA9480 multiplexes the appropriate signal out to the attached car kit device. The FSA9480 performs all handshaking necessary with the attached car kit accessory and automatically configures the switch MUX based on the mode setting called for by the baseband processor. Car Kit Audio Mode requires a 1.2V bias applied to the audio signal. The FSA9480 contains a special audio path that provides a 1.2V bias to the Audio\_R and Audio L channels when in Car Kit Audio Mode. To achieve the proper bias, the FSA9480 incorporates a separate car kit audio path, containing two unity gain amplifiers. The FSA9480 also uses these audio amplifiers to implement the Car Kit Data During Audio (DDA) Mode. While in DDA mode, the phone must limit the audio signal being driven through the FSA9480 to amplitude no greater than 1V, peak to peak.

## Phone Powered Device Mode (PPD)

In Phone Power Device (PPD) Mode, the cell phone provides power to the attached accessory through the charger FET. In this mode, the charger FET is not closed until after the wait time has expired; at which time, the phone should have already biased its output voltage level on the  $V_{BUS}$  pin. The phone should never source more than 10mA through the FSA9480 charger FET while in PPD mode. When in PPD mode, the charger FET provides a current path out of the phone to the PPD. There is no inrush current limiting or OCP protection provided by the charger FET when the FSA9480 is in PPD Mode.

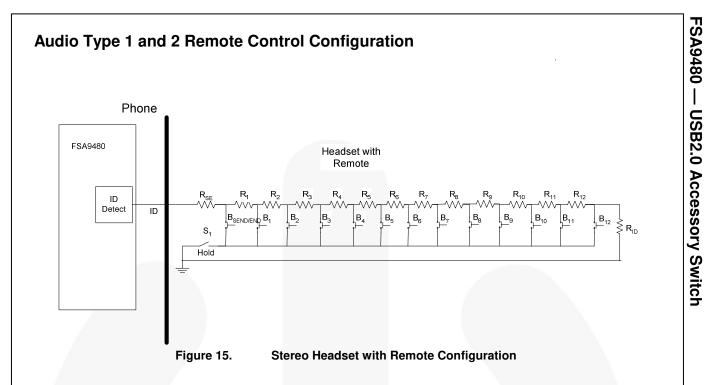

## Audio Modes

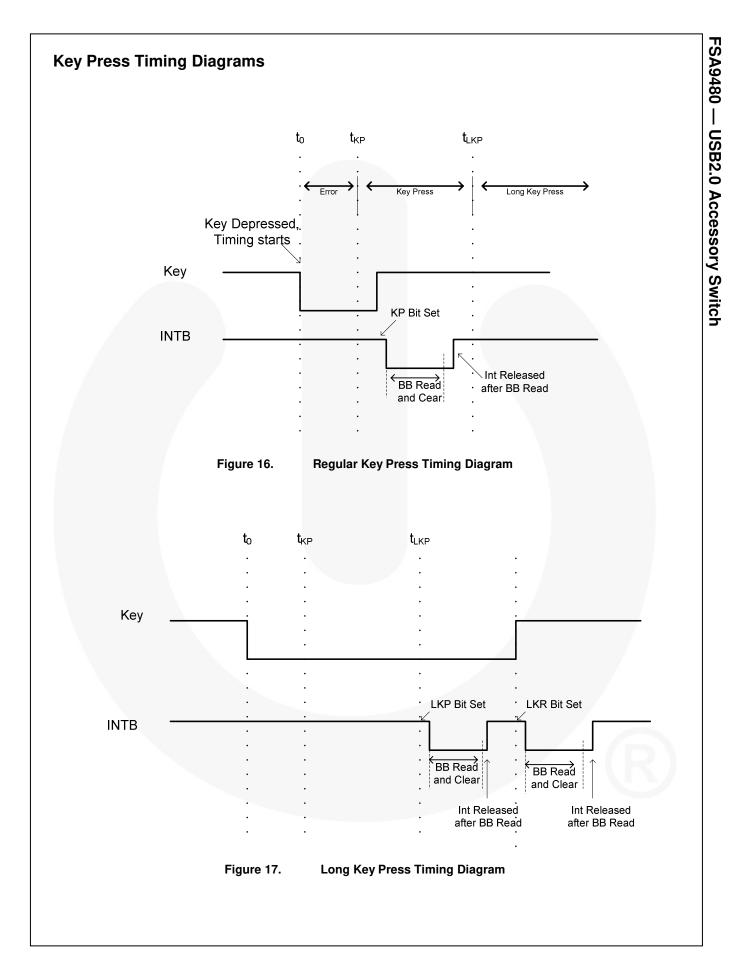

When any of the compatible headsets are attached, the FSA9480 configures as described in Table 3. The FSA9480 is compatible with Samsung headphones that include a remote-control feature. When in Audio Mode, the FSA9480 continuously monitors for remote-control button presses and reports any presses back to the baseband. Figure 15 illustrates the headset with remote basic circuit; Table 4 provides resistor values.

**Audio Device Type-1** accessories are passive devices with only one switch configuration per device. They may or may not include a remote controller.

FSA9480 — USB2.0 Accessory Switch

Audio Device Type-2 devices include a built-in UART controller and the FSA9480 auto configures with UART switch paths connected, as described in Table 3. These devices include a remote controller. After initial configuration in UART Mode, the baseband may change the FSA9480 switch mode configuration by writing any of the following bit patterns in the Car Kit Status Register mode bits: 000, 001, 100, 101. While an audio type-2 accessory is attached, it is possible for the baseband to signal changes in switch configuration from any mode to any mode until device detach is detected. While in DDA Mono (100) mode, the FSA9480 DDA circuitry is activated, allowing data to be sent and received during audio transmission between the resident UART transceivers in the phone and the audio type-2 device. The FSA9480 DDA audio scheme follows that of the CEA-936-A specification as implemented in the car kit mode of the FSA9480. Other than implementing the DDA transmission and reception scheme in CEA-936-A, the FSA9480 does not implement any car kit protocols or state machines while in Audio Device Type-2 Mode. In DDA Mode, the phone must limit the audio signal driven through the FSA9480 to amplitude no greater than 1V, peak to peak.

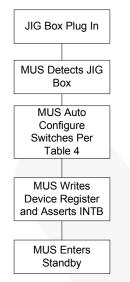

#### **Factory Modes**

Factory Modes are initiated with the attachment of a Samsung proprietary JIG Box and are used for phone assembly and testing. The Factory Mode attach procedure is slightly different from the standard accessory attach flow. The primary difference is that the FSA9480 automatically configures the switch paths as soon as a Factory Mode accessory is attached and  $V_{\text{DDIO}}$  is present. This is unique in that the FSA9480 does not wait for an  $I^2$ C read acknowledge from the baseband and does not employ the switch wait timer. A second difference is that, in this mode, the JIG pin is driven LOW even if the VDDIO pin is LOW. Figure 4 provides the attach flow for the JIG Box accessory.

Figure 4. JIG Box Detection Flow

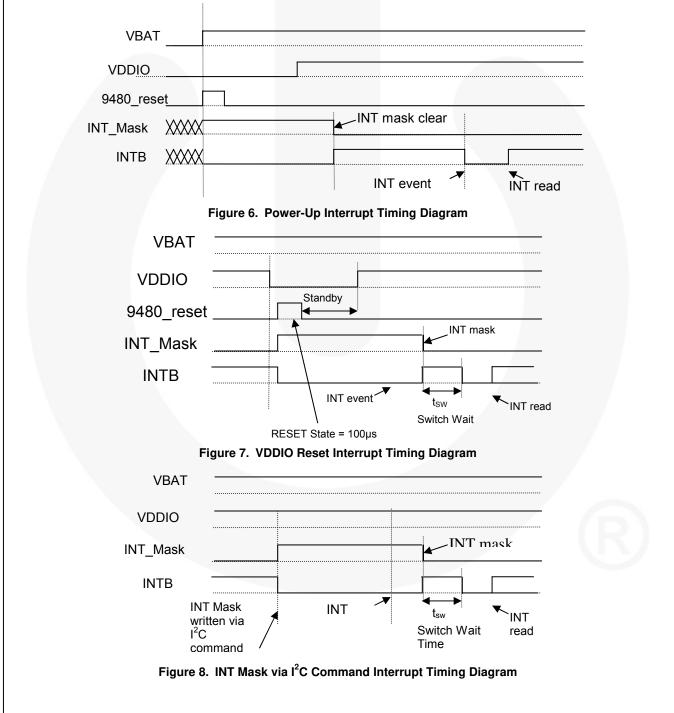

#### Interrupt Operation Description

The FSA9480 follows the Interrupt guidelines as described in the Samsung Interrupt Definition and Default Path specification Rev 0.1 released July 15 2008. The baseband processor recognizes interrupt signals by observing the falling edge of the INTB signal in a high-to-low transition. During the phone power-up sequence,  $V_{DDIO}$  reset or I<sup>2</sup>C reset the INTB pin is masked on initialization and defaults LOW. After the INTB mask is cleared by the baseband processor, the INTB pin is HIGH in preparation of a future interrupt. If the interrupt mask bit in the I<sup>2</sup>C Control Register is

written HIGH when the system is already powered up, the INTB remains HIGH until the INTB mask is cleared. If an interruptible event occurs while the INTB pin is masked, the FSA9480 changes the appropriate register value and waits until the INTB mask bit is cleared, plus the switch wait time before signaling an interrupt to the baseband. Figure 6 illustrates the interrupt timing for the FSA9480 during initial power up. Figure 7 shows the INTB behavior during a V<sub>DDIO</sub> reset. Figure 8 illustrates the INTB timing when the INT Mask bit is written by the baseband using  $I^2C$  commands.

| Table 4. | <b>Remote Control</b> | <b>Besistor Table</b> | (1% Resistor  | Values)  |

|----------|-----------------------|-----------------------|---------------|----------|

|          |                       |                       | (1/0110313101 | l'uluco) |

| Switch and Resistor Number | Resistor Value | Resistor Number | Resistor Value       |  |  |  |  |  |

|----------------------------|----------------|-----------------|----------------------|--|--|--|--|--|

| RSE                        | 2ΚΩ            | B7, R7          | 2ΚΩ                  |  |  |  |  |  |

| B1, R1                     | 0.604ΚΩ        | B8, R8          | 2ΚΩ                  |  |  |  |  |  |

| B2, R2                     | 0.604KΩ        | B9, R9          | 2.43ΚΩ               |  |  |  |  |  |

| B3, R3                     | 0.806ΚΩ        | B10, R10        | 2.8ΚΩ                |  |  |  |  |  |

| B4, R4                     | 0.806KΩ        | B11, R11        | 3.24ΚΩ               |  |  |  |  |  |

| B5, R5                     | 1.21ΚΩ         | B12, R12        | 3.57ΚΩ               |  |  |  |  |  |

| B6, R6                     | 260            | RID             | 976KΩ (Audio Type 1) |  |  |  |  |  |

| 00, R0                     | 2ΚΩ            | RID             | 56KΩ (Audio Type 2)  |  |  |  |  |  |

|       | Column 1 | Column 2             | Column 3  | Column 4 | Column 5 |

|-------|----------|----------------------|-----------|----------|----------|

| Row A | INTB     | VDDIO                | CHG_DET   | VBUS_OUT | VBUS_IN  |

| Row B | DP_Host  | I <sup>2</sup> C_SDA | Audio_L   | MIC      | DM_CON   |

| Row C | DM_Host  | I <sup>2</sup> C_SCL | V_Audio_L | Audio_R  | DP_CON   |

| Row D | VBAT     | ID_Bypass            | V_Audio_R | Video    | ID_CON   |

| Row E | RxD      | TxD                  | BOOT      | JIG      | GND      |

| Name                           | Pin # | Туре                     | Default<br>State | Description                                                                                                                                     |

|--------------------------------|-------|--------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Interfac                   | e     |                          |                  |                                                                                                                                                 |

| DP_Host                        | B1    | Signal<br>Path           | Open             | D+ signal, dedicated USB port to be connected to the resident USB transceiver on the phone                                                      |

| DM_Host                        | C1    | Signal<br>Path           | Open             | D- signal, dedicated USB port to be connected to the resident USB transceiver on the phone                                                      |

| ID_Bypass                      | D2    | Signal<br>Path           | Open             | USB ID pin bypass allows the FSA9480 to pass the ID signal pin through<br>to the resident phone USB controller when a USB accessory is attached |

| Audio Interfa                  | ace   |                          |                  |                                                                                                                                                 |

| Audio_L                        | В3    | Signal<br>Path           | Open             | Left audio channel from phone audio-out codec                                                                                                   |

| Audio_R                        | C4    | Signal<br>Path           | Open             | Right audio channel from phone audio-out codec                                                                                                  |

| MIC                            | B4    | Signal<br>Path           | Open             | Connected to the phone audio codec MIC input pin                                                                                                |

| Video Interfa                  | ace   |                          |                  |                                                                                                                                                 |

| Video                          | D4    | Signal<br>Path           | Open             | Input signal driven by the phone DMB video-out signal                                                                                           |

| V_Audio_L                      | C3    | Signal<br>Path           | Open             | Left audio channel from TV audio out                                                                                                            |

| V_Audio_R                      | D3    | Signal<br>Path           | Open             | Right audio channel from TV audio out                                                                                                           |

| UART Interfa                   | ace   |                          |                  |                                                                                                                                                 |

| TxD                            | E2    | Signal<br>Path           | Open             | Tx connection from resident UART transceiver on the phone                                                                                       |

| RxD                            | E1    | Signal<br>Path           | Open             | Rx connection from resident UART transceiver on the phone                                                                                       |

| Factory Inter                  | rface |                          |                  |                                                                                                                                                 |

| Jig                            | E4    | Open-<br>Drain<br>Output | Hi-Z             | Output control signal driven by the FSA9480; used by the processor for Samsung factory test modes                                               |

| Boot                           | E3    | Push-<br>Pull<br>Output  | LOW              | Output control signal driven by the FSA9480, used by the processor for Samsung factory test modes                                               |

| Power Interf                   | ace   |                          |                  |                                                                                                                                                 |

| V <sub>BAT</sub>               | D1    | Power                    | N/A              | Input voltage supply pin to be connected to the phone battery output                                                                            |

| V <sub>BUS_OUT</sub>           | A4    | Power                    | N/A              | Output voltage supply pin to be connected to the source voltage pin on the charger IC                                                           |

| V <sub>DDIO</sub>              | A2    | Power                    | N/A              | Input baseband interface I/O supply pin                                                                                                         |

| CHG_DET<br>(I <sub>SET</sub> ) | A3    | Open-<br>Drain<br>Output | Hi-Z             | Open-drain I/O pin, active LOW, used to signal charger IC that a charge has been attached                                                       |

| nued)            |                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Default<br>State | Description                                                                                                                                              |

|                  |                                                                                                                                                          |

| N/A              | Input voltage supply pin; connect to the $V_{\text{BUS}}$ pin of the USB connector                                                                       |

| N/A              | Ground                                                                                                                                                   |

| Open             | Connected to the USB connector ID pin; depending on the FSA9480 state, this pin can share ID or video signals                                            |

| Open             | Connected to the USB connector D+ pin; depending on the FSA9480 signaling mode, this pin can share D+, S_R, V_R, Rxd, or MIC signals                     |

| Open             | Connected to the USB connector D- pin; depending on the FSA9480 signaling mode, this pin can share D-, S_L, Txd, or V_L signals                          |

|                  |                                                                                                                                                          |

| N/A              | I <sup>2</sup> C serial clock signal to be connected to the phone based I <sup>2</sup> C master                                                          |

| Hi-Z             | Open-drain I/O pin; I <sup>2</sup> C serial data signal to be connected to the phone based I <sup>2</sup> C master                                       |

| Low              | Interrupt signal to prompt the phone baseband to read the I <sup>2</sup> C register bits, indicates a change in ID pin status or accessory attach status |

Pin Descriptions (Continued

Pin #

A5

E5

D5

C5

B5

C2

B2

A1

Туре

Power

Power

Signal

Path Signal

Path Signal

Path

Input

Open-

Drain

I/O Push-

Pull

Output

Name

$V_{\text{BUS}\_\text{IN}}$

GND

ID\_CON

DP\_CON

DM\_CON

I<sup>2</sup>C Interface

I<sup>2</sup>C\_SDA

INTB

**Connector Interface**

FSA9480 — USB2.0 Accessory Switch

#### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                              | Param                                                            | Min.                            | Max.       | Unit |                       |    |  |

|-------------------------------------|------------------------------------------------------------------|---------------------------------|------------|------|-----------------------|----|--|

| V <sub>BAT</sub> /V <sub>DDIO</sub> | Supply Voltage from Battery / Baseba                             | -0.5                            | 6.0        | V    |                       |    |  |

| V <sub>BUS</sub>                    | Supply Voltage from Mini–USB Conn                                | ector                           |            | -0.5 | 28.0                  | V  |  |

|                                     |                                                                  | USB or Car Kit Path A           | ctive      | -1.0 | V <sub>BUS</sub> +0.5 |    |  |

| $V_{\text{SW}}$                     | Switch I/O Voltage                                               | Stereo/Mono Audio Pa            | ath Active | -1.5 | V <sub>BAT</sub> +0.5 | V  |  |

|                                     |                                                                  | All Other Channels              |            | -0.5 | V <sub>BAT</sub> +0.5 |    |  |

| I <sub>IK</sub>                     | Input Clamp Diode Current                                        |                                 |            | -50  |                       | mA |  |

| Chg_Det                             | Charger Detect Sets Current Sink Capability of the Charger IC    |                                 |            |      | 30                    | mA |  |

| I <sub>sw</sub>                     |                                                                  | USB                             |            |      | 50                    |    |  |

|                                     | Switch I/O Current (Continuous)                                  | Audio                           |            |      | 60                    | mA |  |

|                                     |                                                                  | All Other Channels              |            | 50   |                       |    |  |

|                                     |                                                                  | USB                             |            |      | 150                   | mA |  |

|                                     | Peak Switch Current (Pulsed at 1ms<br>Duration, <10% Duty Cycle) | Audio                           |            |      | 150                   | mA |  |

| SWPEAK                              |                                                                  | Charger FET                     |            |      | 1.2                   | А  |  |

|                                     |                                                                  | All Other Channels              |            | 150  | mA                    |    |  |

| T <sub>STG</sub>                    | Storage Temperature Range                                        |                                 |            | -65  | +150                  | °C |  |

| TJ                                  | Maximum Junction Temperature                                     |                                 |            |      | +150                  | °C |  |

| TL                                  | Lead Temperature (Soldering, 10 Sec                              | conds)                          |            |      | +260                  | °C |  |

|                                     | IEC 61000-4-2 System                                             | USB Connector Pins              | Air Gap    | 15   |                       |    |  |

| ESD                                 | Electrostatic Discharge                                          | (D+, D-, V <sub>BUS</sub> , ID) | Contact    | 8    |                       | kV |  |

|                                     | JEDEC JESD22-A114, Human Body                                    | Model                           | All Pins   | 4    |                       |    |  |

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol            | Parameter                                                          |                  |      | Max. | Units |

|-------------------|--------------------------------------------------------------------|------------------|------|------|-------|

| $V_{BAT}$         | Battery Supply Voltage                                             |                  | 3.0  | 4.4  | V     |

| $V_{BAT_TH}$      | Battery Supply Voltage Threshold                                   |                  |      | 3.0  | V     |

| V <sub>BUS</sub>  | Supply Voltage                                                     |                  | 4.00 | 5.25 | V     |

| V <sub>DDIO</sub> | Baseband-supplied Reference Voltage                                |                  |      | 3.6  | V     |

|                   | US                                                                 | SB Path Active   | 0    | 3.6  | V     |

| V <sub>SW</sub>   | Switch I/O Voltage Au                                              | udio Path Active | -0.8 | 0.8  | V     |

|                   | All                                                                | Other Pins       | 0    | 5.0  | V     |

| $ID_{Cap}$        | Maximum Capacitive Load on ID pin for Reliable Accessory Detection |                  |      | 1.5  | nF    |

| T <sub>A</sub>    | Operating Temperature                                              |                  | -40  | +85  | °C    |

FSA9480 — USB2.0 Accessory Switch

## Switch Path DC Electrical Characteristics

All typical values are at 25°C unless otherwise specified.

| Symbol               | Parameter                                               | V ()/)               | Conditions                                                                                               | T <sub>A</sub> =           | Unit |      |    |

|----------------------|---------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------|----------------------------|------|------|----|

| Symbol               | Parameter                                               | V <sub>BAT</sub> (V) | Conditions                                                                                               | Min.                       | Тур. | Max. |    |

| UART Int             | erface Pins                                             |                      |                                                                                                          |                            |      |      |    |

| V <sub>OHRXD</sub>   | R <sub>xD</sub> Output High Voltage                     | 3.0 to 4.4           | I <sub>OH</sub> =2mA                                                                                     | 0.7 •<br>V <sub>DDIO</sub> |      |      | V  |

| VOLRXD               | R <sub>XD</sub> Output Low Voltage                      | 3.0 to 4.4           | I <sub>OL</sub> =10mA                                                                                    |                            |      | 0.4  | V  |

| VIHDPCon             | UART Input (DP_Con) High<br>Voltage                     | 3.0 to 4.4           |                                                                                                          | 0.7 •<br>V <sub>DDIO</sub> |      |      | V  |

| VILDPCon             | UART Path (DP_Con) Input Low Voltage                    | 3.0 to 4.4           |                                                                                                          |                            |      | 0.4  | V  |

| VOHDMCon             | UART Output (DM_Con) High<br>Voltage                    | 3.0 to 4.4           | I <sub>OH</sub> =2mA                                                                                     | 0.7 •<br>V <sub>BAT</sub>  |      |      | V  |

| VOLDMCon             | UART Output (DM_Con) Low Voltage                        | 3.0 to 4.4           | I <sub>OL</sub> =10mA                                                                                    |                            |      | 0.4  | V  |

| VIHTXD               | T <sub>XD</sub> Input High Voltage                      | 3.0 to 4.4           |                                                                                                          | 0.7 •<br>V <sub>DDIO</sub> |      |      | V  |

| VILTXD               | T <sub>XD</sub> Input Low Voltage                       | 3.0 to 4.4           |                                                                                                          |                            |      | 0.4  | V  |

| Host Inte            | rface Pins (JIG, BOOT, INTB, CH                         | G-DET)               |                                                                                                          |                            |      |      |    |

| Vон                  | Output High Voltage <sup>(9)</sup>                      | 3.0 to 4.4           | I <sub>OH</sub> =2mA                                                                                     | 0.7 •<br>V <sub>DDIO</sub> |      |      | v  |

| Vol                  | Output Low Voltage                                      | 3.0 to 4.4           | I <sub>OL</sub> =10mA                                                                                    |                            |      | 0.4  | V  |

| Switch O             | ff Characteristics                                      |                      |                                                                                                          |                            |      |      |    |

| I <sub>OFF</sub>     | Power Off Leakage Current                               | 0                    | All Data Ports Except Video,<br>ID Bypass and MIC V <sub>SW</sub> =0V<br>to 4.4V                         |                            |      | 18   | μA |

| I <sub>NO(0FF)</sub> | Off-Leakage Current                                     | 3.0 to 4.4           | I/O pins=0.3V, V <sub>BAT</sub> , or<br>Floating                                                         | -100                       | 1    | 100  | nA |

| USB Swit             | tch On Path                                             |                      |                                                                                                          |                            |      |      | 1  |

| USB Anal             | og Signal Range                                         | 3.0 to 4.4           |                                                                                                          | 0                          |      | 3.6  | V  |

| RONUSB               | HS Switch On Resistance <sup>(10,13)</sup>              | 3.0 to 4.4           | V <sub>D+/D-</sub> =0V, 0.4V, I <sub>ON</sub> =8mA                                                       |                            | 6    | 8    | Ω  |

| Charging             | FET On Path                                             |                      |                                                                                                          |                            | 1    |      | •  |

| VOVP                 | OVP Threshold Voltage <sup>(13)</sup>                   | 3.8                  |                                                                                                          | 6.2                        | 6.6  | 7.0  | V  |

| RONFET               | Charging FET On Resistance <sup>(10)</sup>              |                      | V <sub>BUS</sub> =4.2V to 5.0V, I <sub>ON</sub> =1A                                                      |                            | 100  |      | mΩ |

| I <sub>OCP</sub>     | OCP Threshold Current <sup>(13)</sup>                   |                      |                                                                                                          | 1.1                        | 1.5  | 1.6  | Α  |

| I <sub>RUSH</sub>    | Charging FET Inrush Current<br>Limiting <sup>(13)</sup> |                      | C <sub>L</sub> =4.7µF Typical,<br>C <sub>L</sub> =10µF Maximum, Duration<br>= 100ms after Initial Attach |                            |      | 100  | mA |

| Audio R/I            | L Switch On Paths                                       |                      |                                                                                                          |                            |      |      |    |

| DC Audio             | Analog Signal Range                                     | 3.0 to 4.4           |                                                                                                          | 0                          |      | 3    | V  |

| AC Audio             | Analog Signal Range                                     | 3.0 to 4.4           |                                                                                                          | -1.5                       |      | 3.0  | V  |

| R <sub>ON</sub>      | Audio Switch On<br>Resistance <sup>(10,13)</sup>        | 3.8                  | V <sub>L/R</sub> =-0.8V, 0.8V,<br>I <sub>ON</sub> =30mA, f=0-470kHz                                      |                            | 2.0  | 3.0  | Ω  |

| R <sub>FLAT</sub>    | Audio R <sub>ON</sub> Flatness <sup>(11)</sup>          | 3.8                  |                                                                                                          |                            | 0.1  |      | Ω  |

| O make a l                          | Demonstern                                                                      | V 00                 | O an dition a                                       | T <sub>A</sub> = | -40 to + | .85°C | Unit |

|-------------------------------------|---------------------------------------------------------------------------------|----------------------|-----------------------------------------------------|------------------|----------|-------|------|

| Symbol                              | Parameter                                                                       | V <sub>BAT</sub> (V) | Conditions                                          | Min.             | Тур.     | Max.  | Unit |

| Video Au                            | dio R/L Switch On Paths                                                         |                      | ·                                                   |                  |          |       |      |

| DC Audio                            | Analog Signal Range <sup>(14)</sup>                                             | 3.0 to 4.4           |                                                     | 0                |          | 3     | V    |

| AC Audio                            | Analog Signal Range <sup>(14)</sup>                                             | 3.0 to 4.4           |                                                     | -1.5             |          | 3.0   | V    |

| R <sub>ON</sub>                     | R <sub>ON</sub> Audio Switch On<br>Resistance <sup>(10,13)</sup>                |                      | V <sub>L/R</sub> =0V, 1.6V,                         |                  | 2.8      | 5.0   | Ω    |

| R <sub>FLAT</sub>                   | Audio R <sub>ON</sub> Flatness <sup>(11,13)</sup>                               | 3.0 to 4.4           | I <sub>ON</sub> =30mA, f=0-470kHz                   |                  | 0.2      | 0.4   | Ω    |

| MIC Switch On Path                  |                                                                                 |                      |                                                     |                  |          |       |      |

| Analog Signal Range <sup>(12)</sup> |                                                                                 | 3.0 to 4.4           |                                                     | 0                |          | 4.4   | V    |

| R <sub>ON</sub>                     | Switch On Resistance <sup>(10)</sup>                                            | 3.0 to 4.4           | V <sub>SW</sub> =1.4 to 1.8V, I <sub>ON</sub> =30mA | 25               | 40       | 52    | Ω    |

| IDBP and                            | I Video Switch On Paths                                                         |                      |                                                     |                  |          |       |      |

| Analog Si                           | gnal Range                                                                      | 3.0 to 4.4           |                                                     | 0                |          | 4.4   | V    |

| R <sub>ON</sub>                     | Switch On Resistance <sup>(10,13)</sup>                                         | 3.0 to 4.4           | V <sub>SW</sub> =0V, 4.4V, I <sub>ON</sub> =30mA    | 10               | 15       | 20    | Ω    |

| Total Sw                            | itch Current Consumption                                                        |                      |                                                     |                  |          |       |      |

| I <sub>CCSLNA</sub>                 | Battery Supply Sleep Mode<br>Current No Accessory Attached                      | 3.8                  | Static Current During Sleep<br>Mode                 |                  | 9        | 15    | μA   |

| Iccslwa                             | Battery Supply Sleep Mode<br>Current with Accessory<br>Attached <sup>(13)</sup> | 3.8                  | Static Current During Sleep<br>Mode                 |                  | 30       | 40    | μA   |

| Іссик                               | Battery Supply Active Mode Current <sup>(13)</sup>                              | 3.8                  | Average Pulse Current<br>(~100µs Pulse)             |                  | 2.5      | 3     | mA   |

#### Notes:

9. Does not apply to CHG\_DET or JIG pins.

10. On resistance is determined by the voltage drop between the A and B pins at the indicated current through the switch.

11. Flatness is defined as the difference between the maximum and minimum values of on resistance over the specified range of conditions.

12. The MIC bias applied by the phone should not exceed 3.5V.

13. Guaranteed by characterization data.

14. Negative swing audio is not recommended when the switch is open.

## Capacitance

| Symbol                  | Parameter                           |                      | Conditions                      | T <sub>A</sub> =- | Unit |      |      |

|-------------------------|-------------------------------------|----------------------|---------------------------------|-------------------|------|------|------|

| Symbol Parameter        |                                     | V <sub>BAT</sub> (V) | Conditions                      | Min.              | Тур. | Max. | Unit |

| $C_{\text{INOFF}}$      | Host Interface Pins Off Capacitance | 3.8                  | V <sub>BIAS</sub> =0V           |                   | 10   |      | pF   |

| C <sub>ON(D+, D-)</sub> | D+, D- On Capacitance (USB Mode)    | 3.8                  | V <sub>BIAS</sub> =0.2V, f=1MHz |                   | 8    |      | pF   |

## I<sup>2</sup>C<sup>™</sup> Controller DC Characteristics

| Symbol           | Peremeter                                                |                       | Fast M        | ode (400k            | (Hz) |

|------------------|----------------------------------------------------------|-----------------------|---------------|----------------------|------|

| Symbol           | Parameter                                                | Min.                  | Max.          | Unit                 |      |

| VIL              | Low-Level Input Voltage                                  |                       | -0.5          | 0.3V <sub>DDIO</sub> | V    |

| V <sub>IH</sub>  | High-Level Input Voltage                                 |                       | $0.7V_{DDIO}$ |                      | V    |

| V                | Low-Level Output Voltage at 3mA Sink Current             | V <sub>DDIO</sub> >2V | 0             | 0.4                  | v    |

| V <sub>OL1</sub> | (Open-Drain or Open-Collector)                           | V <sub>DDIO</sub> <2V |               | 0.2V <sub>DDIO</sub> | v    |

| li -             | Input Current of Each I/O Pin, Input Voltage 0.26V to 2. | .34V                  | -10           | 10                   | μA   |

| Cı               | Capacitance for Each I/O Pin                             |                       |               | 10                   | pF   |

## Switch Path AC Electrical Characteristics

All typical value are for  $V_{BAT}$ =3.8V at 25°C unless otherwise specified.

| Symbol             | Dexemptor                                             | Parameter  |                                                                                                                                | V <sub>BAT</sub> (V) Conditions                      |      | T <sub>A</sub> = -40 to +85°C |      |      |

|--------------------|-------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|-------------------------------|------|------|

| Symbol             | Parameter                                             |            | V <sub>BAT</sub> (V)                                                                                                           | Conditions                                           | Min. | Тур.                          | Max. | Unit |

| Xtalk              | Non-Adjacent Channel                                  | Audio Mode | 3.8                                                                                                                            | f=20kHz, R⊤=32Ω,<br>C <sub>L</sub> =0pF              |      | -50                           |      | dB   |

| Aldik              | Crosstalk                                             | USB Mode   | 3.8                                                                                                                            | f=1MHz, R <sub>T</sub> =50Ω,<br>C <sub>L</sub> =0pF  |      | -60                           |      | uБ   |

|                    | Official                                              | Audio Mode | 3.8                                                                                                                            | f=20kHz, R⊤=32Ω,<br>C <sub>L</sub> =0pF              |      | -100                          |      | dB   |

| UIRR               | O <sub>IRR</sub> Off Isolation                        |            | 3.8                                                                                                                            | f=1 MHz, R <sub>T</sub> =50Ω,<br>C <sub>L</sub> =0pF |      | -60                           |      | uБ   |

| PSRR               | Power Supply Rejection Ra                             | 3.8        | Power Supply Noise<br>300mV <sub>PP</sub> , f=217Hz on<br>MIC, DP_Con,<br>DM_Con                                               |                                                      | -100 |                               | dB   |      |

| t <sub>SK(P)</sub> | Skew of Opposite Transition<br>Same Output (USB Mode) | 3.8        | t <sub>r</sub> =t <sub>f</sub> =750ps (10-90%)<br>at 240MHz, C∟=0pF,<br>R <sub>L</sub> =50Ω                                    |                                                      | 35   | F                             | ps   |      |

| tj                 | Total Jitter (USB Mode)                               | 3.8        | $R_L$ =50Ω, C <sub>L</sub> =50pF,<br>t <sub>r</sub> =t <sub>f</sub> =500ps (10-90%)<br>at 480Mbps<br>(PRBS=2 <sup>15</sup> -1) |                                                      | 130  |                               | ps   |      |

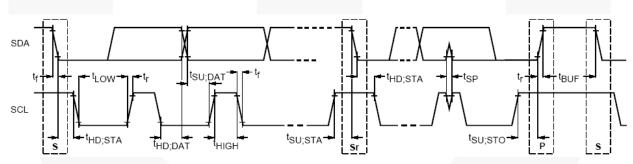

## I<sup>2</sup>C<sup>™</sup> AC Electrical Characteristics

| Sumhel              | Doromotor                                                         | Fast Mode           |      |      |  |  |

|---------------------|-------------------------------------------------------------------|---------------------|------|------|--|--|

| Symbol              | Parameter                                                         | Min.                | Max. | Unit |  |  |

| f <sub>SCL</sub>    | SCL Clock Frequency                                               | 0                   | 400  | kHz  |  |  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6                 |      | μs   |  |  |

| t <sub>LOW</sub>    | Low Period of SCL Clock                                           | 1.3                 |      | μs   |  |  |

| t <sub>HIGH</sub>   | High Period of SCL Clock                                          | 0.6                 |      | μs   |  |  |

| t <sub>su;sta</sub> | Set-up Time for Repeated START Condition                          | 0.6                 |      | μs   |  |  |

| t <sub>HD;DAT</sub> | Data Hold Time                                                    | 0                   | 0.9  | μs   |  |  |

| t <sub>SU;DAT</sub> | Data Set-Up Time                                                  | 100 <sup>(15)</sup> |      | ns   |  |  |

| tr                  | Rise Time of SDA and SCL Signals <sup>(16)</sup>                  | 20+0.1Cb            | 300  | ns   |  |  |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals <sup>(16)</sup>                  | 20+0.1Cb            | 300  | ns   |  |  |

| t <sub>su;sто</sub> | Set-up Time for STOP Condition                                    | 0.6                 |      | μs   |  |  |

| t <sub>BUF</sub>    | Bus Free Time between a STOP and START Conditions                 | 1.3                 |      | μs   |  |  |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0                   | 50   | ns   |  |  |

#### Note:

15. A fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>su,DAT</sub> ≥ 250ns must be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If the device stretches the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>r max</sub> + t<sub>su,DAT</sub>=1000+250=1250ns (according to the standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released.

C<sub>b</sub> equals the total capacitance of one bus line in pf. If mixed with high-speed mode devices, faster fall times are allowed according to the I<sup>2</sup>C specification.

Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C-bus

| Nam      | e                           | Size (E             | Bits)          |                 |                  |                   |                  |                   |                   |                     |                 |

|----------|-----------------------------|---------------------|----------------|-----------------|------------------|-------------------|------------------|-------------------|-------------------|---------------------|-----------------|

| Slave Ad | draga                       | 8                   |                | Bit 7           | Bit 6            | Bit 5             | Bit 4            | Bit 3             | Bit 2             | Bit 1               | Bit 0           |

| Slave Au | uless                       | 0                   |                | 0               | 1                | 0                 | 0                | 1                 | 0                 | 1                   | R/W             |

| Table 6. | l²C™ Re                     | gister              | Мар            |                 |                  |                   |                  |                   |                   |                     |                 |

| Address  | Register                    | Туре                | Reset<br>Value | Bit 7           | Bit 6            | Bit 5             | Bit 4            | Bit 3             | Bit 2             | Bit 1               | Bit 0           |

| 01H      | Device ID                   | R                   | N/A            |                 |                  | Version ID        |                  |                   |                   | Vendor ID           |                 |

| 02H      | Control                     | R/W                 | XXX11111       | Reserved        | Reserved         | Reserved          | Switch<br>Open   | RAW Data          | Manual<br>S/W     | Wait                | INT Mask        |

| 03H      | Interrupt 1 <sup>(17)</sup> | R                   | 00000000       | OVP_OCP<br>_DIS | OCP_EN           | OVP_EN            | LKR              | LKP               | KP                | Detach              | Attach          |

| 04H      | Interrupt 2 <sup>(17)</sup> | R                   | XXX00000       | Reserved        | Reserved         | Reserved          | Stuck Key<br>RCV | Stuck Key         | ADC<br>Change     | Reserved<br>Attach  | A/V<br>Charging |

| 05H      | Interrupt<br>Mask 1         | R/W                 | 00000000       | OVP_OCP<br>_DIS | OCP_EN           | OVP_EN            | LKR              | LKP               | KP                | Detach              | Attach          |

| 06H      | Interrupt<br>Mask 2         | R/W                 | XXX00000       | Reserved        | Reserved         | Reserved          | Stuck Key<br>RCV | Stuck Key         | ADC<br>Change     | Reserved<br>Attach  | A/V<br>Charging |

| 07H      | ADC                         | R                   | XXX11111       | Reserved        | Reserved         | Reserved          |                  | ADC Value         |                   |                     |                 |

| 08H      | Timing Set 1                | R/W                 | 00000100       |                 | Keyl             | Press             |                  |                   | Device V          | Vake Up             |                 |

| 09H      | Timing Set 2                | R/W                 | 00000000       |                 | Switchi          | ng Wait           | 1                |                   | Long Ke           | ey Press            |                 |

| 0AH      | Device Type<br>1            | R                   | 00000000       | USB OTG         | Dedicated<br>CHG | USB<br>Charger    | Car kit          | UART              | USB               | Audio Type<br>2     | Audio Type<br>1 |

| 0BH      | Device Type<br>2            | R                   | X0000000       | Reserved        | A/V              | TTY               | PPD              | Jig UART<br>Off   | Jig UART<br>On    | Jig USB<br>Off      | Jig USB<br>On   |

| 0CH      | Button 1                    | R                   | 00000000       | 7               | 6                | 5                 | 4                | 3                 | 2                 | 1                   | Send End        |

| 0DH      | Button 2                    | R                   | X0000000       | Reserved        | Unknown          | Error             | 12               | 11                | 10                | 9                   | 8               |

| 0EH      | Car Kit<br>Status           | R/W <sup>(18)</sup> | X0000100       | Reserved        | DISC_Req<br>uest | UART<br>Traffic   |                  | Mode              |                   | Ту                  | rpe             |

| 0FH      | Car Kit Int 1               | R                   | 00000000       | CR_UART         | PH_Disc          | PH_DDA_<br>Stereo | PH_DDA_<br>Mono  | PH_Aud_<br>Stereo | PH_Aud_M<br>ono   | PH_UART             | PH_Init         |

| 10H      | Car Kit Int 2               | R                   | XXXXX000       | Reserved        | Reserved         | Reserved          | Reserved         | Reserved          | CR_DDA_<br>Stereo | CR_Stereo           | CR_Mono         |

| 11H      | Car Kit Int<br>Mask 1       | R/W                 | 00000000       | CR_UART         | PH_Disc          | PH_DDA_<br>Stereo | PH_DDA_<br>Mono  | PH_Aud_<br>Stereo | PH_Aud_M<br>ono   | PH_UART             | PH_Init         |

| 12H      | Car Kit Int<br>Mask 2       | R/W                 | XXXXX000       | Reserved        | Reserved         | Reserved          | Reserved         | Reserved          | CR_DDA_<br>Stereo | CR_Stereo           | CR_Mono         |

| 13H      | Manual SW 1                 | R/W                 | 00000000       |                 | D- Switching     | 1                 |                  | D+ Switching      | 1                 | V <sub>BUS</sub> sv | vitching        |

| 14H      | Manual SW 2                 | R/W                 | XXX00000       | Reserved        | Reserved         | Reserved          | Reserved         | BOOT SW           | JIG ON            | ID Sw               | itching         |

Notes:

17. The following four bit pairs are mutually exclusive; OVP\_EN/OVP\_DIS, Stuck\_Key/Stuck\_Key\_Rcv, LKP/LKR, Detach/Attach. If the FSA9480 writes either bit in these pairs before its counterpart has been read and cleared, the FSA9480 clears the first bit before writing the second bit in the mutually exclusive pair. This ensures only one bit from each pair is ever HIGH.

18. Bits 0 and 1 of the Car Kit Status Register 0EH cannot be written.

#### Table 7. Device ID

- Address: 01h

- Type: Read

| Bit # | Name       | Size (Bits) | Description                  |

|-------|------------|-------------|------------------------------|

| 7:3   | Version ID | 5           | Rev1.0, Rev 1.1 : 000000     |

|       |            |             | Rev2.0: 00001                |

|       |            |             | Rev2.1: 00010                |

|       |            |             | Rev3.0: 00011                |

|       |            |             | Rev3.1: 00100                |

|       |            |             | Rev3.2: 00101                |

| 2:0   | Vendor ID  | 3           | 000: Fairchild Semiconductor |

| -     |            |             |                              |

#### Table 8. Control

- Address: 02h

- Reset Value: xxx11111

- Type: Read/Write

| Bit # | Name          | Size (Bits) | Description                                                                                                                 |                                                                  |

|-------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 7:5   | Reserved      | 3           | NA                                                                                                                          |                                                                  |

| 1     | 4 Switch Open |             | 1                                                                                                                           | 0: Open all switches                                             |

| 4     |               | I           | 1: Automatic switching by accessory status                                                                                  |                                                                  |

| 3     | RAW Data      | 1           | 0: Report the status changes on ID to HOST                                                                                  |                                                                  |

| 3     | RAW Dala      | V Dala I    | 1: Don't report the status changes on ID to HOST                                                                            |                                                                  |

| 2     | Manual C/M    |             | Manual S/W 1                                                                                                                | 0: Manual switching mode (refer to attach flow diagram Figure 2) |

| 2     | Manual 5/W    | I           | 1: Automatic switching mode (refer to attach flow diagram Figure 2)                                                         |                                                                  |

| 1     | \M/oit        | 1           | 0: Keep all switches open until this bit is reset to 1 by the baseband; when reset to 1, immediately configure the switches |                                                                  |

| I     | 1 Wait        | 1           | <ol> <li>Wait for the duration of wait time specified in Timing Set Register before<br/>configuring switches</li> </ol>     |                                                                  |

| 0     | 0 INT Mask    | 1           | 0: Unmask interrupt – interrupt baseband on change of state in either Interrupt Register                                    |                                                                  |

|       |               |             | 1: Mask interrupt – do not interrupt baseband                                                                               |                                                                  |

#### Table 9. Interrupt 1

- Address: 03h

- Reset Value: 00000000

- Type: Read/Clear

| Bit # | Name        | Size (Bits) | Description             |  |

|-------|-------------|-------------|-------------------------|--|

| 7     | OVP_OCP_DIS | 1           | 1: OVP and OCP disabled |  |

| 6     | OCP_EN      | 1           | 1: OCP enabled          |  |

| 5     | OVP_EN      | 1           | 1: OVP enabled          |  |

| 4     | LKR         | 1           | 1: Long key release     |  |

| 3     | LKP         | 1           | 1: Long key press       |  |

| 2     | KP          | 1           | 1: Key press            |  |

| 1     | Detach      | 1           | 1: Accessory detached   |  |

| 0     | Attach      | 1           | 1: Accessory attached   |  |

#### Table 10. Interrupt 2

- Address: 04h

- Reset Value: xxx00000

#### Type: Read/Clear

| Bit # | Name            | Size (Bits) | Description                                    |

|-------|-----------------|-------------|------------------------------------------------|

| 7:5   | Reserved        | 3           | NA                                             |

| 4     | Stuck_Key_RCV   | 1           | 1: Stuck key is recovered                      |

| 3     | Stuck_Key       | 1           | 1: Stuck key is detected                       |

| 2     | ADC_Change      | 1           | 1: ADC value change (when RAW data is enabled) |

| 1     | Reserved_Attach | 1           | 1: Reserved device is attached                 |

| 0     | A/V_Charging    | 1           | 1: Charger detected when A/V cable is attached |

#### Table 11. Interrupt Mask 1

- Address: 05h

- Reset Value: 00000000

- Type: Read/Write

| Bit # | Name        | Size (Bits) | Description                            |  |

|-------|-------------|-------------|----------------------------------------|--|

| 7     | OVP_OCP_DIS | 1           | 1: Mask OVP and OCP disabled interrupt |  |

| 6     | OCP_EN      | 1           | 1: Mask OCP enabled interrupt          |  |

| 5     | OVP_EN      | 1           | 1: Mask OVP enabled interrupt          |  |

| 4     | LKR         | 1           | 1: Mask long key release interrupt     |  |

| 3     | LKP         | 1           | 1: Mask long key press interrupt       |  |

| 2     | KP          | 1           | 1: Mask key press interrupt            |  |

| 1     | Detach      | 1           | 1: Mask detach interrupt               |  |

| 0     | Attach      | 1           | 1: Mask attach interrupt               |  |

#### Table 12. Interrupt Mask 2

- Address: 06h

- Reset Value: xxx00000

- Type: Read/Write

| Bit # | Name            | Size (Bits) | Description                                              |

|-------|-----------------|-------------|----------------------------------------------------------|

| 7:5   | Reserved        | 3           | NA                                                       |

| 4     | Stuck_Key_RCV   | 1           | 1: Mask stuck key recovered interrupt                    |

| 3     | Stuck_Key       | 1           | 1: Mask stuck key Interrupt                              |

| 2     | ADC_Change      | 1           | 1: Mask ADC value change interrupt                       |

| 1     | Reserved_Attach | 1           | 1: Mask reserved device interrupt                        |

| 0     | A/V_Charging    | 1           | 1: Mask charger detect when A/V cable attached interrupt |