# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Future Technology Devices International Ltd. FT121 (Enhanced USB Device Controller with SPI Slave IC)

The FT121 is a USB generic interface controller with the following advanced features:

- USB 2.0 Full Speed compatible

- High performance USB device controller with integrated SIE, endpoint buffer, transceiver and voltage regulators

- Fully integrated clock generation with no external crystal required

- Supports Serial Parallel interface (SPI) slave to external microcontroller

- Supports up to 8 bi-directional endpoints with total 2K bytes endpoint buffer

- Max packet size is 504 bytes for isochronous endpoint and 64 bytes for control/bulk/interrupt endpoint

- Double buffer scheme for any endpoint increases data transfer throughput

- Multiple interrupt modes to facilitate both bulk and isochronous transfers

- USB Battery Charger detection allowing optimized charging profile

- Integrated DP pull-up resistor for USB connection

- Supports bus powered or self powered application

- VCC power supply operation at 3.3V or 5V

- Internal 1.8V and 3.3V LDO regulators

- VCC IO level range from 1.8V to 3.3V

- Integrated power-on-reset circuit

- UHCI/OHCI/EHCI host controller compatible

- -40°C to 85°C extended operating temperature range

- Available in Pb-free TSSOP-16 and QFN-16 packages (RoHS compliant)

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied. Future Technology Devices International Ltd will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury. This document provides preliminary information that may be subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Future Technology Devices International Ltd, Unit 1, 2 Seaward Place, Centurion Business Park, Glasgow G41 1HH United Kingdom. Scotland Registered Company Number: SC136640

## **1** Typical Applications

- Provide USB port to Microcontrollers

- USB Industrial Control

- Mass storage data transfers for multitude of embedded systems applications, including medical, industrial data-logger, powermetering, and test instrumentation

- Provide USB port to FPGA's

- Utilising USB to add system modularity

- Isochronous support for video applications in security, industrial control, and quality inspections

### 1.1 Part Numbers

| Part Number | Package  |

|-------------|----------|

| FT121T-x    | TSSOP-16 |

| FT121Q-x    | QFN-16   |

Note: Packaging codes for x is:

- R: Taped and Reel, (TSSOP is 2,500pcs per reel, QFN is 6,000pcs per reel).

- U: Tube packing, 96pcs per tube (TSSOP only)

- T: Tray packing, 490pcs per tray (QFN only)

For example: FT121T-R is 2,500pcs taped and reel packing

## 1.2 USB Compliant

At the time of writing this datasheet, the FT121 was in the process of completing USB compliance testing.

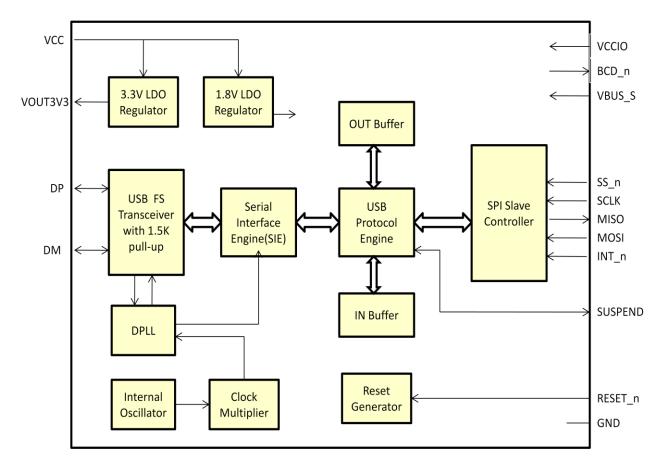

## 2 Block Diagrams

#### Figure 2-1 FT121 Block Diagram

For a description of each function please refer to Section 4.

## **Table of Contents**

| 1                                                                                                                        | Ту                                                                                                  | pical Applications2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | )                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                      | Ρ                                                                                                   | art Numbers 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                                                                                                    |

| 1.2                                                                                                                      | U                                                                                                   | SB Compliant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                                                    |

| 2                                                                                                                        | Blo                                                                                                 | ock Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                                                    |

| 3                                                                                                                        | De                                                                                                  | vice Pin Out and Signal Description6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                                                                                                    |

| 3.1                                                                                                                      |                                                                                                     | SSOP-16 Package Pin Out6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

| 3.2                                                                                                                      |                                                                                                     | PN-16 Package Pin Out6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

| 3.3                                                                                                                      |                                                                                                     | in Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| 4                                                                                                                        |                                                                                                     | nction Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

| 4.1                                                                                                                      |                                                                                                     | unctional Block Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |

| 4.2                                                                                                                      |                                                                                                     | nterrupt Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| 4.3                                                                                                                      |                                                                                                     | PI Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |

| <b>4.</b> 3                                                                                                              | _                                                                                                   | 4-wire write operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

| 4.3                                                                                                                      |                                                                                                     | 4-wire read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                      |

| 4.3                                                                                                                      |                                                                                                     | 3-wire write operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

| 4.3                                                                                                                      |                                                                                                     | 3-wire read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                      |

| 5                                                                                                                        | End                                                                                                 | dpoint Buffer Management13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |

| 5.1                                                                                                                      |                                                                                                     | ndpoint Buffer Management in Default Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                      |

| 011                                                                                                                      |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

| 52                                                                                                                       | F                                                                                                   | ndpoint Buffer Management in Enhanced Mode 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L                                                                                                                    |

| 5.2<br>6                                                                                                                 |                                                                                                     | ndpoint Buffer Management in Enhanced Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |

| 6                                                                                                                        | Co                                                                                                  | mmands and Registers16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                                                                    |

| 6<br>6.1                                                                                                                 | Co<br>C                                                                                             | mmands and Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                                                                                                    |

| 6<br>6.1<br>6.2                                                                                                          | Co<br>C<br>I                                                                                        | mmands and Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

| 6<br>6.1<br>6.2                                                                                                          | Co<br>C<br>I<br>2.1                                                                                 | mmands and Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

| 6<br>6.1<br>6.2<br>6.2                                                                                                   | Cor<br>C<br>I<br>2.1<br>2.2                                                                         | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| 6<br>6.1<br>6.2<br>6.2<br>6.2                                                                                            | Col<br>C<br>I<br>2.1<br>2.2<br>2.3                                                                  | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

| 6<br>6.1<br>6.2<br>6.2                                                                                                   | Cor<br>C<br>I<br>2.1<br>2.2<br>2.3<br>2.4                                                           | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2                                                                                     | Cor<br>C<br>I<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                    | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       23         Set Endpoint Configuration (for Enhanced Mode)       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2                                                                              | Cor<br>C<br>11<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D                                              | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3                                                                       | Coi<br>C<br>I<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D<br>3.1                                        | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       23         Set Endpoint Configuration (for Enhanced Mode)       23         Pata Flow Commands       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3                                                                | Con<br>C<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D<br>3.1<br>3.2                                      | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       22         Set Endpoint Configuration (for Enhanced Mode)       23         Set Afflow Commands       24         Read Interrupt Register       24                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>5</b><br><b>1</b><br><b>1</b><br><b>1</b><br><b>1</b><br><b>3</b><br><b>3</b><br><b>4</b><br><b>4</b><br><b>5</b> |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.3<br>6.3                                                         | Con<br>C<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D<br>3.1<br>3.2<br>3.3                               | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       21         Set Endpoint Configuration (for Enhanced Mode)       22         Pata Flow Commands       24         Read Interrupt Register       24         Select Endpoint       24                                                                                                                                                                                                                                                                                                                                                                    | 5<br>1<br>1<br>1<br>3<br>3<br>4<br>4<br>5<br>5<br>5                                                                  |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.3<br>6.3                                                         | Con<br>C<br>In<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D<br>3.1<br>3.2<br>3.3<br>3.4                  | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       22         Set Endpoint Configuration (for Enhanced Mode)       23         Set Flow Commands       24         Read Interrupt Register       24         Read Interrupt Register       24         Read Last Transaction Status       26                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3                                           | Con<br>C<br>11<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5           | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       22         Set Endpoint Configuration (for Enhanced Mode)       23         Set Endpoint Configuration (for Enhanced Mode)       24         Read Interrupt Register       24         Read Interrupt Register       26         Read Last Transaction Status       26         Read Endpoint Status       27                                                                                                                                                                                                                                                                                | •<br>•<br>•<br>•<br>•<br>•                                                                                           |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3                                    | Con<br>C<br>I<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6     | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       22         Set Interrupt       23         Set Endpoint Configuration (for Enhanced Mode)       23         Set Endpoint Configuration (for Enhanced Mode)       24         Read Interrupt Register       24         Read Interrupt Register       24         Read Interrupt Register       26         Read Last Transaction Status       26         Read Endpoint Status       27         Read Buffer       28         Vrite Buffer       28         Clear Buffer       28                                                                           | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                       |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3 | Con<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Mode       21         Set Interrupt       21         Set Interrupt       21         Set Interrupt       22         Set Interrupt       23         Set Endpoint Configuration (for Enhanced Mode)       22         Set Endpoint Configuration (for Enhanced Mode)       24         Read Interrupt Register       24         Read Interrupt Register       24         Read Last Transaction Status       26         Read Endpoint Status       26         Read Buffer       26         Write Buffer       26         Virie Buffer       26         Virie Buffer       26         Validate Buffer       26 | • • • • • • • • • • • • • • • • • • •                                                                                |

| 6<br>6.1<br>6.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3        | Con<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>D<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | mmands and Registers       16         ommand Summary       16         nitialization Commands       21         Set Address Enable       21         Set Address Enable       21         Set Endpoint Enable       21         Set Mode       21         Set Interrupt       22         Set Interrupt       23         Set Endpoint Configuration (for Enhanced Mode)       23         Set Endpoint Configuration (for Enhanced Mode)       24         Read Interrupt Register       24         Read Interrupt Register       24         Read Interrupt Register       26         Read Last Transaction Status       26         Read Endpoint Status       27         Read Buffer       28         Vrite Buffer       28         Clear Buffer       28                                                                           | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          |

|    |       |             | 1              |             |         |                |            |             |

|----|-------|-------------|----------------|-------------|---------|----------------|------------|-------------|

|    | 6.4   | General     |                | ds          |         |                |            |             |

|    | 6.4.3 | 1 Read Cur  | rrent Frame N  | Number      |         | <br>           |            |             |

|    | 6.4.2 | 2 Send Res  | sume           |             |         | <br>           |            |             |

|    | 6.4.3 | 3 Set 3-wi  | re Mode        |             |         | <br>           |            |             |

|    | 6.4.4 | 4 Set Buffe | er Interrupt M | 4ode        |         | <br>. Error! B | ookmark no | ot defined. |

|    | 6.4.  | 5 Read Ver  | ndor ID        |             |         | <br>           |            |             |

|    | 6.4.6 | 6 Read Pro  | duct ID        |             |         | <br>           |            |             |

|    | 6.4.2 | 7 Read FTI  | DI ID          |             |         | <br>           |            |             |

|    | 6.4.8 | 3 Set IO Pa | ad Drive Strer | ength       |         | <br>           |            |             |

| 7  | ļ     | Application | on Inforn      | mation      |         | <br>           |            | 32          |

| 8  | 0     | Devices C   | Character      | ristics and | Ratings | <br>           |            | 33          |

| 8  | 8.1   | Absolute    | e Maximur      | m Ratings   |         | <br>           |            | 33          |

| 2  | 8.2   |             |                | S           |         |                |            |             |

|    | 8.3   |             |                | s           |         |                |            |             |

|    |       |             |                |             |         |                |            |             |

| 9  |       | -           |                | ers         |         |                |            |             |

|    | 9.1   |             | -              | je Dimensio |         |                |            |             |

| 9  | 9.2   | TSSOP-1     | 6 Package      | je Markings | s       | <br>           |            | 38          |

| 9  | 9.3   | QFN-16      | Package D      | Dimensions  | 5       | <br>           |            | 39          |

| 9  | 9.4   | QFN-16      | Package        | Markings    |         | <br>           |            | 40          |

| 9  | 9.5   | Solder R    | eflow Pro      | ofile       |         | <br>           |            | 40          |

| 10 | 0 0   | Contact I   | nformati       | ion         |         | <br>           |            | 42          |

|    | Appe  | endix A –   | Reference      | es          |         | <br>           |            | 43          |

|    | Appe  | endix B - I | List of Fig    | ures and Ta | ables   | <br>           |            | 43          |

|    | Appe  | endix C - I | Revision H     | History     |         | <br>           |            | 45          |

|    |       |             |                | -           |         |                |            |             |

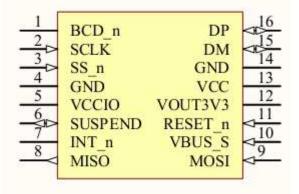

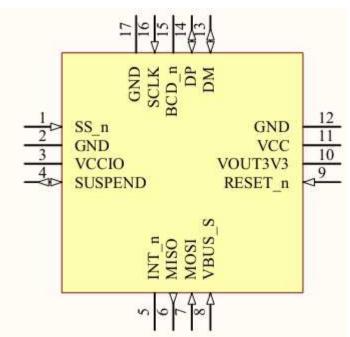

## **3** Device Pin Out and Signal Description

## 3.1 TSSOP-16 Package Pin Out

Figure 3-1 TSSOP-16 package schematic symbol

## 3.2 QFN-16 Package Pin Out

Figure 3-2 QFN-16 package schematic symbol

## 3.3 Pin Description

| PIN No.<br>(TSSOP-<br>16) | PIN No.<br>(QFN-<br>16) | PIN NAME | TYPE | DESCRIPTION                                                                                                             |  |

|---------------------------|-------------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------|--|

| 1                         | 15                      | BCD_n    | OD   | USB Charger detector output                                                                                             |  |

| 2                         | 16                      | SCLK     | Ι    | SPI clock input.                                                                                                        |  |

| 3                         | 1                       | SS_n     | I    | SPI slave select input.                                                                                                 |  |

| 4                         | 2                       | GND      | Р    | Ground.                                                                                                                 |  |

| 5                         | 3                       | VCCIO    | Р    | IO Supply Voltage; 1.8V, 2.5V or 3.3V                                                                                   |  |

| 6                         | 4                       | SUSPEND  | I,OD | Device suspend (output) and wakeup (input).                                                                             |  |

| 7                         | 5                       | INT_n    | OD   | Interrupt (Active Low).                                                                                                 |  |

| 8                         | 6                       | MISO     | 0    | 4-wire mode: SPI slave output.<br>3-wire mode: no function. Leave it un-connected.                                      |  |

| 9                         | 7                       | MOSI     | I/IO | 4-wire mode: SPI salve input<br>3-wire mode: SPI data input/output                                                      |  |

| 10                        | 8                       | VBUS_S   | I    | Vbus sensing input.                                                                                                     |  |

| 11                        | 9                       | RESET_n  | Ι    | Asynchronous reset (Active Low).                                                                                        |  |

| 12                        | 10                      | VOUT3V3  | Р    | 3.3V regulator output for 5V operation;<br>To operate the IC at 3.3 V, supply 3.3 V to both<br>the VCC and VOUT3V3 pins |  |

| 13                        | 11                      | VCC      | Р    | Power supply (3.3V or 5V)                                                                                               |  |

| 14                        | 12                      | GND      | Р    | Ground.                                                                                                                 |  |

| 15                        | 13                      | DM       | AIO  | USB data signal minus                                                                                                   |  |

| 16                        | 14                      | DP       | AIO  | USB data signal plus                                                                                                    |  |

| -                         | 17                      | GND      | Р    | Ground. Die pad for QFN-16 package.                                                                                     |  |

#### Table 3-1 FT121 Pin Description

Note: a) Pin name with suffix "\_n" denotes active low input/output signal.

b) Symbol used for pin TYPE:

- OD : Open Drain Output

- O : Output

- IO : Bi-directional Input and Output

- I : Plain input

- AIO : Analog Input and Output

- P : Power or ground

## **4** Function Description

The FT121 is a USB device controller which interfaces with microcontrollers via an SPI slave interface.

#### 4.1 Functional Block Descriptions

The following sections describe the function of each block. Please refer to the block diagram shown in **Figure 2-1**.

**+1.8V LDO Regulator.** The +1.8V LDO regulator generates the +1.8V reference voltage for the internal core of the IC with input capabilities from 3.3V or 5V.

**+3.3V LDO Regulator.** The +3.3V LDO regulator generates the +3.3V supply voltage for the USB transceiver. An external decoupling capacitor needs to be attached to the VOUT3V3 regulator output pin. The regulator also provides +3.3V power to the  $1.5k\Omega$  internal pull up resistor on DP pin. The allowable input voltages are 5V or 3.3V. When using 3.3V voltage as input voltage, the VCC and VOUT3V3 pins should be tied together. This will result in the regulator being by-passed.

**USB Transceiver.** The USB Transceiver cell provides the USB 1.1 / USB 2.0 full-speed physical interface. Output drivers provide +3.3V level slew rate control, while a differential input and two single ended input receivers provide data in, Single-Ended-0 (SE0) and USB reset detection conditions respectfully. A  $1.5k\Omega$  pull up resistor on DP is incorporated.

**DPLL.** The DPLL cell locks on to the incoming NRZI USB data and generates recovered clock and data signals.

**Internal Oscillator.** The Internal Oscillator cell generates a reference clock. This provides an input to the Clock Multiplier function.

**Clock Multiplier.** The 12MHz and 48MHz reference clock signals for various internal blocks can be generated from the reference clock via the oscillator functions and clock multiplier circuitry.

**Serial Interface Engine (SIE).** The Serial Interface Engine (SIE) block performs the parallel to serial and serial to parallel conversion of the USB data. In accordance with the USB 2.0 specification, it performs bit stuffing/un-stuffing and CRC5/CRC16 generation. It also checks the CRC on the USB data stream.

**USB Protocol Engine.** The USB Protocol Engine manages the data stream from the device USB control endpoint. It handles the low level USB protocol requests generated by the USB host controller. The Protocol Engine also includes a memory management unit which handles endpoint buffers.

**OUT Buffer.** Data sent from the USB host controller to FT121 via the USB data OUT endpoint is stored in the OUT buffer. Data is removed from the OUT buffer to system memory under control of the parallel interface block.

**IN Buffer.** Data from system memory is stored in the IN buffer. The USB host controller removes data from the IN buffer by sending a USB request for data from the device data IN endpoint.

**RESET Generator.** The integrated Reset Generator cell provides a reliable power-on reset to the device internal circuitry at power up. The RESET\_n input pin allows an external device to reset the FT121.

**SPI Controller Block.** The SPI slave controller provides control and data interfaces between the external MCU and internal registers and endpoint buffers. It supports 4-wire (default) or 3-wire SPI operation.

### **4.2 Interrupt Modes**

The FT121 interrupt pin (INT\_n) can be programmed to generate an interrupt in different modes. The interrupt source can be any bit in the Interrupt Register, or receiving SOF packet, or both. The interrupt modes are selectable by two register bits, one is the SOF-only Interrupt Mode bit (bit 7 of Clock Division Factor register), and the other is the Interrupt Pin Mode bit (bit 5 of Interrupt Configuration register).

| Interrupt<br>mode | Bit SOF-only<br>Interrupt<br>Mode | Bit Inter <b>r</b> upt<br>Pin Mode | Interrupt source                      |

|-------------------|-----------------------------------|------------------------------------|---------------------------------------|

| 0                 | 0                                 | 0                                  | Any bit in Interrupt register         |

| 1                 | 0                                 | 1                                  | Any bit in Interrupt register and SOF |

| 2                 | 1                                 | х                                  | SOF only                              |

Table 4-1 Interrupt modes

## 4.3 SPI Slave Interface

The SPI slave interface supports 4-wire (default) and 3-wire operation. In 4-wire operation the SPI master will drive data on MOSI pin and the SPI slave will drive data on MISO pin. In 3-wire operation both SPI master and SPI slave share the same data pin (MOSI pin becomes bi-directional pin). Upon power-on or hardware reset, the FT121 SPI slave interface is in 4-wire mode. The 3-wire operation is enabled when a Set 3-wire command is issued to FT121.

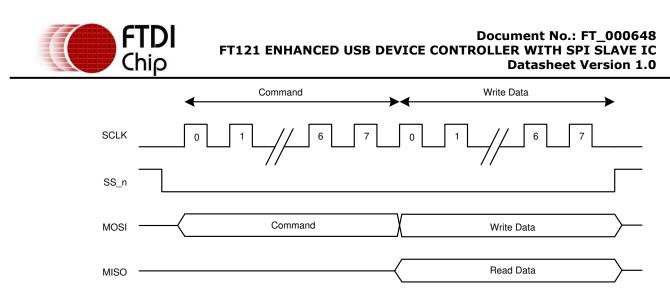

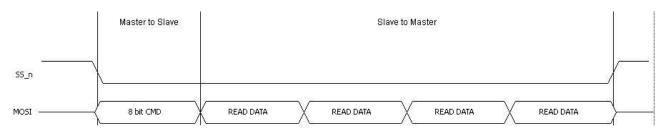

The SPI protocol will follow a command + data format where a command is transmitted after SS\_n is asserted and each subsequent byte will be a data byte. When all data bytes for this command are completed the SS\_n is de-asserted. This can be seen in Figure 4-1.

Figure 4-1 SPI access

The SPI slave supports SPI mode 1 (CPOL=0, CPHA=1). This means the rising edge is the driving edge while the falling edge is the sample edge. The drive edge is always before the sample edge.

The maximum SPI clock supported is 20MHz, for both 4-wire and 3-wire modes. Refer to the AC characteristics section for SPI timing figures.

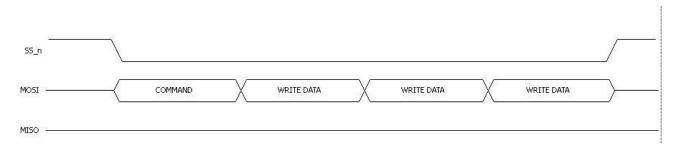

#### 4.3.1 4-wire write operation

When the SPI master performs data write operation, it drives the SS\_n line low, send the 8-bit command byte on MOSI line, followed by sending the data bytes. The length of the data byte ranges from 0 to maximum 506, depending on the command type. The master will signal the end of the data write operation by drive the SS\_n line high.

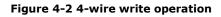

#### 4.3.2 4-wire read operation

When the SPI master performs data read operation, it drives the SS\_n line low, send the 8-bit command byte on MOSI line. The FT121 will output data bytes on the MISO line. The length of the data byte ranges from 0 to maximum 506, depending on the command type. The master will signal the end of the data read operation by drive the SS\_n line high.

|                                           | \ |           |           |           |

|-------------------------------------------|---|-----------|-----------|-----------|

| мозі ———————————————————————————————————— |   |           | <br>      |           |

| MISO                                      | ( | READ DATA | READ DATA | $\supset$ |

Figure 4-3 4-wire read operation

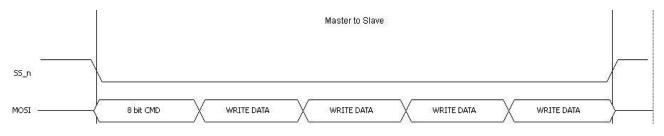

### 4.3.3 3-wire write operation

When the SPI master performs data write operation, it drives the SS\_n line low, send the 8-bit command byte on MOSI line, followed by sending the data bytes. The length of the data byte ranges from 0 to maximum 506, depending on the command type. The master will signal the end of the data write operation by drive the SS\_n line high.

Figure 4-4 3-wire write operation

### 4.3.4 3-wire read operation

When the SPI master performs data read operation, it drives the SS\_n line low, send the 8-bit command byte on MOSI line. The master will stop driving the MOSI line. The FT121 will output data bytes on the MOSI line. The length of the data byte ranges from 0 to maximum 506, depending on the command type. The master will signal the end of the data read operation by drive the SS\_n line high.

It is important that bus contention should be avoided during the bus turnaround period – i.e. moving from the command byte to a read byte. In this instance the master will stop driving at the same clock edge (rising edge) as the slave starts to drive. To avoid bus contention the FT121 will implement delays so that it only start to drive the MOSI line at least 5ns after the SCLK driving edge – this will give the master a minimum of 5ns to stop driving MOSI, which should ensure no bus contentions. At this bus turnaround point it's also more natural for a clash not to occur, as the master is the source of the clock, so will drive the clock and MOSI off at similar times. For the slave to drive MOSI it has to pass the clock

through the I/O buffers, into the internal circuits, clock MOSI and then get MOSI out through the output buffers. This long path in and out of the slave will have an inherent delay of a few nanoseconds.

### 5 Endpoint Buffer Management

The FT121 has 2 modes of operation for command and memory management: the default mode and the enhanced mode. The buffer management schemes are different in these two modes. Upon reset the default mode is functional. The enhanced mode is activated when any of the Set Endpoint Configuration command (B0h – BFh) is received.

## 5.1 Endpoint Buffer Management in Default Mode

In default mode the FT121 has 3 bi-directional endpoints (EP0, EP1 and EP2). EP0 is the control endpoint, with 16 bytes maximum packet size for both the control OUT and control IN endpoints. EP1 can be used as either a bulk endpoint or an interrupt endpoint, with 16 bytes maximum packet size for both OUT and IN endpoints. Table 5-1 shows the endpoint type and maximum packet size for EP0 and EP1.

| Endpoint<br>Number (EP) | Endpoint<br>Index (EPI) | Endpoint<br>Direction | Transfer Type  | Max Packet Size |

|-------------------------|-------------------------|-----------------------|----------------|-----------------|

| 0                       | 0                       | OUT                   | Control        | 16              |

|                         | 1                       | IN                    | Control        | 16              |

| 1                       | 2                       | OUT                   | Bulk/Interrupt | 16              |

|                         | 3                       | IN                    | Bulk/Interrupt | 16              |

Table 5-1 Endpoint configuration for EP0 and EP1

EP2 is the primary endpoint. It can be configured as either bulk/interrupt or isochronous endpoint. The maximum packet size allowed for EP2 depends on the mode of configuration through Set Mode command. Table 5-2 shows all the 4 endpoint configuration modes for EP2.

| EP2 Endpoint<br>Configuration<br>Mode | Endpoint<br>Index (EPI) | Endpoint<br>Direction | Transfer Type  | Max Packet Size |

|---------------------------------------|-------------------------|-----------------------|----------------|-----------------|

| 0                                     | 4                       | OUT                   | Bulk/Interrupt | 64              |

| (default)                             | 5                       | IN                    | Bulk/Interrupt | 64              |

| 1                                     | 4                       | OUT                   | Isochronous    | 128             |

| 2                                     | 5                       | IN                    | Isochronous    | 128             |

| 3                                     | 4                       | OUT                   | Isochronous    | 64              |

| Table 5-2 Ender                       | 5                       | IN                    | Isochronous    | 64              |

Table 5-2 Endpoint configuration for EP2

As the primary endpoint, EP2 is suitable for transmitting or receiving relatively large data. To improve the data throughput, EP2 is implemented with double buffereing. This allows the concurrent operation between USB bus access and MCU local bus access. For example, for EP2 IN endpoint (EPI5), the USB host can read data from FT121 Buffer 0 while the local MCU is writing to Buffer 1 at the same time. The USB host can subsequently read from FT121 Buffer 1 without waiting for it to be filled. Buffer switching is handled automatically by FT121.

## 5.2 Endpoint Buffer Management in Enhanced Mode

In enhanced mode the FT121 supports a dedicated 1kB buffer for IN packets and a dedicated 1kB buffer for OUT packets. The OUT/IN buffer can be allocated to any endpoint with the same direction, up to a maximum of 504 bytes double buffered (1008 bytes in total) to one endpoint. 504 is the maximum byte count as there are 1024 bytes in total per OUT/IN Buffer and 8 bytes for IN and OUT packets on control endpoint 0 must always be reserved. Control, interrupt and bulk endpoints can have a maximum packet size of 64 bytes and only isochronous endpoints can be allocated more than 64 bytes.

Isochronous modes can have larger buffer sizes as USB packets can be larger than 64 bytes for isochronous transfer. Isochronous buffers are managed in the same way as bulk, interrupt and control buffers – i.e. a buffer is for one USB packet only and will not span more than one USB packet.

An example of buffer configurations follows, where Configuration 1 and 2 have larger isochronous buffers.

|                                     | Config | uration 0 | Configu | ration 1 | Configu | ration 2 |

|-------------------------------------|--------|-----------|---------|----------|---------|----------|

|                                     | EP     | Buffer    | EP      | Buffer   | EP      | Buffer   |

|                                     | 7      | 1         | 7       | 4        |         |          |

| сk                                  | 7      | 0         | (ISO)   | I        |         |          |

| plo                                 | 6      | 1         | 7       | 0        |         |          |

| 'te I                               | 6      | 0         | (ISO)   | 0        | 5 (ISO) | 1        |

| by                                  | 5      | 1         | 6       | 1        |         |          |

| 64                                  | 5      | 0         | 6       | 0        |         |          |

| sa                                  | 4      | 1         | 2       | 1        |         |          |

| ate                                 | 4      | 0         | 2       | 0        |         |          |

| dic                                 | 3      | 1         |         |          |         |          |

| lin                                 | 3      | 0         | 1 (ISO) | 1        |         |          |

| cel                                 | 2      | 1         |         |          | 5 (ISO) | 0        |

| Each cell indicates a 64 byte block | 2      | 0         |         |          |         |          |

| Ш                                   | 1      | 1         | 1 (ISO) | 0        |         |          |

|                                     | 1      | 0         |         |          |         |          |

|                                     | 0      | 1         | 0       | 1        | 0       | 1        |

|                                     | 0      | 0         | 0       | 0        | 0       | 0        |

Table 5-3 Example buffer configuration

The endpoint buffer configurations, settable using the Set Endpoint Configuration command, are as follows:

| Endpoint buffer size register setting (0b') | Non-isochronous endpoint | Isochronous endpoint |

|---------------------------------------------|--------------------------|----------------------|

| 0000                                        | 8 bytes                  | 16 bytes             |

| 0001                                        | 16 bytes                 | 32 bytes             |

| 0010                                        | 32 bytes                 | 48 bytes             |

| 0011                                        | 64 bytes                 | 64 bytes             |

| 0100                                        | -                        | 96 bytes             |

| 0101                                        | -                        | 128 bytes            |

| 0110                                        | -                        | 160 bytes            |

| 0111                                        | -                        | 192 bytes            |

| 1000                                        | -                        | 256 bytes            |

| 1001                                        | -                        | 320 bytes            |

| 1010                                        | -                        | 384 bytes            |

| 1011                                        | -                        | 504 bytes            |

| 1100-1111                                   | -                        | -                    |

#### Table 5-4 Endpoint Maximum Packet Size

Note: 504 is the maximum byte count as there are 1024 bytes in total and 8 bytes IN and OUT packets for control endpoint 0 must always be reserved.

## 6 Commands and Registers

The FT121 supports two command sets: a default command set (Table 6-1) and an enhanced command set (Table 6-2). The enhanced command set is activated if any of the Set Endpoint Configuration commands (0xB0-0xBF) are received by the FT121. Otherwise, the default command set shall be valid.

## 6.1 Command Summary

| Command Name                 | Target             | Code (hex) | Data phase             |

|------------------------------|--------------------|------------|------------------------|

|                              | Initialization Com | mands      |                        |

| Set Address Enable           | Device             | D0h        | Write 1 byte           |

| Set Endpoint Enable          | Device             | D8h        | Write 1 byte           |

| Set Mode                     | Device             | F3h        | Write 2 bytes          |

| Set Interrupt                | Device             | FBh        | Write 1 byte           |

|                              | Data Flow Comn     | nands      |                        |

| Read Interrupt Register      | Device             | F4h        | Read 2 bytes           |

| Select Endpoint              | Endpoint 0 OUT     | 00h        | Read 1 byte (optional) |

|                              | Endpoint 0 IN      | 01h        | Read 1 byte (optional) |

|                              | Endpoint 1 OUT     | 02h        | Read 1 byte (optional) |

|                              | Endpoint 1 IN      | 03h        | Read 1 byte (optional) |

|                              | Endpoint 2 OUT     | 04h        | Read 1 byte (optional) |

|                              | Endpoint 2 IN      | 05h        | Read 1 byte (optional) |

| Read Last Transaction Status | Endpoint 0 OUT     | 40h        | Read 1 byte            |

|                              | Endpoint 0 IN      | 41h        | Read 1 byte            |

|                              | Endpoint 1 OUT     | 42h        | Read 1 byte            |

|                              | Endpoint 1 IN      | 43h        | Read 1 byte            |

|                              | Endpoint 2 OUT     | 44h        | Read 1 byte            |

|                              | Endpoint 2 IN      | 45h        | Read 1 byte            |

| Read Endpoint Status         | Endpoint 0 OUT     | 80h        | Read 1 byte            |

|                              | Endpoint 0 IN      | 81h        | Read 1 byte            |

|                              | Endpoint 1 OUT     | 82h        | Read 1 byte            |

|                              | Endpoint 1 IN      | 83h        | Read 1 byte            |

|                              | Endpoint 2 OUT     | 84h        | Read 1 byte            |

| Command Name              | Target            | Code (hex) | Data phase           |  |

|---------------------------|-------------------|------------|----------------------|--|

|                           | Endpoint 2 IN     | 85h        | Read 1 byte          |  |

| Read Buffer               | Selected Endpoint | E0h        | Read multiple bytes  |  |

| Write Buffer              | Selected Endpoint | F0h        | Write multiple bytes |  |

| Set Endpoint Status       | Endpoint 0 OUT    | 50h        | Write 1 byte         |  |

|                           | Endpoint 0 IN     | 51h        | Write 1 byte         |  |

|                           | Endpoint 1 OUT    | 52h        | Write 1 byte         |  |

|                           | Endpoint 1 IN     | 53h        | Write 1 byte         |  |

|                           | Endpoint 2 OUT    | 54h        | Write 1 byte         |  |

|                           | Endpoint 2 IN     | 55h        | Write 1 byte         |  |

| Acknowledge Setup         | Selected Endpoint | F1h        | None                 |  |

| Clear Buffer              | Selected Endpoint | F2h        | None                 |  |

| Validate Buffer           | Selected Endpoint | FAh        | None                 |  |

| General Commands          |                   |            |                      |  |

| Read Current Frame Number | Device            | F5h        | Read 1 or 2 bytes    |  |

| Send Resume               | Device            | F6h        | None                 |  |

Table 6-1 FT121 default command set

| Command Name               | Target         | Code (hex) | Data phase    |  |  |

|----------------------------|----------------|------------|---------------|--|--|

| Initialization Commands    |                |            |               |  |  |

| Set Address Enable         | Device         | D0h        | Write 1 byte  |  |  |

| Set Endpoint Enable        | Device         | D8h        | Write 1 byte  |  |  |

| Set Mode                   | Device         | F3h        | Write 2 bytes |  |  |