# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconduc

July 2012

SEMICONDUCTOR

## FXMHD103 — HDMI Voltage Translator

## Features

- CEC, DDC, and HPD Level Shifting without a Direction Pin

- Host Port Voltage Supply (V<sub>CCA</sub>): 1.6V 3.6V

- HDMI Port Voltage Supply (V<sub>CCC</sub>): 4.8V 5.3V

- Long HDMI Cable Support with Integrated DDC (I<sup>2</sup>C) Edge Rate Accelerators

- Supports DDC (I<sup>2</sup>C) Clock Stretching

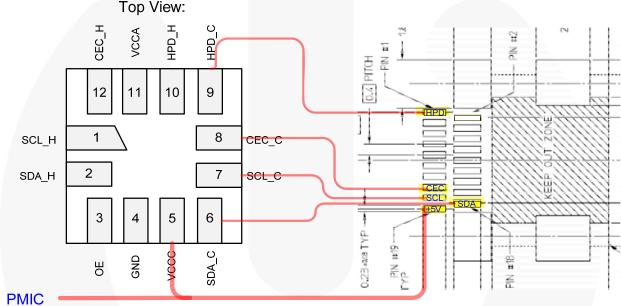

- Pin Out Tailored for PCB Trace Routing to HDMI Type D Connectors

- Back Drive Protection

- Non-Preferential Power-Up/Down Sequencing between VCCA and VCCC

- Operating Temperature Range: -40°C to 85°C

- ESD Protection:

- 8kV HBM (per JESD22-A114)

- 2kV CDM (per JESD22-C101)

## Applications

- Smart Phones

- Multimedia Phones

- Digital Camcorders

- Digital Still Cameras

- Portable Game Consoles

- Notebooks

- MP3 Players

- PC and Consumer Electronics

## Description

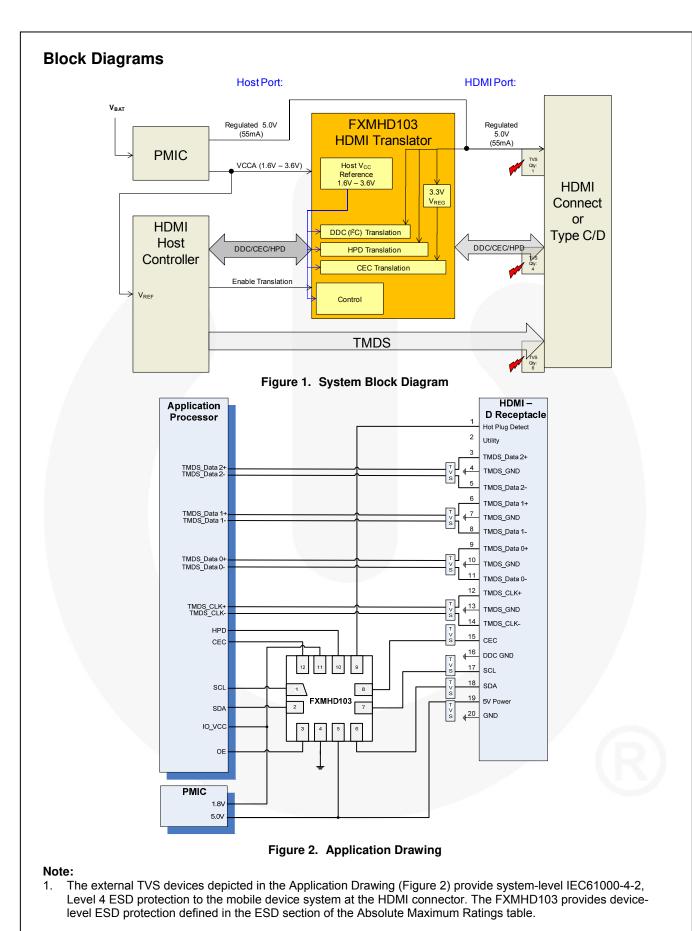

The FXMHD103 is a reduced-pin-count, low-power, High-Definition Multimedia Interface (HDMI), voltage translator for the Data Display Channel (DDC), Consumer Electronic Control (CEC), and Hot Plug Detect (HPD) control lines.

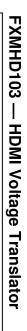

There are three non-inverting bi-directional voltage translation circuits for the DDC serial data (SDA)/clock (SCL) lines and CEC lines. Each line has a common power rail (V<sub>CCA</sub>) on the host side from 1.6V to 3.6V. On the HDMI connector side, the SCL\_C and SDA\_C pins each have an internal 1.75K $\Omega$  pull-up connected to the HDMI 5V rail, V<sub>CCC</sub>. The SCL and SDA pins exceed the HDMI specification for driving up to 800pF loads. The CEC\_C pin has an internal 27K $\Omega$  pull-up to an internal 3.3V supply (V<sub>REG</sub>).

The HPD\_C path is uni-directional. The direction is from the HDMI connector port to the host port. HPD\_H references  $V_{CCA}$ , and HPD\_C references  $V_{CCC}$ . HPD\_C offers hysteresis to avoid false detection due to bouncing while inserting the HDMI plug.

The FXMHD103 device can be powered down if the OE pin is LOW. If OE is HIGH, the HPD path is enabled. If an HDMI sink asserts the HPD\_C pin HIGH, the DDC and CEC paths are enabled. OE references  $V_{CCA}$ .

Back drive protection is provided on pins facing the HDMI connector.

| Part Number Top Mar |    | Operating<br>Temperature Range | Package                                          | Packing<br>Method              |  |  |  |  |  |

|---------------------|----|--------------------------------|--------------------------------------------------|--------------------------------|--|--|--|--|--|

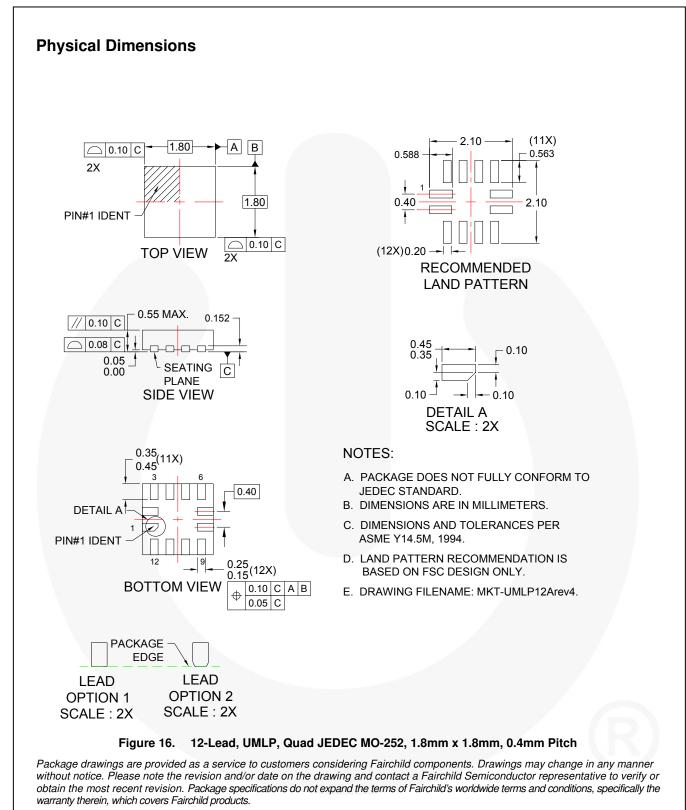

| FXMHD103UMX         | BZ | -40°C to 85°C                  | 12-Terminal, Quad µMLP,<br>1.8mm x 1.8mm Package | 5000 Units on<br>Tape and Reel |  |  |  |  |  |

## **Ordering Information**

# Block Diagrams (Continued)

Figure 3. Circuit Block Diagram

Table 1. Truth Table (V<sub>CCA</sub> & V<sub>CCC</sub> Valid)

| OE   | HPD_C      | OE Internal | VREG     | HPD_H   | SCL_C                  | SDA_C                  | CEC_C                  |

|------|------------|-------------|----------|---------|------------------------|------------------------|------------------------|

| LOW  | Don't Care | LOW         | Disabled | 3-State | 3-State                | 3-State                | 3-State                |

| HIGH | LOW        | LOW         | Disabled | Enabled | 3-State <sup>(2)</sup> | 3-State <sup>(2)</sup> | 3-State <sup>(2)</sup> |

| HIGH | HIGH       | HIGH        | Enabled  | Enabled | Enabled                | Enabled                | Enabled                |

#### Note:

2. SCL\_C and SDA\_C internally pulled up to V<sub>CCC</sub>. CEC\_C is 0V because V<sub>REG</sub> is disabled. This is required for HDMI compliance testing. The VOUT<sub>DIS</sub> parameter captures this requirement.

**Pin Configuration** CEC\_H н\_очн нрр\_с VCCA 12 11 10 9 8 1 CEC\_C SCL\_H 2 7 SCL\_C SDA\_H 3 5 6 4 SDA\_C VCCC GND Ю

## **Pin Definitions**

| Pin # | Signal Name | Description                                                                                                                                                                      |

|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SCL_H       | Host-side (DDC) SCL bi-directional I <sup>2</sup> C pin; referenced to VCCA.                                                                                                     |

| 2     | SDA_H       | Host-side (DDC) SDA bi-directional I <sup>2</sup> C pin; referenced to VCCA.                                                                                                     |

| 3     | OE          | Output enable: LOW=DDC, CEC, & HPD paths disabled; HIGH=DDC, CEC, & HPD paths enabled.                                                                                           |

| 4     | GND         | Device GND                                                                                                                                                                       |

| 5     | VCCC        | HDMI port supply: 5V $V_{CC}$ reference for HPD_C, SCL_C, SDA_C, and $V_{REG}$ input.                                                                                            |

| 6     | SDA_C       | Connector-side (DDC) SDA bi-directional I <sup>2</sup> C pin; referenced to VCCC.                                                                                                |

| 7     | SCL_C       | Connector-side (DDC) SCL bi-directional I <sup>2</sup> C pin; referenced to VCCC.                                                                                                |

| 8     | CEC_C       | Connector-side (CEC) bi-directional pin; referenced to internal 3.3V voltage regulator ( $V_{REG}$ ). RPU decoupled from "3.3V Internal" if OE=LOW.                              |

| 9     | HPD_C       | Connector-side HPD, input for the "hot plug" detect.                                                                                                                             |

| 10    | HPD_H       | Host-side HPD; output for the hot plug detect. This pin references VCCA and indicates to the HDMI controller (HDMI source) when there is an HDMI sink connected to the FXMHD103. |

| 11    | VCCA        | Host-side power supply, 1.6V – 3.6V.                                                                                                                                             |

| 12    | CEC_H       | Host-side CEC, bi-directional pin; referenced to VCCA. RPU decoupled from VCCA if OE=LOW.                                                                                        |

FXMHD103 — HDMI Voltage Translator

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                         | Parameter                          | Condition                          |          | Min. | Max. | Unit |

|--------------------------------|------------------------------------|------------------------------------|----------|------|------|------|

| Vcc                            | Supply Voltage Range               | VCCA, VCCC                         |          | -0.5 | 6.5  | V    |

| V <sub>IN</sub> <sup>(3)</sup> | Innut Voltage Dange                | SCL_H, SDA_H, CEC_H                | , OE     | -0.5 | 6.5  | V    |

| VIN                            | Input Voltage Range                | SCL_C, SDA_C, CEC_C                | , HPD_C  | -0.5 | 6.5  |      |

| V <sub>0</sub> <sup>(3)</sup>  | Output Voltage                     | SCL_H, SDA_H, CEC_H                | , HPD_H  | -0.5 | 6.5  |      |

| V <sub>O</sub> `´              | Output Voltage                     | SCL_C, SDA_C, CEC_C                |          | -0.5 | 6.5  | V    |

| I <sub>IK</sub>                | Input Clamp Current                | V <sub>IN</sub> < 0V               |          |      | -50  | mA   |

| l <sub>ок</sub>                | Output Clamp Current               | V <sub>0</sub> < 0V                |          |      | -50  | mA   |

| TJ                             | Junction Temperature               |                                    |          | -40  | +150 | °C   |

| T <sub>STG</sub>               | Storage Temperature Range          |                                    |          | -65  | +150 | °C   |

|                                |                                    | Human Body Model,<br>JESD22-A114-B | All Pins |      | 8    |      |

| ESD                            | Electrostatic Discharge Capability | Charged Device Model, JESD22-C101  | All Pins |      | 2    | kV   |

|                                |                                    |                                    | Air Gap  |      | 16   |      |

|                                |                                    | IEC 61000-4-2                      | Contact  |      | 9    |      |

Note:

3. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings. Unless otherwise noted, values are across the recommended operating free-air temperature range.

| Symbol           | Parameter            |                | Condition           | Min. | Max.             | Unit |  |

|------------------|----------------------|----------------|---------------------|------|------------------|------|--|

| $V_{CCA}$        | Supply Voltage       | VCCA           |                     |      | 3.6              | V    |  |

| V <sub>ccc</sub> | Supply Voltage       | VCCC           |                     |      | 5.3              | V    |  |

|                  | Input Voltages       | Host Port      | SCL_H, SDA_H, CEC_H | 0    | V <sub>CCA</sub> |      |  |

|                  |                      |                | OE                  | 0    | V <sub>CCA</sub> |      |  |

| V <sub>IN</sub>  |                      | Connector Port | SCL_C, SDA_C        | 0    | V <sub>CCC</sub> | V    |  |

|                  |                      |                | CEC_C               | 0    | 3.3V (Internal)  |      |  |

|                  |                      |                | HPD_C               | 0    | V <sub>CCC</sub> |      |  |

| TA               | Ambient Temperature  |                |                     | -40  | +85              | °C   |  |

| TJ               | Junction Temperature |                |                     | -40  | +125             | °C   |  |

## **Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with fourlayer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_J$  (maximum) at a given ambient temperature.

| Symbol        | Dol     Parameter     T       Junction-to-Ambient Thermal Resistance     3 |     | Unit |

|---------------|----------------------------------------------------------------------------|-----|------|

| $\Theta_{JA}$ | Junction-to-Ambient Thermal Resistance                                     | 320 | °C/W |

## DC Electrical Characteristics (I<sub>cc</sub>)

Unless otherwise specified,  $T_A$ =-40 to 85°C.

| Symbol             | Parameter        | Condition                                                                                               | Min. | Тур. | Max. | Unit |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>CCPD1</sub> | Power Down 1     | $V_{CCA}$ =0V, or $V_{CCC}$ =0V, All Other Pins=Don't Care                                              |      |      | 1    | μA   |

| I <sub>CCPD2</sub> | Power Down 2     | OE=LOW, V <sub>CCA</sub> and V <sub>CCC</sub> Valid, All Other<br>Pins=Don't Care                       |      |      | 1    | μA   |

| I <sub>CCHPD</sub> | Active HPD Only  | OE=HIGH, V <sub>CCA</sub> and V <sub>CCC</sub> Valid, SCL_H,<br>SDA_H and CEC_H=HIGH, HPD_C=0V          |      |      | 1.5  | μA   |

| I <sub>CCA</sub>   | Active HDMI Link | $V_{\text{CCA}}$ and $V_{\text{CCC}}$ Valid, SCL_H, SDA_H and CEC_H=HIGH, HPD_C=V_{\text{CCC}}, OE=HIGH |      |      | 5    | μA   |

| Iccc               |                  | $V_{\text{CCA}}$ and $V_{\text{CCC}}$ Valid, SCL_H, SDA_H and CEC_H=HIGH, HPD_C=V_{\text{CCC}}, OE=HIGH |      |      | 5    | μA   |

## **Back Drive Current**

Unless otherwise specified,  $T_A$ =-40 to 85°C.

| Symbol                | Parameter                          | Condition               | $V_{\text{CCA}}$ | V <sub>ccc</sub> | Тур. | Max. | Unit |

|-----------------------|------------------------------------|-------------------------|------------------|------------------|------|------|------|

| Iback <sub>CEC</sub>  | Current Through CEC_C              | CEC_C=0V - 5V           | 0V               | 0V               | 0.1  | 1.8  | μA   |

| Iback <sub>DDC</sub>  | Current Through SDA_C<br>and SCL_C | SDA_C and SCL_C=0V – 5V | 0V               | 0V               | 0.1  | 5.0  | μA   |

| Iback <sub>VCCC</sub> | Current Through VCCC               | $V_{CCC}=0V-5V$         | 0V               | NA               | 0.1  | 5.0  | μA   |

| Iback <sub>HPD</sub>  | Current Through HPD_C              | HPD_C=0V – 5V           | 0V               | 0V               | 0.1  | 5.0  | μA   |

## Voltage Level Shifter: SCL, SDA Lines (Host/Connector Ports)

Unless otherwise specified,  $T_A$ =-40 to 85°C.

| Symbol                | Parameter                                                       | Condition                                                          | V <sub>CCA</sub> | Min.                      | Тур.  | Max.                      | Unit |  |

|-----------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------|---------------------------|-------|---------------------------|------|--|

| V                     | High Level input Voltage                                        | Host Side                                                          | 1.6V to 3.6V     | V <sub>CCA</sub> - 0.4    |       |                           | v    |  |

| V <sub>IH</sub>       | nigh Level linput voltage                                       | Connector Side                                                     | 1.6V to 3.6V     | V <sub>CCC</sub> - 0.4    |       |                           | v    |  |

|                       |                                                                 | Host Side                                                          | <2V              |                           |       | 0.2 x<br>V <sub>CCA</sub> | v    |  |

| VIL                   | Low Level Input Voltage                                         | Host Side                                                          | >2V              |                           |       | 0.4                       |      |  |

|                       |                                                                 | Connector Side                                                     | 1.6V to 3.6V     |                           |       | 0.4                       |      |  |

| M                     |                                                                 | Host Side: I <sub>OH</sub> =-10µA                                  | 1.6V to 3.6V     | V <sub>CCA</sub> x<br>0.8 |       |                           | v    |  |

| V <sub>OH</sub>       | High Level Output Voltage                                       | Connector Side: I <sub>OH</sub> =-10µA                             | 1.6V to 3.6V     | V <sub>CCC</sub> - 0.3    |       |                           | v    |  |

| V <sub>OL1</sub>      |                                                                 | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0V; Both<br>Directions      | 1.6V to 3.6V     |                           |       | 0.05                      | V    |  |

| V <sub>OL2</sub>      | Low Level Output Voltage                                        | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0.25V; Both<br>Directions   | 1.6V to 3.6V     |                           |       | 0.30                      | V    |  |

| V <sub>OL3</sub>      |                                                                 | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0.3V; Both<br>Directions    | 1.6V to 3.6V     |                           |       | 0.35                      | v    |  |

| V <sub>OL4</sub>      |                                                                 | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0.4V; Both<br>Directions    | 1.6V to 3.6V     |                           |       | 0.45                      | v    |  |

| V <sub>OL5</sub>      |                                                                 | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0.6V C→ H<br>Direction Only | 1.6V to 3.6V     |                           |       | 0.65                      | v    |  |

| RPU                   | lateral Dall or                                                 | SCL_H, Internal Pull-up<br>Connected to SDA_H,<br>VCCA Rail        |                  |                           | 10.00 |                           |      |  |

| RPU                   | Internal Pull-up                                                | SCL_C, Internal Pull-up<br>Connected to SDA_C,<br>VCCC             |                  |                           | 1.75  |                           | kΩ   |  |

| I <sub>PULLUPAC</sub> | Transient Boosted Pull-up<br>Current (Edge Rate<br>Accelerator) | SCL_C, Internal Pull-up<br>Connected to SDA_C,<br>VCCC             |                  |                           | 15    |                           | mA   |  |

|                       | Host Port                                                       | $V_{CCA}$ =0V, V <sub>I</sub> or V <sub>O</sub> =0 to 3.6V         | 0V               |                           |       | ±5                        |      |  |

| IOFF                  | Connector Port                                                  | $V_{CCC}$ =0V, V <sub>I</sub> or V <sub>O</sub> =0 to 5.3V         | 0V to 3.6V       |                           |       | ±5                        | μA   |  |

| L.                    | Connector Port                                                  | V <sub>O</sub> =VCCO or GND                                        | 1.6V to 3.6V     |                           |       | ±5                        |      |  |

| loz                   | Host Port                                                       | V <sub>I</sub> =VCCI or GND                                        | 1.6V to 3.6V     |                           | 1     | ±5                        | μA   |  |

## Voltage Level Shifter: CEC Lines (Host/Connector Ports)

Unless otherwise specified,  $T_A$ =-40 to 85°C.

| Symbol              | Parameter                                          | Condition                                                      | V <sub>CCA</sub> | Min.                      | Тур. | Max.                      | Unit |  |

|---------------------|----------------------------------------------------|----------------------------------------------------------------|------------------|---------------------------|------|---------------------------|------|--|

| V <sub>IH</sub>     | High Level input Voltage                           | Host Side                                                      | 1.6V to 3.6V     | V <sub>CCA</sub> - 0.4    |      | V <sub>CCA</sub>          | V    |  |

|                     |                                                    | Host Side                                                      | <2V              |                           |      | 0.2 x<br>V <sub>CCA</sub> |      |  |

| VIL                 | Low Level Input Voltage                            | Host Side                                                      | >2V              |                           |      | 0.4                       | V    |  |

|                     |                                                    | Connector Side                                                 | 1.6V to 3.6V     |                           |      | 0.6                       |      |  |

| V <sub>OH</sub>     | High Level Output Voltage                          | Host Side, I <sub>OH</sub> =-10µA                              | 1.6V – 3.6V      | V <sub>CCA</sub> x<br>0.8 |      |                           | V    |  |

| V <sub>OH</sub>     | High Level Output Voltage                          | Connector Side, I <sub>OH</sub> =-10µA                         | 1.6V – 3.6V      | 2.75                      | 3.10 |                           | V    |  |

| V <sub>OL1</sub>    |                                                    | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0V                      | 1.6V to 3.6V     |                           |      | 0.05                      | V    |  |

| $V_{OL2}$           |                                                    | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0.25V                   | 1.6V to 3.6V     |                           |      | 0.30                      | V    |  |

| V <sub>OL3</sub>    | Low Level Output Voltage<br>Host & Connector Sides | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0.3V                    | 1.6V to 3.6V     |                           |      | 0.35                      | V    |  |

| V <sub>OL4</sub>    |                                                    | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0.4V                    | 1.6V to 3.6V     |                           |      | 0.45                      | V    |  |

| V <sub>OL5</sub>    |                                                    | I <sub>OL</sub> =3mA, V <sub>IL</sub> =0.6V                    | 1.6V to 3.6V     |                           |      | 0.65                      | V    |  |

| VOUT <sub>DIS</sub> | Output Voltage when<br>Disabled                    | CEC_C: HPD_C=LOW,<br>OE=HIGH, V <sub>CCC</sub> =4.8V –<br>5.3V | 1.6V to 3.6V     |                           |      | 0.3                       | V    |  |

|                     |                                                    | CEC_H, Internal Pull-up<br>Connected to VCCA Rail              |                  |                           | 10   |                           |      |  |

| R <sub>PU</sub>     | Internal Pull-up                                   | CEC_C, Internal Pull-up<br>Connected to Internal 3.3V<br>Rail  |                  |                           | 27   |                           | kΩ   |  |

| 1                   | H Port                                             | $V_{CCA}$ =0V, V <sub>I</sub> or V <sub>O</sub> =0 to 3.6V     | 0V               |                           |      | ±5.0                      |      |  |

| I <sub>OFF</sub>    | C Port                                             | $V_{CCC}$ =0V, V <sub>I</sub> or V <sub>O</sub> =0 to 5.3V     | 0V to 3.6V       |                           |      | ±1.8                      | μA   |  |

| 1                   | C Port                                             | V <sub>O</sub> =VCCO or GND                                    | 1.6V to 3.6V     |                           |      | ±5.0                      |      |  |

| l <sub>oz</sub>     | H Port                                             | VI=VCCI or GND                                                 | 1.6V to 3.6V     |                           |      | ±5.0                      | μA   |  |

## Voltage Level Shifter: HPD Lines (Host/Connector Ports)

$T_A$ =-40 to 85°C unless otherwise specified.

| Symbol           | Parameter                                  | Condition                                                                     | V <sub>CCA</sub> | Min.                   | Тур. | Max. | Unit |

|------------------|--------------------------------------------|-------------------------------------------------------------------------------|------------------|------------------------|------|------|------|

| V <sub>IH</sub>  | High Level Input<br>Voltage                |                                                                               | 1.6V to 3.6V     | 2                      |      |      | V    |

| VIL              | Low Level Input<br>Voltage                 |                                                                               | 1.6V to 3.6V     |                        |      | 0.8  | V    |

| V <sub>OH</sub>  | High Level Output<br>Voltage               | I <sub>OH</sub> =-3mA                                                         | 1.6V to 3.6V     | 0.7 x V <sub>CCA</sub> |      | 1    | V    |

| V <sub>OL</sub>  | Low Level Output<br>Voltage                | I <sub>OL</sub> =3mA                                                          | 1.6V to 3.6V     |                        |      | 0.3  | V    |

| V <sub>HYS</sub> | HPD_C (V <sub>T+</sub> - V <sub>T-</sub> ) |                                                                               | 1.6V to 3.6V     |                        | 200  |      | mV   |

| R <sub>PD</sub>  | Internal Pull-Down                         | HPD_C, Internal Pull-down<br>Connected to Ground, VCCA<br>and VCCC Powered up |                  |                        | 100  |      | KΩ   |

| I <sub>OFF</sub> | Host Port                                  | Vo=Vcco or GND                                                                | 0V               |                        |      | ±5   | μA   |

| I <sub>OZ</sub>  | Host Port                                  | V <sub>I</sub> =V <sub>CCI</sub> or GND                                       | 3.6V             |                        |      | ±5   | μA   |

## AC Electrical Characteristics<sup>(4)</sup>

Unless otherwise specified,  $T_A$ =-40 to 85°C. Typical values  $T_A$ = 25°C.

## Voltage Level Shifter: SCL, SDA Lines (Host and Connector Ports); V<sub>CCA</sub>=1.8V

| Symbol           | Parameter                      | Pins   | Condition                     | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------|--------|-------------------------------|------|------|------|------|

| 4                | Propagation Delay              | H to C | DDC Channels Enabled          |      | 100  |      |      |

| t <sub>PHL</sub> |                                | C to H |                               |      | 5    |      |      |

| +                |                                | H to C |                               |      | 25   |      | ns   |

| t <sub>PLH</sub> |                                | C to H |                               |      | 5    |      |      |

| +                | H Port Fall Time               | H Port | DDC Channels Enabled 70% -30% |      | 2    |      | ns   |

| t <sub>f</sub>   | C Port Fall time               | C Port |                               |      | 80   |      |      |

| +                | H Port Rise Time               | H Port | DDC Channels Enabled 30% -70% |      | 2    |      | 20   |

| tr               | C Port Rise Time               | C Port | DDC Channels Enabled 30% -70% |      | 50   |      | ns   |

| f <sub>MAX</sub> | Maximum Switching<br>Frequency |        | DDC Channels Enabled          | 400  |      |      | kHZ  |

## Voltage Level Shifter: CEC Line (Host and Connector Ports); V<sub>CCA</sub>=1.8V

| Symbol           | Parameter                             | Pins   | Condition                      | Min. | Тур. | Max.  | Unit |

|------------------|---------------------------------------|--------|--------------------------------|------|------|-------|------|

| +                | <ul> <li>Propagation Delay</li> </ul> | H to C |                                |      | 100  |       |      |

| t <sub>PHL</sub> |                                       | C to H | CEC Channels Enabled           |      | 5    |       | ns   |

| +                |                                       | H to C | CEC Channels Enabled           |      | 25   |       |      |

| t <sub>PLH</sub> |                                       | C to H |                                |      | 5    |       | ns   |

|                  | H Port Fall Time                      | H Port | CEC Channels Enabled 90% - 10% |      | 10   | 50000 |      |

| t <sub>f</sub>   | C Port Fall time                      | C Port |                                |      | 200  | 50000 | ns   |

|                  | H Port Rise Time                      | H Port | OFC Changels England 10% - 00% |      | 5    | 400   | ns   |

| t <sub>r</sub>   | C Port Rise Time                      | C Port | CEC Channels Enabled 10% - 90% |      | 0.2  | 250   | μs   |

## Voltage Level Shifter: HPD Line (Host and Connector Ports); V<sub>CCA</sub>=1.8V

| Symbol           | Parameter         | Pins   | Condition                     | Min. | Тур. | Max. | Unit |

|------------------|-------------------|--------|-------------------------------|------|------|------|------|

| t <sub>PHL</sub> | Dropagation Dalay | C to H | UPD Channel Enchlad           |      | 10   |      | 2    |

| t <sub>PLH</sub> | Propagation Delay | C to H | HPD Channel Enabled           |      | 5    |      | ns   |

| t <sub>f</sub>   | H Port Fall Time  | H Port | HPD Channel Enabled 90% - 10% |      | 1    |      | ns   |

| tr               | H Port Rise Time  | H Port | HPD Channel Enabled 10% - 90% |      | 3    | 1    | ns   |

### I/O Capacitance

$T_A$ = 25°C unless otherwise specified.

| Symbol          | Parameter              | Condition                                                                | $V_{CCA \&} V_{CCC}$ | Min. | Тур. | Max. | Unit |

|-----------------|------------------------|--------------------------------------------------------------------------|----------------------|------|------|------|------|

| Cı              | Control Inputs         |                                                                          | 0V                   |      | 2    | 1    | pF   |

|                 | DDC & CEC on Host Port |                                                                          | 0V                   |      | 5    |      | pF   |

| C <sub>IO</sub> | DDC on Connector Port  | LCR: V <sub>bias</sub> =2.5V; AC<br>Input=3.5V <sub>pp</sub> ; f=100kHZ  | 0V                   |      | 10   | 16.5 | pF   |

|                 | CEC on Connector Port  | LCR: V <sub>bias</sub> =1.65V; AC<br>Input=2.5V <sub>pp</sub> ; f=100kHZ | 0V                   |      | 10   | 16.5 | pF   |

#### Note:

4. AC Characteristics are guaranteed by Design and Characterization, not production tested.

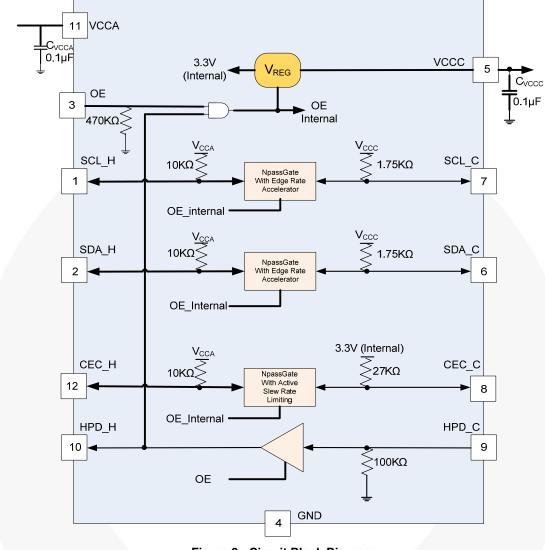

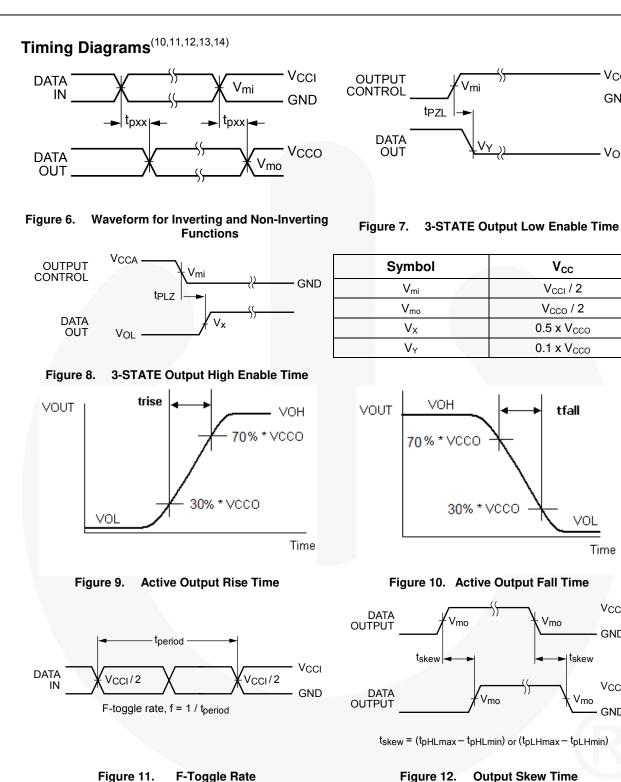

## AC Parameter Measurement Information<sup>(5,6,7,8,9)</sup>

Figure 5. Device Under Test Setup

#### Table 2. AC Load

| Symbol | Parameter                             | Condition | V <sub>CCA</sub> | Min. | Тур. | Max. | Unit |

|--------|---------------------------------------|-----------|------------------|------|------|------|------|

|        | Bus Load Capacitance (Connector-Side) | CEC       | 1.6V to 3.6V     |      |      | 1300 |      |

| CL     | Bus Load Capacitance (Connector-Side) | DDC & HPD | 1.6V to 3.6V     |      |      | 800  | pF   |

|        | Bus Load Capacitance (Host-Side)      | All Pins  | 1.6V to 3.6V     |      |      | 15   |      |

Notes:

5.  $R_T$  termination resistance should be equal to  $Z_{OUT}$  of the pulse generator.

6.  $C_L$  includes probe and jig capacitance.

7. All input pulses supplied by generators have the following characteristics: PRR  $\leq$  10MHz, Z<sub>0</sub>=50 $\Omega$ , slew rate  $\geq$  1V/ns.

8. The outputs are measured one at a time, with one transition per measurement.

9.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{PD}$ .

VCCA

GND

VOL

Vcc

V<sub>CCI</sub> / 2

V<sub>cco</sub> / 2

$0.5 \times V_{CCO}$

0.1 x V<sub>cco</sub>

tfall

VOL

Vmo

ltskew

Vmo

Time

Vcco

GND

Vcco

GND

Figure 12.

#### Notes:

- 10. Input  $t_R=t_F=2.0$ ns, 10% to 90% at  $V_{IN}=1.65V$  to 1.95V; Input  $t_R=t_F=2.0$  ns, 10% to 90% at  $V_{IN}=2.3$  to 2.7V; Input  $t_{R}=t_{F}=2.5$  ns, 10% to 90%, at  $V_{IN}=3.0$ V to 3.6V only; Input  $t_R=t_F=2.5$ ns, 10% to 90%, at  $V_{IN}=4.5$ V to 5.5 only.

- 11.  $V_{CCI}=V_{CCA}$  for control pin OE or  $V_{mi}=(V_{CCA} / 2)$ .

- 12. DDC Rise Times 30% 70%, CEC & HPD Rise Times 10% 90%

- 13. DDC Fall Times 30% 70%, CEC & HPD Fall Times 10% 90%

- 14.  $V_{CCI}$  is the V<sub>CC</sub> associated with the input side. V<sub>CCO</sub> is the V<sub>CC</sub> associated with the output side.

## **Application Information**

#### **Power Down**

The FXMHD103 can be powered down if either  $V_{CCA}$  or  $V_{CCC}$  equals 0V, or if OE is LOW.

#### "Hot Plug" Detect Operation

After VCCA and VCCC have powered up to valid levels, and OE enabled (HIGH) the HPD path is enabled. The internal 3.3V voltage regulator and the CEC & DDC blocks are disabled due to the internal weak pull-down resistor (100k $\Omega$  to GND) on HPD\_C. When the HDMI sink recognizes a valid 5V signal on the HDMI connector, to inform the HDMI source there is a valid HDMI sink connected to the HDMI connector; the sink typically ties the HPD\_C signal to the HDMI 5V supply through a 1K $\Omega$  resistor. A HIGH on HPD\_C, in turn, enables the internal voltage regulator, as well as the DDC & CEC paths. The HDMI link is active between the HDMI source and the HDMI sink.

When HPD\_C is LOW, the respective resistor pullups (RPUs) on the host and connector sides of the DDC paths remain coupled to their respective voltage references. Likewise, when HPD\_C is LOW, the RPUs on the host and connector sides of the CEC path remain coupled to their respective voltage references. Since HPD\_C disables  $V_{REG}$ and  $V_{REG}$  is the CEC\_C voltage reference, CEC\_C is held to 0V by a weak (50nA) current source when HPD\_C is LOW. This is captured by the VOUT<sub>DIS</sub> parameter.

#### **Backdrive Protection**

Backdrive-current protection is available on all FXMHD103 signals interfacing with the HDMI connector, including VCCC, SCL\_C, SDA\_C, CEC\_C, and HPD\_C. If the FXMHD103 is powered down,  $V_{CCA}$ =0V or  $V_{CCC}$ =0V and the HDMI sink forces 0V – 5V onto any of the HDMI connector-facing pins (VCCC, SCL\_C, SDA\_C, CEC\_C & HPD\_C). The maximum current flow from the FXMHD103 is only 5µA, with the exception of 1.8µA (maximum) on CEC C.

#### **DDC Channel Description**

The HDMI specification implements the Video Electronics Standards Association (VESA) Display Data Channel (DDC) for communication between a single HDMI source and a single HDMI sink. The DDC is used by the HDMI source to read the sink's Enhanced Extended Display HDMI Identification Data (E-EDID) to discover the sink's configuration or capabilities. DDC must meet the I<sup>2</sup>C specification, version 2.1, for Standard Mode devices. Because the HDMI application is meant for high-definition Transition-Minimized Differential Signaling (TMDS) video transport across a cable, the HDMI specification requires the DDC signals (SCL & SDA) be able to drive a minimum capacitance of 800pF (source 50pF + cable assembly 700pF + sink 50pF). The  $I^2C$  specification requires a minimum of 400pF capacitance.

## **Edge Rate Accelerators**

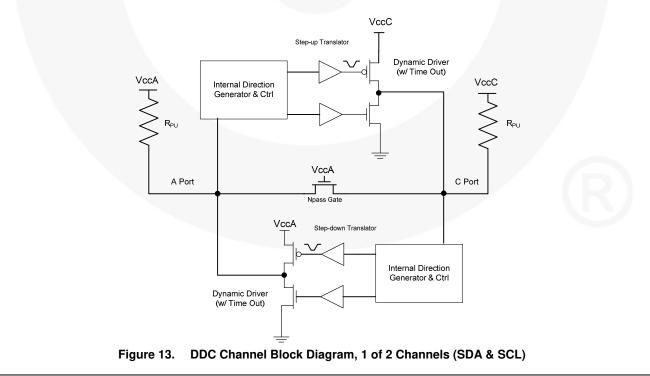

The FXMHD103 DDC channel is designed for highperformance  $I^2C$  level shifting. Figure 13 shows that each bi-directional channel contains an Npassgate and two dynamic drivers. This hybrid architecture is highly beneficial in an  $I^2C$  application with large capacitive loads and where auto-direction is necessary.

For example, during the following  $l^2C$  protocol events the bus direction needs to change from "Source-to-Sink" to "Sink-to-Source" without the occurrence of an edge:

- Clock Stretching

- Slave's ACK Bit (9th bit=0) following a Master's Write Bit (8th bit=0)

- Clock Synchronization and Multi Master Arbitration

If there is an  $I^2C$  translator between the source and sink in these examples, the  $I^2C$  translator must change direction when both A and C ports are LOW. The Npassgate can accomplish this efficiently because, when both A and C ports are LOW, the Npassgate acts as a low resistive short between the (A and C) ports.

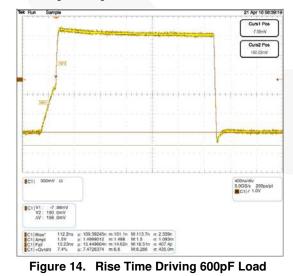

Due to the  $I^2C$  open-drain topology,  $I^2C$  drivers are not push/pull devices. Logic LOWs are "pulled down" (Isink), while logic HIGHs are "let go" (3-state). For example, when the source lets go of SCL (SCL always comes from the source), the rise time of SCL is largely determined by the RC time constant, where R=RPU and C=the bus capacitance. If the FXMHD103 is attached to the source [on the A port] and there is a source on the C port, the Npassgate acts as a low-resistive short between both ports until either of the port's V<sub>CC/2</sub> thresholds is reached. After the RC time constant has reached the V<sub>CC/2</sub> threshold of either port, the port's edge detector triggers both dynamic drivers to drive their respective ports in the LOW-to-HIGH (LH) direction, accelerating the rising edge. The resulting rise time resembles the scope shot in Figure 14. Effectively, two distinct slew rates appear in rise time. The first slew rate (slower) is the RC time constant of the bus. The second slew rate (much faster) is the dynamic driver accelerating the edge.

If both the A and C ports of the translator are HIGH, a high-impedance path exists between the A and C ports because both the Npassgates are turned off. If a source or sink device decides to pull SCL or SDA LOW, that device's driver pulls down ( $I_{sink}$ ) SCL or SDA until the edge reaches the A or C port  $V_{CC}/2$  threshold. When either the A or C port threshold is reached, the port's edge detector triggers both dynamic drivers to drive their respective ports in the HIGH-to-LOW (HL) direction, accelerating the falling edge.

## **Driving a Capacitive Load**

The FXMHD103 dynamic drivers have enough current sourcing capability to drive an 800pF capacitive bus. The Figure 14 scope shot is of an FXMHD103 driving a lumped load of 600pF. Notice the (30% - 70%) rise time is only 112ns ( $R_{PU}$ =5K $\Omega$ ). This is well below the maximum rise time of 1000ns in Standard Mode (100KHz) or 300ns in Fast Mode (400KHz).

### Vol vs. VIL & IoL

The I<sup>2</sup>C specification mandates a maximum V<sub>IL</sub> (I<sub>OL</sub> of 3mA) of  $V_{CC} \ge 0.3$  for an I<sup>2</sup>C receiver and a maximum V<sub>OL</sub> of 0.4V for an I<sup>2</sup>C transmitter. If there is an HDMI source on the A port of an I<sup>2</sup>C translator with a V<sub>CC</sub> of 1.8V and an HDMI sink on the I<sup>2</sup>C translator C port with a V<sub>CC</sub> of 5.0V, the maximum V<sub>IL</sub> of the source is (1.6V x 0.3) 480mV. Meanwhile, the sink could transmit a valid logic LOW of 0.4V to the source. 80mV is not very much margin between the maximum transmitted VoL of 400mV (HDMI sink) to the maximum received  $V_{IL}$  of 480mV (HDMI source). This appears to be an oversight in the I<sup>2</sup>C specification, but there is an explanation. The I<sup>2</sup>C specification assumes transmitters and receivers share the same V<sub>CC</sub>. The I<sup>2</sup>C specification does call out separate V\_{OL} requirements vs. V\_{CC} conditions where V\_{OL1}=0.4V when V\_{CC} is > 2.0V and V\_{OL3}=0.2 x V\_{CC}, when  $V_{CC}$  is < 2.0V. When there is  $V_{CC}$  alignment between I<sup>2</sup>C transmitters and receivers, the I<sup>2</sup>C specification provides adequate V<sub>IL</sub> vs. V<sub>OL</sub> margins. However, when you have a transmitter operating at 5V and a receiver operating at 1.6V through a translator or level shifter, the  $V_{OL}$  vs.  $V_{IL}$  margin gets very tight, as in the above example. Therefore, the voltage drop across the I<sup>2</sup>C translator must be as low as possible.

In general, if the I<sup>2</sup>C translator's channel resistance is too high, the voltage drop across the translator could present a V<sub>IL</sub> to a receiver greater than the receiver's maximum V<sub>IL</sub>. To complicate matters, the I<sup>2</sup>C specification states that 6mA of I<sub>OL</sub> is recommended for bus capacitances approaching 400pF in Fast Mode. More I<sub>OL</sub> increases the voltage drop across the I<sup>2</sup>C translator. The I<sup>2</sup>C application benefits when I<sup>2</sup>C translators exhibit low V<sub>OL</sub> performance. Table 3 depicts the FXMHD103 targeted V<sub>OL</sub> performance vs. V<sub>IL</sub>/I<sub>OL</sub> when the direction is from C side to A side, V<sub>CCC</sub>=5.0V and V<sub>CCA</sub>=1.6V.

| 6<br>6<br>6 | 50<br>300      | 50<br>50                         | 8.33<br>8.33                     |

|-------------|----------------|----------------------------------|----------------------------------|

| 6           |                | 50                               | 8.33                             |

| -           | 250            |                                  |                                  |

|             | 350            | 50                               | 8.33                             |

| 6           | 450            | 50                               | 8.33                             |

| 6           | 650            | 50                               | 8.33                             |

|             |                |                                  |                                  |

| CEC_H       | HPD_H          |                                  | 2 PN #2                          |

|             | yout Reco<br>T | yout Recommendation<br>Top View: | yout Recommendation<br>Top View: |

Figure 15. PCB Routing Example (Molex HDMI Type-D Connector)

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

## FAIRCHILD

#### SEMICONDUCTOR

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool™ AccuPower™ AX-CAPTM BitSiC™ Build it Now™ CorePLUS™ CorePOWER™ CROSSVOLT CTL™ Current Transfer Logic™ DEUXPEED<sup>®</sup> Dual Cool™ **EcoSPARK**® EfficientMax™ **ESBC™** R Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT<sup>®</sup> FAST<sup>®</sup>

F-PFS™ FRFET® Global Power Resource<sup>SM</sup> GreenBridge™ Green FPS™ Green FPS™ e-Series™ Gmax™ **GTO™** IntelliMAX™ **ISOPLANAR™** Making Small Speakers Sound Louder and Better MegaBuck™ MICROCOUPLER™ MicroEET™ MicroPak™ MicroPak2™ MillerDrive™ MotionMax™ Motion-SPM™ mWSaver™ OptoHiT™ **OPTOLOGIC<sup>®</sup> OPTOPLANAR®**

PowerTrench<sup>®</sup> **PowerXS™** Programmable Active Droop™ **QFET**<sup>®</sup> OST Quiet Series™ RapidConfigure™  $\bigcirc$ Saving our world, 1mW/W/kW at a time™ SignalWise™ SmartMax™ SMART START Solutions for Your Success™ SPM® **STEALTH™** SuperFET® SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET™ Sync-Lock™

TinyBuck™ TinyLogic® TinyDect™ TinyLogic® TiNYOPTO™ TinyPower™ TinyPWM™ TinyWire™ TranSiC™ Trifault Detect™ TRUECURRENT®\* µSerDes™

The Power Franchise®

UHC<sup>®</sup> UItra FRFET™ UniFET™ VCX™ VisualMax™ VoltagePlus™ XS™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

®

#### DISCLAIMER

FastvCore™

**FETBench**<sup>™</sup>

EP.STM

FlashWriter®\*

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild to combat this global problem and encourage our customers to ob their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                          |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make<br>changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |

Rev. 161

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC