Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **GN4124 x4 Lane PCI Express to Local Bridge**

**Data Sheet**

# **Revision History**

| Version | ECR    | Date          | Changes and Modifications                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | 151915 | May 2009      | Created new document describing functionality and the register map for GN4124 & GN4121 devices. These common sections have been removed.                                                                                                                                                                                                                                                                                                                  |

| 1       | 151527 | May 2009      | It is now a Data Sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |        |               | Added the content of the document: GN4124 x4 PCI Express to Local Bus Bridge User Manual (Document ID: 47719) to this data sheet. This User Manual is no longer a stand-alone document.                                                                                                                                                                                                                                                                   |

|         |        |               | Changed some parameters in Table 2-1 (EEPROM_EN), Table 3-2, Table 3-3, Table 5-2 and Table 13-2.                                                                                                                                                                                                                                                                                                                                                         |

|         |        |               | Changed Figure 4-2, Figure 6-2, Figure 7-1 and Figure 9-16.                                                                                                                                                                                                                                                                                                                                                                                               |

|         |        |               | Modified descriptions in 9.4 Operation, 9.7.3 FCL FPGA Configuration and 9.7.4 FCL FSM FPGA Configuration.                                                                                                                                                                                                                                                                                                                                                |

|         |        |               | Changes to registers to PCI_BAR0_LOW, PCI_BAR2_LOW, PCI_BAR2_HIGH, PCI_BAR4_LOW, PCI_BAR4_HIGH, PCI_SUB_VENDOR, PCI_SUB_SYS, PCIE_DEVICE_CAP, PCIE_DCR, INT_CTRL, INT_STAT, INT_CFG0-7, GPIO_DIRECTION_MODE, GPIO_OUTPUT_ENABLE, GPIO_OUTPUT_VALUE, GPIO_INT_MASK, GPIO_INT_MASK_CLR (Note: formerly GPIO_INT_ENABLE), GPIO_INT_MASK_SET (Note: formerly GPIO_INT_DISABLE), GPIO_INT_STATUS, GPIO_INT_TYPE, GPIO_INT_VALUE, GPIO_INT_ON_ANY and FCL_CTRL. |

| D       | 151519 | March 2009    | Clarified output voltage and local bus timing in Table 3-6 and Table 3-11.                                                                                                                                                                                                                                                                                                                                                                                |

| С       | 150789 | December 2008 | Corrected pin assignments and definitions.  Updated electrical characteristics.  Corrected Figure 2-2.  Updated Local Bus Interface clock range.                                                                                                                                                                                                                                                                                                          |

| В       | 150182 | August 2008   | Corrected pin assignments, part number and other updates.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Α       | 148626 | May 2008      | New document.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### **Contents**

| l. In | troduction                               | 4 |

|-------|------------------------------------------|---|

|       | 1.1 Features                             | 4 |

|       | 1.2 Live on Power-up                     | 5 |

|       | 1.3 FPGA On-the-Fly Configuration Loader | 6 |

|       | 1.4 Local Bus Interface                  | 6 |

|       | 1.5 Virtual Channel Support              | 6 |

|       | 1.6 PCI Express Application Layer        | 7 |

|       | 1.7 Interrupt Controller                 | 7 |

|       | 1.8 2-Wire Serial Controller             |   |

|       | 1.9 Data Sheet Usage                     | 7 |

|       | 1.10 Getting Help from Gennum            |   |

| 1.11 Getting Answers to PCI Express Related Questions | 8  |

|-------------------------------------------------------|----|

| 2. Pin Descriptions                                   | 9  |

| 2.1 Pin Assignments                                   | 9  |

| 2.2 Pin Descriptions                                  | 10 |

| 3. Electrical Characteristics                         | 16 |

| 3.1 Absolute Maximum Ratings                          | 16 |

| 3.2 Operating Conditions                              | 16 |

| 3.3 DC Electrical Characteristics                     | 17 |

| 3.4 PCI Express Electrical Characteristics            | 18 |

| 3.4.1 PCI Express Transmitter Characteristics         | 18 |

| 3.4.2 PCI Express Receiver Characteristics            | 21 |

| 3.4.3 Local Bus Timing                                | 22 |

| 3.4.4 Local Clocks' Pins Settings                     | 24 |

| 4. Overview                                           | 25 |

| 4.1 GN4124 Signals                                    | 26 |

| 5. Package & Ordering Information                     | 27 |

| 5.1 Package Dimensions                                | 27 |

| 5.2 Packaging Data                                    | 28 |

| 5.3 Ordering Information                              | 28 |

### GN4124 x4 Lane PCI Express to Local Bridge Data Sheet

### 1. Introduction

For the past decade, PCI has been a dominant interconnect for both PC and embedded systems. With the shift to high-speed serial interfaces, PCI Express® is quickly replacing parallel PCI. As a leader in providing solutions for high-speed serial communications, Gennum has developed the GN4124 family of PCI bridge controller components to complement FPGA devices. The GN4124 is specifically designed to take advantage of the architectural features of low-cost FPGA devices that do not have PCI Express capable SerDes on-chip. The result is a low-cost bridging solution for high-performance native PCI Express bridging.

The GN4124 is a desirable companion to large FPGA devices, where the requirement for firmware upgrading and on-the-fly reconfiguration are required.

The GN4124 is a 4-lane PCI Express to local bus bridge that is designed to work as a companion for FPGA devices to provide a complete bridging solution for general applications. In addition to a 4-lane PCI Express compliant PHY interface, the GN4124 contains the link and transaction layers, and an applications interface that is ideally suited to FPGA interfacing using a small number of pins.

Since the PCI Express transaction/link IP is hard-wired into the GN4124, there is no need to license PCIe IP. The level of integration and very low power operation of the GN4124 make it an ideal alternative to using a PIPE PHY, where IP licensing and the cost of FPGA resources and power consumption is unattractive by comparison. Using the GN4124, allows FPGA resources to be spent on what differentiates the product, rather than on implementing the PCI Express protocol.

#### 1.1 Features

- 4 Lane PCI Express interface

- Complies with PCI Express Base Specification 1.1

- On-chip PHY, transaction, and link layer eliminates the cost of IP licensing

- Two hardware virtual channels supported

- Payload size of up to 512 bytes with up to three outstanding transactions in each direction

- Supports 3x64-bit base address registers

- Provides flexible power management capability

- Provides pin efficient local bus interface for easy attachment to popular low-cost FPGA devices

- Uses DDR SSTL I/O for high-speed data transfer (up to 800MB/s)

- FPGA source code provided for 64-bit master/target read/write buses for easy user logic attachment

- Local bus may be operated asynchronously to the PCIe clock rate for power optimization

- "Live" on power up

- On-chip type 0 PCI configuration space enables auto detection without FPGA activity

- On-chip extended configuration space supports power management, serial number, MSI, and PCIe capability registers

- FPGA bitstream loader

- Allows easy configuration of the attached FPGA through PCIe

- Provides on-the-fly FPGA reconfiguration capability

- 2-wire master/target

- Boot master mode allows PCI configuration space defaults to be loaded from a small EEPROM upon system reset

- General master mode allows attached 2-wire devices to be read/written

- Target mode allows internal registers to be accessed from an external circuit or processor

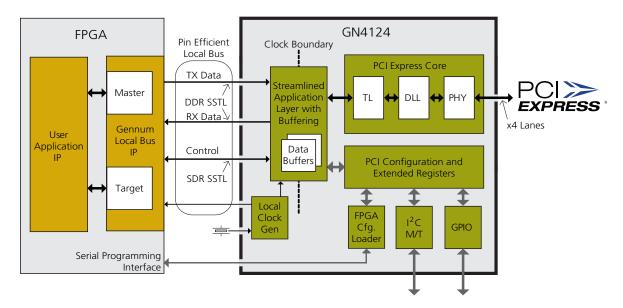

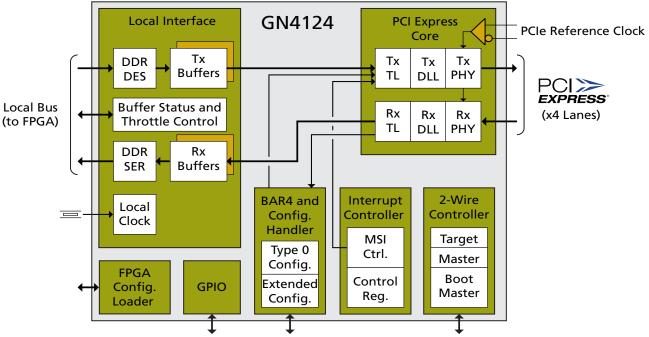

A simplified block diagram of the GN4124 chip is shown in Figure 1-1.

Figure 1-1: GN4124 with FPGA Simplified Block Diagram

## 1.2 Live on Power-up

Since the GN4124 contains a complete type 0 PCI configuration space, it is live on power-up so that a plug-and-play BIOS can auto-detect it and enumerate it without an attached FPGA having to be configured.

### 1.3 FPGA On-the-Fly Configuration Loader

An FPGA bitstream may be downloaded from the host system over PCIe to the attached FPGA using the on-chip FPGA configuration loader. This eliminates the expense of a dedicated FPGA ROM and makes on-the-fly reconfiguration and firmware upgrades simple. The ability to dynamically configure an attached FPGA over PCIe makes the GN4124 an ideal companion to all ranges of FPGA devices, including large SerDes capable devices, that require reconfiguration or firmware upgrades over PCIe.

#### 1.4 Local Bus Interface

The local bus interface uses a combination of single and dual data rate SSTL I/O to accomplish very high data rates in the fewest possible pins. A singe data rate clock is used for SSTL control signals and separate dual data rate source synchronous clocking is used for the DDR SSTL data. The SDR control signals operate at up to 200MHz and the DDR I/O operate at up to 400MT/s across 16 bits using a 200MHz DDR clock. This provides 800MB/s in each direction.

The local bus may operate asynchronously from the PCI Express rate. In order to save power, the local bus clock can operate at the lowest possible rate required by an application.

The local bus protocol facilitates four types of transactions:

- PCIe-to-Local Target Writes: A PCIe agent (such as the host processor/root complex) writes data to the local bus.

- PCIe-to-Local Target Reads: A PCIe agent reads data from the local bus. Reads are split into a request phase (address phase) and a completion phase (data phase).

- Local-to-PCIe Master Writes: The attached FPGA writes data to a PCIe device (such as host memory via a root complex).

- Local-to-PCIe Master Reads: The attached FPGA reads data from a PCIe device.

The PCIe-to-Local transactions would typical involve a target controller implemented in the FPGA. Local-to-PCIe Master transactions allow a DMA controller in the FPGA to access PCI Express devices.

### 1.5 Virtual Channel Support

The GN4124 has two independent virtual channels that support the eight PCIe defined traffic classes. This enables high local bus utilization by supporting non-blocking traffic between virtual channels. This is accomplished with separate on-chip buffering resources for each of the two virtual channels. For example, when write buffering is full for VC0 and VC1 has room, then VC1 traffic may proceed without reference to the state of VC0.

Virtual channels may be used to separate different types of application traffic. For example, a DMA engine in the FPGA may be aggressively reading and writing host memory to stream video data. At the same time another agent in the FPGA may need to communicate low bandwidth, latency sensitive synchronization information. If the two

types of traffic are segregated in terms of virtual channels and traffic classes, then the low latency traffic can be allowed to pass the high bandwidth traffic.

### 1.6 PCI Express Application Layer

The on-chip applications layer transfers data between the PCI Express port and an attached FPGA using the local bus interface. It provides a mechanism to access internal registers through configuration space access and through one of the Base Address Registers (BAR4). The applications layer supports the transmission of message signalled interrupts.

### 1.7 Interrupt Controller

A flexible interrupt controller automatically generates PCIe message signalled interrupts from either external pins (GPIO pins) or internally generated interrupt sources. The interrupt controller can route any interrupt source to up to four GPIO pins.

#### 1.8 2-Wire Serial Controller

An on-chip I<sup>2</sup>C compatible controller provides both a master and target mode. After device reset, default configuration register values, such as Subsystem Vendor ID and BAR sizes, can be automatically loaded from a small serial EEPROM. After initialization, an external 2-wire master can access on-chip registers to read/write them.

### 1.9 Data Sheet Usage

The GN4124 Data Sheet includes detailed specifications on GN4124 device. However, there are other complementary documents to assist designers available on the Gennum Web site: <a href="https://www.gennum.com/mygennum">www.gennum.com/mygennum</a>. A complete set of documentation includes the following:

- GN4124 Data Sheet (this document)

- GN412x PCI Express Family Reference Manual (Document ID: 52624), which

provides the details on functionality and the register map associated with the

GN412x family of chips

- GN4124 Master List of Documents & Electronic Files (Document ID: 52423), which provides a summary of the content of the documentation & electronic files, to help navigate the content on MyGennum

- Reference Design Kit (RDK) board and the asssociated documentation

Following chapters detail the specifications of the GN4124:

- 2. Pin Descriptions

- 3. Electrical Characteristics

- 5. Package & Ordering Information

Before finalizing a system design based on the GN4124, please contact Gennum to verify that you have the most recent specifications.

Gennum is constantly trying to improve the quality of its product documentation. If you have any questions or comments, please contact Gennum Technical Support.

### 1.10 Getting Help from Gennum

For technical support, contact Gennum by telephone or e-mail. E-mail ensures the quickest response. The most up-to-date technical support information is also posted on the Gennum website. E-mail: vbapps@gennum.com.

### 1.11 Getting Answers to PCI Express Related Questions

This data sheet assumes a basic understanding of the PCI Express Specification. If you are looking for a copy of the specification please contact the PCI Special Interest group at 503-619-0569 or visit their Web site at: http://www.pcisig.com.

If you are not familiar with the PCI Express specification, a good place to start is by reading one of several books on the subject. One of the most popular is PCI Express System Architecture written by Tom Shanley, Don Anderson, and Ravi Budruk (published by MindShare Inc.).

# 2. Pin Descriptions

## 2.1 Pin Assignments

Figure 2-1: GN4124 Pin Assignment

|   | 1            | 2            | 3             | 4              | 5              | 6              | 7              | 8             | 9              | 10               | 11              | 12                | 13                | 14              | 15               | 16             |   |

|---|--------------|--------------|---------------|----------------|----------------|----------------|----------------|---------------|----------------|------------------|-----------------|-------------------|-------------------|-----------------|------------------|----------------|---|

| Α | VSS_<br>PCIE | PERn0        | VSS_<br>PCIE  | DBG0           | DBG7           | GPIO15         | GPIO9          | SPRI_CLK      | TDI            | GPIO7            | GPIO6           | SPRI_<br>DONE     | GPIO4             | TDO             | PLL_TEST<br>_OUT | VSS            | Α |

| В | VDD_<br>PCIE | PERp0        | NC            | DBG2           | DBG6           | GPIO13         | GPIO14         | RSTIN         | GPIO8          | SPRI_<br>DATAOUT | SCLK            | TRST              | SPRI_XI_<br>SWAP  | SPRI_<br>STATUS | VSS              | L2P_<br>DATA15 | В |

| С | РЕТр0        | VSS_<br>PCIE | VDD_<br>PCIE  | VSS            | DBG5           | DBG1           | GPIO12         | GPIO10        | RSTOUT<br>33   | GPIO2            | SPRI_<br>CONFIG | SDATA             | LB_REF_<br>CLK_MO | VSS             | L2P_<br>DATA7    | L2P_<br>DATA14 | C |

| D | PETn0        | VSS_<br>PCIE | VDD_<br>PCIE  | VSS            | VDDC           | SCAN_EN        | DBG3           | VDDC          | GPIO3          | NC               | GPIO1           | LB_REF_<br>CLK_MI | VDDC              | NC              | L2P_<br>DATA6    | VDDC           | D |

| E | VDDP         | PETn1        | VSS_<br>PCIE  | VSS            | EEPROM<br>_EN  | TEST_EN        | DBG4           | VCCO33        | VCCO33         | VDDC             | GPIO5           | GPIO0             | VDDC              | NC              | L2P_<br>DATA5    | L2P_<br>DATA13 | Ε |

| F | VTT_AB       | PETp1        | VSS_<br>PCIE  | NC             | VDDW           | VDDC           | GPIO11         | VCCO33        | VCCO33         | TMS              | TCK             | VDDC              | VDDC              | L2P_RDY         | L2P_<br>DATA4    | L2P_<br>DATA12 | F |

| G | PERp1        | VSS_<br>PCIE | VDDAUX        | VSS            | PECLKINp       | VSS            | VSS            | VSS           | VSS            | VSS              | VSS             | VDDC              | NC                | L2P_EDB         | L2P_<br>CLKn     | L2P_<br>CLKp   | G |

| Н | PERn1        | VSS_<br>PCIE | PCIE_<br>VDDA | VDDC           | PECLKINn       | VSS            | VSS            | VSS           | VSS            | VSS              | VCCO18          | VCCO18            | VSS               | L2P_<br>DFRAME  | VDDC             | L2P_<br>VALID  | Н |

| J | PERn2        | VSS_<br>PCIE | PCIE_<br>VDDA | VSS            | VSS            | NC             | VSS            | VSS           | VSS            | VSS              | VCCO18          | VCCO18            | VDDC              | L_WR_<br>RDY1   | L2P_<br>DATA3    | L2P_<br>DATA11 | J |

| K | PERp2        | VSS_<br>PCIE | VSS           | VDDP           | VDDW           | LCLK_<br>MODE3 | VSS            | VSS           | VSS            | VSS              | VSS             | VSS               | NC                | L_WR_<br>RDY0   | VDDC             | L2P_<br>DATA10 | K |

| L | VSS          | PETp2        | VSS_<br>PCIE  | LCLK_<br>MODE2 | VDDC           | VDDC           | NC             | VCCO18        | VCCO18         | VDDC             | VSS             | VSS               | VDDC              | P_RD_<br>D_RDY1 | L2P_<br>DATA2    | L2P_<br>DATA9  | L |

| М | VTT_CD       | PETn2        | VSS_<br>PCIE  | LCLK_<br>MODE1 | LCLK_<br>MODE0 | VDDC           | VSS            | VCCO18        | VCCO18         | VDDC             | VSS             | VSS               | NC                | P_RD_<br>D_RDY0 | L2P_<br>DATA1    | VDDC           | M |

| N | PETn3        | VSS_<br>PCIE | VDD_<br>PCIE  | NC             | VSS            | RX_<br>ERROR   | NC             | VDDC          | P_WR<br>_REQ0  | VDDC             | P_WR<br>_RDY1   | P_WR<br>_RDY0     | PLL_<br>AVSS      | TX_<br>ERROR    | L2P_<br>DATA0    | L2P_<br>DATA8  | N |

| Р | РЕТр3        | VSS_<br>PCIE | VDD_<br>PCIE  | VSS            | P2L_<br>DATA15 | VDDC           | P2L_<br>VALID  | P2L_CLKp      | P2L_RDY        | P_WR<br>_REQ1    | VC_<br>RDY1     | VC_<br>RDY0       | VDDC              | LCLK            | VDDC             | RSTOUT<br>18   | Р |

| R | VDD_PCIE     | PERp3        | VSS           | P2L_<br>DATA14 | P2L_<br>DATA13 | P2L_<br>DATA12 | P2L_<br>DFRAME | P2L_CLKn      | P2L_<br>DATA11 | VREF             | P2L_<br>DATA10  | P2L_<br>DATA9     | P2L_<br>DATA8     | NC              | VSS              | LCLKn          | R |

| Т | VSS_PCIE     | PERn3        | VSS_PCIE      | VDDC           | P2L_<br>DATA7  | P2L_<br>DATA6  | P2L_<br>DATA5  | P2L_<br>DATA4 | P2L_<br>DATA3  | P2L_<br>DATA2    | P2L_<br>DATA1   | VDDC              | P2L_<br>DATA0     | PLL_<br>AVDD    | NC               | VSS            | Т |

|   | 1            | 2            | 3             | 4              | 5              | 6              | 7              | 8             | 9              | 10               | 11              | 12                | 13                | 14              | 15               | 16             |   |

|   |              |              |               |                | 3.             | 3V             | 1.8V           | 1.3           | 2V             | 900mV            | 0               | V                 |                   |                 |                  |                |   |

# 2.2 Pin Descriptions

Table 2-1: GN4124 Pin Descriptions

| Group  | Pin No. | No. of<br>Pins | Pin Name              | I/O | Description                                                                                                                                                                                                  |

|--------|---------|----------------|-----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Global | В8      | 1              | RSTIN                 | I   | Global Asynchronous Reset (Active LOW). LVCMOS, 3.3V, input, hysteresis.                                                                                                                                     |

|        | C9      | 1              | RSTOUT33              | 0   | Reset Output; 3.3V (Active LOW). 3.3 V LVCMOS, totem-pole.                                                                                                                                                   |

|        | D12     | 1              | LB_REF_CLK_MI         | 1   | Local Bus Reference Clock Crystal or Oscillator Input.                                                                                                                                                       |

|        | C13     | 1              | LB_REF_CLK_MO         | 0   | Local Bus Reference Clock Crystal feedback output. Functional mode only.                                                                                                                                     |

|        | H3, J3  | 2              | PCIE_VDDA             | Р   | Clock Reference Analog Supply. (1.2V)                                                                                                                                                                        |

|        | G5, H5  | 2              | PECLKINp,<br>PECLKINn | I   | PCIe Reference Clock Signal. For a PCI Express add-in card, these signals should be driven by the card edge connector and AC coupled using 150nF capacitors.                                                 |

|        | E5      | 1              | EEPROM_EN             | I   | Used to report that EEPROM is present. (1 = present) LVCMOS, 3.3V, input.                                                                                                                                    |

|        |         |                |                       |     | EEPROM_EN should be tied HIGH, to allow the internal GN4124 registers to load on power up from the EEPROM. Refer to Initialization from a 2-Wire EEPROM from on what is required for EEPROM boot up options. |

| Group                                      | Pin No.                                                                           | No. of<br>Pins | Pin Name     | I/O | Description                                                                                     |

|--------------------------------------------|-----------------------------------------------------------------------------------|----------------|--------------|-----|-------------------------------------------------------------------------------------------------|

| Global:<br>Test Interface                  | A9                                                                                | 1              | TDI          | İ   | JTAG Test Data Input.<br>LVCMOS, 3.3V, input, pull-up.                                          |

|                                            | F10                                                                               | 1              | TMS          | I   | JTAG Test Mode Select Input.<br>LVCMOS, 3.3V, input, pull-up.                                   |

|                                            | F11                                                                               | 1              | TCK          | I   | JTAG Test Clock.<br>LVCMOS, 3.3V, input.                                                        |

|                                            | B12                                                                               | 1              | TRST         | I   | JTAG Test Reset.<br>LVCMOS, 3.3V, input, hysteresis, pull-up.                                   |

|                                            | A14                                                                               | 1              | TDO          | 0   | JTAG Test Data Output.<br>LVTTL, 3.3V, output, 6mA, tristate.                                   |

|                                            | D6                                                                                | 1              | SCAN_EN      | I   | Scan Enable (Tied LOW for normal operations).<br>LVCMOS, 3.3V, input, pull-down.                |

|                                            | E6                                                                                | 1              | TEST_EN      | Ī   | Test Mode Enable (Tied LOW for normal operations). LVCMOS, 3.3V, input, pull-down.              |

|                                            | A15                                                                               | 1              | PLL_TEST_OUT | I/O | PLL Test Output (No connect for normal operations). LVCMOS, 3.3V, bidirectional, 4mA, tristate. |

| Global:<br>2-Wire<br>Interface             | B11                                                                               | 1              | SCLK         | I/O | Two-wire Clock port. LVCMOS, 3.3V, bidirectional, 4mA, tristate.                                |

| meriace                                    | C12                                                                               | 1              | SDATA        | I/O | Two-wire Data port.<br>LVCMOS, 3.3V, bidirectional, 4mA, tristate.                              |

| Global:<br>General<br>Purpose<br>Interface | A6, B7, B6, C7,<br>F7, C8, A7, B9,<br>A10, A11, E11,<br>A13, D9, C10,<br>D11, E12 | 16             | GPIO[15:0]   | I/O | General Purpose Input/Output. LVCMOS, 3.3V, bidirectional, 4mA, tristate.                       |

| Global:<br>Debug<br>Interface              | A5, B5, C5, E7,<br>D7, B4, C6, A4                                                 | 8              | DBG[7:0]     | I   | Debug Bus Port (Tied LOW for normal operations). LVCMOS, 3.3V, input, pull-down.                |

| Group                                            | Pin No.                                                                 | No. of<br>Pins | Pin Name     | I/O | Description                                                                                                  |

|--------------------------------------------------|-------------------------------------------------------------------------|----------------|--------------|-----|--------------------------------------------------------------------------------------------------------------|

| Global:<br>Serial<br>Programming                 | A8                                                                      | 1              | SPRI_CLK     | I/O | Serial Programming Interface (FPGA<br>Configuration Loader).<br>LVCMOS, 3.3V, bidirectional, 12mA, tristate. |

| Interface                                        | B10                                                                     | 1              | SPRI_DATAOUT | I/O | Serial Programming Interface (FPGA<br>Configuration Loader).<br>LVCMOS, 3.3V, bidirectional, 12mA, tristate. |

|                                                  | C11                                                                     | 1              | SPRI_CONFIG  | I/O | Serial Programming Interface (FPGA Configuration Loader).  LVCMOS, 3.3V, bidirectional, 12mA, tristate.      |

|                                                  | A12                                                                     | 1              | SPRI_DONE    | I/O | Serial Programming Interface (FPGA Configuration Loader).  LVCMOS, 3.3V, bidirectional, 12mA, tristate.      |

|                                                  | B13                                                                     | 1              | SPRI_XI_SWAP | I/O | Serial Programming Interface (FPGA Configuration Loader).  LVCMOS, 3.3V, bidirectional, 12mA, tristate.      |

|                                                  | B14                                                                     | 1              | SPRI_STATUS  | I/O | Serial Programming Interface (FPGA Configuration Loader).  LVCMOS, 3.3V, bidirectional, 12mA, tristate.      |

| PCI Express<br>Link:<br>PCIe x4 PHY<br>interface | A1, A3, C2, D2,<br>E3, F3, G2, H2,<br>J2, K2, L3, M3,<br>N2, P2, T1, T3 | 16             | VSS_PCIE     | G   | PHY VSS.                                                                                                     |

|                                                  | B1, C3, D3, N3,<br>P3, R1                                               | 6              | VDD_PCIE     | Р   | PHY VDD.<br>1.2V (Core)                                                                                      |

|                                                  | G3                                                                      | 1              | VDDAUX       | Р   | PHY VDDAUX.<br>1.2V                                                                                          |

|                                                  | F1                                                                      | 1              | VTT_AB       | Р   | PCIe PHY transmit termination lanes A/B. Driven to voltage VTT. 1.5V See Table 3-6.                          |

|                                                  | M1                                                                      | 1              | VTT_CD       | Р   | PCIe PHY transmit termination lanes C/D. Driven to voltage VTT. 1.5V See Table 3-6.                          |

| PCI Express<br>Link:<br>PCIe Transmit            | N1, M2, E2, D1                                                          | 4              | PETn[3:0]    | 0   | PCIe Transmit -Bus Lane A. CML                                                                               |

| [Output from<br>the device]                      | P1, L2, F2, C1                                                          | 4              | PETp[3:0]    | 0   | PCIe Transmit +Bus Lane A. CML                                                                               |

| Group                                                            | Pin No.                                                                          | No. of<br>Pins | Pin Name              | I/O | Description                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Express<br>Link:<br>PCIe Receive<br>[Input to the<br>device] | T2, J1, H1, A2                                                                   | 4              | PERn[3:0]             | I   | PCIe Receive -Bus Lane A.  CML  Note: PERp[3:0] / PERn[3:0] each receiver lane can be connected using either the indicated polarity, or inverted polarity. Inverted polarity may be chosen in order to simplify the PCB layout by avoiding signal crossover and additional PCB vias. The GN4124 will automatically detect and compensate for polarity inversion during link training. |

|                                                                  | R2, K1, G1, B2                                                                   | 4              | PERp[3:0]             | I   | PCIe Receive +Bus Lane A.<br>CML                                                                                                                                                                                                                                                                                                                                                      |

| Local Bus                                                        | P14, R16                                                                         | 2              | LCLK, LCLKn           | 0   | Local Bus Clock.<br>SSTL, 1.8V, differential                                                                                                                                                                                                                                                                                                                                          |

|                                                                  | K6, L4, M4, M5                                                                   | 4              | LCLK_MODE[3:0]        | I   | Selects the clock mode.<br>LVCMOS, 3.3V, input, pull-down.                                                                                                                                                                                                                                                                                                                            |

|                                                                  | P16                                                                              | 1              | RSTOUT18              | 0   | Reset Output; 1.8V (Active LOW).<br>CMOS, 1.8V, output                                                                                                                                                                                                                                                                                                                                |

| Local Bus:<br>PCIe to Local<br>[Inbound Data]                    | P9                                                                               | 1              | P2L_RDY               | I   | Rx Buffer Full Flag.<br>SSTL, 1.8V, input, with ODT.                                                                                                                                                                                                                                                                                                                                  |

| [334.16.24.6]                                                    | P5, R4, R5, R6,<br>R9, R11, R12,<br>R13, T5, T6, T7,<br>T8, T9, T10, T11,<br>T13 | 16             | P2L_DATA[15:0]        | 0   | Parallel Receive Data.<br>SSTL, 1.8V, output                                                                                                                                                                                                                                                                                                                                          |

|                                                                  | R7                                                                               | 1              | P2L_DFRAME            | 0   | Receive Frame.<br>SSTL, 1.8V, output                                                                                                                                                                                                                                                                                                                                                  |

|                                                                  | P7                                                                               | 1              | P2L_VALID             | 0   | Receive Data Valid.<br>SSTL, 1.8V, output                                                                                                                                                                                                                                                                                                                                             |

|                                                                  | P8, R8                                                                           | 2              | P2L_CLKp,<br>P2L_CLKn | 0   | Receiver Source Synchronous Clock.<br>SSTL, 1.8V, output, differential                                                                                                                                                                                                                                                                                                                |

| Group                                          | Pin No.                                                                                       | No. of<br>Pins | Pin Name              | I/O | Description                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------|-----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Local Bus:<br>Inbound Buffer<br>Request/Status | P10, N9                                                                                       | 2              | P_WR_REQ[1:0]         | 0   | PCIe Write Request.<br>SSTL, 1.8V, output                                                                                                                                                                                                                                                                                |

| Requestistatus                                 | N11, N12                                                                                      | 2              | P_WR_RDY[1:0]         | I   | PCIe Write Ready.<br>SSTL, 1.8V, input, with ODT.                                                                                                                                                                                                                                                                        |

|                                                | N6                                                                                            | 1              | RX_ERROR              | I   | Receive Error.<br>SSTL, 1.8V, input, with ODT.                                                                                                                                                                                                                                                                           |

|                                                | P11, P12                                                                                      | 2              | VC_RDY[1:0]           | 0   | Virtual Channel Ready Status.  This provides a VC_RDY output to indicate the DL_UP <sup>1</sup> status of the Virtual Channel. This can be used to provide a synchronous reset to the external application in the event one of the Virtual Channels goes down e.g. hot reset initiated by PCIe host.  SSTL, 1.8V, output |

| Local Bus:<br>Local PCIe<br>[Outbound<br>Data] | B16, C16, E16,<br>F16, J16, K16,<br>L16, N16, C15,<br>D15, E15, F15,<br>J15, L15, M15,<br>N15 | 16             | L2P_DATA[15:0]        | I   | Parallel Transmit Data. SSTL, 1.8V, input, with ODT.                                                                                                                                                                                                                                                                     |

|                                                | H14                                                                                           | 1              | L2P_DFRAME            | I   | Transmit Data Frame.<br>SSTL, 1.8V, input, with ODT.                                                                                                                                                                                                                                                                     |

|                                                | H16                                                                                           | 1              | L2P_VALID             | I   | Transmit Data Valid.<br>SSTL, 1.8V, input, with ODT.                                                                                                                                                                                                                                                                     |

|                                                | G14                                                                                           | 1              | L2P_EDB               | I   | End-of-Packet Bad Flag.  When a packet is considered bad and is terminated with EDB.  SSTL, 1.8V, input, with ODT.                                                                                                                                                                                                       |

|                                                | G16, G15                                                                                      | 2              | L2P_CLKp,<br>L2P_CLKn | I   | Transmitter Source Synchronous Clock. SSTL, 1.8V, input, differential, with ODT.                                                                                                                                                                                                                                         |

| Local Bus:<br>Outbound                         | F14                                                                                           | 1              | L2P_RDY               | 0   | Tx Buffer Full Flag.<br>SSTL, 1.8V, output                                                                                                                                                                                                                                                                               |

| Buffer Status                                  | J14, K14                                                                                      | 2              | L_WR_RDY[1:0]         | 0   | Local-to-PCIe Write.<br>SSTL, 1.8V, output                                                                                                                                                                                                                                                                               |

|                                                | L14, M14                                                                                      | 2              | P_RD_D_RDY[1:0]       | 0   | PCIe-to-Local Read Response Data Ready.<br>SSTL, 1.8V, output                                                                                                                                                                                                                                                            |

|                                                | N14                                                                                           | 1              | TX_ERROR              | 0   | Transmit Error.<br>SSTL, 1.8V, output                                                                                                                                                                                                                                                                                    |

| Group      | Pin No.                                                                                                                                                                                                                         | No. of<br>Pins | Pin Name | I/O | Description                                                                                                                                                                                              |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power      | F5, K5                                                                                                                                                                                                                          | 2              | VDDW     | Р   | 3.3V                                                                                                                                                                                                     |

|            | R10                                                                                                                                                                                                                             | 1              | VREF     | Р   | 900mV reference voltage for SSTL I/O                                                                                                                                                                     |

|            | T14                                                                                                                                                                                                                             | 1              | PLL_AVDD | Р   | 1.2V PLL supply voltage                                                                                                                                                                                  |

|            | D5, D8, D13,<br>D16, E10, E13,<br>F6, F12, F13,<br>G12, H4, H15,<br>J13, K15, L5, L6,<br>L10, L13, M6,<br>M10, M16, N8,<br>N10, P6, P13,<br>P15, T4, T12                                                                        | 28             | VDDC     | P   | 1.2V core power                                                                                                                                                                                          |

|            | E1, K4                                                                                                                                                                                                                          | 2              | VDDP     | Р   | 3.3V                                                                                                                                                                                                     |

|            | H11, H12, J11,<br>J12, L8, L9, M8,<br>M9                                                                                                                                                                                        | 8              | VCCO18   | Р   | Power for 1.8V I/O                                                                                                                                                                                       |

|            | E8, E9, F8, F9                                                                                                                                                                                                                  | 4              | VCCO33   | Р   | Power for 3.3V I/O                                                                                                                                                                                       |

| Ground     | N13                                                                                                                                                                                                                             | 1              | PLL_AVSS | G   | PLL Ground.  This pin is internally connected to VSS and, for noise isolation, should not be connected to VSS externally. Refer to the Gullwing RDK schematics and PCB layout for proper implementation. |

|            | A16, B15, C4,<br>C14, D4, E4, G4,<br>G6, G7, G8, G9,<br>G10, G11, H6,<br>H7, H8, H9,<br>H10, H13, J4, J5,<br>J7, J8, J9, J10,<br>K3, K7, K8, K9,<br>K10, K11, K12,<br>L1, L11, L12,<br>M7, M11, M12,<br>N5, P4, R3, R15,<br>T16 | 43             | VSS      | G   | Ground.                                                                                                                                                                                                  |

| No Connect | B3, D10, D14,<br>E14, F4, G13, J6,<br>K13, L7, M13,<br>N4, N7, R14,<br>T15                                                                                                                                                      | 14             | NC       | _   | No Connect.                                                                                                                                                                                              |

<sup>1.</sup> Data Link Layer indicates that a connection with the upstream devices has been established.

# 3. Electrical Characteristics

## 3.1 Absolute Maximum Ratings

**Table 3-1: Absolute Maximum Ratings**

| Parameter                 | Value                          |

|---------------------------|--------------------------------|

| Core Supply Voltage       | -0.5V to +1.8 VDC              |

| SSTL IO Supply Voltage    | -0.5V to +2.5 V <sub>DC</sub>  |

| LVCMOS IO Supply Voltage  | -0.5V to +4.6 V <sub>DC</sub>  |

| Input ESD Voltage (HBM)   | 2kV                            |

| Storage Temperature Range | -50°C < T <sub>s</sub> < 125°C |

| Solder Reflow Temperature | 260°C                          |

### **3.2 Operating Conditions**

#### **Table 3-2: Operating Conditions**

All electrical characteristics are valid over the range of these operating conditions, unless otherwise noted.

| Parameter                                                               | Symbol              | Conditions | Min  | Тур | Max  | Units | Notes |

|-------------------------------------------------------------------------|---------------------|------------|------|-----|------|-------|-------|

| Core Supply Voltage on pins VDDC, VDD_PCIE, VDDAUX, PLL_AVDD, PCIE_VDDA | $V_{CORE}$          | -          | 1.14 | 1.2 | 1.26 | V     | ±5%   |

| SSTL IO Supply Voltage on pins VCCO18                                   | V <sub>VCCO18</sub> | -          | 1.71 | 1.8 | 1.89 | V     | ±5%   |

| LVCMOS IO and 3.3V Core<br>Supply Voltage: pins VCCO33,<br>VDDW, VDDP   | V <sub>VCCO33</sub> | -          | 3.0  | 3.3 | 3.6  | V     | ±10%  |

| Operating Temperature<br>Range                                          | T <sub>A</sub>      | Ambient    | 0    | 25  | 85   | °C    |       |

### 3.3 DC Electrical Characteristics

#### **Table 3-3: DC Electrical Characteristics**

Power and current limits listed have been derived from design and characteristics data. They are not 100% tested in production.

| Parameter                                                                     | Symbol              | Conditions              | Min | Тур              | Max                           | Units | Notes |

|-------------------------------------------------------------------------------|---------------------|-------------------------|-----|------------------|-------------------------------|-------|-------|

| Power Consumption                                                             | P <sub>D</sub>      | PCIe x4,<br>LCLK=200MHz | _   | 650              | 950                           | mW    | 1     |

|                                                                               |                     | PCIe x4,<br>LCLK=100MHz | -   | 600              | -                             | mW    | 2     |

|                                                                               |                     | PCIe x1,<br>LCLK=100MHz | -   | 475              | _                             | mW    | 3     |

| Total Core Supply Current on pins VDDC, VDD_PCIE, VDDAUX, PLL_AVDD, PCIE_VDDA | I <sub>CORE</sub>   | -                       | -   | 110 <sup>4</sup> | –<br>(See Note <sup>5</sup> ) | mA    | -     |

| SSTL IO Supply Current                                                        | I <sub>VCCO18</sub> | -                       | -   | 340 <sup>6</sup> | -<br>(See Note 5)             | mA    | _     |

| LVCMOS IO and 3.3V Core<br>Supply Current: pins VCCO33,<br>VDDW, VDDP         | I <sub>VCCО33</sub> | -                       | -   | 90 <sup>7</sup>  | -<br>(See Note<br>5.)         | mA    | -     |

- 1. Data is based on an application circuit equivalent to that used on the GN4124 RDK board (Gullwing), typical operating conditions, PCle negotiated to 4 lanes, default PCle PHY settings, 200MHz local bus operation, and with concurrent data traffic at 75% bus utilization. Doesn't include power dissipated by components outside of the GN4124.

- 2. See Note 1. Typical operating conditions, 100MHz local bus operation.

- 3. See Note 1. Typical operating conditions, 100MHz local bus operation, PCIe negotiated to 1 lane.

- 4. This information is intended to guide power supply design. Data is based on an application circuit equivalent to that used on the GN4124 RDK board (Gullwing), typical operating conditions, 200MHz local bus operation, and with concurrent data traffic at 75% bus utilization.

- 5. Maximum supply current will vary greatly depending on the application circuit and device usage. A specific application's maximum current can be be predicted by measuring current under high temperature, high supply and full load conditions. To this resultant number, the following factors needed to be added:

- +25% for  $I_{CORE}$

- +35% for  $I_{VCCO18}$

- +25% for I<sub>VCCO33</sub>

- 6. See Note 4. Based on use of 22-ohm serial termination and 51-ohm parallel termination in the application circuit.

- 7. See Note 4. Also includes current draw from an LDO used to power VTT\_AB and VTT\_CD.

**Table 3-4: DC Electrical Characteristics for LVCMOS Buffers**

| Parameter                 | Symbol          | Conditions    | Min | Тур | Max | Units | Notes |

|---------------------------|-----------------|---------------|-----|-----|-----|-------|-------|

| High-level input voltage  | V <sub>IH</sub> | -             | 2   | -   | -   | V     | _     |

| Low-level input voltage   | VIL             | -             | _   | _   | 0.8 | V     | _     |

| Input leakage current     | IL              | -             | -   | -   | ±5  | μΑ    | _     |

| High-level output voltage | V <sub>OH</sub> | IOH = -100 μA | 2.8 | _   | -   | V     | _     |

| Low-level output voltage  | VOL             | IOL = 100 μA  | _   | =   | 0.2 | V     | -     |

**Table 3-5: DC Electrical Characteristics for SSTL Buffers**

| Parameter                     | Symbol           | Conditions | Min                   | Тур              | Max                          | Units | Notes |

|-------------------------------|------------------|------------|-----------------------|------------------|------------------------------|-------|-------|

| VREF input reference voltage  | V <sub>REF</sub> | -          | 833                   | 900              | 969                          | mV    | 1     |

| SSTL termination voltage      | V <sub>TT</sub>  | -          | V <sub>REF</sub> -40  | V <sub>REF</sub> | V <sub>REF</sub> +40         | mV    | 2     |

| High-level input voltage (DC) | V <sub>IH</sub>  | _          | V <sub>REF</sub> +125 | -                | V <sub>VCCO18</sub> +<br>300 | mV    | _     |

| Low-level input voltage (DC)  | $V_{IL}$         | -          | -300                  | -                | V <sub>REF</sub> -125        | mV    | _     |

| High-level input voltage (AC) | V <sub>IH</sub>  | -          | V <sub>REF</sub> +250 | -                | _                            | mV    | -     |

| Low-level input voltage (AC)  | $V_{IL}$         | -          | -                     | -                | V <sub>REF</sub> -250        | mV    | -     |

<sup>1.</sup> Typically the value of VREF is expected to be 50% \* VDDQ of the transmitting device. Peak to peak AC noise on VREF may not exceed +/- 2% of VREF.

## **3.4 PCI Express Electrical Characteristics**

### **3.4.1 PCI Express Transmitter Characteristics**

**Table 3-6: Transmitter Characteristics**

| Symbol                            | Description                                            | Min     | Typical                                       | Max  | Unit |

|-----------------------------------|--------------------------------------------------------|---------|-----------------------------------------------|------|------|

| Voltage Parameters                |                                                        |         |                                               |      |      |

| V <sub>TX-DIFF</sub> <sup>1</sup> | Output voltage compliance @ typica                     | l swing |                                               |      |      |

|                                   | V <sub>TX-DIFFp</sub> (peak-to-peak, single ended)     | 400     | 500                                           | 600  | mV   |

|                                   | V <sub>TX-DIFFpp</sub> (peak-to-peak,<br>differential) | 800     | 1000                                          | 1200 | mV   |

| V <sub>TT</sub>                   | Transmitter termination voltage                        | 1.2     | 1.5                                           | 1.89 | V    |

| V <sub>OL</sub>                   | Low-level output voltage                               | -       | V <sub>TT</sub> - 1.5 * V <sub>TX-DIFFp</sub> | _    | V    |

<sup>2.</sup> The termination voltage VTT should track the reference voltage VREF.

| Symbol                                       | Description                                                                                        | Min    | Typical                                       | Max               | Unit            |

|----------------------------------------------|----------------------------------------------------------------------------------------------------|--------|-----------------------------------------------|-------------------|-----------------|

| V <sub>OH</sub>                              | High-level output voltage                                                                          | -      | V <sub>TT</sub> - 0.5 * V <sub>TX-DIFFp</sub> | -                 | V               |

| V <sub>TX-DC-CM</sub>                        | Transmit common-mode voltage                                                                       | 0      | V <sub>TT</sub> - V <sub>TX-DIFFp</sub>       | 3.6               | V               |

| V <sub>TX-CM-DCACTIVE</sub> -                | Absolute Delta of DC Common Mode<br>Voltage During L0 and Electrical Idle.                         | -      | -                                             | 100               | mV              |

| V <sub>TX-DE-RATIO</sub>                     | De-emphasized differential output voltage                                                          | 0      | -3.35                                         | -7.96             | dB <sup>2</sup> |

| V <sub>TX-IDLE-DIFFp</sub>                   | Electric Idle differential peak voltage                                                            | _      | -                                             | 20                | mV              |

| V <sub>TX-RCV-DETECT</sub>                   | Voltage change during Receive<br>Detection                                                         | _      | -                                             | 600               | mV              |

| RL <sub>TX-DIFF</sub>                        | Transmitter Differential Return loss                                                               | 10     | -                                             | -                 | dB              |

| RL <sub>TX-CM</sub>                          | Transmitter Common Mode Return<br>loss                                                             | 6      | -                                             | -                 | dB              |

| Z <sub>OSE</sub>                             | Single-ended output impedance                                                                      | 40     | 50                                            | 60                | Ω               |

| Z <sub>TX-DIFF-DC</sub>                      | DC Differential TX Impedance                                                                       | 80     | 100                                           | 120               | Ω               |

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub>  | Rise / Fall time of TxP, TxN outputs                                                               | .125   | -                                             |                   | UI <sup>3</sup> |

| Jitter Parameters                            |                                                                                                    |        |                                               |                   |                 |

| UI                                           | Unit Interval                                                                                      | 399.88 | 400                                           | 400.12            | ps <sup>4</sup> |

| T <sub>TX-MAX-JITTER</sub>                   | Transmitter total jitter<br>(peak-to-peak)                                                         | _      | -                                             | 0.30 <sup>5</sup> | UI              |

| T <sub>TX-EYE</sub>                          | Minimum TX Eye Width<br>(1 - T <sub>TX-MAX-JITTER</sub> )                                          | 0.70   | -                                             | -                 | UI              |

| T <sub>TX-EYE-MEDIAN-to-MAX-</sub><br>JITTER | Maximum time between the jitter median and maximum deviation from the median                       | -      | -                                             | 0.15              | UI              |

| Timing Parameters                            |                                                                                                    |        |                                               |                   |                 |

| L <sub>TX-SKEW</sub>                         | Transmitter data skew between any 2 lanes                                                          | 0      | -                                             | 2UI +<br>200ps    | ps              |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>             | Maximum time to transition to a valid electrical idle after sending an Electrical Idle ordered set | -      | 4                                             | 6                 | ns              |

| T <sub>EIExit</sub>                          | Time to exit Electrical Idle (L0s) state into L0                                                   | -      | 12                                            | 16                | ns              |

- 1. Measured with Vtt = 1.2V, PHY\_CONTROL register bits HIDRV='0', LODRV='0' and DTX="0000"(1x).

- 2. The de-emphasis ratio is determined through the DEQ bits of the PHY\_CONTROL register inside the GN4124. Typical value is based on recommended setting of the PHY\_CONTROL register.

- 3. As measured between 20% and 80% points.

- 4. UI does not account for SSC dictated variations.

- 5. Measured using PCI Express Compliance Pattern.

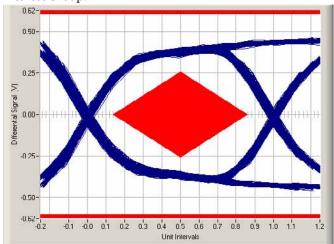

Figure 3-1: Typical Transition Signal Eye, De-emphasis Disabled, Default Drive Setting

The eye diagram is generated from SIGtest Version 2.1 available from the PCI Special Interest Group.

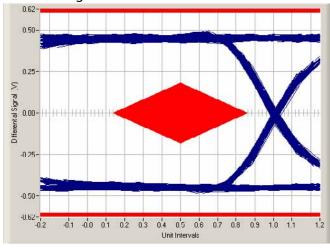

Figure 3-2: Typical Non-Transition Signal Eye, De-emphasis Disabled, Default Drive Setting

## **3.4.2 PCI Express Receiver Characteristics**

**Table 3-7: PCI Express Receiver Characteristics**

| Symbol                                       | Description                                                                                                | Min  | Typical | Max   | Unit |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------|------|---------|-------|------|

| Voltage Parameters                           |                                                                                                            |      |         |       |      |

| V <sub>RX-DIFFp-p</sub>                      | Differential input voltage<br>(peak-to-peak)                                                               | 170  | -       | 1200  | mV   |

| V <sub>RX-IDLE-DET-DIFFp-p</sub>             | Differential input threshold voltage (peak-to-peak) to assert TxIdleDetect output                          | 65   | -       | 235   | mV   |

| V <sub>RX-CM-AC</sub>                        | Receiver common-mode voltage for AC-coupling                                                               |      | 0       | 150   | mV   |

| T <sub>RX-RISE</sub> , T <sub>RX-FALL</sub>  | Rise time / Fall time of RxP, RxN inputs                                                                   | _    | _       | 160   | ps   |

| Z <sub>RX-DIFF-DC</sub>                      | Differential input impedance (DC)                                                                          | 80   | 100     | 120   | Ω    |

| Z <sub>RX-COM-DC</sub>                       | Single-ended input impedance                                                                               | 40   | 50      | 60    | Ω    |

| Z <sub>RX-COM-INITIAL-DC</sub>               | Initial input common mode impedance (DC)                                                                   | 5    | 50      | 60    | Ω    |

| Z <sub>RX-COM-HIGH-IMP-DC</sub>              | Powered down input common mode impedance (DC)                                                              | 200k | _       | -     | Ω    |

| RL <sub>RX-DIFF</sub>                        | Receiver Differential Return Loss <sup>1</sup>                                                             | 10   | -       | -     | dB   |

| R <sub>LRX-CM</sub>                          | Receiver Common Mode Return Loss                                                                           | 6    | -       | -     | dB   |

| Jitter Parameters                            |                                                                                                            |      |         |       |      |

| T <sub>RX-MAX-JITTER</sub>                   | Receiver maximum total jitter tolerance                                                                    | 0.65 | -       | -     | UI   |

| T <sub>RX-EYE</sub>                          | Minimum Receiver Eye Width                                                                                 | 0.35 | -       | -     | UI   |

| T <sub>RX-EYE-MEDIAN-to-MAX-</sub><br>JITTER | Maximum time between jitter<br>median and max deviation from<br>median                                     | -    | -       | 0.325 | UI   |

| Timing Parameters                            |                                                                                                            |      |         |       |      |

| T <sub>RX-SKEW</sub>                         | Maximum skew across all 4 lanes of the link                                                                | -    | -       | 20    | ns   |

| $T_{BDDIy}$                                  | Beacon-Activity on channel to detection of Beacon <sup>2</sup>                                             | 33   | -       | 100   | ns   |

| T <sub>RX-IDLE_ENTER</sub>                   | Delay from detection of Electrical<br>Idle condition on the channel to<br>assertion of TxIdleDetect output | -    | 10      | 20    | ns   |

| T <sub>RX-IDLE_EXIT</sub>                    | Delay from detection of L0s to L0<br>transition to de-assertion of<br>TxIdleDetect output                  | -    | 5       | 10    | ns   |

<sup>1.</sup> Over a frequency range of 50MHz to 1.25GHz.

<sup>2.</sup> This is a function of beacon frequency.

Table 3-8: Reference Clock (PECLKINn) Requirements

| Symbol                               | Description                                                         | Min  | Typical  | Max                   | Unit             |

|--------------------------------------|---------------------------------------------------------------------|------|----------|-----------------------|------------------|

| V <sub>IL-RC</sub>                   | Low-level CML/CMOS input voltage                                    | 0    | _        | V <sub>DD</sub> - 0.5 | V                |

| V <sub>IH-RC</sub>                   | High-level CML/CMOS input voltage                                   | _    | $V_{DD}$ |                       | V                |

| F <sub>RefClk</sub>                  | Clock frequency range                                               | 99.5 | 100      | 100.03                | MHz <sup>1</sup> |

| D.C. <sub>RefClk</sub>               | Duty cycle                                                          | 40   | 50       | 60                    | %                |

| T <sub>Skew-Ref</sub>                | Skew between PECLKINp/PECLKINn inputs                               | -    | -        | 0.05                  | RCUI             |

| TCCJITTER                            | Cycle to Cycle jitter                                               | -    | -        | 150                   | ps               |

| T <sub>RRef</sub> ,T <sub>FRef</sub> | Rise/Fall time of PECLKINp/PECLKINn inputs                          | -    | 0.2      | 0.25                  | RCUI             |

| PPM                                  | PPM difference between reference clocks on different ends of a link | -300 | -        | +300                  | PPM              |

<sup>1.</sup> Includes 0 to -0.5% spread spectrum clock range.

### 3.4.3 Local Bus Timing

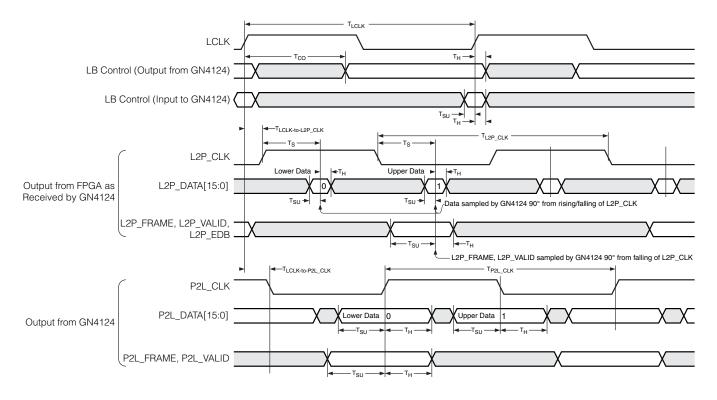

Figure 3-3 illustrates the timing relationships of the three local bus clock domains.

Figure 3-3: Local Bus Timing

Table 3-9: Local Bus Signal Timing for Single Data Rate SSTL Over Specified Operating Conditions (TARGET SPECIFICATION)

| Symbol            | Description                                                     | Min | Max              | Units           |

|-------------------|-----------------------------------------------------------------|-----|------------------|-----------------|

| T <sub>LCLK</sub> | LCLK Cycle Time                                                 | 5   | 10               | ns              |

| T <sub>CO</sub>   | Clock to output delay for local bus control signals             | 0.7 | 5.0              | ns <sup>1</sup> |