Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### GS1559 HD-LINX™ II Multi-Rate Deserializer with Loop-Through Cable Driver

### **Key Features**

- SMPTE 292M and SMPTE 259M-C compliant descrambling and NRZI —NRZ decoding (with bypass)

- DVB-ASI 8b/10b decoding

- Auto-configuration for HD-SDI and SD-SDI

- Serial loop-through Cable Driver output selectable as reclocked or non-reclocked

- Dual serial digital input buffers with 2 x 1 mux

- Integrated serial digital signal termination

- Integrated Reclocker

- Automatic or Manual rate selection/indication (HD/SD)

- Descrambler Bypass option

- User selectable additional processing features including:

- CRC, TRS, ANC data checksum, line number and EDH CRC error detection and correction

- Programmable ANC data detection

- Illegal code remapping

- Internal Flywheel for noise immune H, V, F extraction

- FIFO load Pulse

- 20-bit/10-bit CMOS parallel output data bus

- 148.5MHz / 74.25MHz / 27MHz / 13.5MHz parallel digital output

- Automatic standards detection and indication

- 1.8V core Power Supply and 3.3V Charge Pump Power Supply

- 3.3V digital I/O supply

- JTAG test interface

- Available in a Pb-free package

- Small footprint (11mm x 11mm)

#### **Applications**

- SMPTE 292M Serial Digital Interfaces

- SMPTE 259M-C Serial Digital Interfaces

- DVB-ASI Serial Digital Interfaces

### **Description**

The GS1559 is a reclocking Deserializer with a serial loop-through Cable Driver. When used in conjunction with the GS1574 Automatic Cable Equalizer and the GO1555/GO1525\* Voltage Controlled Oscillator, a receive solution can be realized for HD-SDI, SD-SDI and DVB-ASI applications.

In addition to reclocking and deserializing the input data stream, the GS1559 performs NRZI-to-NRZ decoding, descrambling as per SMPTE 292M/259M-C, and word alignment when operating in SMPTE mode. When operating in DVB-ASI mode, the device will word align the data to K28.5 sync characters and 8b/10b decode the received stream.

Two serial digital input buffers are provided with a 2x1 Multiplexer to allow the device to select from one of two serial digital input signals.

The Integrated Reclocker features a very wide Input Jitter Tolerance of  $\pm 0.3$  UI (total 0.6 UI), a rapid asynchronous lock time, and full compliance with DVB-ASI data streams.

An integrated Cable Driver is provided for serial input loop-through applications and can be selected to output either buffered or reclocked data. This Cable Driver also features an output mute on loss of signal, high-impedance mode, adjustable signal swing, and automatic dual slew-rate selection depending on HD/SD operational requirements.

The GS1559 also includes a range of data processing functions such as error detection and correction, automatic standards detection, and EDH support. The device can also detect and extract SMPTE 352M payload identifier packets and independently identify the received video standard. This information is read from internal registers via the Host Interface port.

Line-based CRC errors, line number errors, TRS errors, EDH CRC errors and ancillary data checksum errors can all be detected. A single 'DATA\_ERROR' pin is provided which is a logical 'OR'ing of all detectable errors. Individual error status is stored in internal 'ERROR\_STATUS' registers.

Finally, the device can correct detected errors and insert new TRS ID words, line-based CRC words, ancillary data checksum words, EDH CRC words, and line numbers. Illegal code re-mapping is also available. All processing functions may be individually enabled or disabled via Host Interface control.

\*For new designs use the GO1555.

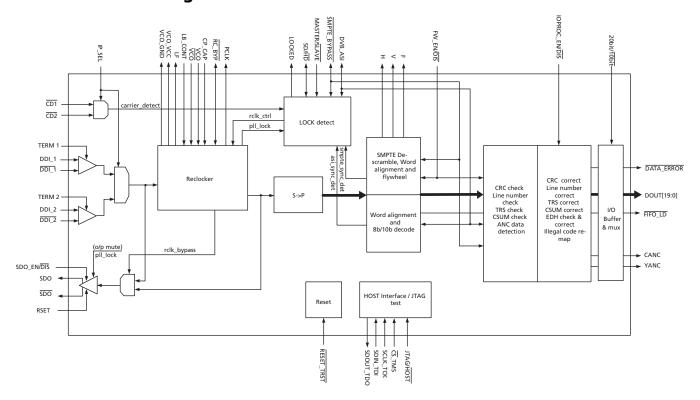

## **Functional Block Diagram**

**GS1559 Functional Block Diagram**

## **Revision History**

| Version | ECR    | PCN   | Date            | Changes and / or Modifications                                                                                                                                                                                                                                                                   |

|---------|--------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8       | 147971 | 50711 | July 2008       | Changed register RASTER_STRUCTURE2 from 12 bits to 13 bits in Table 4-8: Host Interface Description for Raster Structure Registers. Changed SMPTE 352 Lines from 13 to 10 in Table 4-9: Supported Video Standards. Removed references to DVB_ASI in Master mode. Updated document to new format. |

| 7       | 145031 | _     | May<br>2007     | Updated description of H2 from PDBUFF_GND to EQ_GND in Table 1-1: Pin Descriptions. Changed GND_EQ to EQ_GND in 5.2 Typical Application Circuit (Part B).                                                                                                                                        |

| 6       | 143592 | 42774 | January<br>2007 | Added RoHS compliance statement to 7.3 Packaging Data. Recommended GO1555 VCO for new designs.                                                                                                                                                                                                   |

| 5       | 140420 | 39452 | May<br>2006     | Corrected minor typing errors in Functional Block Diagram. Modified video format numbers for system 1125 on Table 4-4: Switch Line Position for Digital Systems.                                                                                                                                 |

## **Contents**

| Key Features                                          | 1  |

|-------------------------------------------------------|----|

| Applications                                          | 1  |

| Description                                           | 1  |

| Functional Block Diagram                              | 2  |

| Revision History                                      | 2  |

| 1. Pin Out                                            | 5  |

| 1.1 Pin Assignment                                    | 5  |

| 1.2 Pin Descriptions                                  | 6  |

| 2. Electrical Characteristics                         | 16 |

| 2.1 Absolute Maximum Ratings                          | 16 |

| 2.2 DC Electrical Characteristics                     | 16 |

| 2.3 AC Electrical Characteristics                     |    |

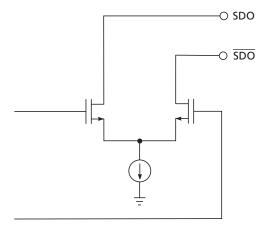

| 3. Input/Output Circuits                              | 20 |

| 3.1 Host Interface Map                                | 22 |

| 3.1.1 Host Interface Map (R/W Configurable Registers) | 23 |

| 3.1.2 Host Interface Map (Read Only Registers)        | 24 |

| 4. Detailed Description                               | 25 |

| 4.1 Functional Overview                               | 25 |

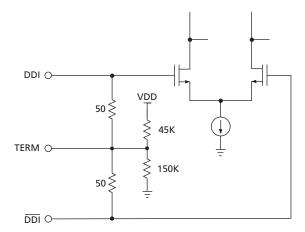

| 4.2 Serial Digital Input                              | 25 |

| 4.2.1 Input Signal Selection                          | 25 |

| 4.2.2 Carrier Detect Input                            | 26 |

| 4.2.3 Single Input Configuration                      | 26 |

| 4.3 Serial Digital Reclocker                          | 26 |

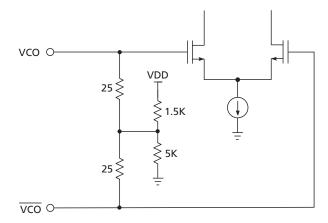

| 4.3.1 External VCO                                    |    |

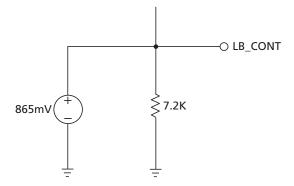

| 4.3.2 Loop Bandwidth                                  | 27 |

| 4.4 Serial Digital Loop-Through Output                | 27 |

| 4.4.1 Output Swing                                    | 27 |

| 4.4.2 Reclocker Bypass Control                        | 28 |

| 4.4.3 Serial Digital Output Mute                      |    |

| 4.5 Serial-To-Parallel Conversion                     |    |

| 4.6 Modes Of Operation                                | 29 |

| 4.6.1 Lock Detect                                     |    |

| 4.6.2 Master Mode                                     |    |

| 4.6.3 Slave Mode                                      | 31 |

| 4.7 SMPTE Functionality                               | 31 |

| 4.7.1 SMPTE Descrambling and Word Alignment           |    |

| 4.7.2 Internal Flywheel                               |    |

| 4.7.3 Switch Line Lock Handling                       | 33 |

| 4.7.4 HVF Timing Signal Generation                    |    |

| 4.8 DVB-ASI Functionality                             |    |

| 4.8.1 DVB-ASI 8b/10b Decoding and Word Alignment      |    |

| 4.8.2 Status Signal Outputs                           | 38 |

| 4.9 Data Through Mode                                     | 39 |

|-----------------------------------------------------------|----|

| 4.10 Additional Processing Functions                      | 39 |

| 4.10.1 FIFO Load Pulse                                    | 39 |

| 4.10.2 Ancillary Data Detection and Indication            | 40 |

| 4.10.3 SMPTE 352M Payload Identifier                      | 43 |

| 4.10.4 Automatic Video Standard and Data Format Detection | 44 |

| 4.10.5 Error Detection and Indication                     | 47 |

| 4.10.6 Error Correction and Insertion                     | 53 |

| 4.10.7 EDH Flag Detection                                 | 55 |

| 4.11 Parallel Data Outputs                                | 57 |

| 4.11.1 Parallel Data Bus Buffers                          | 57 |

| 4.11.2 Parallel Output in SMPTE Mode                      | 58 |

| 4.11.3 Parallel Output in DVB-ASI Mode                    | 58 |

| 4.11.4 Parallel Output in Data-Through Mode               | 59 |

| 4.11.5 Parallel Output Clock (PCLK)                       | 59 |

| 4.12 GSPI Host Interface                                  | 60 |

| 4.12.1 Command Word Description                           | 61 |

| 4.12.2 Data Read and Write Timing                         | 61 |

| 4.12.3 Configuration and Status Registers                 | 62 |

| 4.13 JTAG                                                 | 63 |

| 4.14 Device Power Up                                      | 64 |

| 4.15 Device Reset                                         | 64 |

| 5. Application Reference Design                           | 65 |

| 5.1 Typical Application Circuit (Part A)                  | 65 |

| 5.2 Typical Application Circuit (Part B)                  | 66 |

| 6. References & Relevant Standards                        | 67 |

| 7. Package & Ordering Information                         | 68 |

| 7.1 Package Dimensions                                    | 68 |

| 7.2 Solder Reflow Profiles                                | 69 |

| 7.3 Packaging Data                                        | 70 |

| 7.4 Ordering Information                                  | 70 |

# 1. Pin Out

# 1.1 Pin Assignment

|   | 1            | 2           | 3               | 4                 | 5                | 6                | 7              | 8       | 9      | 10     |

|---|--------------|-------------|-----------------|-------------------|------------------|------------------|----------------|---------|--------|--------|

| Α | LF           | VCO_<br>VCC | VCO_<br>GND     | VCO               | VCO              | NC               | PCLK           | IO_VDD  | DOUT18 | DOUT19 |

| В | CP_CAP       | CP_VDD      | CP_GND          | LB_<br>CONT       | NC               | NC               | FW_EN<br>/DIS  | IO_GND  | DOUT16 | DOUT17 |

| С | BUFF<br>_VDD | PD_VDD      | PD/BUFF<br>_GND | NC                | NC               | MASTER/<br>SLAVE | RC_BYP         | YANC    | DOUT14 | DOUT15 |

| D | DDI1         | NC          | NC              | IP_SEL            | DVB_ASI          | LOCKED           | NC             | CANC    | DOUT12 | DOUT13 |

| Е | DDI1         | TERM1       | NC              | SD/HD             | CORE<br>_GND     | CORE<br>_VDD     | NC             | IO_VDD  | DOUT10 | DOUT11 |

| F | CD1          | NC          | NC              | 20bit/<br>10bit   | CORE<br>_GND     | CORE<br>_VDD     | NC             | IO_GND  | DOUT8  | DOUT9  |

| G | DDI2         | NC          | NC              | IOPROC<br>_EN/DIS | SMPTE_<br>BYPASS | RESET<br>_TRST   | NC             | FIFO_LD | DOUT6  | DOUT7  |

| Н | DDI2         | TERM2       | NC              | CS_<br>TMS        | SCLK<br>_TCK     | SDOUT<br>_TDO    | DATA_<br>ERROR | н       | DOUT4  | DOUT5  |

| J | CD2          | NC          | NC              | NC                | SDO_EN<br>/DIS   | SDIN<br>_TDI     | V              | IO_GND  | DOUT2  | DOUT3  |

| K | RSET         | CD_VDD      | SDO             | SD0               | CD_GND           | JTAG/<br>HOST    | F              | IO_VDD  | DOUT0  | DOUT1  |

# **1.2 Pin Descriptions**

**Table 1-1: Pin Descriptions**

| Pin<br>Number                                                                                           | Name     | Timing | Туре            | Description                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------|----------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

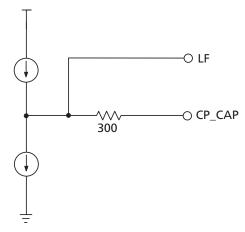

| A1                                                                                                      | LF       | Analog | Output          | Control voltage to external Voltage Controlled Oscillator. Nominally +1.25V DC.                                                                      |

| A2                                                                                                      | VCO_VCC  | -      | Output<br>Power | Power Supply for the external Voltage Controlled Oscillator. Connect to pin 7 of the GO1555/GO1525*. This pin is an output.                          |

|                                                                                                         |          |        |                 | Should be isolated from all other power supplies.                                                                                                    |

|                                                                                                         |          |        |                 | *For new designs use the GO1555.                                                                                                                     |

| А3                                                                                                      | VCO_GND  | -      | Output<br>Power | Ground reference for the external Voltage Controlled Oscillator.<br>Connect to pins 2, 4, 6, and 8 of the GO1555/GO1525*. This pin is an output.     |

|                                                                                                         |          |        |                 | Should be isolated from all other grounds.                                                                                                           |

|                                                                                                         |          |        |                 | *For new designs use the GO1555.                                                                                                                     |

| A4, A5                                                                                                  | VCO, VCO | Analog | Input           | Differential inputs for the external VCO reference signal. For single ended devices such as the GO1555/GO1525*, VCO should be AC coupled to VCO_GND. |

|                                                                                                         |          |        |                 | VCO is nominally 1.485GHz.                                                                                                                           |

|                                                                                                         |          |        |                 | *For new designs use the GO1555.                                                                                                                     |

| A6, B5,<br>B6, C4,<br>C5, D2,<br>D3, D7,<br>E3, E7, F2,<br>F3, F7, G2,<br>G3, G7,<br>H3, J2, J3,<br>J4, | NC       | -      | -               | No Connect.                                                                                                                                          |

| A7                                                                                                      | PCLK     | -      | Output          | PARALLEL DATA BUS CLOCK<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                |

|                                                                                                         |          |        |                 | HD 20-bit mode PCLK = 74.25MHz or 74.25/1.001MHz                                                                                                     |

|                                                                                                         |          |        |                 | HD 10-bit mode PCLK = 148.5MHz or 148.5/1.001MHz                                                                                                     |

|                                                                                                         |          |        |                 | SD 20-bit mode PCLK = 13.5MHz                                                                                                                        |

|                                                                                                         |          |        |                 | SD 10-bit mode PCLK = 27MHz                                                                                                                          |

| A8, E8, K8                                                                                              | IO_VDD   | -      | Power           | Power Supply connection for digital I/O buffers. Connect to +3.3V DC digital.                                                                        |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number                                | Name        | Timing                   | Туре   | Description                                                                                           |                                                                                                                                         |  |

|----------------------------------------------|-------------|--------------------------|--------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| A10, A9,<br>B10, B9,<br>C10, C9,<br>D10, D9, | DOUT[19:10] | Synchronous<br>with PCLK | Output | PARALLEL DATA BUS Signal levels are LVCMOS/LVTTL compatible. DOUT19 is the MSB and DOUT10 is the LSB. |                                                                                                                                         |  |

| E10, E9                                      |             |                          |        | HD 20-bit mode<br>SD/HD = LOW<br>20bit/10bit = HIGH                                                   | Luma data output in SMPTE mode  SMPTE_BYPASS = HIGH  DVB_ASI = LOW  Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW |  |

|                                              |             |                          |        | HD 10-bit mode<br>SD/HD = LOW<br>20bit/10bit = LOW                                                    | Multiplexed Luma and Chroma data output in SMPTE mode  SMPTE_BYPASS = HIGH  DVB_ASI = LOW                                               |  |

|                                              |             |                          |        |                                                                                                       | Data output in Data-Through mode<br>SMPTE_BYPASS = LOW<br>DVB_ASI = LOW                                                                 |  |

|                                              |             |                          |        | SD 20-bit mode<br>SD/HD = HIGH<br>20bit/10bit = HIGH                                                  | Luma data output in SMPTE mode SMPTE_BYPASS = HIGH DVB_ASI = LOW                                                                        |  |

|                                              |             |                          |        |                                                                                                       | Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW                                                                     |  |

|                                              |             |                          |        |                                                                                                       | DVB-ASI data in DVB-ASI mode  SMPTE_BYPASS = LOW  DVB_ASI = HIGH                                                                        |  |

|                                              |             |                          |        | SD 10-bit mode<br>SD/HD = HIGH<br>20bit/10bit = LOW                                                   | Multiplexed Luma and Chroma data<br>output in SMPTE mode<br>SMPTE_BYPASS = HIGH<br>DVB_ASI = LOW                                        |  |

|                                              |             |                          |        |                                                                                                       | Data input in data through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW                                                                      |  |

|                                              |             |                          |        |                                                                                                       | DVB-ASI data in DVB-ASI mode  SMPTE_BYPASS = LOW  DVB_ASI = HIGH                                                                        |  |

| B1                                           | CP_CAP      | Analog                   | Input  | PLL lock time constant capacitor connection. Normally connected to VCO_GND through 2.2nF.             |                                                                                                                                         |  |

| В2                                           | CP_VDD      | -                        | Power  | Power supply connection for the Charge Pump. Connect to +3.3V Do analog.                              |                                                                                                                                         |  |

| В3                                           | CP_GND      | _                        | Power  | Ground connection for                                                                                 | the Charge Pump. Connect to analog GND.                                                                                                 |  |

| В4                                           | LB_CONT     | Analog                   | Input  | _                                                                                                     | ne loop bandwidth of the integrated Reclocker. VCO_GND through $40 \mathrm{k}\Omega$                                                    |  |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name               | Timing             | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|--------------------|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В7            | FW_EN/DIS          | Non<br>Synchronous | Input            | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                                                                                                                                        |

|               |                    |                    |                  | Used to enable or disable the noise immune Flywheel of the device.                                                                                                                                                                                                                                                                                                                        |

|               |                    |                    |                  | When set HIGH, the internal Flywheel is enabled. This Flywheel is used in the extraction and generation of TRS timing signals, in automatic video standards detection, and in manual switch line lock handling.                                                                                                                                                                           |

|               |                    |                    |                  | When set LOW, the internal Flywheel is disabled and TRS correction and insertion is unavailable.                                                                                                                                                                                                                                                                                          |

| B8, F8, J8    | IO_GND             | _                  | Power            | Ground connection for digital I/O buffers. Connect to digital GND.                                                                                                                                                                                                                                                                                                                        |

| C1            | BUFF_VDD           | _                  | Power            | Power Supply connection for the Serial Digital Input buffers. Connect to +1.8V DC analog.                                                                                                                                                                                                                                                                                                 |

| C2            | PD_VDD             | PD_VDD – Power     |                  | Power Supply connection for the Phase Detector. Connect to +1.8V DC analog.                                                                                                                                                                                                                                                                                                               |

| C3            | PDBUFF_GND – Power |                    | Power            | Ground connection for the Phase Detector and Serial Digital Input buffers. Connect to analog GND.                                                                                                                                                                                                                                                                                         |

| C6            | MASTER/SLAVE       | Non<br>Synchronous | Input            | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                                                                                                                                           |

|               |                    |                    |                  | Used to determine the input / output selection for the DVB_ASI, SD/ $\overline{\text{HD}}$ , RC_BYP and $\overline{\text{SMPTE}}$ _BYPASS pins.                                                                                                                                                                                                                                           |

|               |                    |                    |                  | When set HIGH, the GS1559 is set to operate in Master mode where SD/HD, RC_BYP and SMPTE_BYPASS become status signal output pins set by the device. In this mode, the GS1559 will automatically detect, reclock, deserialize and process SD SMPTE and HD SMPTE input data.                                                                                                                |

|               |                    |                    |                  | When set LOW, the GS1559 is set to operate in Slave mode where DVB_ASI, SD/HD, RC_BYP and SMPTE_BYPASS become control signal input pins. In this mode, the application layer must set these external device pins for the correct reception of either SMPTE or DVB-ASI data. Slave mode also supports the reclocking and deserializing of data not conforming to SMPTE or DVB-ASI streams. |

| C7            | RC_BYP             | Non<br>Synchronous | Input<br>/Output | CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                                                                                                                    |

|               |                    |                    |                  | This pin will be an input set by the application layer in Slave mode, and will be an output set by the device in Master mode.                                                                                                                                                                                                                                                             |

|               |                    |                    |                  | Master mode (MASTER/SLAVE = HIGH) The RC_BYP signal will be HIGH only when the device has successfully locked to a SMPTE compliant input data stream. In this case, the serial digital loop-through output will be a reclocked version of the input.                                                                                                                                      |

|               |                    |                    |                  | The RC_BYP signal will be LOW whenever the input does not conform to a SMPTE compliant data stream. In this case, the serial digital loop-through output will be a buffered version of the input.                                                                                                                                                                                         |

|               |                    |                    |                  | Slave mode (MASTER/SLAVE = LOW) When set HIGH, the serial digital output will be a reclocked version of the input signal regardless of whether the device is in SMPTE, DVB-ASI or Data-Through mode.                                                                                                                                                                                      |

|               |                    |                    |                  | When set LOW, the serial digital output will be a buffered version of the input signal in all modes.                                                                                                                                                                                                                                                                                      |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name       | Timing                   | Туре              | Description                                                                                                                                                                                                                        |

|---------------|------------|--------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C8            | YANC       | Synchronous<br>with PCLK | Output            | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                    |

|               |            |                          |                   | Used to indicate the presence of ancillary data in the video stream.                                                                                                                                                               |

|               |            |                          |                   | HD Mode ( $SD/\overline{HD} = LOW$ ) The YANC signal will be HIGH when the device has detected VANC or HANC data in the luma video stream and LOW otherwise.                                                                       |

|               |            |                          |                   | SD Mode (SD/ $\overline{\text{HD}}$ = LOW)<br>For 20-bit demultiplexed data (20bit/ $\overline{\text{10bit}}$ = HIGH), the YANC signal will be HIGH when VANC or HANC data is detected in the Luma video stream and LOW otherwise. |

|               |            |                          |                   | For 10-bit multiplexed data (20bit/ $\overline{10bit}$ = LOW), the YANC signal will be HIGH when VANC or HANC data is detected anywhere in the data stream and LOW otherwise.                                                      |

| D1, E1        | DDI1, DDI1 | Analog                   | Input             | Differential input pair for serial digital input 1.                                                                                                                                                                                |

| D4            | IP_SEL     | Non<br>Synchronous       | Input             | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                    |

|               |            |                          |                   | Used to select DDI1 / DDI1 or DDI2 / DDI2 as the Serial Digital Input signal, and CD1 or CD2 as the Carrier Detect input signal.                                                                                                   |

|               |            |                          |                   | When set HIGH, DDI1 / DDI1 is selected as the Serial Digital Input and CD1 is selected as the Carrier Detect input signal.                                                                                                         |

|               |            |                          |                   | When set LOW, DDI2 / $\overline{\text{DDI2}}$ Serial Digital Input and $\overline{\text{CD2}}$ Carrier Detect input signal is selected.                                                                                            |

| D5            | DVB_ASI    | Non<br>Synchronous       | Input /<br>Output | CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                             |

|               |            |                          |                   | This pin will be an input set by the application layer in Slave mode.                                                                                                                                                              |

|               |            |                          |                   | This pin and its function are not supported in Master mode.                                                                                                                                                                        |

|               |            |                          |                   | Slave mode (MASTER/SLAVE = LOW) When set HIGH in conjunction with SD/HD = HIGH and SMPTE_BYPASS = LOW, the device will be configured to operate in DVB-ASI mode.                                                                   |

|               |            |                          |                   | When set LOW, the device will not support the decoding or word alignment of received DVB-ASI data.                                                                                                                                 |

| D6            | LOCKED     | Synchronous<br>with PCLK | Output            | STATUS SIGNAL OUTPUT Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                  |

|               |            |                          |                   | The LOCKED signal will be HIGH whenever the device has correctly received and locked to SMPTE compliant data in SMPTE mode or DVB-ASI compliant data in DVB-ASI mode.                                                              |

|               |            |                          |                   | It will be LOW otherwise.                                                                                                                                                                                                          |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name     | Timing                   | Туре              | Description                                                                                                                                                                                                            |

|---------------|----------|--------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D8            | CANC     | Synchronous<br>with PCLK | Output            | STATUS SIGNAL OUTPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                     |

|               |          |                          |                   | Used to indicate the presence of ancillary data in the video stream.                                                                                                                                                   |

|               |          |                          |                   | HD Mode (SD/HD = LOW) The CANC signal will be HIGH when the device has detected VANC or HANC data in the chroma video stream and LOW otherwise.                                                                        |

|               |          |                          |                   | SD Mode (SD/ $\overline{HD}$ = LOW)<br>For 20-bit demultiplexed data (20bit/ $\overline{10bit}$ = HIGH), the CANC signal will be HIGH when VANC or HANC data is detected in the Chroma video stream and LOW otherwise. |

|               |          |                          |                   | For 10-bit multiplexed data (20bit/10bit = LOW), the CANC signal will be HIGH when VANC or HANC data is detected anywhere in the data stream and LOW otherwise.                                                        |

| E2            | TERM1    | Analog                   | Input             | Termination for Serial Digital Input 1. AC couple to EQ_GND.                                                                                                                                                           |

| E4            | SD/HD    | Non<br>Synchronous       | Input /<br>Output | CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                 |

|               |          |                          |                   | This pin will be an input set by the application layer in Slave mode, and will be an output set by the device in Master mode.                                                                                          |

|               |          |                          |                   | Master mode (MASTER/SLAVE = HIGH) The SD/HD signal will be LOW whenever the received serial digital signal is 1.485Gb/s or 1.485/1.001Gb/s.                                                                            |

|               |          |                          |                   | The SD/HD signal will be HIGH whenever the received serial digital signal is 270Mb/s.                                                                                                                                  |

|               |          |                          |                   | Slave mode (MASTER/SLAVE = LOW) When set LOW, the device will be configured for the reception of 1.485Gb/s or 1.485/1.001Gb/s signals only and will not lock to any othe serial digital signal.                        |

|               |          |                          |                   | When set HIGH, the device will be configured for the reception of 270Mb/s signals only and will not lock to any other serial digital signa                                                                             |

|               |          |                          |                   | NOTE: When in Slave mode, reset the device after the SD/HD input habeen initially configured, and after each subsequent SD/HD data rate change.                                                                        |

|               |          |                          |                   | NOTE: This pin has an internal pull-up resistor of 100K.                                                                                                                                                               |

| E5, F5        | CORE_GND | -                        | Power             | Ground connection for the digital core logic. Connect to digital GND.                                                                                                                                                  |

| E6, F6        | CORE_VDD | -                        | Power             | Power Supply connection for the digital core logic. Connect to +1.8V DC digital.                                                                                                                                       |

| F1            | CD1      | Non<br>Synchronous       | Input             | STATUS SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                      |

|               |          |                          |                   | Used to indicate the presence of a serial digital input signal. Normally generated by a Gennum automatic cable Equalizer.                                                                                              |

|               |          |                          |                   | When LOW, the serial digital input signal received at the DDI1 and DDI1 pins is considered valid.                                                                                                                      |

|               |          |                          |                   | When HIGH, the associated serial digital input signal is considered to be invalid. In this case, the LOCKED signal is set LOW and all parallel outputs are muted.                                                      |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number                    | Name                    | Timing                   | Туре   | Description                                                            |                                                                                                                                           |

|----------------------------------|-------------------------|--------------------------|--------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| F4                               | 20bit/ <del>10bit</del> | Non<br>Synchronous       | Input  | modes. This signal is ign<br>When set HIGH, the para                   | S/LVTTL compatible.<br>It data bus width in SMPTE or Data-Through                                                                         |

| F10, F9,<br>G10, G9,<br>H10, H9, | DOUT[9:0]               | Synchronous<br>with PCLK | Output | PARALLEL DATA BUS<br>Signal levels are LVCMO<br>DOUT9 is the MSB and D |                                                                                                                                           |

| J10, J9,<br>K10, K9              |                         |                          |        | HD 20-bit mode<br>SD/HD = LOW<br>20bit/10bit = HIGH                    | Chroma data output in SMPTE mode  SMPTE_BYPASS = HIGH  DVB_ASI = LOW  Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW |

|                                  |                         |                          |        | HD 10-bit mode<br>SD/HD = LOW<br>20bit/10bit = LOW                     | Forced LOW in all modes.                                                                                                                  |

|                                  |                         |                          |        | SD 20-bit mode<br>SD/HD = HIGH<br>20bit/10bit = HIGH                   | Chroma data output in SMPTE mode SMPTE_BYPASS = HIGH DVB_ASI = LOW                                                                        |

|                                  |                         |                          |        |                                                                        | Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW                                                                       |

|                                  |                         |                          |        |                                                                        | Forced LOW in DVB-ASI mode  SMPTE_BYPASS = LOW  DVB_ASI = HIGH                                                                            |

|                                  |                         |                          |        | SD 10-bit mode<br>SD/HD = HIGH<br>20bit/10bit = LOW                    | Forced LOW in all modes.                                                                                                                  |

| G1, H1                           | DDI2, DDI2              | Analog                   | Input  | Differential input pair fo                                             | or serial digital input 2.                                                                                                                |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name          | Timing             | Туре              | Description                                                                                                                                                                                                      |

|---------------|---------------|--------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G4            | IOPROC_EN/DIS | Non<br>Synchronous | Input             | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                  |

|               |               |                    |                   | Used to enable or disable I/O processing features.                                                                                                                                                               |

|               |               |                    |                   | When set HIGH, the following I/O processing features of the device are enabled:                                                                                                                                  |

|               |               |                    |                   | • EDH CRC Error Correction (SD-only)                                                                                                                                                                             |

|               |               |                    |                   | ANC Data Checksum Correction                                                                                                                                                                                     |

|               |               |                    |                   | <ul> <li>Line-based CRC Error Correction (HD-only)</li> </ul>                                                                                                                                                    |

|               |               |                    |                   | <ul> <li>Line Number Error Correction (HD-only)</li> </ul>                                                                                                                                                       |

|               |               |                    |                   | TRS Error Correction                                                                                                                                                                                             |

|               |               |                    |                   | Illegal Code Remapping                                                                                                                                                                                           |

|               |               |                    |                   | To enable a subset of these features, keep IOPROC_EN/DIS HIGH and disable the individual feature(s) in the IOPROC_DISABLE register accessible via the Host Interface.                                            |

|               |               |                    |                   | When set LOW, the I/O processing features of the device are disabled, regardless of whether the features are enabled in the IOPROC_DISABLE register.                                                             |

| G5            | SMPTE_BYPASS  | Non<br>Synchronous | Input /<br>Output | CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                           |

|               |               | •                  |                   | This pin will be an input set by the application layer in Slave mode, and will be an output set by the device in Master mode.                                                                                    |

|               |               |                    |                   | Master mode (MASTER/SLAVE = HIGH) The SMPTE_BYPASS signal will be HIGH only when the device has locked to a SMPTE compliant data stream. It will be LOW otherwise.                                               |

|               |               |                    |                   | Slave mode (MASTER/SLAVE = LOW) When set HIGH in conjunction with DVB_ASI = LOW, the device will be configured to operate in SMPTE mode. All I/O processing features may be enabled in this mode.                |

|               |               |                    |                   | When set LOW, the device will not support the descrambling, decoding or word alignment of received SMPTE data. No I/O processing features will be available.                                                     |

| G6            | RESET_TRST    | Non<br>Synchronous | Input             | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                  |

|               |               |                    |                   | Used to reset the internal operating conditions to default settings and to reset the JTAG test sequence.                                                                                                         |

|               |               |                    |                   | Host mode (JTAG/HOST = LOW) When asserted LOW, all functional blocks will be set to default conditions and all input and output signals become high-impedance, including the Serial Digital Outputs SDO and SDO. |

|               |               |                    |                   | Must be set HIGH for normal device operation.                                                                                                                                                                    |

|               |               |                    |                   | NOTE: When in Slave mode, reset the device after the SD/HD input has been initially configured, and after each subsequent SD/HD data rate change.                                                                |

|               |               |                    |                   | JTAG test mode (JTAG/HOST = HIGH) When asserted LOW, all functional blocks will be set to default and the JTAG test sequence will be held in reset.                                                              |

|               |               |                    |                   | When set HIGH, normal operation of the JTAG test sequence resumes.                                                                                                                                               |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name       | Timing                   | Туре   | Description                                                                                                                                                                                                           |

|---------------|------------|--------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G8            | FIFO_LD    | Synchronous<br>with PCLK | Output | CONTROL SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                      |

|               |            |                          |        | Used as a control signal for external FIFO(s).                                                                                                                                                                        |

|               |            |                          |        | Normally HIGH but will go LOW for one PCLK period at SAV.                                                                                                                                                             |

| H2            | TERM2      | Analog                   | Input  | Termination for serial digital input 2. AC couple to EQ_GND.                                                                                                                                                          |

| H4            | CS_TMS     | Synchronous<br>with      | Input  | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                       |

|               |            | SCLK_TCK                 |        | Chip Select/Test Mode Select                                                                                                                                                                                          |

|               |            |                          |        | Host mode (JTAG/ $\overline{\text{HOST}}$ = LOW) $\overline{\text{CS}}_{\text{TMS}}$ operates as the Host Interface Chip Select, $\overline{\text{CS}}_{\text{N}}$ , and is active LOW.                               |

|               |            |                          |        | JTAG Test mode (JTAG/ $\overline{\text{HOST}}$ = HIGH) $\overline{\text{CS}}_{-}$ TMS operates as the JTAG Test Mode Select, TMS, and is active HIGH.                                                                 |

|               |            |                          |        | NOTE: If the Host Interface is not being used, tie this pin HIGH.                                                                                                                                                     |

| H5            | SCLK_TCK   | Non<br>Synchronous       | Input  | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                       |

|               |            |                          |        | Serial Data Clock/Test Clock.                                                                                                                                                                                         |

|               |            |                          |        | Host mode (JTAG/HOST = LOW)  SCLK_TCK operates as the Host Interface Burst Clock, SCLK. Command and data read/write words are clocked into the device synchronously with this clock.                                  |

|               |            |                          |        | JTAG Test Mode (JTAG/HOST = HIGH) SCLK_TCK operates as the JTAG test clock, TCK.                                                                                                                                      |

|               |            |                          |        | NOTE: If the Host Interface is not being used, tie this pin HIGH.                                                                                                                                                     |

| Н6            | SDOUT_TDO  | Synchronous<br>with      | Output | CONTROL SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                      |

|               |            | SCLK_TCK                 |        | Serial Data Output/Test Data Output Host mode (JTAG/HOST = LOW)                                                                                                                                                       |

|               |            |                          |        | SDOUT_TDO operates as the Host Interface Serial Digital Output, SDOUT, used to read status and configuration information from the internal registers of the device.                                                   |

|               |            |                          |        | JTAG Test Mode (JTAG/HOST = HIGH) SDOUT_TDO operates as the JTAG test data output, TDO.                                                                                                                               |

| H7            | DATA_ERROR | Synchronous<br>with PCLK | Output | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                       |

|               |            |                          |        | The DATA_ERROR signal will be LOW when an error within the received data stream has been detected by the device. This pin is a logical 'OR'ing of all detectable errors listed in the internal ERROR_STATUS register. |

|               |            |                          |        | Once an error is detected, DATA_ERROR will remain LOW until the start of the next video frame/field, or until the ERROR_STATUS regist is read via the Host Interface.                                                 |

|               |            |                          |        | The DATA_ERROR signal will be HIGH when the received data stream has been detected without error.                                                                                                                     |

|               |            |                          |        | NOTE: It is possible to program which error conditions are monitored by the device by setting appropriate bits of the ERROR_MASK register HIGH. All error conditions are detected by default.                         |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name       | Timing                   | Туре   | Description                                                                                                                                                                                           |

|---------------|------------|--------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н8            | Н          | Synchronous<br>with PCLK | Output | STATUS SIGNAL OUTPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                    |

|               |            |                          |        | Used to indicate the portion of the video line containing active video data. H signal timing is configurable via the H_CONFIG bit of the IOPROC_DISABLE register accessible via the Host Interface.   |

|               |            |                          |        | Active Line Blanking (H_CONFIG = $0_h$ )<br>The H signal will be HIGH for the entire Horizontal blanking period, including the EAV and SAV TRS words, and LOW otherwise. This is the default setting. |

|               |            |                          |        | TRS Based Blanking (H_CONFIG = $1_h$ )<br>The H signal will be HIGH for the entire Horizontal blanking period as indicated by the H bit in the received TRS ID words, and LOW otherwise.              |

| J1            | CD2        | Non<br>Synchronous       | Input  | STATUS SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                        |

|               |            | ,                        |        | Used to indicate the presence of a serial digital input signal. Normally generated by a Gennum automatic Cable Equalizer.                                                                             |

|               |            |                          |        | When LOW, the serial digital input signal received at the DDI2 and DDI2 pins is considered valid.                                                                                                     |

|               |            |                          |        | When HIGH, the associated serial digital input signal is considered to be invalid. In this case, the LOCKED signal is set LOW and all parallel outputs are muted.                                     |

| J5            | SDO_EN/DIS | Non<br>Synchronous       | Input  | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                       |

|               |            |                          |        | Used to enable or disable the serial digital output loop-through stage.                                                                                                                               |

|               |            |                          |        | When set LOW, the Serial Digital Output signals SDO and SDO are disabled and become high-impedance.                                                                                                   |

|               |            |                          |        | When set HIGH, the Serial Digital Output signals SDO and $\overline{\text{SDO}}$ are enabled.                                                                                                         |

| J6            | SDIN_TDI   | Synchronous<br>with      | Input  | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                       |

|               |            | SCLK_TCK                 |        | Serial Data In/Test Data Input                                                                                                                                                                        |

|               |            |                          |        | Host mode (JTAG/HOST = LOW)  SDIN_TDI operates as the Host Interface Serial Digital Input, SDIN, used to write address and configuration information to the internal registers of the device.         |

|               |            |                          |        | JTAG Test Mode (JTAG/ <del>HOST</del> = HIGH) SDIN_TDI operates as the JTAG test data input, TDI.                                                                                                     |

|               |            |                          |        | NOTE: If the Host Interface is not being used, tie this pin HIGH.                                                                                                                                     |

| J7            | V          | Synchronous<br>with PCLK | Output | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                       |

|               |            |                          |        | Used to indicate the portion of the video field/frame that is used for Vertical blanking.                                                                                                             |

|               |            |                          |        | The V signal will be HIGH for the entire Vertical blanking period as indicated by the V bit in the received TRS signals.                                                                              |

|               |            |                          |        | The V signal will be LOW for all lines outside of the Vertical blanking interval.                                                                                                                     |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name                  | Timing                   | Туре   | Description                                                                                                                                                                                                                                                                                                                                        |

|---------------|-----------------------|--------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K1            | RSET                  | Analog                   | Input  | Used to set the serial digital loop-through output signal amplitude. Connect to CD_VDD through 281 $\Omega$ +/- 1% for 800mV <sub>p-p</sub> single-ended output swing.                                                                                                                                                                             |

| K2            | CD_VDD                | -                        | Power  | Power Supply connection for the serial digital Cable Driver. Connect to +1.8V DC analog.                                                                                                                                                                                                                                                           |

| K3, K4        | SDO, SDO              | Analog                   | Output | Serial digital loop-through output signal operating at 1.485Gb/s, 1.485/1.001Gb/s, or 270Mb/s.                                                                                                                                                                                                                                                     |

|               |                       |                          |        | The slew rate of these outputs is automatically controlled to meet SMPTE 292M and 259M requirements according to the setting of the SD/ $\overline{\text{HD}}$ pin.                                                                                                                                                                                |

| K5            | CD_GND                | -                        | Power  | Ground connection for the serial digital Cable Driver. Connect to analog GND.                                                                                                                                                                                                                                                                      |

| К6            | JTAG/ <del>HOST</del> | Non<br>Synchronous       | Input  | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible. Used to select JTAG Test mode or Host Interface mode. When set HIGH, CS_TMS, SDOUT_TDO, SDI_TDI and SCLK_TCK are configured for JTAG boundary scan testing. When set LOW, CS_TMS, SDOUT_TDO, SDI_TDI and SCLK_TCK are configured as GSPI pins for normal Host Interface operation. |

| K7            | F                     | Synchronous<br>with PCLK | Output | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible. Used to indicate the ODD/EVEN field of the video signal. The F signal will be HIGH for the entire period of field 2 as indicated by the F bit in the received TRS signals. The F signal will be LOW for all lines in field 1 and for all lines in progressive scan systems.        |

# 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

| Parameter                               | Value/Units                      |

|-----------------------------------------|----------------------------------|

| Supply Voltage Core                     | -0.3V to +2.1V                   |

| Supply Voltage I/O                      | -0.3V to +4.6V                   |

| Input Voltage Range (any input)         | -2.0V to + 5.25V                 |

| Ambient Operating Temperature           | -20°C ≤ T <sub>A</sub> ≤ 85°C    |

| Storage Temperature                     | -40°C ≤ T <sub>STG</sub> ≤ 125°C |

| ESD Protection On All Pins (see Note 1) | 1kV                              |

NOTES:

## 2.2 DC Electrical Characteristics

**Table 2-1: DC Electrical Characteristics**

$T_A = 0$ °C to 70°C, unless otherwise specified.

| Parameter                             | Symbol           | Conditions  | Min  | Тур | Max  | Units | Test<br>Level | Notes |

|---------------------------------------|------------------|-------------|------|-----|------|-------|---------------|-------|

| System                                |                  |             |      |     |      |       |               |       |

| Operation Temperature<br>Range        | T <sub>A</sub>   | -           | 0    | -   | 70   | °C    | 3             | 1     |

| Digital Core Supply Voltage           | CORE_VDD         | -           | 1.71 | 1.8 | 1.89 | V     | 3             | 1     |

| Digital I/O Supply Voltage            | IO_VDD           | -           | 3.13 | 3.3 | 3.47 | V     | 3             | 1     |

| Charge Pump Supply Voltage            | CP_VDD           | -           | 3.13 | 3.3 | 3.47 | V     | 3             | 1     |

| Phase Detector Supply<br>Voltage      | PD_VDD           | -           | 1.71 | 1.8 | 1.89 | V     | 3             | 1     |

| Input Buffer Supply Voltage           | BUFF_VDD         | -           | 1.71 | 1.8 | 1.89 | V     | 3             | 1     |

| Cable Driver Supply Voltage           | CD_VDD           | -           | 1.71 | 1.8 | 1.89 | V     | 3             | 1     |

| External VCO Supply Voltage<br>Output | VCO_VCC          | _           | 2.25 | _   | 2.75 | V     | 1             | -     |

| +1.8V Supply Current                  | I <sub>1V8</sub> | SDO Enabled | -    | -   | 245  | mA    | 3             | 4     |

| +3.3V Supply Current                  | I <sub>3V3</sub> | -           | -    | -   | 55   | mA    | 3             | 5     |

<sup>1.</sup> HBM, per JESDA-114B.

### Table 2-1: DC Electrical Characteristics (Continued)

$T_A = 0$ °C to 70°C, unless otherwise specified.

| Parameter                     | Symbol             | Conditions                                     | Min             | Тур  | Max  | Units | Test<br>Level | Notes      |

|-------------------------------|--------------------|------------------------------------------------|-----------------|------|------|-------|---------------|------------|

| Total Device Power            | P <sub>D</sub>     | SDO Enabled                                    | _               | _    | 550  | mW    | 3             | _          |