Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**GS1662**

#### **HD/SD-SDI Serializer with Complete SMPTE Video Support**

#### **Key Features**

- Operation at 1.485Gb/s, 1.485/1.001Gb/s and 270Mb/s

- Supports SMPTE ST 292, SMPTE ST 259-C and DVB-ASI

- Integrated Cable Driver

- Integrated, low-noise VCO

- Integrated ClockCleaner<sup>TM</sup>

- Ancillary data insertion

- Parallel data bus selectable as either 20-bit or 10-bit

- SMPTE video processing including TRS calculation and insertion, line number calculation and insertion, line based CRC calculation and insertion, illegal code re-mapping, SMPTE ST 352 payload identifier generation and insertion

- GSPI host interface

- +1.2V digital core power supply, +1.2V and +3.3V analog power supplies, and selectable +1.8V or +3.3V I/O power supply

- -20°C to +85°C operating temperature range

- Low power operation (typically at 330mW, including Cable Driver)

- Small 11mm x 11mm 100-ball BGA package

- Pb-free and RoHS compliant

#### **Applications**

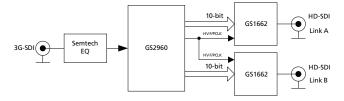

Application: Single Link (3G-SDI) to Dual Link (HD-SDI) Converter

#### **Description**

The GS1662 is a complete SDI Transmitter, generating a SMPTE ST 292, SMPTE ST 259-C or DVB-ASI compliant serial digital output signal.

The integrated ClockCleaner™ allows the device to accept parallel clocks with greater than 300ps input jitter and still provide a SMPTE compliant serial digital output.

The device can operate in four basic user selectable modes: SMPTE mode, DVB-ASI mode, Data-Through mode, or Standby mode.

In SMPTE mode, the GS1662 performs SMPTE scrambling and NRZ to NRZI coding. In addition, the device can insert TRS words, calculate and insert line numbers and line based CRC's, re-map illegal code words, map 8-bit TRS to 10-bit TRS, calculate and insert EDH CRC's and flags, and insert SMPTE ST 352 payload identifier packets. All of the processing features are optional, and may be disabled via external control pins and/or via the Host Interface.

The GS1662 provides ancillary data insertion in SMPTE mode as well. The entire ancillary packet is programmed into internal registers through the GSPI Host Interface, including the Ancillary Data Flag (ADF), Data Identification words (DID and SDID) and checksum. The GS1662 then recalculates the checksum and inserts the complete ancillary packet into the video stream.

In DVB-ASI mode, the device will perform 8b/10b encoding prior to transmission.

In Data-Through mode, all SMPTE and DVB-ASI processing is disabled, and the device can be used as a simple parallel to serial converter.

The device can also operate in a lower power Standby mode. In this mode, no signal is generated at the output.

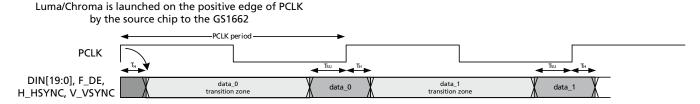

Parallel data inputs must be provided in 20-bit or 10-bit multiplexed format for HD and SD video rates. The associated Parallel Clock input signal operates at 148.5 or 148.5/1.001MHz (HD 10-bit multiplexed format), 74.25 or 74.25/1.001MHz (for HD 20-bit format), 27MHz (for SD 10-bit format) and 13.5MHz (for SD 20-bit format).

The GS1662 includes an integrated Cable Driver fully compliant with SMPTE ST 259-C and SMPTE ST 292. It features automatic dual slew-rate selection, depending on HD or SD operational requirements.

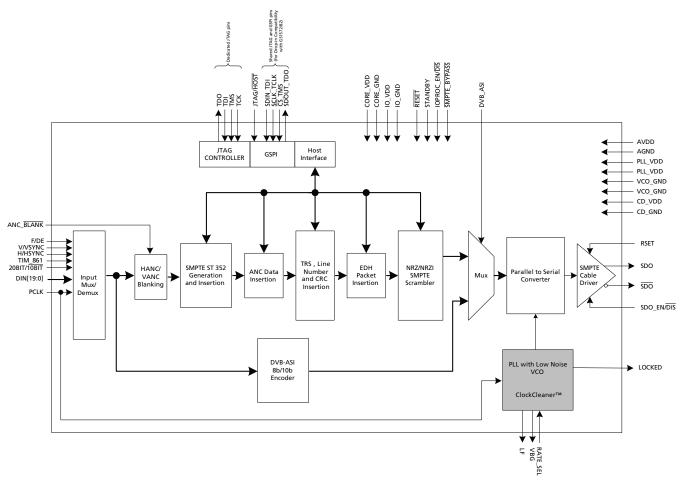

### **Functional Block Diagram**

Figure A: GS1662 Functional Block Diagram

## **Revision History**

| Version | ECO    | PCN   | Date           | Changes and/or Modifications                                                                                                                                                                                                                      |

|---------|--------|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | 014806 | -     | September 2013 | Updates throughout the document.                                                                                                                                                                                                                  |

| 3       | 155080 | 56060 | October 2010   | Revised power rating in standby mode. Documented CSUM behaviour in Section 4.7, Section 4.8.3 and Configuration and Status Registers.                                                                                                             |

| 2       | 153743 | -     | March 2010     | Correction to ANC Data Insertion addresses 040h - 13Fh in Table 4-16: Configuration and Status Registers. Changed Reset Pulse width from 10ms to 1ms in Table 2-4: AC Electrical Characteristics and 4.16 Device Reset. Changed Pin E4 to IO_GND. |

| 1       | 153472 | -     | January 2010   | Converted to Data Sheet.                                                                                                                                                                                                                          |

| 0       | 153210 | -     | November 2009  | Converted to Preliminary Data Sheet. Changed pin E4 to RSV in Pin Assignment, Pin Descriptions and Typical Application Circuit.                                                                                                                   |

| A       | 152910 | _     | October 2009   | New Document.                                                                                                                                                                                                                                     |

### **Contents**

| Key Features                                           | 1  |

|--------------------------------------------------------|----|

| Applications                                           | 1  |

| Description                                            | 1  |

| Functional Block Diagram                               | 2  |

| Revision History                                       | 3  |

| 1. Pin Out                                             | 7  |

| 1.1 Pin Assignment                                     | 7  |

| 1.2 Pin Descriptions                                   | 8  |

| 2. Electrical Characteristics                          | 16 |

| 2.1 Absolute Maximum Ratings                           | 16 |

| 2.2 Recommended Operating Conditions                   | 16 |

| 2.3 DC Electrical Characteristics                      | 17 |

| 2.4 AC Electrical Characteristics                      | 18 |

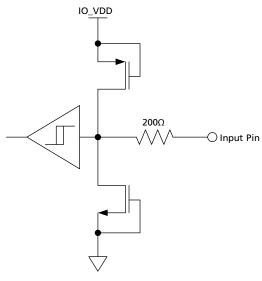

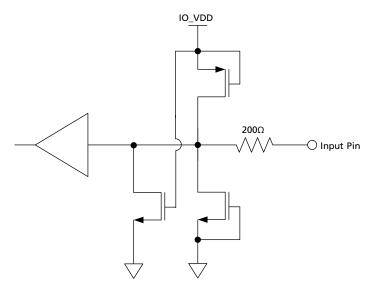

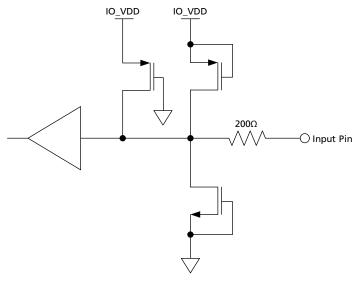

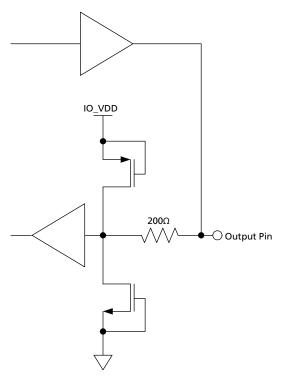

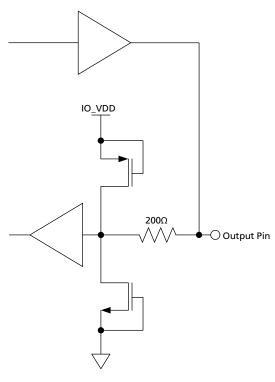

| 3. Input/Output Circuits                               | 20 |

| 4. Detailed Description                                | 25 |

| 4.1 Functional Overview                                | 25 |

| 4.2 Parallel Data Inputs                               | 25 |

| 4.2.1 Parallel Input in SMPTE Mode                     | 27 |

| 4.2.2 Parallel Input in DVB-ASI Mode                   | 27 |

| 4.2.3 Parallel Input in Data-Through Mode              | 27 |

| 4.2.4 Parallel Input Clock (PCLK)                      | 28 |

| 4.3 SMPTE Mode                                         | 29 |

| 4.3.1 H:V:F Timing                                     | 29 |

| 4.3.2 CEA 861 Timing                                   | 30 |

| 4.4 DVB-ASI Mode                                       | 36 |

| 4.5 Data-Through Mode                                  | 36 |

| 4.6 Standby Mode                                       | 37 |

| 4.7 ANC Data Insertion                                 | 37 |

| 4.7.1 ANC Insertion Operating Modes                    | 38 |

| 4.7.2 HD ANC Insertion                                 | 39 |

| 4.7.3 SD ANC Insertion                                 | 40 |

| 4.8 Additional Processing Functions                    | 41 |

| 4.8.1 Video Format Detection                           | 41 |

| 4.8.2 ANC Data Blanking                                | 43 |

| 4.8.3 ANC Data Checksum Calculation and Insertion      | 44 |

| 4.8.4 TRS Generation and Insertion                     | 44 |

| 4.8.5 HD Line Number Calculation and Insertion         | 44 |

| 4.8.6 Illegal Code Re-Mapping                          | 45 |

| 4.8.7 SMPTE ST 352 Payload Identifier Packet Insertion | 45 |

| 4.8.8 Line Based CRC Generation and Insertion (HD)     | 45 |

| 4.8.9 EDH Generation and Insertion                     | 46 |

| 4.8.10 Processing Feature Disable                      | 47 |

| 4.9 Serial Digital Output                              | 47 |

| 4.9.1 Output Signal Interface Levels                   | 48 |

|       | 4.9.2 Overshoot/Undershoot        | 49 |

|-------|-----------------------------------|----|

|       | 4.9.3 Slew Rate Selection         | 49 |

|       | 4.9.4 Serial Digital Output Mute  | 49 |

|       | 4.10 Serial Clock PLL             | 50 |

|       | 4.10.1 PLL Bandwidth              | 50 |

|       | 4.10.2 Lock Detect                | 51 |

|       | 4.11 GSPI Host Interface          | 52 |

|       | 4.11.1 Command Word Description   | 53 |

|       | 4.11.2 Data Read or Write Access  | 53 |

|       | 4.11.3 GSPI Timing                | 54 |

|       | 4.12 Host Interface Register Maps | 56 |

|       | 4.13 JTAG ID Codeword             | 65 |

|       | 4.14 JTAG Test Operation          | 65 |

|       | 4.15 Device Power-Up              | 65 |

|       | 4.16 Device Reset                 | 65 |

| 5. A  | pplication Reference Design       | 66 |

|       | 5.1 Typical Application Circuit   | 66 |

| 6. R  | eferences & Relevant Standards    | 67 |

| 7. Pá | nckage & Ordering Information     | 68 |

|       | 7.1 Package Dimensions            | 68 |

|       | 7.2 Packaging Data                | 69 |

|       | 7.3 Marking Diagram               | 69 |

|       | 7.4 Solder Reflow Profiles        | 70 |

|       | 7.5 Ordering Information          | 70 |

|       | Table 7-2: Ordering Information   | 70 |

## **List of Figures**

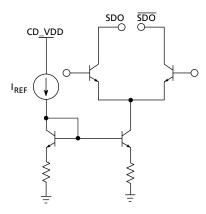

| Figure 3-1: Differential Output Stage (SDO/SDO)                                        |

|----------------------------------------------------------------------------------------|

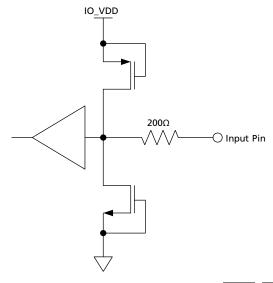

| Figure 3-2: Digital Input Pin                                                          |

| Figure 3-3: Digital Input Pin with Schmitt Trigger (RESET)                             |

| Figure 3-4: Digital Input Pin with weak pull-down - maximum pull-down current          |

| Figure 3-5: Digital Input Pin with weak pull-up - maximum pull-up current              |

| Figure 3-6: Bidirectional Digital Input/Output Pin with programmable drive strength 22 |

| Figure 3-7: Bidirectional Digital Input/Output Pin with programmable drive strength 23 |

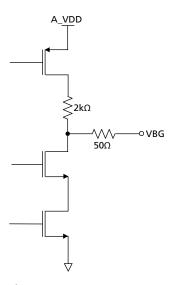

| Figure 3-8: VBG                                                                        |

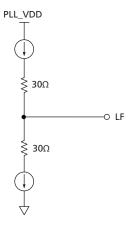

| Figure 3-9: Loop Filter                                                                |

| Figure 4-1: GS1662 Video Host Interface Timing Diagrams                                |

| Figure 4-2: H:V:F Input Timing - HD 20-bit Input Mode                                  |

| Figure 4-3: H:V:F Input Timing - HD 10-bit Input Mode                                  |

| Figure 4-4: H:V:F Input Timing - SD 20-bit Mode                                        |

| Figure 4-5: H:V:F Input Timing - SD 10-bit Mode                                        |

| Figure 4-6: H:V:DE Input Timing 1280 x 720p @ 59.94/60 (Format 4)                      |

| Figure 4-7: H:V:DE Input Timing 1920 x 1080i @ 59.94/60 (Format 5)                     |

| Figure 4-8: H:V:DE Input Timing 720 (1440) x 480i @ 59.94/60 (Format 6&7)              |

| Figure 4-9: H:V:DE Input Timing 1280 x 720p @ 50 (Format 19)                           |

| Figure 4-10: H:V:DE Input Timing 1920 x 1080i @ 50 (Format 20)                         |

| Figure 4-11: H:V:DE Input Timing 720 (1440) x 576 @ 50 (Format 21 & 22)                |

| Figure 4-12: H:V:DE Input Timing 1920 x 1080p @ 23.94/24 (Format 32) | 35 |

|----------------------------------------------------------------------|----|

| Figure 4-13: H:V:DE Input Timing 1920 x 1080p @ 25 (Format 33)       | 35 |

| Figure 4-14: H:V:DE Input Timing 1920 x 1080p @ 29.97/30 (Format 34) | 36 |

| Figure 4-15: ORL Matching Network, BNC and Coaxial Cable Connection  | 48 |

| Figure 4-16: GSPI Application Interface Connection                   | 52 |

| Figure 4-17: Command Word Format                                     | 53 |

| Figure 4-18: Data Word Format                                        | 53 |

| Figure 4-19: Write Mode                                              | 54 |

| Figure 4-20: Read Mode                                               | 54 |

| Figure 4-21: GSPI Time Delay                                         | 54 |

| Figure 4-22: Reset Pulse                                             |    |

| Figure 5-1: Typical Application Circuit                              | 66 |

| Figure 7-1: Package Dimensions                                       | 68 |

| Figure 7-2: Marking Diagram                                          | 69 |

| Figure 7-3: Pb-free Solder Reflow Profile                            | 70 |

|                                                                      |    |

### **List of Tables**

| Table 1-1: Pin Descriptions                                   | 8  |

|---------------------------------------------------------------|----|

| Table 2-1: Absolute Maximum Ratings                           | 16 |

| Table 2-2: Recommended Operating Conditions                   | 16 |

| Table 2-3: DC Electrical Characteristics                      | 17 |

| Table 2-4: AC Electrical Characteristics                      | 18 |

| Table 4-1: GS1662 Digital Input AC Electrical Characteristics | 26 |

| Table 4-2: GS1662 Input Video Data Format Selections          | 26 |

| Table 4-3: GS1662 PCLK Input Rates                            | 28 |

| Table 4-4: CEA861 Timing Formats                              |    |

| Table 4-5: Supported Video Standards                          | 42 |

| Table 4-6: IOPROC Register Bits                               | 47 |

| Table 4-7: Serial Digital Output - Serial Output Data Rate    | 47 |

| Table 4-8: R <sub>SET</sub> Resistor Value vs. Output Swing   | 48 |

| Table 4-9: Serial Digital Output - Overshoot/Undershoot       |    |

| Table 4-10: Serial Digital Output - Rise/Fall Time            | 49 |

| Table 4-11: PCLK and Serial Digital Clock Rates               | 50 |

| Table 4-12: GS1662 PLL Bandwidth                              | 50 |

| Table 4-13: GS1662 Lock Detect Indication                     |    |

| Table 4-14: GSPI Time Delay                                   | 54 |

| Table 4-15: GSPI AC Characteristics                           | 55 |

| Table 4-16: Configuration and Status Registers                |    |

| Table 7-1: Packaging Data                                     | 69 |

## 1. Pin Out

## 1.1 Pin Assignment

|   | 1            | 2            | 3              | 4               | 5            | 6                | 7                 | 8             | 9             | 10           |

|---|--------------|--------------|----------------|-----------------|--------------|------------------|-------------------|---------------|---------------|--------------|

| Α | DIN17        | DIN18        | F/DE           | H/HSYNC         | CORE<br>_VDD | PLL_<br>VDD      | LF                | VBG           | RSV           | A_VDD        |

| В | DIN15        | DIN16        | DIN19          | PCLK            | CORE<br>_GND | PLL_<br>VDD      | VCO_<br>VDD       | VCO_<br>GND   | A_GND         | A_GND        |

| С | DIN13        | DIN14        | DIN12          | V/VSYNC         | CORE<br>_GND | PLL_<br>GND      | PLL_<br>GND       | PLL_<br>GND   | CD_GND        | SDO          |

| D | DIN11        | DIN10        | STANDBY        | SDO_<br>EN/DIS  | CORE<br>_GND | RSV              | RSV               | RSV           | CD_GND        | SDO          |

| Ε | CORE<br>_VDD | CORE<br>_GND | RATE_<br>SEL   | IO_GND          | CORE<br>_GND | CORE<br>_GND     | TDI               | TMS           | CD_GND        | CD_VDD       |

| F | DIN9         | DIN8         | DETECT<br>_TRS | CORE<br>_GND    | CORE<br>_GND | CORE<br>_GND     | CORE<br>_GND      | TDO           | CD_GND        | RSET         |

| G | IO_VDD       | IO_GND       | TIM_861        | 20bit/<br>10bit | DVB_ASI      | SMPTE_<br>BYPASS | IOPROC<br>_EN/DIS | RESET         | CORE<br>_GND  | CORE<br>_VDD |

| Н | DIN7         | DIN6         | ANC_<br>BLANK  | LOCKED          | CORE<br>_GND | CORE<br>_GND     | RSV               | JTAG/<br>HOST | IO_GND        | IO_VDD       |

| J | DIN5         | DIN4         | DIN1           | RSV             | RSV          | RSV              | RSV               | TCK           | SDOUT_<br>TDO | SCLK_<br>TCK |

| K | DIN3         | DIN2         | DIN0           | RSV             | RSV          | RSV              | RSV               | CORE<br>_VDD  | CS_<br>TMS    | SDIN_<br>TDI |

## **1.2 Pin Descriptions**

**Table 1-1: Pin Descriptions**

| Pin<br>Number                                   | Name       | Timing                           | Туре  | Description                                                                                                                                                                                                                                        |                                                                                                          |

|-------------------------------------------------|------------|----------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                                 | DIN[19:10] |                                  | Input |                                                                                                                                                                                                                                                    | t Logic parameters in the DC Electrical logic level threshold and compatibility.                         |

| B3, A2, A1,<br>B2, B1, C2,<br>C1, C3, D1,<br>D2 |            |                                  |       | 20-bit mode<br>20BIT/10BIT = HIGH                                                                                                                                                                                                                  | Luma data input in SMPTE mode (SMPTE_BYPASS = HIGH) Data input in data through mode (SMPTE_BYPASS = LOW) |

|                                                 |            |                                  |       | 10-bit <u>mode</u><br>20BIT/ <del>10BIT</del> = LOW                                                                                                                                                                                                | Multiplexed Luma and Chroma data input in SMPTE mode (SMPTE_BYPASS = HIGH)                               |

|                                                 |            |                                  |       |                                                                                                                                                                                                                                                    | Data input in data through mode (SMPTE_BYPASS = LOW)                                                     |

|                                                 |            |                                  |       |                                                                                                                                                                                                                                                    | DVB-ASI data input in DVB-ASI mode<br>(SMPTE_BYPASS = LOW)<br>(DVB_ASI = HIGH)                           |

|                                                 |            |                                  |       | PARALLEL DATA TIMING                                                                                                                                                                                                                               | i.                                                                                                       |

|                                                 |            |                                  | Input | •                                                                                                                                                                                                                                                  | t Logic parameters in the DC Electrical logic level threshold and compatibility.                         |

| A3                                              | F/DE       | Synch-<br>ronous<br>with<br>PCLK |       | DETECT_TRS is set LOW. TRS signals for the entire (IOPROC_EN/DIS must all The F signal should be set should be set LOW for all progressive scan systems The F signal is ignored we TIM_861 = HIGH: The DE signal is used to DETECT_TRS is set LOW. | et HIGH for the entire period of field 2 and<br>Ill lines in field 1 and for all lines in                |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number                                                  | Name     | Timing                           | Туре             | Description                                                               |                                                                                                                                                                                                                                    |

|----------------------------------------------------------------|----------|----------------------------------|------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                |          |                                  |                  | PARALLEL DATA TIMIN                                                       | NG.                                                                                                                                                                                                                                |

|                                                                |          |                                  |                  |                                                                           | out Logic parameters in the DC Electrical or logic level threshold and compatibility.                                                                                                                                              |

| Α4                                                             | H/HSYNC  |                                  | Input            |                                                                           | o indicate the portion of the video line to data, when DETECT_TRS is set LOW.                                                                                                                                                      |

|                                                                |          | Synch-<br>ronous<br>with<br>PCLK |                  | The signal goes LOW a<br>goes HIGH after the la<br>The H signal should be | e LOW for the active portion of the video line.<br>at the first active pixel of the line, and then<br>ast active pixel of the line.<br>e set HIGH for the entire horizontal blanking<br>n EAV and SAV TRS words, and LOW otherwise |

|                                                                |          | I CLK                            |                  |                                                                           | H_CONFIG = 1 <sub>h</sub> )<br>e set HIGH for the entire horizontal blanking<br>the H bit in the received TRS ID words, and                                                                                                        |

|                                                                |          |                                  |                  | TIM_861 = HIGH:                                                           | icates horizontal timing. See Section 4.3.                                                                                                                                                                                         |

|                                                                |          |                                  |                  | When DETECT_TRS is I                                                      | HIGH, this pin is ignored at all times.<br>IGH and TIM_861 is set HIGH, the DETECT_TRS                                                                                                                                             |

| A5, E1, G10,<br>K8                                             | CORE_VDD |                                  | Input Power      | Power supply connect digital.                                             | ion for digital core logic. Connect to +1.2V DC                                                                                                                                                                                    |

| A6, B6                                                         | PLL_VDD  |                                  | Input Power      | Power supply pin for F                                                    | PLL. Connect to +1.2V DC analog.                                                                                                                                                                                                   |

| A7                                                             | LF       |                                  | Analog<br>Output | Loop Filter componen                                                      | t connection.                                                                                                                                                                                                                      |

| A8                                                             | VBG      |                                  | Output           | Bandgap voltage filte                                                     | r connection.                                                                                                                                                                                                                      |

| A9, D6, D7,<br>D8, H7, J4,<br>J5, J6, J7,<br>K4, K5, K6,<br>K7 | RSV      |                                  | -                | These pins are reserve                                                    | d and should be left unconnected.                                                                                                                                                                                                  |

| A10                                                            | A_VDD    |                                  | Input Power      | VDD for sensitive anal                                                    | log circuitry. Connect to +3.3VDC analog.                                                                                                                                                                                          |

|                                                                |          |                                  |                  | PARALLEL DATA BUS O                                                       | CLOCK.                                                                                                                                                                                                                             |

|                                                                |          |                                  |                  |                                                                           | out Logic parameters in the DC Electrical or logic level threshold and compatibility.                                                                                                                                              |

|                                                                |          |                                  |                  | HD 20-bit mode                                                            | PCLK @ 74.25MHz                                                                                                                                                                                                                    |

| B4                                                             | PCLK     |                                  | Input            | HD 10-bit mode                                                            | PCLK @ 148.5MHz                                                                                                                                                                                                                    |

|                                                                |          |                                  |                  | SD 20-bit mode                                                            | PCLK @ 13.5MHz                                                                                                                                                                                                                     |

|                                                                |          |                                  |                  | SD 10-bit mode                                                            | PCLK @ 27MHz                                                                                                                                                                                                                       |

|                                                                |          |                                  |                  | DVB-ASI mode                                                              | PCLK @ 27MHz                                                                                                                                                                                                                       |

| B5, C5, D5,<br>E2, E5, E6,<br>F4, F5, F6,<br>F7, G9, H5,<br>H6 | CORE_GND |                                  | Input Power      | Reserved. Connect to                                                      | CORE_GND.                                                                                                                                                                                                                          |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number     | Name                   | Timing                 | Туре        | Description                                                                                                                                                                                                                                                         |

|-------------------|------------------------|------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В7                | VCO_VDD                |                        | Input Power | Power pin for VCO. Connect to +1.2V DC analog followed by an RC filter (see Typical Application Circuit on page 66). VCO_VDD is nominally 0.7V.                                                                                                                     |

| В8                | VCO_GND                |                        | Input Power | Ground connection for VCO. Connect to analog GND.                                                                                                                                                                                                                   |

| B9, B10           | A_GND                  |                        | Input Power | GND pins for sensitive analog circuitry. Connect to analog GND.                                                                                                                                                                                                     |

|                   |                        |                        |             | PARALLEL DATA TIMING.                                                                                                                                                                                                                                               |

|                   |                        |                        |             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                  |

|                   |                        |                        |             | TIM_861 = LOW:                                                                                                                                                                                                                                                      |

|                   |                        | Synch-                 |             | The V signal is used to indicate the portion of the video field/frame that is used for vertical blanking, when DETECT_TRS is set LOW.                                                                                                                               |

| C4                | V/VSYNC                | ronous<br>with<br>PCLK |             | The V signal should be set HIGH for the entire vertical blanking period and should be set LOW for all lines outside of the vertical blanking interval.                                                                                                              |

|                   |                        |                        |             | The V signal is ignored when DETECT_TRS = HIGH.                                                                                                                                                                                                                     |

|                   |                        |                        |             | TIM_861 = HIGH:                                                                                                                                                                                                                                                     |

|                   |                        |                        |             | The VSYNC signal indicates vertical timing. See Section 4.3 for timing details.                                                                                                                                                                                     |

|                   |                        |                        |             | The VSYNC signal is ignored when DETECT_TRS = HIGH.                                                                                                                                                                                                                 |

| C6, C7, C8        | PLL_GND                |                        | Input Power | Ground connection for PLL. Connect to analog GND.                                                                                                                                                                                                                   |

| C9, D9, E9,<br>F9 | CD_GND                 |                        | Input Power | Ground connection for the serial digital cable driver. Connect to analog GND.                                                                                                                                                                                       |

| C10, D10          | SDO, <del>SDO</del>    |                        | Output      | Serial Data Output Signal.  Serial digital output signal operating at 1.485Gb/s, 1.485 /1.001Gb/s or 270Mb/s.  The slew rate of the output is automatically controlled to meet SMPTE ST 292 and ST 259 specifications according to the setting of the RATE_SEL pin. |

| D3                | STANDBY                |                        | loout       | Standby input.                                                                                                                                                                                                                                                      |

| נט                | STAINUDT               |                        | Input       | HIGH to place the device in Standby mode.                                                                                                                                                                                                                           |

|                   |                        |                        |             | CONTROL SIGNAL INPUT.                                                                                                                                                                                                                                               |

|                   |                        |                        |             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                  |

| D4                | SDO_EN/ <del>DIS</del> |                        | Input       | Used to enable or disable the serial digital output stage.                                                                                                                                                                                                          |

|                   | 2DO_EN/DI2             |                        |             | When SDO_EN/DIS is LOW, the serial digital output signals SDO and SDO are disabled and become high impedance.                                                                                                                                                       |

|                   |                        |                        |             | When SDO_EN/DIS is HIGH, the serial digital output signals SDO and SDO are enabled.                                                                                                                                                                                 |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number              | Name     | Timing Type | Description                                                                                                                        |                                                                                  |

|----------------------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                            |          |             |                                                                                                                                    | t Logic parameters in the DC Electrical logic level threshold and compatibility. |

| E3                         | RATE_SEL | Input       | RATE_SEL                                                                                                                           | Data Rate                                                                        |

| 23                         | NATE_SEE | IIIput      | 0                                                                                                                                  | 1.485 or 1.485/1.001Gb/s                                                         |

|                            |          |             | 1                                                                                                                                  | 270Mb/s                                                                          |

|                            |          |             | COMMUNICATION SIGN                                                                                                                 | AL INPUT.                                                                        |

|                            | TDI      |             |                                                                                                                                    | t Logic parameters in the DC Electrical logic level threshold and compatibility. |

| E7                         |          | Input       | Dedicated JTAG pin.                                                                                                                |                                                                                  |

|                            |          |             | Test data in.                                                                                                                      |                                                                                  |

|                            |          |             | This pin is used to shift .<br>JTAG/HOST pin is LOW.                                                                               | JTAG test data into the device when the                                          |

|                            |          |             | COMMUNICATION SIGN                                                                                                                 | AL INPUT.                                                                        |

|                            |          |             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility. |                                                                                  |

| E8                         | TMS      | Input       | Dedicated JTAG pin.                                                                                                                |                                                                                  |

|                            |          |             | Test mode start.                                                                                                                   |                                                                                  |

|                            |          |             | This pin is JTAG Test Mo<br>the JTAG test when the                                                                                 | de Start, used to control the operation of JTAG/HOST pin is LOW.                 |

| E10                        | CD_VDD   | Input Power | Power for the serial digi                                                                                                          | tal cable driver. Connect to +3.3V DC analog.                                    |

|                            |          |             | PARALLEL DATA BUS.                                                                                                                 |                                                                                  |

|                            |          |             |                                                                                                                                    | t Logic parameters in the DC Electrical logic level threshold and compatibility. |

|                            |          |             | In 10-bit mode, these pi                                                                                                           | ns are not used.                                                                 |

| F1, F2, H1,<br>H2, J1, J2, |          |             |                                                                                                                                    | Chroma data input in SMPTE mode SMPTE_BYPASS = HIGH DVB_ASI = LOW                |

| K1, K2, J3,<br>K3          | DIN[9:0] | Input       | 20-bit mode<br>20BIT/10BIT = HIGH                                                                                                  | Data input in data through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW               |

|                            |          |             |                                                                                                                                    | Not Used in DVB-ASI mode  SMPTE_BYPASS = LOW  DVB_ASI = HIGH                     |

|                            |          |             | 10-bit mode<br>20BIT/10BIT = LOW                                                                                                   | Not used.                                                                        |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name        | Timing | Туре        | Description                                                                                                                                                   |

|---------------|-------------|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |             |        |             | CONTROL SIGNAL INPUT.                                                                                                                                         |

|               |             |        | Input       | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                            |

| F3            | DETECT_TRS  |        |             | Used to select external HVF timing mode or TRS extraction timing mode.                                                                                        |

|               | _           |        | ·           | When DETECT_TRS is LOW, the device extracts all internal timing from the supplied H:V:F or CEA-861 timing signals, dependent on the status of the TIM861 pin. |

|               |             |        |             | When DETECT_TRS is HIGH, the device extracts all internal timing from TRS signals embedded in the supplied video stream.                                      |

|               |             |        |             | COMMUNICATION SIGNAL OUTPUT.                                                                                                                                  |

|               |             |        |             | Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                           |

| F8            | TDO         |        | Output      | Dedicated JTAG pin.                                                                                                                                           |

|               |             |        |             | JTAG Test Data Output.                                                                                                                                        |

|               |             |        |             | This pin is used to shift results from the device when the JTAG/HOST pin is LOW.                                                                              |

| F10           | RSET        |        | Input       | An external 1% resistor connected to this input is used to set the SDO/SDO output signal amplitude.                                                           |

| G1, H10       | IO_VDD      |        | Input Power | Power connection for digital I/O. Connect to +3.3V or +1.8V DC digital.                                                                                       |

| E4, G2, H9    | IO_GND      |        | Input Power | Ground connection for digital I/O. Connect to digital GND.                                                                                                    |

|               |             |        | Input       | CONTROL SIGNAL INPUT.                                                                                                                                         |

|               |             |        |             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                            |

|               |             |        |             | Used to select external CEA-861 timing mode.                                                                                                                  |

| G3            | TIM_861     |        |             | When DETECT_TRS is LOW and TIM-861 is LOW, the device extracts all internal timing from the supplied H:V:F timing signals.                                    |

|               |             |        |             | When DETECT_TRS is LOW and TIM-861 is HIGH, the device extracts all internal timing from the supplied HSYNC, VSYNC, DE timing signals.                        |

|               |             |        |             | When DETECT_TRS is HIGH, the device extracts all internal timing from TRS signals embedded in the supplied video stream.                                      |

|               |             |        |             | CONTROL SIGNAL INPUT.                                                                                                                                         |

| G4            | 20bit/10bit |        | Input       | Please refer to the Input Logic parameters in the DC Electrical                                                                                               |

|               |             |        | прис        | Characteristics table for logic level threshold and compatibility.  Used to select the input bus width.                                                       |

|               |             |        |             | CONTROL SIGNAL INPUT                                                                                                                                          |

|               |             |        |             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                            |

|               |             |        | _           | Used to enable/disable the DVB-ASI data transmission.                                                                                                         |

| G5            | DVB_ASI     |        | Input       | When DVB_ASI is set HIGH and SMPTE_BYPASS is set LOW, then the device will carry out DVB-ASI word alignment, I/O processing and transmission.                 |

|               |             |        |             | When SMPTE_BYPASS and DVB_ASI are both set LOW, the device operates in data-through mode.                                                                     |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name          | Timing | Туре   | Description                                                                                                                                                          |

|---------------|---------------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |               |        |        | CONTROL SIGNAL INPUT.                                                                                                                                                |

|               |               |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                   |

|               |               |        |        | Used to enable / disable all forms of encoding / decoding, scrambling and EDH insertion.                                                                             |

| G6            | SMPTE_BYPASS  |        | Input  | When set LOW, the device operates in data through mode (DVB_ASI = LOW), or in DVB-ASI mode (DVB_ASI = HIGH).                                                         |

|               |               |        |        | No SMPTE scrambling takes place and none of the I/O processing features of the device are available when SMPTE_BYPASS is set LOV                                     |

|               |               |        |        | When set HIGH, the device carries out SMPTE scrambling and I/O processing.                                                                                           |

|               |               |        |        | CONTROL SIGNAL INPUT.                                                                                                                                                |

|               |               |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                   |

| G7            | IOPROC_EN/DIS |        | Input  | Used to enable or disable the I/O processing features.                                                                                                               |

| <b>.</b>      |               |        |        | When IOPROC_EN/DIS is HIGH, the I/O processing features of the device are enabled. When IOPROC_EN/DIS is LOW, the I/O processin features of the device are disabled. |

|               |               |        |        | Only applicable in SMPTE mode.                                                                                                                                       |

|               |               |        |        | CONTROL SIGNAL INPUT.                                                                                                                                                |

|               |               |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                   |

|               |               | Input  |        | Used to reset the internal operating conditions to default settings and to reset the JTAG sequence.                                                                  |

|               |               |        |        | Normal mode (JTAG/ $\overline{HOST}$ = LOW).                                                                                                                         |

| G8            | RESET         |        | Input  | When LOW, all functional blocks will be set to default conditions and all input and output signals become high impedance.                                            |

|               |               |        |        | When HIGH, normal operation of the device resumes.                                                                                                                   |

|               |               |        |        | JTAG test mode (JTAG/ $\overline{\text{HOST}}$ = HIGH).                                                                                                              |

|               |               |        |        | When LOW, all functional blocks will be set to default and the JTA test sequence will be reset.                                                                      |

|               |               |        |        | When HIGH, normal operation of the JTAG test sequence resumes.                                                                                                       |

|               |               |        |        | CONTROL SIGNAL INPUT.                                                                                                                                                |

|               |               |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                   |

| Н3            | ANC_BLANK     | Input  | Input  | When $\overline{\text{ANC\_BLANK}}$ is LOW, the Luma and Chroma input data is set to the appropriate blanking levels during the H and V blanking intervals.          |

|               |               |        |        | When $\overline{\text{ANC\_BLANK}}$ is HIGH, the blanking function is disabled.                                                                                      |

|               |               |        |        | Only applicable in SMPTE mode.                                                                                                                                       |

|               |               |        |        | STATUS SIGNAL OUTPUT.                                                                                                                                                |

|               | 100           |        |        | Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                  |

| H4            | LOCKED        |        | Output | PLL lock indication.                                                                                                                                                 |

|               |               |        |        | HIGH indicates PLL is locked.                                                                                                                                        |

|               |               |        |        | LOW indicates PLL is not locked.                                                                                                                                     |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name                  | Timing | Туре   | Description                                                                                                                                                                           |  |  |  |

|---------------|-----------------------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|               |                       |        |        | CONTROL SIGNAL INPUT.                                                                                                                                                                 |  |  |  |

|               |                       |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                    |  |  |  |

| Н8            | JTAG/ <del>HOST</del> |        | Input  | Used to select JTAG test mode or host interface mode.                                                                                                                                 |  |  |  |

|               |                       |        |        | When JTAG/HOST is HIGH, the host interface port is configured for JTAG test.                                                                                                          |  |  |  |

|               |                       |        |        | When JTAG/HOST is LOW, normal operation of the host interface port resumes and the separate JTAG pins become the JTAG port.                                                           |  |  |  |

|               |                       |        |        | COMMUNICATION SIGNAL INPUT.                                                                                                                                                           |  |  |  |

| J8            | TCK                   |        | Input  | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                    |  |  |  |

|               |                       |        | ·      | JTAG Serial Data Clock Signal.                                                                                                                                                        |  |  |  |

|               |                       |        |        | This pin is the JTAG clock when the JTAG/HOST pin is LOW.                                                                                                                             |  |  |  |

|               |                       |        |        | COMMUNICATION SIGNAL OUTPUT.                                                                                                                                                          |  |  |  |

|               |                       |        |        | Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                   |  |  |  |

|               |                       |        |        | Shared JTAG/HOST pin. Provided for compatibility with the GS1582. Serial Data Output/Test Data Output.                                                                                |  |  |  |

|               | SDOUT_TDO             |        |        | Host Mode (JTAG/HOST = LOW) This pin operates as the host interface serial output, used to read status and configuration information from the internal registers of the device.       |  |  |  |

| 19            |                       |        | Output | JTAG Test Mode (JTAG/HOST = HIGH) This pin is used to shift test results and operates as the JTAG test data output, TDO (for new designs, use the dedicated JTAG port).               |  |  |  |

|               |                       |        |        | <b>Note:</b> If the host interface is not being used leave this pin unconnected.                                                                                                      |  |  |  |

|               |                       |        |        | IO_VDD = +3.3V<br>Drive Strength = 12mA                                                                                                                                               |  |  |  |

|               |                       |        |        | IO_VDD = +1.8V<br>Drive Strength = 4mA                                                                                                                                                |  |  |  |

|               |                       |        |        | COMMUNICATION SIGNAL INPUT.                                                                                                                                                           |  |  |  |

|               |                       |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                    |  |  |  |

|               |                       |        |        | Shared JTAG/HOST pin. Provided for pin compatibility with GS1582.                                                                                                                     |  |  |  |

|               |                       |        |        | Serial data clock signal.                                                                                                                                                             |  |  |  |

| J10           | SCLK_TCK              |        | Input  | Host Mode (JTAG/HOST = LOW)  SCLK_TCK operates as the host interface burst clock, SCLK.  Command and data read/write words are clocked into the device synchronously with this clock. |  |  |  |

|               |                       |        |        | JTAG Test Mode (JTAG/HOST = HIGH) This pin is the TEST MODE START pin, used to control the operation of the JTAG test clock, TCK (for new designs, use the dedicated JTAG port).      |  |  |  |

|               |                       |        |        | Note: If the host interface is not being used, tie this pin HIGH.                                                                                                                     |  |  |  |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name     | Timing | Туре  | Description                                                                                                                                                                                                         |

|---------------|----------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |          |        |       | COMMUNICATION SIGNAL INPUT.                                                                                                                                                                                         |

|               |          |        |       | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                  |

|               |          |        |       | Chip select / test mode start.                                                                                                                                                                                      |

| К9            | CS_TMS   |        | Input | JTAG Test mode (JTAG/ <del>HOST</del> = HIGH)  CS_TMS operates as the JTAG test mode start, TMS, used to control the operation of the JTAG test, and is active HIGH (for new designs, use the dedicated JTAG port). |

|               |          |        |       | Host mode (JTAG/ $\overline{\text{HOST}}$ = LOW), $\overline{\text{CS}}$ _TMS operates as the host interface Chip Select, $\overline{\text{CS}}$ , and is active LOW.                                               |

|               |          |        |       | COMMUNICATION SIGNAL INPUT.                                                                                                                                                                                         |

|               |          |        |       | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                  |

|               | SDIN_TDI |        |       | Shared JTAG/HOST pin. Provided for pin compatibility with GS1582.                                                                                                                                                   |

| K10           |          |        | Input | Serial data in/test data in.                                                                                                                                                                                        |

|               |          |        |       | In JTAG mode, this pin is used to shift test data into the device (for new designs, use the dedicated JTAG port).                                                                                                   |

|               |          |        |       | In host interface mode, this pin is used to write address and configuration data words into the device.                                                                                                             |

## 2. Electrical Characteristics

### 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                       | Value/Units     |

|-------------------------------------------------|-----------------|

| Supply Voltage, Digital Core (CORE_VDD)         | -0.3V to +1.5V  |

| Supply Voltage, Digital I/O (IO_VDD)            | -0.3V to +3.6V  |

| Supply Voltage, Analog +1.2V (PLL_VDD, VCO_VDD) | -0.3V to +1.5V  |

| Supply Voltage, Analog +3.3V (CD_VDD, A_VDD)    | -0.3V to +3.6V  |

| Input Voltage Range (digital inputs)            | -2.0V to +5.25V |

| Operating Temperature Range                     | -20°C to +85°C  |

| Functional Temperature Range                    | -40°C to +85°C  |

| Storage Temperature Range                       | -40°C to +125°C |

| Peak Reflow Temperature (JEDEC J-STD-020C)      | 260°C           |

| ESD Sensitivity, HBM (JESD22-A114)              | 2kV             |

**Note:** Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation outside of the ranges shown in Table 2-1 is not implied.

#### 2.2 Recommended Operating Conditions

**Table 2-2: Recommended Operating Conditions**

| Parameter                               | Symbol         | Conditions | Min  | Тур | Max  | Units | Notes |

|-----------------------------------------|----------------|------------|------|-----|------|-------|-------|

| Operating Temperature Range,<br>Ambient | T <sub>A</sub> | -          | -20  | _   | 85   | °C    | _     |

| Supply Voltage, Digital Core            | CORE_VDD       | -          | 1.14 | 1.2 | 1.26 | V     | _     |

| Supply Voltage Digital I/O              | IO VDD         | +1.8V mode | 1.71 | 1.8 | 1.89 | V     | _     |

| Supply Voltage, Digital I/O             | IO_VDD         | +3.3V mode | 3.13 | 3.3 | 3.47 | V     | =     |

| Supply Voltage, PLL                     | PLL_VDD        | -          | 1.14 | 1.2 | 1.26 | V     | _     |

| Supply Voltage, VCO                     | VCO_VDD        | -          | -    | 0.7 | _    | V     | 1     |

| Supply Voltage, Analog                  | A_VDD          | -          | 3.13 | 3.3 | 3.47 | V     | _     |

| Supply Voltage, CD                      | CD_VDD         | -          | 3.13 | 3.3 | 3.47 | V     | _     |

| Operating Temperature Range             | -              | =          | -20  | _   | 85   | °C    | 2     |

| Functional Temperature Range            | -              | -          | -40  | -   | 85   | °C    | 2     |

#### Notes

GENDOC-053628 September 2013

<sup>1.</sup> This is 0.7V rather than 1.2V because there is a voltage drop across an external  $105\Omega$  resistor. See Typical Application Circuit on page 66.

<sup>2.</sup> Operating Temperature Range guarantees the parameters given in the DC Electrical Characteristics and AC Electrical Characteristics. Functional Temperature Range guarantees a device start-up.

### 2.3 DC Electrical Characteristics

**Table 2-3: DC Electrical Characteristics**

$V_{CC}$  = +3.3V ±5%,  $T_A$  = -20°C to +85°C, unless otherwise shown

| Parameter                               | Symbol             | Conditions                           | Min             | Тур                               | Max          | Units | Notes |

|-----------------------------------------|--------------------|--------------------------------------|-----------------|-----------------------------------|--------------|-------|-------|

| System                                  |                    |                                      |                 |                                   |              |       |       |

|                                         |                    | 10/20bit HD                          | _               | 90                                | 150          | mA    | _     |

| +1.2V Supply Current                    | I <sub>1V2</sub>   | 10/20bit SD                          | _               | 75                                | 120          | mA    | _     |

|                                         |                    | DVB_ASI                              | _               | 75                                | 120          | mA    | _     |

|                                         |                    | 10/20bit HD                          | _               | 10                                | 25           | mA    | _     |

| +1.8V Supply Current                    | I <sub>1V8</sub>   | 10/20bit SD                          | -               | 3                                 | 10           | mA    | =     |

|                                         |                    | DVB_ASI                              | -               | 3                                 | 10           | mA    | =     |

|                                         |                    | 10/20bit HD                          | -               | 80                                | 100          | mA    | _     |

| +3.3V Supply Current                    | $I_{3V3}$          | 10/20bit SD                          | -               | 70                                | 90           | mA    | _     |

|                                         |                    | DVB_ASI                              | -               | 70                                | 90           | mA    | _     |

|                                         |                    | 10/20bit HD                          | -               | 330                               | 490          | mW    | _     |

|                                         | P <sub>1D8</sub>   | 10/20bit SD                          | -               | 300                               | 450          | mW    | _     |

| Total Device Power (IO_VDD = +1.8V)     |                    | DVB_ASI                              | -               | 300                               | 410          | mW    | _     |

| ,                                       |                    | Reset                                | -               | 200                               | _            | mW    | -     |

|                                         |                    | Standby                              | -               | 100                               | 180          | mW    | 1     |