Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**GS1670**

# **HD/SD SDI Receiver Complete with SMPTE Audio and Video Processing**

#### **Key Features**

- Operation at 1.485Gb/s, 1.485/1.001Gb/s and 270Mb/s

- Supports SMPTE 292, SMPTE 259M-C and DVB-ASI

- Integrated Reclocker with low phase noise, integrated VCO

- Serial digital reclocked, or non-reclocked loop-through output

- Integrated audio de-embedder for 8 channels of 48kHz audio

- Integrated audio clock generator

- Ancillary data extraction

- Parallel data bus selectable as either 20-bit or 10-bit

- Comprehensive error detection and correction features

- Output H, V, F or CEA 861 timing signals

- 1.2V digital core power supply, 1.2V and 3.3V analog power supplies, and selectable 1.8V or 3.3V I/O power supply

- GSPI host interface

- -20°C to +85°C operating temperature range

- Low power operation (typically 300mW)

- Small 11mm x 11mm 100-ball BGA package

- Pb-free and RoHS compliant

#### **Errata**

Refer to Errata document entitled **GS1670/GS1671 Errata** for this device (document number **53878**).

## **Applications**

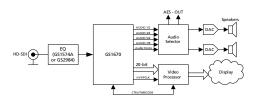

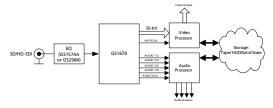

Application: 1080p30 or 720p60 Monitor

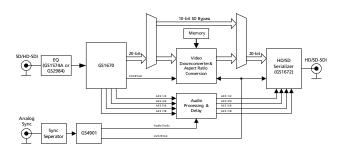

#### Application: Multi-format Downconverter

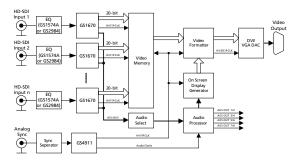

#### Application: Multi-input Video Monitoring System

Application: Multi-format Audio De-embedder Module

Application: Multi-format Digital VTR/Video Server

#### **Description**

The GS1670 is a multi-rate SDI Receiver which includes complete SMPTE processing, as per SMPTE 292 and SMPTE 259M-C. The SMPTE processing features can be bypassed to support signals with other coding schemes.

The device features an Integrated Reclocker with an internal VCO and a wide Input Jitter Tolerance (IJT) of 0.7UI.

A serial digital loop-through output is provided, which can be configured to output either reclocked or non-reclocked serial digital data. The serial digital output can be connected to an external cable driver.

The device operates in one of four basic modes: SMPTE mode, DVB-ASI mode, Data-Through mode or Standby mode.

In SMPTE mode, the GS1670 performs SMPTE de-scrambling and NRZI to NRZ decoding and word alignment. Line-based CRC errors, line number errors, TRS errors and ancillary data check sum errors can all be detected. The GS1670 also provides ancillary data extraction. The entire ancillary data packet is extracted, and written to host-accessible registers. Other processing functions include H:V:F timing extraction, Luma and

Chroma ancillary data indication, video standard detection, and SMPTE 352M packet detection and decoding. All of the processing features are optional, and may be enabled or disabled via the Host Interface.

In DVB-ASI mode, 8b/10b decoding is applied to the received data stream.

In Data-Through mode all forms of SMPTE and DVB-ASI processing are disabled, and the device can be used as a simple serial to parallel converter.

The device can also operate in a lower power Standby mode. In this mode, no signal processing is carried out and the parallel output is held static.

Parallel data outputs are provided in 20-bit or 10-bit multiplexed format for HD and SD video rates. The associated Parallel Clock input signal operates at 148.5 or 148.5/1.001MHz (HD 10-bit multiplexed modes), 74.25 or 74.25/1.001MHz (for HD 20-bit mode), 27MHz (for SD 10-bit mode) and 13.5MHz (for SD 20-bit mode).

Up to eight channels, in two groups, of serial digital audio may be extracted from the video data stream, in accordance with SMPTE 272M and SMPTE 299M. The output signal formats supported by the device include AES/EBU and three other industry standard serial digital formats. 16, 20 and 24-bit audio formats are supported at 48kHz synchronous for SD modes and 48kHz synchronous or asynchronous in HD mode. Additional audio processing features include group selection, channel swapping, ECC error detection and correction (HD mode only), and audio channel status extraction. Audio clock and control signals provided by the device include Word Clock (fs), Serial Clock (64fs), and Audio Master Clock at user-selectable rates of 128fs, 256fs or 512fs.

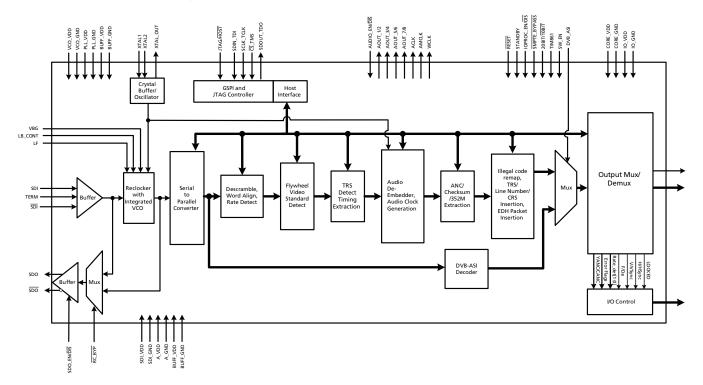

# **Functional Block Diagram**

**GS1670 Functional Block Diagram**

## **Revision History**

| Version | ECR    | PCN | Date           | Changes and/or Modifications                                                   |

|---------|--------|-----|----------------|--------------------------------------------------------------------------------|

| 2       | 158468 | -   | September 2012 | Changes throughout the document.                                               |

| 1       | 153472 | -   | January 2010   | Converted to Data Sheet.                                                       |

| 0       | 153078 | -   | November 2009  | New Document. Added reference to GS1670/GS1671 Errata (document number 53878). |

## **Contents**

| Key Features                               | 1  |

|--------------------------------------------|----|

| Errata                                     | 1  |

| Applications                               | 1  |

| Description                                | 2  |

| Functional Block Diagram                   | 3  |

| Revision History                           | 3  |

| 1. Pin Out                                 | 8  |

| 1.1 Pin Assignment                         | 8  |

| 1.2 Pin Descriptions                       | 8  |

| 2. Electrical Characteristics              | 15 |

| 2.1 Absolute Maximum Ratings               | 15 |

| 2.2 Recommended Operating Conditions       | 15 |

| 2.3 DC Electrical Characteristics          | 16 |

| 2.4 AC Electrical Characteristics          | 18 |

| 3. Input/Output Circuits                   | 22 |

| 4. Detailed Description                    | 25 |

| 4.1 Functional Overview                    | 25 |

| 4.2 Serial Digital Input                   | 25 |

| 4.3 Serial Digital Loop-Through Output     | 25 |

| 4.4 Serial Digital Reclocker               | 26 |

| 4.4.1 PLL Loop Bandwidth                   | 26 |

| 4.5 External Crystal/Reference Clock       | 27 |

| 4.6 Lock Detect                            | 28 |

| 4.6.1 Asynchronous Lock                    | 29 |

| 4.6.2 Signal Interruption                  | 29 |

| 4.7 SMPTE Functionality                    | 30 |

| 4.7.1 Descrambling and Word Alignment      | 30 |

| 4.8 Parallel Data Outputs                  | 30 |

| 4.8.1 Parallel Data Bus Buffers            | 30 |

| 4.8.2 Parallel Output in SMPTE Mode        | 33 |

| 4.8.3 Parallel Output in DVB-ASI Mode      | 33 |

| 4.8.4 Parallel Output in Data-Through Mode | 34 |

| 4.8.5 Parallel Output Clock (PCLK)         | 34 |

| 4.9 Timing Signal Generator                | 35 |

| 4.9.1 Manual Switch Line Lock Handling     | 35 |

| 4.9.2 Automatic Switch Line Lock Handling  | 36 |

| 4.10 Programmable Multi-function Outputs   | 38 |

| 4.11 H:V:F Timing Signal Generation        | 39 |

| 4.11.1 CEA-861 Timing Generation           | 40 |

| 4.12 Automatic Video Standards Detection   | 46 |

| 4.13 Data Format Detection & Indication    | 48 |

| 4.14 EDH Detection                         | 49 |

| 4.14.1 EDH Packet Detection                | 49 |

| 4.14.2 EDH Flag Detection                  | 50 |

|                                            |    |

|      | 4.15 Video Signal Error Detection & Indication        | 50  |

|------|-------------------------------------------------------|-----|

|      | 4.15.1 TRS Error Detection                            | 52  |

|      | 4.15.2 Line Based CRC Error Detection                 | 52  |

|      | 4.15.3 EDH CRC Error Detection                        | 53  |

|      | 4.15.4 HD Line Number Error Detection                 | 53  |

|      | 4.16 Ancillary Data Detection & Indication            | 53  |

|      | 4.16.1 Programmable Ancillary Data Detection          | 54  |

|      | 4.16.2 SMPTE 352M Payload Identifier                  | 55  |

|      | 4.16.3 Ancillary Data Checksum Error                  | 55  |

|      | 4.16.4 Video Standard Error                           | 56  |

|      | 4.17 Signal Processing                                | 56  |

|      | 4.17.1 TRS Correction & Insertion                     | 57  |

|      | 4.17.2 Line Based CRC Correction & Insertion          | 58  |

|      | 4.17.3 Line Number Error Correction & Insertion       | 58  |

|      | 4.17.4 ANC Data Checksum Error Correction & Insertion | 58  |

|      | 4.17.5 EDH CRC Correction & Insertion                 | 58  |

|      | 4.17.6 Illegal Word Re-mapping                        | 59  |

|      | 4.17.7 TRS and Ancillary Data Preamble Remapping      | 59  |

|      | 4.17.8 Ancillary Data Extraction                      |     |

|      | 4.18 Audio De-embedder                                | 63  |

|      | 4.18.1 Serial Audio Data I/O Signals                  | 63  |

|      | 4.18.2 Serial Audio Data Format Support               | 64  |

|      | 4.18.3 Audio Processing                               | 69  |

|      | 4.18.4 Error Reporting                                | 75  |

|      | 4.19 GSPI - HOST Interface                            | 76  |

|      | 4.19.1 Command Word Description                       | 76  |

|      | 4.19.2 Data Read or Write Access                      | 77  |

|      | 4.19.3 GSPI Timing                                    | 78  |

|      | 4.20 Host Interface Register Maps                     | 80  |

|      | 4.20.1 Video Core Registers                           | 80  |

|      | 4.20.2 SD Audio Core Registers                        | 89  |

|      | 4.20.3 HD Audio Core Registers                        | 103 |

|      | 4.21 JTAG Test Operation                              | 119 |

|      | 4.22 Device Power-up                                  | 120 |

|      | 4.23 Device Reset                                     | 120 |

|      | 4.24 Standby Mode                                     | 120 |

| 5. A | pplication Reference Design                           | 121 |

|      | 5.1 Typical Application Circuit                       | 121 |

| 6. R | eferences & Relevant Standards                        | 122 |

| 7. P | ackage & Ordering Information                         | 123 |

|      | 7.1 Package Dimensions                                | 123 |

|      | 7.2 Packaging Data                                    | 124 |

|      | 7.3 Marking Diagram                                   | 124 |

|      | 7.4 Solder Reflow Profiles                            | 125 |

|      | 7.5 Ordering Information                              | 125 |

# **List of Figures**

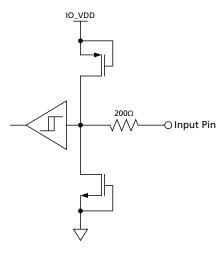

| Figure 3-1: Digital Input Pin with Schmitt Trigger                                  | 22 |

|-------------------------------------------------------------------------------------|----|

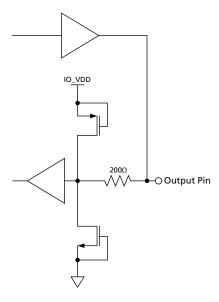

| Figure 3-2: Bidirectional Digital Input/Output Pin                                  | 22 |

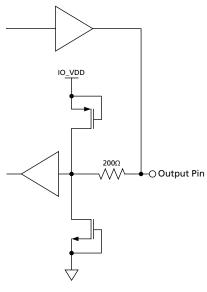

| Figure 3-3: Bidirectional Digital Input/Output Pin with programmable drive strength | 23 |

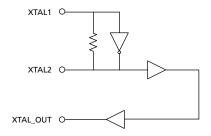

| Figure 3-4: XTAL1/XTAL2/XTAL-OUT                                                    | 23 |

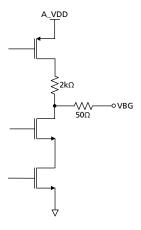

| Figure 3-5: VBG                                                                     | 23 |

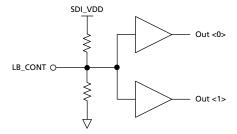

| Figure 3-6: LB_CONT                                                                 | 24 |

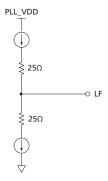

| Figure 3-7: Loop Filter                                                             | 24 |

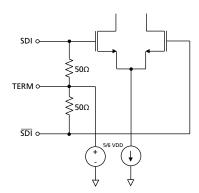

| Figure 3-8: SDI/SDI and TERM                                                        | 24 |

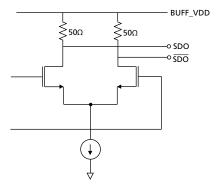

| Figure 3-9: SDO/SDO                                                                 | 24 |

| Figure 4-1: 27MHz Clock Sources                                                     | 28 |

| Figure 4-2: PCLK to Data and Control Signal Output Timing - SDR Mode 1              | 31 |

| Figure 4-3: PCLK to Data and Control Signal Output Timing - SDR Mode 2              | 32 |

| Figure 4-4: Switch Line Locking on a Non-Standard Switch Line                       | 36 |

| Figure 4-5: H:V:F Output Timing - HDTV 20-bit Mode                                  | 39 |

| Figure 4-6: H:V:F Output Timing - HDTV 10-bit Mode                                  | 39 |

| Figure 4-7: H:V:F Output Timing - HD 20-bit Output Mode                             |    |

| Figure 4-8: H:V:F Output Timing - HD 10-bit Output Mode                             |    |

| Figure 4-9: H:V:F Output Timing - SD 20-bit Output Mode                             |    |

| Figure 4-10: H:V:F Output Timing - SD 10-bit Output Mode                            |    |

| Figure 4-11: H:V:DE Output Timing 1280 x 720p @ 59.94/60 (Format 4)                 |    |

| Figure 4-12: H:V:DE Output Timing 1920 x 1080i @ 59.94/60 (Format 5)                |    |

| Figure 4-13: H:V:DE Output Timing 720 (1440) x 480i @ 59.94/60 (Format 6&7)         |    |

| Figure 4-14: H:V:DE Output Timing 1280 x 720p @ 50 (Format 19)                      |    |

| Figure 4-15: H:V:DE Output Timing 1920 x 1080i @ 50 (Format 20)                     |    |

| Figure 4-16: H:V:DE Output Timing 720 (1440) x 576 @ 50 (Format 21 & 22)            |    |

| Figure 4-17: H:V:DE Output Timing 1920 x 1080p @ 23.94/24 (Format 32)               |    |

| Figure 4-18: H:V:DE Output Timing 1920 x 1080p @ 25 (Format 33)                     |    |

| Figure 4-19: H:V:DE Output Timing 1920 x 1080p @ 29.97/30 (Format 34)               |    |

| Figure 4-20: Y/1ANC and C/2ANC Signal Timing                                        |    |

| Figure 4-21: Ancillary Data Extraction - Step A                                     |    |

| Figure 4-22: Ancillary Data Extraction - Step B                                     |    |

| Figure 4-23: Ancillary Data Extraction - Step C                                     |    |

| Figure 4-24: Ancillary Data Extraction - Step D                                     |    |

| Figure 4-25: ACLK to Data Signal Output Timing                                      |    |

| Figure 4-26: I <sup>2</sup> S Audio Output Format                                   |    |

| Figure 4-27: AES/EBU Audio Output Format                                            |    |

| Figure 4-28: Serial Audio, Left Justified, MSB First                                |    |

| Figure 4-29: Serial Audio, Left Justified, LSB First                                |    |

| Figure 4-30: Serial Audio, Right Justified, MSB First                               |    |

| Figure 4-31: Serial Audio, Right Justified, LSB First                               |    |

| Figure 4-32: AES/EBU Audio Output to Bit Clock Timing                               |    |

| Figure 4-33: ECC 24-bit Array and Examples                                          |    |

| Figure 4-34: Sample Distribution over 5 Video Frames (525-line Systems)             |    |

| Figure 4-35: Audio Buffer After Initial 26 Sample Write                             |    |

| Figure 4-36: Audio Buffer Pointer Boundary Checking                                 |    |

| Figure 4-37: GSPI Application Interface Connection                                  |    |

| Figure 4-38: Command Word Format                                                    |    |

| Figure 4-39: Data Word Format                                                       |    |

| Figure 4-40: Write Mode                                                             |    |

| Figure 4-41: Read Mode                                                              |    |

| Figure 4-42: GSPI Time Delay                                                        |    |

| •                                                                                   |    |

| Figure 4-43: In-Circuit JTAG              | 119  |

|-------------------------------------------|------|

| Figure 4-44: System JTAG                  | .119 |

| Figure 4-45: Reset Pulse                  | .120 |

| Figure 7-1: Pb-free Solder Reflow Profile | 125  |

## **List of Tables**

| Table 1-1: Pin Descriptions                                                 | 8     |

|-----------------------------------------------------------------------------|-------|

| Table 2-1: Absolute Maximum Ratings                                         | 15    |

| Table 2-2: Recommended Operating Conditions                                 | 15    |

| Table 2-3: DC Electrical Characteristics                                    | 16    |

| Table 2-4: AC Electrical Characteristics                                    | 18    |

| Table 4-1: Serial Digital Output                                            | 26    |

| Table 4-2: PLL Loop Bandwidth                                               | 27    |

| Table 4-3: Input Clock Requirements                                         | 28    |

| Table 4-4: Lock Detect Conditions                                           | 29    |

| Table 4-5: GS1670 Output Video Data Format Selections                       | 32    |

| Table 4-6: GS1670 PCLK Output Rates                                         | 34    |

| Table 4-7: Switch Line Position for Digital Systems                         | 37    |

| Table 4-8: Output Signals Available on Programmable Multi-Function Pins     | 38    |

| Table 4-9: Supported CEA-861 Formats                                        | 41    |

| Table 4-10: CEA861 Timing Formats                                           |       |

| Table 4-11: Supported Video Standard Codes                                  | 47    |

| Table 4-12: Data Format Register Codes                                      | 49    |

| Table 4-13: Error Status Register and Error Mask Register                   |       |

| Table 4-14: IOPROC_DISABLE Register Bits                                    | 57    |

| Table 4-15: Serial Audio Pin Descriptions                                   | 63    |

| Table 4-16: Audio Output Formats                                            | 65    |

| Table 4-17: Audio Data Packet Detect Register                               | 66    |

| Table 4-18: Audio Group DID Host Interface Settings                         | 67    |

| Table 4-19: Audio Data and Control Packet DID Setting Register              | 68    |

| Table 4-20: Audio Buffer Pointer Offset Settings                            | 71    |

| Table 4-21: Audio Channel Mapping Codes                                     | 72    |

| Table 4-22: Audio Sample Word Lengths                                       | 72    |

| Table 4-23: Audio Channel Status Information Registers                      | 73    |

| Table 4-24: Audio Channel Status Block for Regenerate Mode Default Settings | 74    |

| Table 4-25: Audio Mute Control Bits                                         | 74    |

| Table 4-26: GSPI Time Delay                                                 | 78    |

| Table 4-27: GSPI Timing Parameters (50% levels; 3.3V or 1.8V operation)     | 79    |

| Table 4-28: Video Core Configuration and Status Registers                   | 80    |

| Table 4-29: SD Audio Core Configuration and Status Registers                | 89    |

| Table 4-30: HD Audio Core Configuration and Status Registers                | . 103 |

| Table 4-31: ANC Extraction FIFO Access Registers                            | . 118 |

| Table 7-1: Packaging Data                                                   | . 124 |

|                                                                             |       |

# 1. Pin Out

# 1.1 Pin Assignment

|   | 1            | 2              | 3                | 4           | 5            | 6            | 7                      | 8                 | 9      | 10     |

|---|--------------|----------------|------------------|-------------|--------------|--------------|------------------------|-------------------|--------|--------|

| Α | VBG          | LF             | LB_CONT          | VCO_<br>VDD | STAT0        | STAT1        | IO_VDD                 | PCLK              | DOUT18 | DOUT17 |

| В | A_VDD        | PLL_<br>VDD    | RSV              | VCO_<br>GND | STAT2        | STAT3        | IO_GND                 | DOUT19            | DOUT16 | DOUT15 |

| С | SDI          | A_GND          | PLL_<br>VDD      | PLL_<br>VDD | STAT4        | STAT5        | RESET<br>_TRST         | DOUT12            | DOUT14 | DOUT13 |

| D | SDI          | A_GND          | A_GND            | PLL_<br>GND | CORE<br>_GND | CORE<br>_VDD | SW_EN                  | JTAG/<br>HOST     | IO_GND | IO_VDD |

| Е | SDI_VDD      | SDI_GND        | A_GND            | PLL_<br>GND | CORE<br>_GND | CORE<br>_VDD | SDOUT_<br>TDO          | SDIN_<br>TDI      | DOUT10 | DOUT11 |

| F | TERM         | RSV            | A_GND            | PLL_<br>GND | CORE<br>_GND | CORE<br>_VDD | CS_<br>TMS             | SCLK_<br>TCK      | DOUT8  | DOUT9  |

| G | RSV          | RSV            | RC_BYP           | RSV         | CORE<br>_GND | CORE<br>_VDD | SMPTE_<br>BYPASS       | DVB_ASI           | IO_GND | IO_VDD |

| Н | BUFF_<br>VDD | BUFF_<br>GND   | AUDIO_<br>EN/DIS | WCLK        | TIM_861      | XTAL_<br>OUT | <u>20bit/</u><br>10bit | IOPROC_<br>EN/DIS | DOUT6  | DOUT7  |

| J | SDO          | SDO_<br>EN/DIS | AOUT_1/2         | ACLK        | AOUT_5/6     | XTAL2        | IO_GND                 | DOUT1             | DOUT4  | DOUT5  |

| K | SDO          | STANDBY        | AOUT_3/4         | AMCLK       | AOUT_7/8     | XTAL1        | IO_VDD                 | DOUT0             | DOUT2  | DOUT3  |

# **1.2 Pin Descriptions**

**Table 1-1:Pin Descriptions**

| Pin<br>Number | Name    | Timing | Туре         | Description                                                                                                                                                                                                                 |

|---------------|---------|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1            | VBG     |        | Analog Input | Band Gap voltage filter connection.                                                                                                                                                                                         |

| A2            | LF      |        | Analog Input | Loop Filter component connection.                                                                                                                                                                                           |

| А3            | LB_CONT |        | Analog Input | Connection for loop bandwidth control resistor.                                                                                                                                                                             |

| A4            | VCO_VDD |        | Input Power  | POWER pin for the VCO. Connect to a 1.2V $\pm$ 5% analog supply followed by a RC filter (see 5. Application Reference Design). A 105 $\Omega$ 1% resistor must be used in the RC filter circuit. VCO_VDD is nominally 0.7V. |

Table 1-1:Pin Descriptions (Continued)

| Pin<br>Number       | Name      | Timing | Туре        | Description                                          |                                                                                    |

|---------------------|-----------|--------|-------------|------------------------------------------------------|------------------------------------------------------------------------------------|

| A5, A6, B5,         | STAT[0:5] |        | Output      | MULTI-FUNCTIONAL OU                                  | ITPUT PORT.                                                                        |

| B6, C5, C6          |           |        |             |                                                      | out Logic parameters in the DC Electrical logic level threshold and compatibility. |

|                     |           |        |             | Each of the STAT [0:5] p<br>one of the following sig | ins can be configured individually to output<br>gnals:                             |

|                     |           |        |             | Signal                                               | Default                                                                            |

|                     |           |        |             | H/HSYNC                                              | STAT0                                                                              |

|                     |           |        |             | V/VSYNC                                              | STAT1                                                                              |

|                     |           |        |             | F/DE                                                 | STAT2                                                                              |

|                     |           |        |             | LOCKED                                               | STAT3                                                                              |

|                     |           |        |             | Y/1ANC                                               | STAT4                                                                              |

|                     |           |        |             | C/2ANC                                               | =                                                                                  |

|                     |           |        |             | DATA ERROR                                           | STAT5                                                                              |

|                     |           |        |             | VIDEO ERROR                                          | _                                                                                  |

|                     |           |        |             | AUDIO ERROR                                          | =                                                                                  |

|                     |           |        |             | EDH DETECTED                                         | =                                                                                  |

|                     |           |        |             | CARRIER DETECT                                       | _                                                                                  |

|                     |           |        |             | RATE_DET                                             | -                                                                                  |

| A7, D10,<br>G10, K7 | IO_VDD    |        | Input Power | POWER connection for o                               | digital I/O. Connect to 3.3V or 1.8V DC                                            |

| A8                  | PCLK      |        | Output      | PARALLEL DATA BUS CL                                 | оск                                                                                |

|                     |           |        |             |                                                      | out Logic parameters in the DC Electrical logic level threshold and compatibility. |

|                     |           |        |             | HD 10-bit mode                                       | PCLK @ 148.5 or 148.5/1.001MHz                                                     |

|                     |           |        |             | HD 20-bit mode                                       | PCLK @ 74.25 or 74.25/1.001MHz                                                     |

|                     |           |        |             | SD 10-bit mode                                       | PCLK @ 27MHz                                                                       |

|                     |           |        |             | SD 20-bit mode                                       | PCLK @ 13.5MHz                                                                     |

Table 1-1:Pin Descriptions (Continued)

| Pin<br>Number                      | Name                          | Timing | Туре         | Description                                    |                                                                                                                            |

|------------------------------------|-------------------------------|--------|--------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| A9, A10, B8,                       | DOUT18, 17, 19,               |        | Output       | PARALLEL DATA BUS                              |                                                                                                                            |

| B9, B10,C8,<br>C9, C10, E9,<br>E10 | 16, 15, 12, 14, 13,<br>10, 11 |        |              |                                                | out Logic parameters in the DC Electrical logic level threshold and compatibility.                                         |

| EIO                                |                               |        |              | 20-bit mode<br>20bit/10bit = HIGH              | SMPTE mode (SMPTE_BYPASS = HIGH<br>and DVB_ASI = LOW):<br>Luma data output for SD and HD data<br>rates.                    |

|                                    |                               |        |              |                                                | DVB-ASI mode (SMPTE_BYPASS = LOW<br>and DVB_ASI = HIGH):<br>Not defined                                                    |

|                                    |                               |        |              |                                                | Data-Through mode (SMPTE_BYPASS =<br>LOW and DVB_ASI = LOW):<br>Data output                                                |

|                                    |                               |        |              | 10-bit mode<br>20bit/10bit = LOW               | SMPTE mode (SMPTE_BYPASS = HIGH<br>and DVB_ASI = LOW):<br>Multiplexed Luma/Chroma data output<br>for SD and HD data rates. |

|                                    |                               |        |              |                                                | DVB-ASI mode ( <u>SMPTE_BYPASS</u> = LOW<br>and DVB_ASI = HIGH):<br>8b/10b decoded DVB-ASI data                            |

|                                    |                               |        |              |                                                | Data-Through mode (SMPTE_BYPASS =<br>LOW and DVB_ASI = LOW):<br>Data output                                                |

| B1                                 | A_VDD                         |        | Input Power  | POWER pin for analog o                         | circuitry. Connect to 3.3V DC analog.                                                                                      |

| B2, C3, C4                         | PLL_VDD                       |        | Input Power  | POWER pins for the Rec                         | locker PLL. Connect to 1.2V DC analog.                                                                                     |

| B3, F2, G1,<br>G2, G4              | RSV                           |        |              | These pins must be left                        | unconnected.                                                                                                               |

| B4                                 | VCO_GND                       |        | Input Power  | GND pin for the VCO. C                         | onnect to analog GND.                                                                                                      |

| B7, D9, G9,<br>J7                  | IO_GND                        |        | Input Power  | GND connection for dig                         | ital I/O. Connect to digital GND.                                                                                          |

| C1, D1                             | SDI, <del>SDI</del>           |        | Analog Input | Serial Digital Differentia                     | al Input.                                                                                                                  |

| C2, D2, D3,<br>E3, F3              | A_GND                         |        | Input Power  | GND pins for sensitive a                       | nalog circuitry. Connect to analog GND.                                                                                    |

| C7                                 | RESET_TRST                    |        | Input        | CONTROL SIGNAL INPU                            | Т                                                                                                                          |

|                                    |                               |        |              |                                                | t Logic parameters in the DC Electrical logic level threshold and compatibility.                                           |

|                                    |                               |        |              | and to reset the JTAG se                       |                                                                                                                            |

|                                    |                               |        |              | Normal mode (JTAG/HO                           | NST = LOW): nal blocks are set to default conditions and                                                                   |

|                                    |                               |        |              |                                                | s become high impedance.                                                                                                   |

|                                    |                               |        |              | •                                              | eration of the device resumes.                                                                                             |

|                                    |                               |        |              | JTAG test mode (JTAG/F                         | ·                                                                                                                          |

|                                    |                               |        |              | When LOW, all function sequence is reset.      | al blocks are set to default and the JTAG tes                                                                              |

|                                    |                               |        |              | When HIGH, normal operafter RESET_TRST is de-a | eration of the JTAG test sequence resumes asserted.                                                                        |

Table 1-1:Pin Descriptions (Continued)

| Pin<br>Number     | Name                  | Timing | Туре         | Description                                                                                                                         |

|-------------------|-----------------------|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| D4, E4, F4        | PLL_GND               |        | Input Power  | GND pins for the Reclocker PLL. Connect to analog GND.                                                                              |

| D5, E5, F5,<br>G5 | CORE_GND              |        | Input Power  | GND connection for device core. Connect to digital GND.                                                                             |

| D6, E6, F6,<br>G6 | CORE_VDD              |        | Input Power  | POWER connection for device core. Connect to 1.2V DC digital.                                                                       |

| D7                | SW_EN                 |        | Input        | CONTROL SIGNAL INPUT                                                                                                                |

|                   |                       |        |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  |

|                   |                       |        |              | Used to enable switch-line locking, as described in Section 4.9.1.                                                                  |

| D8                | JTAG/ <del>HOST</del> |        | Input        | CONTROL SIGNAL INPUT                                                                                                                |

|                   |                       |        |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  |

|                   |                       |        |              | Used to select JTAG test mode or host interface mode.                                                                               |

|                   |                       |        |              | When JTAG/HOST is HIGH, the host interface port is configured for JTAG test.                                                        |

|                   |                       |        |              | When JTAG/HOST is LOW, normal operation of the host interface port resumes.                                                         |

| E1                | SDI_VDD               |        | Input Power  | POWER pin for SDI buffer. Connect to 3.3V DC analog.                                                                                |

| E2                | SDI_GND               |        | Input Power  | GND pin for SDI buffer. Connect to analog GND.                                                                                      |

| E7                | SDOUT_TDO             |        | Output       | COMMUNICATION SIGNAL OUTPUT                                                                                                         |

|                   |                       |        |              | Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility. |

|                   |                       |        |              | GSPI serial data output/test data out.                                                                                              |

|                   |                       |        |              | In JTAG mode (JTAG/ $\overline{\text{HOST}}$ = HIGH), this pin is used to shift test results from the device.                       |

|                   |                       |        |              | In host interface mode, this pin is used to read status and configuration data from the device.                                     |

|                   |                       |        |              | <b>Note:</b> GSPI is slightly different than the SPI. For more details on GSPI, please refer to 4.19 GSPI - HOST Interface.         |

| E8                | SDIN_TDI              |        | Input        | COMMUNICATION SIGNAL INPUT                                                                                                          |

|                   |                       |        |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  |

|                   |                       |        |              | GSPI serial data in/test data in.                                                                                                   |

|                   |                       |        |              | In JTAG mode (JTAG/ $\overline{\text{HOST}}$ = HIGH), this pin is used to shift test data into the device.                          |

|                   |                       |        |              | In host interface mode, this pin is used to write address and configuration data words into the device.                             |

| F1                | TERM                  |        | Analog Input | Decoupling for internal SDI termination resistors.                                                                                  |

Table 1-1:Pin Descriptions (Continued)

| Pin<br>Number                       | Name               | Timing | Туре   | Description                                                                                                                                                                                           |

|-------------------------------------|--------------------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F7                                  | CS_TMS             |        | Input  | COMMUNICATION SIGNAL INPUT                                                                                                                                                                            |

|                                     |                    |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                    |

|                                     |                    |        |        | Chip select / test mode start.                                                                                                                                                                        |

|                                     |                    |        |        | In JTAG mode (JTAG/ $\overline{HOST}$ = HIGH), this pin is Test Mode Start, used to control the operation of the JTAG test.                                                                           |

|                                     |                    |        |        | In host interface mode (JTAG/ $\overline{\text{HOST}}$ = LOW), this pin operates as the host interface chip select and is active LOW.                                                                 |

| F8                                  | SCLK_TCK           |        | Input  | COMMUNICATION SIGNAL INPUT                                                                                                                                                                            |

|                                     |                    |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  Serial data clock signal.                                         |

|                                     |                    |        |        | In JTAG mode (JTAG/HOST = HIGH), this pin is the JTAG clock.                                                                                                                                          |

|                                     |                    |        |        | In host interface mode (JTAG/ $\overline{\text{HOST}}$ = LOW), this pin is the host interface serial bit clock.                                                                                       |

|                                     |                    |        |        | All JTAG/host interface addresses and data are shifted into/out of the device synchronously with this clock.                                                                                          |

| F9, F10, H9,                        | DOUT8, 9, 6, 7, 1, |        | Output | PARALLEL DATA BUS                                                                                                                                                                                     |

| H10, J8, J9,<br>J10, K8, K9,<br>K10 | 4, 5, 0, 2, 3      |        |        | Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                   |

| KIO                                 |                    |        |        | 20-bit mode 20bit/10bit = HIGH  20bit/10bit = HIGH  SMPTE mode (SMPTE_BYPASS = HIGH and DVB_ASI = LOW): Chroma data output for SD and HD data rates.  DVB-ASI mode (SMPTE_BYPASS = LOW                |

|                                     |                    |        |        | and DVB_ASI = HIGH):  Not defined                                                                                                                                                                     |

|                                     |                    |        |        | Data-Through mode (SMPTE_BYPASS =<br>LOW and DVB_ASI = LOW):<br>Data output                                                                                                                           |

|                                     |                    |        |        | 10-bit mode Forced LOW 20bit/10bit = LOW                                                                                                                                                              |

| G3                                  | RC_BYP             |        | Input  | CONTROL SIGNAL INPUT                                                                                                                                                                                  |

|                                     |                    |        |        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                    |

|                                     |                    |        |        | When this pin is LOW, the serial digital output is the buffered version of the input serial data. When this pin is HIGH, the serial digital output is the reclocked version of the input serial data. |

Table 1-1:Pin Descriptions (Continued)

| Pin<br>Number | Name         | Timing | Туре              | Description                                                                                                                                                                                                                                                                                                   |

|---------------|--------------|--------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>G</b> 7    | SMPTE_BYPASS |        | Input/Output      | CONTROL SIGNAL INPUT/OUTPUT                                                                                                                                                                                                                                                                                   |

|               |              |        |                   | Please refer to the Input/Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                     |

|               |              |        |                   | Indicates the presence of valid SMPTE data.                                                                                                                                                                                                                                                                   |

|               |              |        |                   | When the AUTO/MAN bit in the host interface register is HIGH (Default), this pin is an OUTPUT. SMPTE_BYPASS is HIGH when the device locks to a SMPTE compliant input. SMPTE_BYPASS is LOW under all other conditions.                                                                                         |

|               |              |        |                   | When the AUTO/MAN bit in the host interface register is LOW, this pin is an INPUT:                                                                                                                                                                                                                            |

|               |              |        |                   | No SMPTE scrambling takes place, and none of the I/O processing features of the device are available when $\overline{\text{SMPTE\_BYPASS}}$ is set LOW.                                                                                                                                                       |

|               |              |        |                   | When SMPTE_BYPASS is set HIGH, the device carries out SMPTE scrambling and I/O processing.  When SMPTE_BYPASS and DVB_ASI are both set LOW, the device operates in Data-Through mode.                                                                                                                         |

| G8            | DVB_ASI      |        | Input/Output      | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                                          |

|               | _            |        |                   | Please refer to the Input/Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                     |

|               |              |        |                   | Used to enable/disable DVB-ASI data extraction in manual mode.                                                                                                                                                                                                                                                |

|               |              |        |                   | When the AUTO/MAN bit in the host interface is LOW, this pin is a input and when the DVB_ASI pin is set HIGH the device will carry ou DVB_ASI data extraction and processing. The SMPTE_BYPASS pin must be set LOW. When SMPTE_BYPASS and DVB_ASI are both set LOW, the device operates in Data-Through mode. |

|               |              |        |                   | When the AUTO/MAN bit in the host interface is HIGH (default), DVB-ASI is configured as a status output (set LOW), and DVB-ASI input streams are not supported or recognized.                                                                                                                                 |

| H1            | BUFF_VDD     |        | Input Power       | POWER pin for the serial digital output $50\Omega$ buffer. Connect to 3.3 DC analog.                                                                                                                                                                                                                          |

| H2            | BUFF_GND     |        | Input Power       | GND pin for the cable driver buffer. Connect to analog GND.                                                                                                                                                                                                                                                   |

| НЗ            | AUDIO_EN/DIS |        | Input             | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                                          |

|               |              |        |                   | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility. Enables or disables audio extraction.                                                                                                                                      |

| H4            | WCLK         |        | Output            | 48kHz word clock for Audio.                                                                                                                                                                                                                                                                                   |

| H5            | TIM_861      |        | Input             | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                                          |

| 113           | 11101_001    |        | input             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                            |

|               |              |        |                   | Used to select CEA-861 timing mode.                                                                                                                                                                                                                                                                           |

|               |              |        |                   | When TIM_861 is HIGH, the device outputs CEA 861 timing signals (HSYNC/VSYNC/DE) instead of H:V:F digital timing signals.                                                                                                                                                                                     |

| Н6            | XTAL_OUT     |        | Digital<br>Output | Buffered 27MHz crystal output. Can be used to cascade the crystal signal.                                                                                                                                                                                                                                     |

Table 1-1:Pin Descriptions (Continued)

| Pin<br>Number | Name                   | Timing | Туре         | Description                                                                                                                                                                                                                                                                             |

|---------------|------------------------|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H7            | 20bit/10bit            |        | Input        | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                    |

|               |                        |        |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                      |

|               |                        |        |              | Used to select the output bus width.                                                                                                                                                                                                                                                    |

|               |                        |        |              | HIGH = 20-bit, LOW = 10-bit.                                                                                                                                                                                                                                                            |

| Н8            | IOPROC_EN/DIS          |        | Input        | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                    |

|               |                        |        |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                      |

|               |                        |        |              | Used to enable or disable audio and video processing features. When IOPROC_EN is HIGH, the audio and video processing features of the device are enabled. When IOPROC_EN is LOW, the processing features of the device are disabled, and the device is in a low-latency operating mode. |

| J1, K1        | SDO, <del>SDO</del>    |        | Output       | Serial Data Output Signal.                                                                                                                                                                                                                                                              |

|               |                        |        |              | $50\Omega\text{CML}$ buffer for interfacing to an external cable driver.                                                                                                                                                                                                                |

|               |                        |        |              | Serial digital output signal operating at 1.485Gb/s, 1.485/1.001Gb/s and 270Mb/s.                                                                                                                                                                                                       |

| J2            | SDO_EN/ <del>DIS</del> |        | Input        | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                    |

|               |                        |        |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                      |

|               |                        |        |              | Used to enable/disable the serial digital output stage.                                                                                                                                                                                                                                 |

|               |                        |        |              | When SDO_EN/DIS is LOW, the serial digital output signals, SDO and SDO, are both pulled HIGH.                                                                                                                                                                                           |

|               |                        |        |              | When SDO_EN/DIS is HIGH, the serial digital output signals, SDO and SDO, are enabled.                                                                                                                                                                                                   |

| J3            | AOUT_1/2               |        | Output       | Serial Audio Output; Channels 1 and 2.                                                                                                                                                                                                                                                  |

| J4            | ACLK                   |        | Output       | 64fs sample clock for audio.                                                                                                                                                                                                                                                            |

| J5            | AOUT_5/6               |        | Output       | Serial Audio Output; Channels 5 and 6.                                                                                                                                                                                                                                                  |

| J6, K6        | XTAL2, XTAL1           | ,      | Analog Input | Input connection for 27MHz crystal.                                                                                                                                                                                                                                                     |

| K2            | STANDBY                |        | Input        | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                    |

|               |                        |        |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                      |

|               |                        |        |              | When this pin is set HIGH, the device is placed in a power-saving mode. No data processing occurs, and the digital I/Os are powered down.                                                                                                                                               |

|               |                        |        |              | In this mode, the serial digital output signals, SDO and $\overline{\text{SDO}}$ , are both pulled HIGH.                                                                                                                                                                                |

| К3            | AOUT_3/4               |        | Output       | Serial Audio Output; Channels 3 and 4.                                                                                                                                                                                                                                                  |

| K4            | AMCLK                  |        | Output       | Oversampled master clock for audio (128fs, 256fs, 512fs selectable).                                                                                                                                                                                                                    |

| K5            | AOUT_7/8               |        | Output       | Serial Audio Output; Channels 7 and 8.                                                                                                                                                                                                                                                  |

# 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

**Table 2-1:Absolute Maximum Ratings**

| Parameter                                              | Value/Units                      |

|--------------------------------------------------------|----------------------------------|

| Supply Voltage, Digital Core (CORE_VDD)                | -0.3V to +1.5V                   |

| Supply Voltage, Digital I/O (IO_VDD)                   | -0.3V to +4.0V                   |

| Supply Voltage, Analog 1.2V (PD_VDD, VCO_VDD)          | -0.3V to +1.5V                   |

| Supply Voltage, Analog 3.3V (SDI_VDD, BUFF_VDD, A_VDD) | -0.3V to +4.0V                   |

| Input Voltage Range (digital inputs)                   | -2.0V to +5.25V                  |

| Ambient Operating Temperature (T <sub>A</sub> )        | -40°C ≤ T <sub>A</sub> ≤ 95°C    |

| Storage Temperature (T <sub>STG</sub> )                | -40°C ≤ T <sub>STG</sub> ≤ 125°C |

| Peak Reflow Temperature (JEDEC J-STD-020C)             | 260°C                            |

| ESD Sensitivity, HBM (JESD22-A114)                     | 2kV                              |

#### NOTES:

Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation under these conditions or at any other condition beyond those indicated in the AC/DC Electrical Characteristics sections is not implied.

## 2.2 Recommended Operating Conditions

**Table 2-2:Recommended Operating Conditions**

| Parameter                               | Symbol         | Conditions | Min  | Тур | Max  | Units | Notes |

|-----------------------------------------|----------------|------------|------|-----|------|-------|-------|

| Operating Temperature Range,<br>Ambient | T <sub>A</sub> | -          | -20  | _   | 85   | °C    | _     |

| Supply Voltage, Digital Core            | CORE_VDD       | _          | 1.14 | 1.2 | 1.26 | V     | _     |

| Comple Valence Digital I/O              | IO VDD         | 1.8V mode  | 1.71 | 1.8 | 1.89 | V     | =     |

| Supply Voltage, Digital I/O             | IO_VDD         | 3.3V mode  | 3.13 | 3.3 | 3.47 | V     | =     |

| Supply Voltage, PLL                     | PLL_VDD        | _          | 1.14 | 1.2 | 1.26 | V     | _     |

| Supply Voltage, VCO                     | VCO_VDD        | _          | -    | 0.7 | =    | V     | 1     |

| Supply Voltage, Analog                  | A_VDD          | _          | 3.13 | 3.3 | 3.47 | V     | 2     |

| Supply Voltage, Serial Digital Input    | SDI_VDD        | -          | 3.13 | 3.3 | 3.47 | V     | 2     |

| Supply Voltage, CD Buffer               | BUFF_VDD       | -          | 3.13 | 3.3 | 3.47 | V     | 2     |

#### NOTES

- 1. This is 0.7V rather than 1.2V because there is a voltage drop across an external  $105\Omega$  resistor. See Typical Application Circuit on page 121.

- 2. The 3.3V supplies must track the 3.3V supply of an external EQ and external CD.

# 2.3 DC Electrical Characteristics

**Table 2-3:DC Electrical Characteristics**

| Parameter                               | Symbol           | Conditions                | Min                  | Тур                   | Max                   | Units | Notes |

|-----------------------------------------|------------------|---------------------------|----------------------|-----------------------|-----------------------|-------|-------|

| System                                  |                  |                           |                      |                       |                       |       |       |

| +1.2V Supply Current                    | I <sub>1V2</sub> | 10/20bit HD               | _                    | 175                   | 215                   | mA    | _     |

|                                         |                  | 10/20bit SD               | -                    | 145                   | 180                   | mA    | -     |

|                                         |                  | DVB_ASI                   | -                    | 135                   | 165                   | mA    | -     |

| +1.8V Supply Current                    | I <sub>1V8</sub> | 10/20bit HD               | -                    | 20                    | 21                    | mA    | -     |

|                                         |                  | 10/20bit SD               | -                    | 6                     | 7                     | mA    | -     |

|                                         |                  | DVB_ASI                   | -                    | 6                     | 7                     | mA    | -     |

| +3.3V Supply Current                    | I <sub>3V3</sub> | 10/20bit HD               | -                    | 65                    | 75                    | mA    | -     |

|                                         |                  | 10/20bit SD               | =                    | 35                    | 45                    | mA    | -     |

|                                         |                  | DVB_ASI                   | -                    | 35                    | 45                    | mA    | -     |

| Total Device Power                      | P <sub>1D8</sub> | 10/20bit HD               | _                    | 300                   | 360                   | mW    | -     |

| $(IO_VDD = 1.8V)$                       |                  | 10/20bit SD               | _                    | 235                   | 305                   | mW    | -     |

|                                         |                  | DVB_ASI                   | -                    | 235                   | 305                   | mW    | _     |

|                                         |                  | Reset                     | -                    | 200                   | _                     | mW    | _     |

|                                         |                  | Standby                   | -                    | 16                    | 44                    | mW    | _     |

| Total Device Power                      | P <sub>3D3</sub> | 10/20bit HD               | _                    | 430                   | 530                   | mW    | _     |

| $(IO_VDD = 3.3V)$                       |                  | 10/20bit SD               | _                    | 290                   | 370                   | mW    | -     |

|                                         |                  | DVB_ASI                   | _                    | 290                   | 370                   | mW    | -     |

|                                         |                  | Reset                     | _                    | 220                   | _                     | mW    | _     |

|                                         |                  | Standby                   | -                    | 16                    | 44                    | mW    | _     |

| Digital I/O                             |                  |                           |                      |                       |                       |       |       |

| Input Logic LOW                         | V <sub>IL</sub>  | 3.3V or 1.8V operation    | IO_VSS<br>-0.3       | -                     | 0.3 x<br>IO_VDD       | V     | -     |

| Input Logic HIGH                        | V <sub>IH</sub>  | 3.3V or 1.8V operation    | 0.7 x<br>IO_VDD      | -                     | IO_VDD<br>+0.3        | V     | _     |

| Output Logic LOW                        | V                | IOL = 5mA, 1.8V operation | =                    | -                     | 0.2                   | V     | _     |

| Output Logic LOW                        | $V_{OL}$         | IOL = 8mA, 3.3V operation | -                    | -                     | 0.4                   | V     | _     |

| Output Logic IIICII                     | V                | IOH = 5mA, 1.8V operation | 1.4                  | -                     | -                     | V     | -     |

| Output Logic HIGH                       | V <sub>OH</sub>  | IOH = 8mA, 3.3V operation | 2.4                  | -                     | _                     | V     |       |

| Serial Input                            |                  |                           |                      |                       |                       |       |       |

| Serial Input Common<br>Mode Voltage     | -                | 50 $\Omega$ load          | 2.5                  | SDI_VDD<br>-(0.75/2)  | SDI_VDD<br>-(0.55/2)  | V     | -     |

| Serial Output                           |                  |                           |                      |                       |                       |       |       |

| Serial Output<br>Common Mode<br>Voltage | -                | 50Ω load                  | BUFF_VDD<br>-(0.6/2) | BUFF_VDD<br>-(0.45/2) | BUFF_VDD<br>-(0.35/2) | V     | -     |

### **Table 2-3:DC Electrical Characteristics (Continued)**

Guaranteed over recommended operating conditions unless otherwise noted.

| Parameter Symbol Conditions | Min | Тур | Max | Units | Notes |

|-----------------------------|-----|-----|-----|-------|-------|

|-----------------------------|-----|-----|-----|-------|-------|

Notes:

The output drive strength of the digital outputs can be programmed through the host interface. please see Table 4-28: Video Core Configuration and Status Registers, register 06Dh for details.

# 2.4 AC Electrical Characteristics

**Table 2-4:AC Electrical Characteristics**

| Parameter                                       | Symbol             | Conditions |      | Min  | Тур | Max   | Units | Notes |

|-------------------------------------------------|--------------------|------------|------|------|-----|-------|-------|-------|

| System                                          |                    |            |      |      |     |       |       |       |

| Device Latency:                                 |                    | HD         |      | 79   | _   | 83    | PCLK  | _     |

| AUDIO_EN = 1,<br>SMPTE mode,<br>IOPROC_EN = 1   | -                  | SD         | SD   |      | -   | 59    | PCLK  | _     |

| Device Latency:                                 |                    | HD         |      | 44   | _   | 48    | PCLK  | -     |

| AUDIO_EN = 0,<br>SMPTE mode,<br>IOPROC_EN = 1   | -                  | SD         |      | 44   | _   | 48    | PCLK  | -     |

| Device Latency:                                 |                    | HD         |      | 33   | _   | 36    | PCLK  | _     |

| AUDIO_EN = 0,<br>SMPTE mode,<br>IOPROC_EN = 0   | -                  | SD         |      | 32   | _   | 35    | PCLK  | -     |

| Device Latency:                                 |                    | HD         |      | 6    | -   | 9     | PCLK  | _     |

| AUDIO_EN = 0,<br>SMPTE bypass,<br>IOPROC_EN = 0 | -                  | SD         |      | 5    | -   | 9     | PCLK  | -     |