Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### GS2974A HD-LINX™ III Adaptive Cable Equalizer

#### **Features**

- SMPTE 424M, SMPTE 292M and SMPTE 259M compliant

- Automatic cable equalization

- 0.3UI Maximum Output Jitter at 2.97Gb/s

- Multi-standard operation from 143Mb/s to 2.97Gb/s

- Supports DVB-ASI at 270Mb/s

- Small footprint (4mm x 4mm)

- Pb-free and RoHS compliant

- Manual bypass (useful for low data rates with slow rise/fall times)

- Performance optimized for 1.485Gb/s and 2.97Gb/s

- Typical equalized length of Belden 1694A cable: 120m at 2.97Gb/s, 200m at 1.485Gb/s, and 350m at 270Mb/s

- $50\Omega$  differential output (internal  $50\Omega$  pull-ups)

- Programmable mute based on max cable length adjust

- Single 3.3V power supply operation

- Operating temperature range: 0°C to +70°C

#### **Applications**

SMPTE 424M, SMPTE 292M and SMPTE 259M Coaxial Cable Serial Digital Interfaces.

#### **Description**

The GS2974A is a high-speed BiCMOS integrated circuit designed to equalize and restore signals received over 75 $\Omega$ co-axial cable.

The GS2974A is designed to support SMPTE 424M, SMPTE 292M and SMPTE 259M, and is optimized for performance at 1.485Gb/s and 2.97Gb/s.

The GS2974A features DC restoration to compensate for the DC content of SMPTE pathological test patterns.

A voltage programmable mute threshold (MCLADJ), applicable for SD mode (refer to Section 4.3), is included to allow muting of the GS2974A output when an approximate selected cable length is reached for SMPTE 259M signals. This feature allows the GS2974A to distinguish between low amplitude SD-SDI signals and noise at the input of the device. The serial digital outputs of the GS2974A may be forced to a mute state by applying a voltage to the MUTE

Power consumption is typically 215mW using a 3.3V power supply. The GS2974A is lead-free, and the encapsulation compound does not contain halogenated flame retardant.

This component and all homogeneous subcomponents are RoHS compliant.

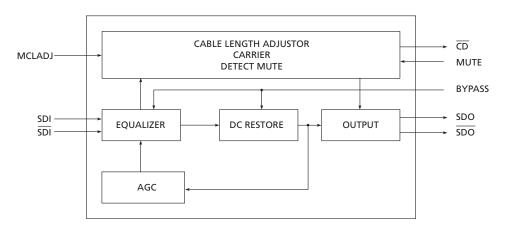

**GS2974A Functional Block Diagram**

# **Revision History**

| Version | ECR    | PCN | Date          | Changes and/or Modifications                                                                                                                                                                                                                                                                                                       |

|---------|--------|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3       | 151331 | -   | January 2009  | Added 2500pc reel size to 6.6 Ordering Information. Changed the Output Voltage Swing from $550 \text{mV}_{\text{p-p}}$ to $600 \text{mV}_{\text{p-p}}$ in Table 2-2: AC Electrical Characteristics.                                                                                                                                |

| 2       | 149719 | -   | April 2008    | Added "0.3UI Maximum Output Jitter at 2.97Gb/s" to Features Section and Table 2-2: AC Electrical Characteristics. Changed cables lengths from 100 to 120 and 400 to 350 in Section 4. Detailed Description. Re-wrote Section 4.3 Programmable Maximum Cable Length Adjust (MCLADJ). Added Tape & Reel to 6.6 Ordering Information. |

| 1       | 145131 | -   | May 2007      | Converted to Data Sheet.                                                                                                                                                                                                                                                                                                           |

| 0       | 144247 | -   | February 2007 | Converted to Preliminary Data Sheet. Removed 'Proprietary and Confidential' footer. Modified DC Electrical Characteristics and AC Electrical Characteristics table. Added section 6.4 Marking Diagram.                                                                                                                             |

| А       | 143102 | -   | December 2006 | New Document.                                                                                                                                                                                                                                                                                                                      |

## **Contents**

| Features                                              | 1  |

|-------------------------------------------------------|----|

| Applications                                          | 1  |

| Description                                           | 1  |

| Revision History                                      | 2  |

| 1. Pin Out                                            | 4  |

| 1.1 GS2974A Pin Assignment                            | 4  |

| 1.2 GS2974A Pin Descriptions                          | 4  |

| 2. Electrical Characteristics                         | 6  |

| 2.1 Absolute Maximum Ratings                          | 6  |

| 2.2 DC Electrical Characteristics                     | 6  |

| 2.3 AC Electrical Characteristics                     | 7  |

| Test Circuit                                          | 8  |

| 3. Input/Output Circuits                              | 8  |

| 4. Detailed Description                               | 9  |

| 4.1 Serial Digital Inputs                             | 9  |

| 4.2 Cable Equalization                                | 10 |

| 4.3 Programmable Maximum Cable Length Adjust (MCLADJ) | 10 |

| 4.4 Mute and Carrier Detect                           | 11 |

| 5. Application Information                            | 12 |

| 5.1 PCB Layout                                        | 12 |

| 5.2 Typical Application Circuit                       | 12 |

| 6. Package & Ordering Information                     | 13 |

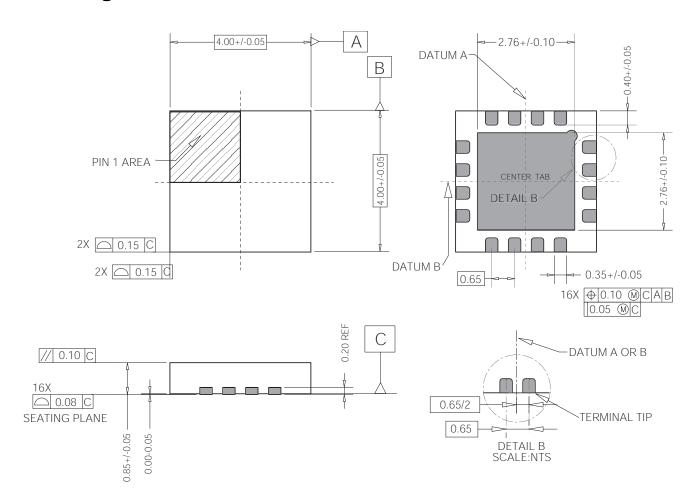

| 6.1 Package Dimensions                                | 13 |

| 6.2 Packaging Data                                    | 13 |

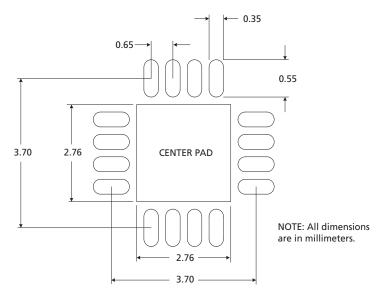

| 6.3 Recommended PCB Footprint                         | 14 |

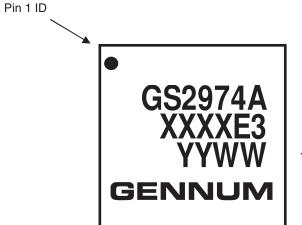

| 6.4 Marking Diagram                                   | 14 |

| 6.5 Solder Reflow Profiles                            | 15 |

| 6.6 Ordering Information                              | 15 |

# 1. Pin Out

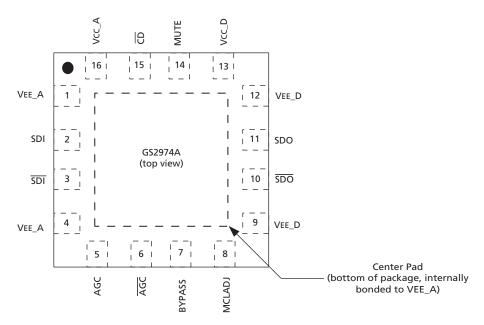

## 1.1 GS2974A Pin Assignment

Figure 1-1: 16-Pin QFN

## 1.2 GS2974A Pin Descriptions

Table 1-1: GS2974A Pin Descriptions

| Pin Number | Name                | Timing             | Туре  | Description                                                                                                                    |

|------------|---------------------|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 1, 4       | VEE_A               | Analog             | Power | Most negative power supply for analog circuitry. Connect to GND.                                                               |

| 2, 3       | SDI, <del>SDI</del> | Analog             | Input | Serial digital differential input.                                                                                             |

| 5, 6       | AGC, <del>AGC</del> | Analog             | -     | External AGC capacitor.  Connect pin 5 and pin 6 together as shown in the Typical Application Circuit on page 12.              |

| 7          | BYPASS              | Not<br>Synchronous | Input | Forces the Equalizing and DC RESTORE stages into bypass mode when HIGH. No equalization occurs in this mode.                   |

| 8          | MCLADJ              | Analog             | Input | Maximum cable length adjust. Adjusts the approximate maximum amount of cable to be equalized. See Section 4.3. and Section 4.4 |

| 9          | VEE_D               | Analog             | Power | Most negative power supply for the digital circuitry and output buffer. Connect to GND.                                        |

Table 1-1: GS2974A Pin Descriptions (Continued)

| Pin Number | Name       | Timing             | Туре   | Description                                                                                                                        |

|------------|------------|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------|

| 10, 11     | SDO, SDO   | Analog             | Output | Equalized serial digital differential output.                                                                                      |

| 12         | VEE_D      | Analog             | Power  | Most negative power supply for the digital circuitry and output buffer. Connect to GND.                                            |

| 13         | VCC_D      | Analog             | Power  | Most positive power supply for the digital I/O pins of the device.<br>Connect to +3.3V DC.                                         |

| 14         | MUTE       | Not<br>Synchronous | Input  | CONTROL SIGNAL INPUT levels are LVCMOS/LVTTL compatible. (3.3V Tolerant) Controls output behaviour on SDO and SDO See Section 4.4. |

| 15         | CD         | Not<br>Synchronous | Output | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible. Indicates the presence of a good input signal. See Section 4.4.    |

| 16         | VCC_A      | Analog             | Power  | Most positive power supply for the analog circuitry of the device.<br>Connect to +3.3V DC.                                         |

| _          | Center Pad | _                  | Power  | Internally bonded to VEE_A.                                                                                                        |

# 2. Electrical Characteristics

### 2.1 Absolute Maximum Ratings

| Parameter                       | Value                           |

|---------------------------------|---------------------------------|

| Supply Voltage                  | -0.3V to +3.6 VDC               |

| Input ESD Voltage               | 2kV                             |

| Storage Temperature Range       | -50°C < T <sub>s</sub> < 125°C  |

| Input Voltage Range (any input) | -0.3 to (V <sub>CC</sub> +0.3)V |

| Operating Temperature Range     | 0°C to 70°C                     |

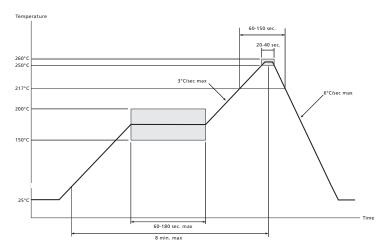

| Solder Reflow Temperature       | 260°C                           |

### 2.2 DC Electrical Characteristics

**Table 2-1: DC Electrical Characteristics**

$V_{CC}$  = 3.3V ±5%,  $T_A$  = 0°C to 70°C, unless otherwise shown

| Parameter                                            | Symbol              | Conditions                | Min   | Тур                                    | Max   | Units | Notes |

|------------------------------------------------------|---------------------|---------------------------|-------|----------------------------------------|-------|-------|-------|

| Supply Voltage                                       | V <sub>CC</sub>     | _                         | 3.135 | 3.3                                    | 3.465 | V     | ±5%   |

| Power Consumption                                    | P <sub>D</sub>      | T <sub>A</sub> = 25°C     | _     | 215                                    | 343   | mW    | _     |

| Supply Current                                       | I <sub>s</sub>      | T <sub>A</sub> = 25°C     | _     | 65                                     | 98    | mA    | _     |

| Output Common Mode<br>Voltage                        | V <sub>CMOUT</sub>  | T <sub>A</sub> = 25°C     | _     | V <sub>CC</sub> - ΔV <sub>SDO</sub> /2 | _     | V     | _     |

| Input Common Mode Voltage                            | V <sub>CMIN</sub>   | T <sub>A</sub> = 25°C     | _     | 1.75                                   | -     | V     | -     |

| MCLADJ DC Voltage (to mute signal)                   | _                   | 0m, T <sub>A</sub> = 25°C | -     | 3.2                                    | _     | V     | _     |

| MCLADJ Range                                         | _                   | T <sub>A</sub> = 25°C     | _     | 0.5                                    | -     | V     | -     |

| CD Output Voltage                                    | V <sub>CD(OH)</sub> | Carrier not present       | 2.4   | -                                      | _     | V     | _     |

|                                                      | V <sub>CD(OL)</sub> | Carrier present           | -     | -                                      | 0.4   | V     | -     |

| Mute Input Voltage Required to Force Outputs to Mute | $V_{Mute}$          | Min to Mute               | 2.0   | -                                      | _     | V     | _     |

| Mute Input Voltage Required to Force Outputs Active  | $V_{Mute}$          | Max to<br>Activate        | -     | -                                      | 0.8   | V     | _     |

### 2.3 AC Electrical Characteristics

**Table 2-2: AC Electrical Characteristics**

$V_{CC}$  = 3.3V ±5%,  $T_A$  = 0°C to 70°C, unless otherwise shown

| Parameter                                          | Symbol                       | Conditions                                                   | Min | Тур  | Max  | Units             | Notes |

|----------------------------------------------------|------------------------------|--------------------------------------------------------------|-----|------|------|-------------------|-------|

| Serial input data rate                             | DR <sub>SDO</sub>            | -                                                            | 143 | _    | 2970 | Mb/s              | _     |

| Input Voltage Swing                                | $\Delta V_{SDI}$             | T <sub>A</sub> =25°C, differential,<br>270Mb/s and 1.485Gb/s | 720 | 800  | 950  | mV <sub>p-p</sub> | 1     |

|                                                    |                              | T <sub>A</sub> =25°C, differential,<br>2.97Gb/s              | 720 | 800  | 880  | mV <sub>p-p</sub> | 1     |

| Output Voltage Swing                               | $\Delta V_{SDO}$             | 100Ω load, T <sub>A</sub> =25°C,<br>differential             | 600 | 750  | 1050 | $mV_{p-p}$        | -     |

| Output Jitter of Various<br>Cable Lengths and Data | -                            | 270Mb/s<br>Belden 1694A: 0-300m                              |     |      | 0.2  | UI                | 2,5   |

| Rates                                              | _                            | 270Mb/s<br>Belden 1694A: 300-350m                            | -   | 0.2  | -    | UI                | 4,5   |

|                                                    | _                            | 1.485Gb/s<br>Belden 1694A: 0-140m                            | -   |      | 0.25 | UI                | 2,5   |

|                                                    | _                            | 1.485Gb/s<br>Belden 1694A: 140-200m                          | -   | 0.3  | -    | UI                | 4,5   |

|                                                    | _                            | 2.97Gb/s<br>Belden 1694A: 0-70m                              | -   | _    | 0.3  | UI                | 2,5   |

|                                                    | _                            | 2.97Gb/s<br>Belden 1694A: 70-120m                            | -   | 0.3  | -    | UI                | 4,5   |

| Output Rise/Fall time                              | _                            | 20% - 80%                                                    | 40  | 80   | 220  | ps                | -     |

| Mismatch in rise/fall time                         |                              | _                                                            | -   | _    | 30   | ps                | _     |

| Duty cycle distortion                              | -                            | _                                                            | _   | _    | 30   | ps                | _     |

| Overshoot                                          | -                            | -                                                            | -   | -    | 10   | %                 | -     |

| Input Return Loss – –                              |                              | -                                                            | 15  | 21   | -    | dB                | 3     |

| Input Resistance                                   | -                            | single ended                                                 | _   | 1.52 | -    | kΩ                | _     |

| Input Capacitance                                  | : Capacitance – single ended |                                                              | _   | 1    | -    | pF                | _     |

| Output Resistance – single ended                   |                              | _                                                            | 50  | -    | Ω    | _                 |       |

#### NOTES:

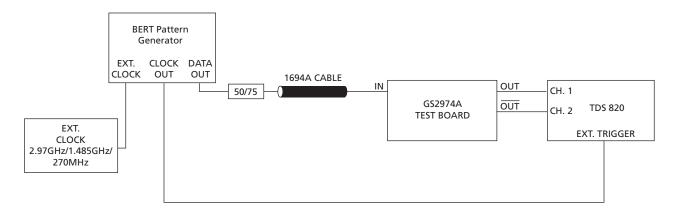

- 1. 0m cable length.

- 2. All parts were production tested. In order to guarantee jitter over the full range of specification ( $V_{CC} = 3.3V \pm 5\%$ ,  $T_A = 0$ °C to 70°C, and 720-880mV launch swing from the SDI cable driver) the recommended applications circuit must be used.

- 3. Tested on CB2974A board from 5MHz to 3GHz.

- 4. Based on characterization data using the recommended applications circuit, at V<sub>CC</sub> = 3.3V, T<sub>A</sub> = 25°C and 800mV launch swing from the SDI cable driver

- 5. Equalizer Pathological test signal was used.

### **Test Circuit**

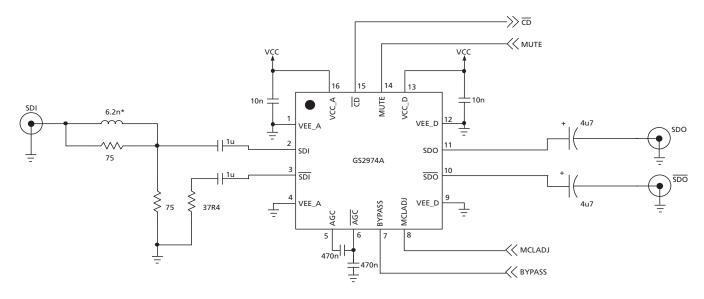

Figure 2-1: Test Circuit

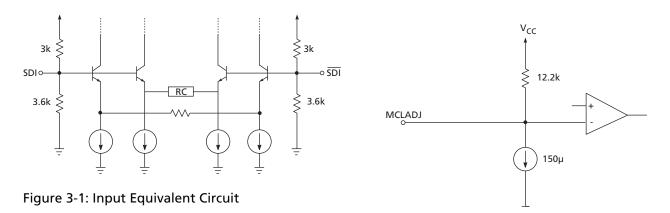

# 3. Input/Output Circuits

Figure 3-2: MCLADJ Equivalent Circuit

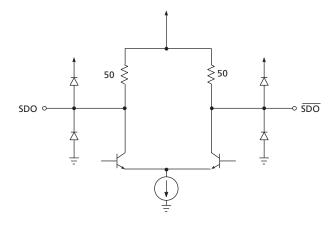

Figure 3-3: Output Circuit

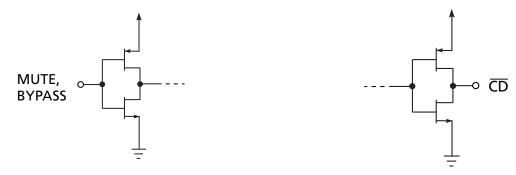

Figure 3-4: MUTE and BYPASS Circuits

Figure 3-5: CD Circuit

# 4. Detailed Description

The GS2974A is a high speed BiCMOS IC designed to equalize serial digital signals.

The GS2974A can equalize both HD and SD serial digital signals, and will typically equalize 120m of Belden 1694A cable at 2.97Gb/s, 200m at 1.485Gb/s and 350m at 270Mb/s.The GS2974A is powered from a single +3.3V power supply and consumes approximately 215mW of power.

## 4.1 Serial Digital Inputs

The serial data signal may be connected to the input pins ( $\overline{SDI}$ ) in either a differential or single-ended configuration. AC-coupling of the inputs is recommended, as the SDI and  $\overline{SDI}$  inputs are internally biased at approximately 1.8V.

### 4.2 Cable Equalization

The input signal passes through a variable gain equalizing stage whose frequency response closely matches the inverse of the cable loss characteristic. In addition, the variation of the frequency response with control voltage imitates the variation of the inverse cable loss characteristic with cable length.

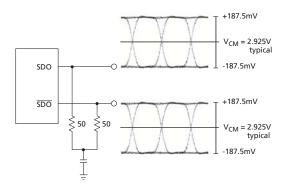

The edge energy of the equalized signal is monitored by a detector circuit which produces an error signal corresponding to the difference between the desired edge energy and the actual edge energy. This error signal is integrated by both an internal and an external AGC filter capacitor providing a steady control voltage for the gain stage. As the frequency response of the gain stage is automatically varied by the application of negative feedback, the edge energy of the equalized signal is kept at a constant level which is representative of the original edge energy at the transmitter. The equalized signal is also DC restored, effectively restoring the logic threshold of the equalized signal to its correct level independent of shifts due to AC coupling. The digital output signals have a nominal voltage of 750mV  $_{\rm pp}$  differential, or 375mV  $_{\rm pp}$  single ended when terminated with 50 $\Omega$  as shown in Figure 4-1.

Figure 4-1: Typical Output Voltage Levels

### 4.3 Programmable Maximum Cable Length Adjust (MCLADJ)

For SMPTE 259M inputs, the GS2974A incorporates a programmable Maximum Cable Length Adjust (MCLADJ) threshold.

This feature can be useful in applications where there are multiple input channels using the GS2974A and the maximum gain can be limited to avoid crosstalk.

The MCLADJ pin acts to change the threshold of the Carrier Detect  $(\overline{CD})$  pin. When the input signal drops below a certain threshold, the  $\overline{CD}$  pin will be driven high, indicating that there is not a valid input signal. In order to enable automatic muting of the output of the GS2974A, the  $\overline{CD}$  pin should be connected directly to the MUTE pin. In applications where programmable maximum cable length adjust is not required, the MCLADJ pin may be left unconnected.

This feature has been designed for use in applications such as routers, where signal crosstalk and circuit noise cause the Equalizer to output erroneous data when no input signal is present. The use of a Carrier Detect function with a fixed internal reference

does not solve this problem, since the signal to noise ratio on the circuit board could be significantly less than the default signal detection level set by the on chip reference.

NOTE: MCLADJ is only recommended for data rates up to 360Mb/s. For data rates above this, MCLADJ should be left floating.

### 4.4 Mute and Carrier Detect

The GS2974A includes a MUTE input pin that allows the application interface to mute the serial digital output at any time. Set the MUTE pin HIGH to mute SDO and SDO. In this case, the outputs will mute regardless of the setting of the BYPASS pin.

A Carrier Detect output pin  $(\overline{CD})$  indicates the presence of a valid signal at the input of the GS2974A. When  $\overline{CD}$  is LOW, the device has detected a valid input on SDI and  $\overline{SDI}$ . When  $\overline{CD}$  is HIGH, the device has not detected a valid input.

NOTE: This pin may be connected directly to the  $\overline{\text{CD}}$  pin to allow mute on loss of carrier.

NOTE:  $\overline{\text{CD}}$  will only detect loss of carrier for data rates greater than 19Mb/s. The  $\overline{\text{CD}}$  output pin may be connected directly to the MUTE input pin to enable automatic muting of the GS2974A when no valid input signal has been detected.

NOTE: If the maximum cable length is exceeded and the device is not in bypass mode the GS2974A will not assert the  $\overline{\text{CD}}$  pin even if a carrier is present.

Table 4-1: Mute Input Table

| Mute | Function                                 |

|------|------------------------------------------|

| 0    | SDO and SDO operate normally             |

| 1    | SDO and SDO are forced to a steady state |

#### **Table 4-2: CD Output Table**

| CD | Input Status                 |

|----|------------------------------|

| 0  | Valid Input on SDI, SDI pins |

| 1  | Input is not valid           |

# 5. Application Information

### **5.1 PCB Layout**

Special attention must be paid to component layout when designing serial digital interfaces for HDTV. An FR-4 dielectric can be used, however, controlled impedance transmission lines are required for PCB traces longer than approximately 1cm. Note the following PCB artwork features used to optimize performance:

- PCB trace width for HD rate signals is closely matched to SMT component width to minimize reflections due to change in trace impedance.

- The PCB ground plane is removed under the GS2974A input components to minimize parasitic capacitance.

- The PCB ground plane is removed under the GS2974A output components to minimize parasitic capacitance.

- High speed traces are curved to minimize impedance changes.

### **5.2 Typical Application Circuit**

NOTE: All resistors in Ohms, capacitors in Farads, and inductors in Henrys, unless otherwise noted.

\* Value dependent on layout

Figure 5-1: GS2974A Typical Application Circuit

# **6. Package & Ordering Information**

# **6.1 Package Dimensions**

### **6.2 Packaging Data**

| Parameter                                                            | Value                |

|----------------------------------------------------------------------|----------------------|

| Package Type                                                         | 4mm x 4mm 16-pin QFN |

| Package Drawing Reference                                            | JEDEC M0220          |

| Moisture Sensitivity Level                                           | 3                    |

| Junction to Case Thermal Resistance, $\theta_{	extstyle{j-c}}$       | 31.0°C/W             |

| Junction to Air Thermal Resistance, $\theta_{j-a}$ (at zero airflow) | 43.8°C/W             |

| Psi, ψ                                                               | 11.0°C/W             |

| Pb-free and RoHS compliant                                           | Yes                  |

## **6.3 Recommended PCB Footprint**

The Center Pad should be connected to the most negative power supply plane for analog circuitry in the device (VEE\_A) by a minimum of five vias.

NOTE: Suggested dimensions only. Final dimensions should conform to customer design rules and process optimizations.

## **6.4 Marking Diagram**

XXXX - Lot/Work Order ID

YYWW - Date Code YY - 2-digit year

WW - 2-digit week number

### **6.5 Solder Reflow Profiles**

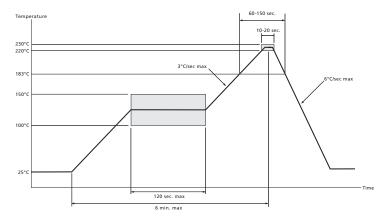

The device is manufactured with Matte-Sn terminations and is compatible with both standard eutectic and Pb-free solder reflow profiles. MSL qualification was performed using the maximum Pb-free reflow profile shown in Figure 6-1. The recommended standard Pb reflow profile is shown in Figure 6-2.

Figure 6-1: Maximum Pb-free Solder Reflow Profile (Preferred)

Figure 6-2: Standard Pb Solder Reflow Profile

## **6.6 Ordering Information**

|         | Part Number   | Package                              | Temperature Range |

|---------|---------------|--------------------------------------|-------------------|

| GS2974A | GS2974ACNE3   | 16-pin QFN                           | 0°C to 70°C       |

| GS2974A | GS2974ACTE3   | 16-pin QFN Tape &<br>Reel (250pcs)   | 0°C to 70°C       |

| GS2974A | GS2974ACNTE3Z | 16-pin QFN Tape &<br>Reel (2,500pcs) | 0°C to 70°C       |

## DOCUMENT IDENTIFICATION DATA SHEET

The product is in production. Gennum reserves the right to make changes to the product at any time without notice to improve reliability, function or design, in order to provide the best product possible.

#### CAUTION

ELECTROSTATIC SENSITIVE DEVICES

DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

#### **GENNUM CORPORATION**

Mailing Address: P.O. Box 489, Station A, Burlington, Ontario L7R 3Y3 Canada Street Addresses: 4281 Harvester Road, Burlington, Ontario L7L 5M4 Canada Phone: +1 (905) 632-2996 Fax: +1 (905) 632-2055 Email: corporate@gennum.com

#### **OTTAWA DESIGN CENTRE**

232 Herzberg Road, Suite 101 Kanata, Ontario K2K 2A1 Canada

Phone: +1 (613) 270-0458 Fax: +1 (613) 270-0429

#### **UNITED KINGDOM DESIGN CENTRE**

North Building, Walden Court

Parsonage Lane,

Bishop's Stortford Hertfordshire, CM23 6DB

**Great Britain**

Phone: +44 (1279) 714170 Fax: +44 (1279) 714171

#### JAPAN KK

Shinjuku Green Tower Building 27F 6-14-1, Nishi Shinjuku Shinjuku-ku, Tokyo, 160-0023

Phone: +81 (03) 3349 5501 Fax: +81 (03) 3349 5505

Email: gennum-japan@gennum.com Web Site: http://www.gennum.co.jp

#### **SNOWBUSH IP - A DIVISION OF GENNUM**

439 University Ave. Suite 1700 Toronto, Ontario M5G 1Y8

Canada

Phone: +1 (416) 925-5643 Fax: +1 (416) 925-0581

Web Site: http://www.snowbush.com

# AGUASCALLIENTES PHYSICAL DESIGN CENTER

Venustiano Carranza 122 Int. 1 Centro, Aguascalientes Mexico CP 20000

Phone: +1 (416) 848-0328

#### **GERMANY**

Niederlassung Deutschland Stefan-George-Ring 29 81929 München, Germany Phone: +49 89 309040 290 Fax: +49 89 309040 293

Email: gennum-germany@gennum.com

#### **UNITED STATES - WESTERN REGION**

Bayshore Plaza 2107 N 1st Street, Suite #300 San Jose, CA 95131 United States

Phone: +1 (408) 392-9430 Fax: +1 (408) 392-9404

#### **UNITED STATES - EASTERN REGION**

4281 Harvester Road Burlington, Ontario L7L 5M4

Canada

Phone: +1 (905) 632-2996 Fax: +1 (905) 632-2055

#### TAIWAN

6F-4, No.51, Sec.2, Keelung Rd. Sinyi District, Taipei City 11502 Taiwan R.O.C.

Phone: (886) 2-8732-8879 Fax: (886) 2-8732-8870

#### **KOREA**

8F, Jinnex Lakeview Bldg. 65-2, Bangidong, Songpagu Seoul, Korea 138-828 Phone: +82-2-414-2991

Fax: +82-2-414-2998

Gennum Corporation assumes no liability for any errors or omissions in this document, or for the use of the circuits or devices described herein. The sale of the circuit or device described herein does not imply any patent license, and Gennum makes no representation that the circuit or device is free from patent infringement.

All other trademarks mentioned are the properties of their respective owners.

GENNUM and the Gennum logo are registered trademarks of Gennum Corporation.

© Copyright 2006 Gennum Corporation. All rights reserved. Printed in Canada.

www.gennum.com