# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### GS1881, GS4881, GS4981 Monolithic Video Sync Separators

#### Features

- noise tolerant odd/even flag, back porch and horizontal sync pulse

- fast recovery from impulse noise

- excellent temperature stability

- 0.5V to 4Vpp input signal amplitude with 5V supply

- well-controlled clamp discharge current and slicing level

- programmable horizontal scan rate (up to 130kHz)

- composite, vertical, back porch, odd/even (GS1881, GS4881), horizontal (GS4981) outputs

- predictable vertical output pulse width with default trigger for non-standard video signals

- Pb-free and Green

- 5V to 12V supply voltage range

- pin compatible with LM1881 sync separator

#### **Application Selection Chart**

| Application                                            | Choose Device: |

|--------------------------------------------------------|----------------|

| Direct LM1881 Replacement with<br>Improved Performance | GS1881         |

| New Applications Substitution for<br>LM1881            | GS4881         |

| New Applications Requiring Horizontal<br>Sync Output   | GS4981         |

#### Description

The GS1881, GS4881 and GS4981 are general purpose sync separators for use in a wide variety of video applications. The devices extract the timing information from composite video signals with scan rates from 15 to 130kHz.

The GS1881 is a drop-in replacement for the industry standard LM1881 with much improved performance. The device generates composite sync, vertical sync, back porch and odd/even field signals. The GS4881 is identical to the GS1881 but features a noise immune back porch pulse which maintains a constant H rate during the vertical interval. The GS4981 is identical to the GS4881, except that it provides horizontal sync in place of the odd/even output.

All three devices feature a self-adjusting windowing circuit for noise immunity, which synchronizes to H rate. This windowing circuit determines the odd or even field in the GS1881 and GS4881, gates the back porch pulse in the GS4881 and GS4981, and generates the horizontal sync output in the GS4981.

The devices feature an improved input stage which ensures that the input signal is sliced at a predictable point due to well-controlled input clamp discharge current and sync slicing level. A missing pulse detector enables the devices to recover quickly from impulse noise disturbances by temporarily increasing the clamp discharge current by roughly ten times. The input stage will operate with signals from 0.5 to 4Vp-p with a 5V supply.

The GS1881, GS4881 and GS4981 also feature a predictable vertical output pulse width with a default trigger for non-standard video signals. All three are available in commercial and industrial temperature ranges and are packaged in both DIP and SOIC.

### **Revision History**

| Version | Date          | Changes and/or Modifications                                                      |

|---------|---------------|-----------------------------------------------------------------------------------|

| 5       | November 2009 | Updated to latest Gennum template and changed from document number 52023 to 6926. |

| 4       | July 2004     | Added lead-free and green information.                                            |

| 3       | -             | Revisions made.                                                                   |

| 2       | -             | Revisions made.                                                                   |

| 1       | March 1991    | New document.                                                                     |

### Contents

| Features                                                                                 | 1  |

|------------------------------------------------------------------------------------------|----|

| Application Selection Chart                                                              | 1  |

| Description                                                                              | 1  |

| Revision History                                                                         | 2  |

| 1. Pin Connections                                                                       | 3  |

| 1.1 Pin Connections                                                                      | 3  |

| 2. Electrical Characteristics                                                            | 4  |

| 2.1 GS1881 Electrical Characteristics                                                    | 4  |

| 2.2 GS4881 Electrical Characteristics                                                    | 5  |

| 2.3 GS4981 Electrical Characteristics                                                    | 6  |

| 2.4 Typical Performance Characteristics                                                  | 8  |

| 3. Temperature Characteristics                                                           |    |

| 4. Circuit Description                                                                   |    |

| 4.1 Composite Video Input (Pin 2) and Composite Sync Output (Pin 1)                      | 14 |

| 4.2 Back Porch Output (Pin 5)                                                            | 15 |

| 4.3 Vertical Sync Output (Pin 3)                                                         |    |

| 4.4 Odd/Even Field Output (Pin 7 GS1881, GS4881)                                         |    |

| 4.5 Horizontal Output (Pin 7 GS4981)                                                     |    |

| 4.6 Block Diagrams                                                                       |    |

| 5. Application Notes                                                                     | 20 |

| 5.1 Choosing the Appropriate Input Capacitor to Optimize Slicing Level and Hum Rejection | 20 |

| 5.2 Filtering                                                                            | 22 |

| 5.3 Deriving Odd/Even Using the GS4981                                                   | 25 |

| 6. Ordering Information                                                                  | 27 |

| 6.1 GS1881 Ordering Information                                                          |    |

| 6.2 GS4881 Ordering Information                                                          |    |

| 6.3 GS4981 Ordering Information                                                          |    |

|                                                                                          |    |

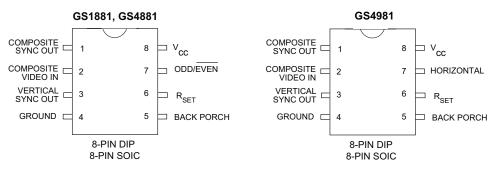

## **1. Pin Connections**

## **1.1 Pin Connections**

Figure 1-1: 8-Pin DIP, 8-Pin SOIC

## 2. Electrical Characteristics

#### 2.1 GS1881 Electrical Characteristics

Table 2-1 shows the electrical characteristics of the GS1881 where conditions are $V_{CC} = 5V$ ,  $R_{SET} = 680 k \Omega$ ,  $T_A = 25^{\circ}$ C, unless otherwise shown.

#### Table 2-1: GS1881 Electrical Characteristics

| Parameter                           | Conditions                         |                         | Min   | Тур   | Max   | Units |

|-------------------------------------|------------------------------------|-------------------------|-------|-------|-------|-------|

| Supply Voltage                      | -                                  |                         | 4.5   | 5     | 13.2  | V     |

| Supply Current                      | Outputs at                         | V <sub>CC</sub> = 5V    | -     | 4.6   | 30    | mA    |

|                                     | Logic 1 –                          | V <sub>CC</sub> = 12V   | _     | 5.0   | 6.5   | mA    |

| Video Input (Pin 2)                 |                                    |                         |       |       |       |       |

| (a) Signal Level                    | V <sub>CC</sub> = 5V               |                         | 0.5   | -     | 4     | Vp-p  |

| (b) Clamp Current                   | Charge                             |                         | 500   | 650   | 850   | μA    |

|                                     | Discharge - nor                    | mal                     | 9     | 11    | 13    | μA    |

|                                     | Discharge - Nos                    | sync flag raised        | 65    | 95    | 115   | μA    |

| (c) Delay to raising of Nosync flag | Video input held high              |                         | 64    | 95    | 130   | μs    |

| (d) Sync Tip Clamp Voltage          |                                    |                         | -     | 1.55  | -     | V     |

| Sync Slice Level                    | Relative to sync tip clamp voltage |                         | 70    | 77    | 84    | mV    |

| RSET Pin Reference Voltage (Pin 6)  | See Note 1.                        |                         | 1.14  | 1.24  | 1.34  | V     |

| Composite Sync Out (Pin 1)          | See Note 2.                        |                         | 40    | 60    | 80    | ns    |

| Delay from Video                    | C <sub>L</sub> = 15p               |                         |       |       |       |       |

| Back Porch Pulse Out (Pin 5)        |                                    |                         |       |       |       |       |

| (a) Delay from Rising Edge of Sync  | C <sub>L</sub> = 15p               |                         | 400   | 500   | 650   | ns    |

| (b) Pulse Width                     |                                    | _                       | 2.0   | 2.5   | 3.2   | μs    |

| Vertical Sync Out (Pin 3)           |                                    |                         |       |       |       |       |

| (a) Pulse Width                     | Serrations duri                    | ng vertical interval    | 197.7 | 197.7 | 197.7 | μs    |

| (b) Default Starting Time           | No serrations d                    | uring vertical interval | 48    | 65    | 82    | μs    |

| Horizontal Scan Rate                | Modified R <sub>SET</sub>          |                         | 15    | -     | 130   | kHz   |

| Logic Outputs                       |                                    |                         |       |       |       |       |

| (a) V <sub>OH</sub>                 | I <sub>OH</sub> = 40μA             | $V_{CC} = 5V$           | 4.2   | 4.6   | -     | V     |

|                                     | -                                  | V <sub>CC</sub> = 12V   | 11.2  | 11.6  | -     | V     |

|                                     | I <sub>OH</sub> =                  | V <sub>CC</sub> = 5V    | 2.4   | 3.4   | _     | V     |

|                                     | 1.6mA -                            | V <sub>CC</sub> = 12V   | 9.4   | 10.4  | _     | V     |

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

**Proprietary & Confidential**

#### Table 2-1: GS1881 Electrical Characteristics (Continued)

| Parameter           | Conditions              | Min | Тур | Max | Units |

|---------------------|-------------------------|-----|-----|-----|-------|

| (b) V <sub>OL</sub> | I <sub>OL</sub> = 1.6mA | -   | 0.3 | 0.6 | V     |

NOTES:

1. When placing the  $R_{SET}$  resistor and the 0.1µF decoupling capacitor, careful attention should be made to ensure that they are as close as possible to Pin 6. Care should also be taken to avoid parasitic capacitive coupling from any output pin (Pins 1, 3, 5 and 7) to Pin 6.

Measured from slicing point of input falling edge to 50% point of composite sync falling edge.

#### 2.2 GS4881 Electrical Characteristics

Table 2-2 shows the electrical characteristics of the GS4881 where conditions are $V_{CC}$  = 5V,  $R_{SET}$  = 680k $\Omega$ ,  $T_A$  =25°C, unless otherwise shown.

| Parameter                           | Conditions            |                                    | Min   | Тур   | Мах   | Units |

|-------------------------------------|-----------------------|------------------------------------|-------|-------|-------|-------|

| Supply Voltage                      | _                     |                                    | 4.5   | 5     | 13.2  | V     |

| Supply Current                      | Outputs at            | V <sub>CC</sub> = 5V               | -     | 4.6   | 30    | mA    |

|                                     | Logic 1 –             | V <sub>CC</sub> = 12V              | -     | 5.0   | 6.5   | mA    |

| Video Input (Pin 2)                 |                       |                                    |       |       |       |       |

| (a) Signal Level                    | V <sub>CC</sub> = 5V  |                                    | 0.5   | -     | 4     | Vp-p  |

| (b) Clamp Current                   | Charge                |                                    | 500   | 650   | 850   | μA    |

|                                     | Discharge - nor       | mal                                | 9     | 11    | 13    | μA    |

|                                     | Discharge - Nos       | ync flag raised                    | 65    | 95    | 115   | μA    |

| (c) Delay to raising of Nosync flag | Video input held high |                                    | 64    | 95    | 130   | μs    |

| (d) Sync Tip Clamp Voltage          | _                     |                                    | -     | 1.55  | -     | V     |

| Sync Slice Level                    | Relative to sync      | Relative to sync tip clamp voltage |       | 77    | 84    | mV    |

| RSET Pin Reference Voltage (Pin 6)  | See Note 1.           |                                    | 1.14  | 1.24  | 1.34  | V     |

| Composite Sync Out (Pin 1)          | See Note 2.           |                                    | 40    | 60    | 80    | ns    |

| Delay from Video                    | C <sub>L</sub> = 15p  |                                    |       |       |       |       |

| Back Porch Pulse Out (Pin 5)        |                       |                                    |       |       |       |       |

| (a) Delay from Rising Edge of Sync  | C <sub>L</sub> = 15p  |                                    | 400   | 500   | 650   | ns    |

| (b) Pulse Width                     |                       | -                                  | 2.0   | 2.5   | 3.2   | μs    |

| (c) Occurrence Rate                 |                       | -                                  | Н     | Н     | Н     | _     |

| Vertical Sync Out (Pin 3)           |                       |                                    |       |       |       |       |

| (a) Pulse Width                     | Serrations durir      | ng vertical interval               | 197.7 | 197.7 | 197.7 | μs    |

| (b) Default Starting Time           | No serrations de      | uring vertical interval            | 48    | 65    | 82    | μs    |

#### Table 2-2: GS4881 Electrical Characteristics

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

| Parameter            | Cor                       | Conditions            |      | Тур  | Мах | Units |

|----------------------|---------------------------|-----------------------|------|------|-----|-------|

| Horizontal Scan Rate | Modified R <sub>SET</sub> |                       | 15   | _    | 130 | kHz   |

| Logic Outputs        |                           |                       |      |      |     |       |

| (a) V <sub>OH</sub>  | Ι <sub>OH</sub> = 40μΑ    | $V_{CC} = 5V$         | 4.2  | 4.6  | -   | V     |

|                      | _                         | V <sub>CC</sub> = 12V | 11.2 | 11.6 | -   | V     |

|                      | I <sub>OH</sub> =         | $V_{CC} = 5V$         | 2.4  | 3.4  | -   | V     |

| 1.6mA —              | V <sub>CC</sub> = 12V     | 9.4                   | 10.4 | -    | V   |       |

| (b) V <sub>OL</sub>  | I <sub>OL</sub> = 1.6mA   |                       | -    | 0.3  | 0.6 | V     |

#### NOTES:

1. When placing the  $R_{SET}$  resistor and the 0.1 $\mu$ F decoupling capacitor, careful attention should be made to ensure that they are as close as

possible to Pin 6. Care should also be taken to avoid parasitic capacitive coupling from any output pin (Pins 1, 3, 5 and 7) to Pin 6.

2. Measured from slicing point of input falling edge to 50% point of composite sync falling edge.

#### 2.3 GS4981 Electrical Characteristics

Table 2-2 shows the electrical characteristics of the GS4981 where conditions are $V_{CC}$  = 5V,  $R_{SET}$  = 680k $\Omega$ ,  $T_A$  =25°C, unless otherwise shown.

| lable 2-3: GS498   Electrical Characterist | 2-3: GS4981 Electrical Character | ristics |

|--------------------------------------------|----------------------------------|---------|

|--------------------------------------------|----------------------------------|---------|

| Parameter                           | Conditions<br>-                    |                       | Min  | Тур  | Max  | Units |

|-------------------------------------|------------------------------------|-----------------------|------|------|------|-------|

| Supply Voltage                      |                                    |                       | 4.5  | 5    | 13.2 | V     |

| Supply Current                      | Outputs at                         | V <sub>CC</sub> = 5V  | -    | 4.6  | 30   | mA    |

|                                     | Logic 1 –                          | V <sub>CC</sub> = 12V | -    | 5.0  | 6.5  | mA    |

| Video Input (Pin 2)                 |                                    |                       |      |      |      |       |

| (a) Signal Level                    | $V_{CC} = 5V$                      |                       | 0.5  | -    | 4    | Vp-р  |

| (b) Clamp Current                   | Charge                             |                       | 500  | 650  | 850  | μA    |

|                                     | Discharge - normal                 |                       | 9    | 11   | 13   | μA    |

|                                     | Discharge - Nosync flag raised     |                       | 65   | 95   | 115  | μA    |

| (c) Delay to raising of Nosync flag | Video input held high              |                       | 64   | 95   | 130  | μs    |

| (d) Sync Tip Clamp Voltage          |                                    |                       | -    | 1.55 | -    | V     |

| Sync Slice Level                    | Relative to sync tip clamp voltage |                       | 70   | 77   | 84   | mV    |

| RSET Pin Reference Voltage (Pin 6)  | See Note 1.                        |                       | 1.14 | 1.24 | 1.34 | V     |

| Composite Sync Out (Pin 1)          | See Note 2.                        |                       | 40   | 60   | 80   | ns    |

| Delay from Video                    | C <sub>L</sub> = 15p               |                       |      |      |      |       |

Back Porch Pulse Out (Pin 5)

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

6 of 29

**Proprietary & Confidential**

| Parameter                          | Con                                    | ditions               | Min   | Тур   | Мах   | Units |

|------------------------------------|----------------------------------------|-----------------------|-------|-------|-------|-------|

| (a) Delay from Rising Edge of Sync | C <sub>L</sub> = 15p                   |                       | 400   | 500   | 650   | ns    |

| (b) Pulse Width                    |                                        | -                     | 2.0   | 2.5   | 3.2   | μs    |

| (c) Occurrence Rate                |                                        | -                     | Н     | Н     | Н     | _     |

| Vertical Sync Out (Pin 3)          |                                        |                       |       |       |       |       |

| (a) Pulse Width                    | Serrations during                      | g vertical interval   | 197.7 | 197.7 | 197.7 | μs    |

| (b) Default Starting Time          | No serrations during vertical interval |                       | 48    | 65    | 82    | μs    |

| Horizontal Sync Out (Pin 7)        |                                        |                       |       |       |       |       |

| (a) Delay From Video               | C <sub>L</sub> = 15p                   | -                     | 90    | 190   | 290   | ns    |

| (b) Pulse Width                    |                                        | -                     | 5.0   | 7.0   | 9.0   | μs    |

| Horizontal Scan Rate               | Modified R <sub>SET</sub>              |                       | 15    | _     | 130   | kHz   |

| Logic Outputs                      |                                        |                       |       |       |       |       |

| (a) V <sub>OH</sub>                | I <sub>OH</sub> = 40μA                 | V <sub>CC</sub> = 5V  | 4.2   | 4.6   | -     | V     |

|                                    | _                                      | V <sub>CC</sub> = 12V | 11.2  | 11.6  | -     | V     |

|                                    | I <sub>OH</sub> =<br>1.6mA             | V <sub>CC</sub> = 5V  | 2.4   | 3.4   | -     | V     |

|                                    | See Note 3.                            | V <sub>CC</sub> = 12V | 9.4   | 10.4  | -     | V     |

| (b) V <sub>OL</sub>                | I <sub>OL</sub> = 1.6mA                |                       | _     | 0.3   | 0.6   | V     |

NOTES:

1. When placing the R<sub>SET</sub> resistor and the 0.1µF decoupling capacitor, careful attention should be made to ensure that they are as close as possible to Pin 6. Care should also be taken to avoid parasitic capacitive coupling from any output pin (Pins 1, 3, 5 and 7) to Pin 6.

2. Measured from slicing point of input falling edge to 50% point of composite sync falling edge.

3. Applies only to composite sync, vertical sync, and back porch outputs. Horizontal sync has a passive  $10k\Omega$  pull-up to V<sub>CC</sub>.

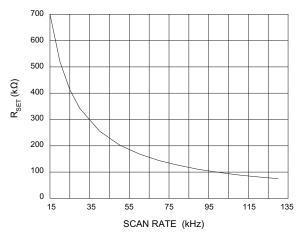

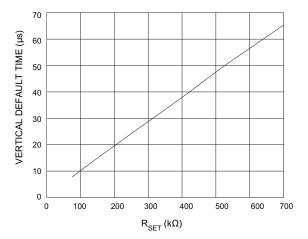

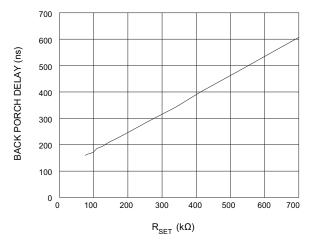

## **2.4 Typical Performance Characteristics**

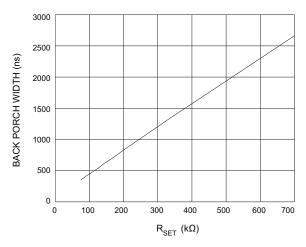

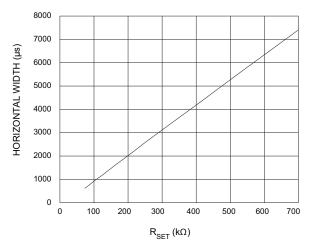

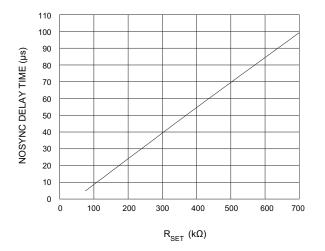

Figure 2-1 through Figure 2-6 show the typical performance characteristics for the GS1881, GS4881, and GS4981, where  $V_S = 5V$ ,  $T_A = 25$ °C, unless otherwise specified.

Figure 2-1: R<sub>SET</sub> vs Scan Rate

Figure 2-2: Vertical Sync Default Starting Time vs R<sub>SET</sub>

Figure 2-3: Back Porch Delay vs R<sub>SET</sub>

Figure 2-4: Back Porch Width vs R<sub>SET</sub>

Figure 2-5: Horizontal Width vs R<sub>SET</sub>

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

Figure 2-6: Nosync Delay Time vs  $\mathsf{R}_{\mathsf{SET}}$

## **3. Temperature Characteristics**

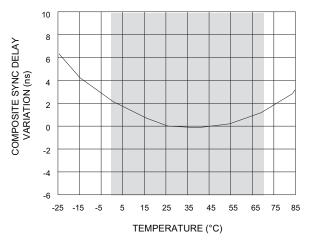

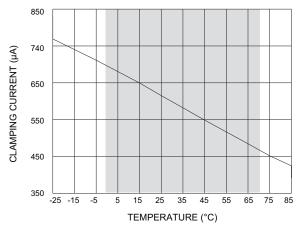

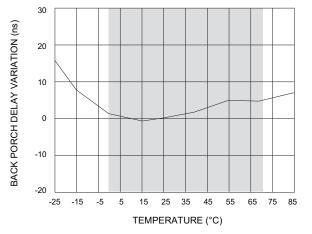

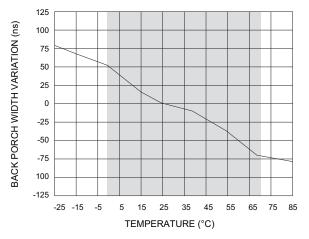

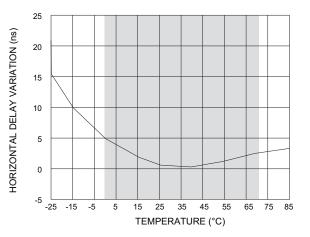

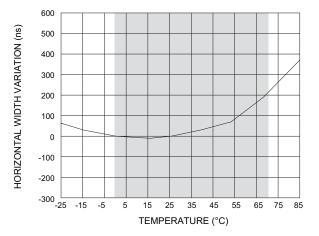

Figure 3-1 through Figure 3-6 show the typical temperature characteristics for the GS1881, GS4881, and GS4981, where  $V_S = 5V$ ,  $R_{SET} = 680$ k $\Omega$  unless otherwise specified.

NOTE: Grey shading on Figure 3-1 through Figure 3-6 indicates commercial temperature range (0 to 70°C).

Figure 3-1: Composite Sync Delay Variation vs Temperature

Figure 3-2: Clamping Current vs Temperature

Figure 3-3: Back Porch Delay Variation vs Temperature

Figure 3-4: Back Porch Width Variation vs Temperature

Figure 3-5: Horizontal Delay Variation vs Temperature

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

Figure 3-6: Horizontal Width Variation vs Temperature

## 4. Circuit Description

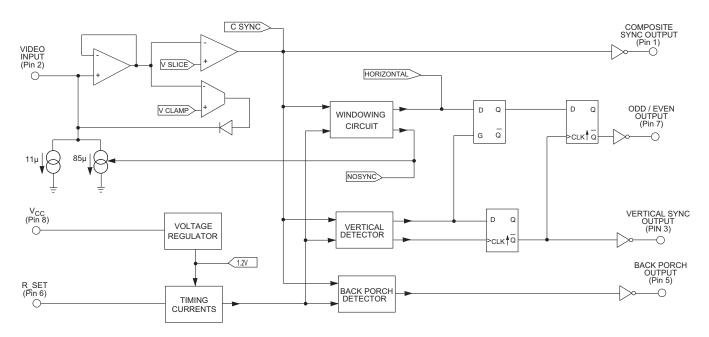

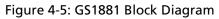

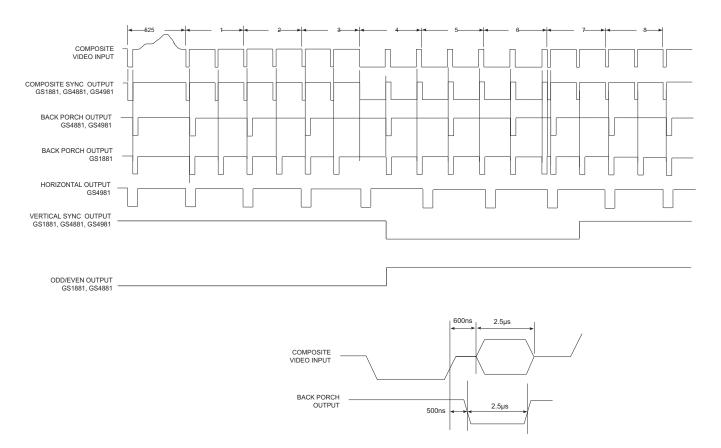

The block diagrams for the GS1881, GS4881 and GS4981, are shown in Figure 4-5 through Figure 4-7, with timing diagrams for the devices shown in Figure 4-8.

When stimulated by a composite input signal, the GS1881 and GS4881 sync separators output composite sync, vertical sync, back porch, and odd/even field information. The GS4981 substitutes the odd/even output of the GS4881 with a horizontal output. An external resistor on Pin 6 is used to define internal currents allowing the devices to accommodate horizontal scan rates from 15kHz to 130kHz.

#### 4.1 Composite Video Input (Pin 2) and Composite Sync Output (Pin 1)

Composite video is AC coupled via an external coupling capacitor to Pin 2. The device clamps the sync tip of the input video to 1.5V ( $V_{clamp}$ ) and then slices at 77mV above the clamp voltage ( $V_{slice}$ ). The resultant signal, provided at Pin 1, is a reproduction of the input signal with the active video portion removed. As  $V_{clamp}$  and  $V_{slice}$  are supply and input signal independent, for 0.5Vp-p signals (sync height of 143mV) slicing will occur at just above the 50% point and for 2Vp-p signals (sync height of 572mV) slicing will occur at approximately 13% of sync height.

The video signal path and composite sync slicing circuitry have been optimized and compensated to achieve a low propagation delay that is stable over temperature. The typical delay is 60ns with less than 3ns drift over the commercial temperature range.

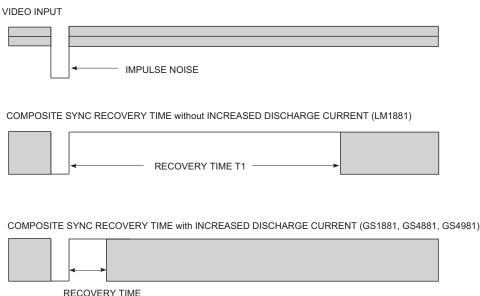

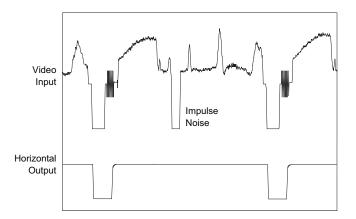

The typical input clamp discharge current is  $11\mu$ A. This current is optimal under normal operating circumstances but needs to be increased when the clamp is trying to recover from negative going impulse noise. The device improves the recovery time by raising a NOSYNC flag when there has not been a sync pulse for approximately 1 1/2 horizontal lines.

When this flag is raised the discharge current is increased by  $85\mu A$  so that the recovery time is sped up by nearly 10 times. Figure 4-1 shows a comparison between the recovery times with and without the increased discharge current.

COVERY TIM T1 / 10

Figure 4-1: Impulse Noise: Recovery Time Comparison

### 4.2 Back Porch Output (Pin 5)

In an NTSC composite video signal, horizontal sync pulses are followed by the back porch interval. The device generates a negative going pulse on Pin 5 during this time. It is delayed typically 500ns from the rising edge of sync and has a typical width of 2.5 $\mu$ s. Both of these times are set by the external R<sub>SET</sub> resistor.

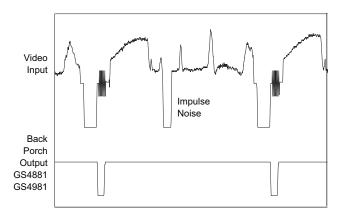

During the pre-equalizing, vertical sync, and post-equalizing periods, composite sync doubles in frequency. The GS4881 and GS4981 maintain the back porch output at the horizontal rate due to Back Porch Enable (BPEN), generated by the internal windowing circuit, which forces back porch to be asserted at the horizontal rate. This gating circuit is also the reason for the excellent impulse noise immunity of the back porch output as shown in Figure 4-2.

Figure 4-2: Back Porch Noise Immunity

The GS1881 does not gate the Back Porch which allows for total pin compatibility with the LM1881.

#### 4.3 Vertical Sync Output (Pin 3)

The vertical sync interval is detected by integrating the composite sync pulses. The first broad vertical sync pulse causes an internal capacitor to charge past a fixed threshold and raises an internal vertical flag. Once the vertical flag is raised, the positive edge of the next serration clocks out the vertical output. When the vertical sync interval ends, the first post equalizing pulse is unable to charge the capacitor sufficiently, causing the internal vertical flag to go high. The rising edge of the second post-equalizing pulse then clocks out the high flag to end the vertical sync pulse. The vertical output is clocked in and out and therefore is a fixed width of  $197.7\mu$ s ( $3H + 4.7\mu$ s +  $2.3\mu$ s). In the case of a non-standard vertical interval that has no serrations, a second internal capacitor is charged and clocks the vertical pulse out after typically 65 $\mu$ s. In this case the end of the vertical pulse will still be the rising edge of the second post-equalizing pulse. As the vertical detector is designed as a true integrator, it provides improved noise immunity.

## 4.4 Odd/Even Field Output (Pin 7 GS1881, GS4881)

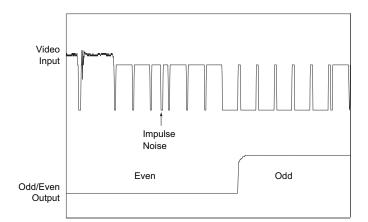

NTSC PAL and SECAM composite video standards are interlaced video schemes and therefore have odd and even fields. For odd fields the first broad vertical sync pulse is coincident with the start of horizontal, while for even fields the first broad vertical sync pulse starts in the middle of a horizontal line. Therefore by comparing the vertical sync with an internally generated horizontal sync the odd/even field information is determined. This output is clocked out by the falling edge of vertical sync. The odd/even output is low during even fields and high during odd fields. This method of detecting odd and even fields is very noise tolerant.

Noise during the pre-equalizing pulses does not affect the output since the field decision is made at the beginning of the vertical interval. This noise immunity is displayed in Figure 4-3 in which an extra pre-equalizing pulse has been added to the video input with no negative effect on the odd/even field information.

#### Figure 4-3: Odd/Even Output

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

### 4.5 Horizontal Output (Pin 7 GS4981)

As mentioned above, the odd/even field output of the GS1881 and GS4881 is generated by comparing vertical sync with an internal horizontal sync signal. This horizontal sync signal is a true horizontal signal (i.e. maintained during the vertical interval) and is outputted on Pin 7 for the GS4981. A delay of 190ns from the video input and a width of  $6.5\mu$ s are typically characteristics for this signal. The windowing circuit which generates horizontal provides excellent impulse noise immunity as shown in Figure 4-4. This output buffer is an open collector stage with an internal 10k $\Omega$ pull up resistor.

Figure 4-4: Horizontal Output

### 4.6 Block Diagrams

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

Figure 4-6: GS4881 Block Diagram

Figure 4-7: GS4981 Block Diagram

Figure 4-8: GS1881, GS4881, GS4981 Video Sync Separator Timing Diagram

## **5. Application Notes**

#### 5.1 Choosing the Appropriate Input Capacitor to Optimize Slicing Level and Hum Rejection

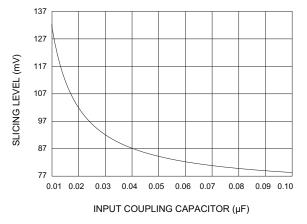

The video designer can adjust the slicing level by choosing the value of the input coupling capacitor. The relationship between slicing level and input coupling capacitor is described by the following equation:

$$\Delta V_{SLICE} = \frac{I_{DIS}}{C_C} \Delta T = V_{DROOP}$$

where:  $I_{DIS}$  = clamp discharge current = 11  $\mu$ A  $\Delta T$  =  $T_{LINE}$  -  $T_{SYNC}$  = (63.5  $\mu$ s - 4.7  $\mu$ s)

$C_{c}$  = input coupling capacitor

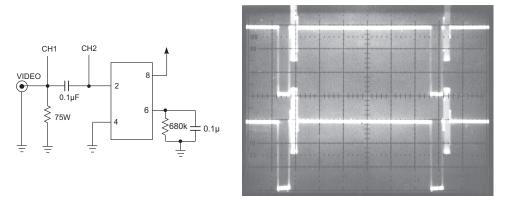

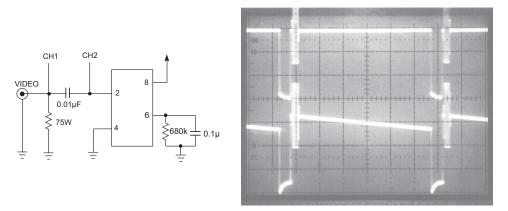

Figure 5-1 is a graphical representation of this equation and Figure 5-2 and Figure 5-3 show the input video waveforms for  $0.1\mu$ F and  $0.01\mu$ F input capacitors respectively. The advantage in choosing a smaller input coupling capacitor, is increased hum rejection as the following analyses illustrates.

Figure 5-1: Slicing Level vs Input Coupling Capacitor

Figure 5-2: Test Circuit 1 and Video Waveforms for 0.1µF

Figure 5-3: Test Circuit 2 and Video Waveforms for  $0.01 \mu F$

The interfering hum component is defined by:

$$v_{HUM}(t) = V_P \cos(2\pi f_{HUM}t)$$

where:  $V_P$  = Peak voltage of AC hum

$f_{HUM}$  = Frequency of hum (50Hz or 60Hz)

The maximum rate of change of this hum signal occurs at the zero crossing points and is:

$$\frac{dv_{HUM}}{dt} \bigg|_{t = \frac{\pi}{2}, \frac{3\pi}{2}} = \pm V_{p} 2\pi f_{HUM}$$

Since the horizontal scan period is much faster than the period of the interference (63.5ms <<  $1/f_{HUM}$ ) a good approximation is to assume that the maximum line to line voltage change resulting from the interfering hum is:

$$\Delta V_{HUM} = \pm V_P 2\pi f_{HUM} T_{LINE}$$

where:  $T_{LINE} = 63.5 \mu s$

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

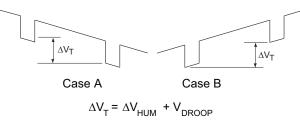

The total line to line voltage change ( $\Delta V_T$ ) can then be calculated by adding the hum component ( $\Delta V_{HUM}$ ) and the droop component ( $V_{DROOP}$ ). This calculation results in two cases:

To correct for  $\Delta V_T$  in case A, the input stage must be able to charge the input capacitor  $\Delta V_T$  volts in 4.7µs. This is not a constraint as the typical clamping current of 650µA can accomplish this for practical values of coupling capacitor.

The only way to compensate for  $\Delta V_T$  in case B is to make  $V_{DROOP} > \Delta V_{HUM}$ .  $V_{DROOP}$  is increased by decreasing the input coupling capacitor value. Therefore the video designer can increase hum rejection by decreasing the value of this capacitor. The following is a numerical example:

choosing C<sub>c</sub> =

$$0.022\mu$$

F

$$\therefore V_{\text{DROOP}} = \frac{11}{0.022} (63.5\mu - 4.7\mu) = 29.4\text{mV}$$

the maximum amount of 60 Hz hum that could be rejected would be when:

$$\Delta V_{\text{DROOP}} = \Delta V_{\text{HUM}} = V_{\text{P}} 2\pi f_{\text{HUM}} T_{\text{LINE}}$$

$$\therefore V_{\text{P}} = \frac{\Delta V_{\text{DROOP}}}{2\pi f_{\text{HUM}} T_{\text{LINE}}} = \frac{29.4\text{mV}}{2\pi (60) (63.5\mu)} = 1.23 V_{\text{PEAK}} \text{HUM}$$

verifying that there is enough clamping current

$$\Delta V_{t} = 29.4 \text{mV} + 29.4 \text{mV} = 58.8 \text{mV}$$

$$\therefore \text{ i } = 0.022 \mu \left(\frac{58.8 \text{mV}}{4.7 \mu}\right) = 275 \mu \text{A}$$

which is less than  $650 \mu A$ .

#### 5.2 Filtering

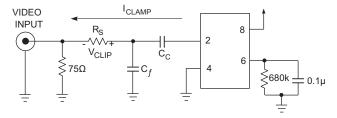

In order to keep the input to output delay small and temperature stable, no chrominance filtering is done within the device. External filtering may be necessary if the input signal contains large chrominance components (less than 77mV from sync tip) or has significant amounts of high frequency noise. This filter can be a simple low pass RC network constructed by a resistance ( $R_S$ ) in series with the source and a capacitor ( $C_f$ ) to ground. A single pole low pass filter having a corner frequency of approximately 500kHz will provide ample bandwidth for passing sync pulses with almost 18dB attenuation at 3.58MHz. Care should be taken in choosing the value of the series resistor in the filter since the source resistance seen by the sync separator affects its performance. See Figure 5-4.

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

As the source resistance rises, the video input sync tip starts to be clipped due to the clamping current during the sync. This clamping current is relatively large due to the non-symmetric duty cycle of video. To a good approximation the amount of sync clamp current can be calculated as follows:

$$(I_{CLAMP_{AVG}}) (T_{SYNC}) = (I_{DIS}) (T_{LINE} - T_{SYNC})$$

$$I_{CLAMP_{AVG}} (4.7 \ \mu s) = (11 \ \mu A) (63.5 \ \mu s - 4.7 \ \mu s)$$

$$\therefore I_{CLAMP_{AVG}} = 137.6 \ \mu A$$

This clamp current flows in the source resistance causing a voltage drop equal to:

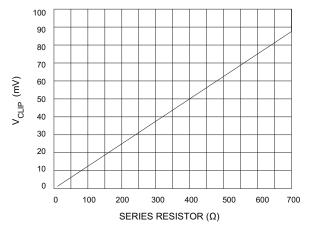

$$V_{CLIP} = (I_{CLAMP_{AVG}}) (R_{S})$$

$$= (137.6\mu) (R_{S})$$

Figure 5-4: Simple Chrominance Filtering

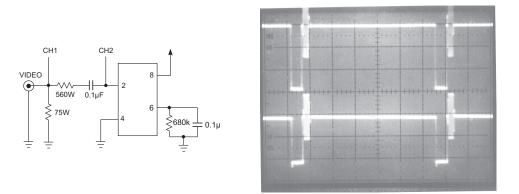

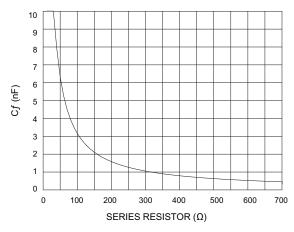

Figure 5-5 shows the amount of sync clipping for a 560 $\Omega$  source resistor. A graph of  $V_{CLIP}$  versus  $R_S$  is shown in Figure 5-6, and Figure 5-7 shows the corresponding capacitor value for a particular series resistor to provide a corner frequency of 500kHz.

In applications where signal levels are small the amount of attenuation should be minimized. It follows from Figure 5-6 and Figure 5-7 that in order to minimize attenuation a small series resistor and a larger capacitor to ground should be chosen. This however, increases the capacitive loading of the signal source.

Figure 5-5: Test Circuit 3 and Sync Clipping for a  $650\Omega$  Source Resistor

Figure 5-6: VCLIP vs Series Resistor

Figure 5-7: Cf vs Series Resistor

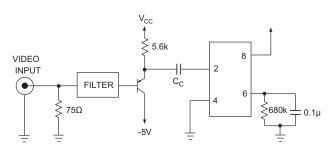

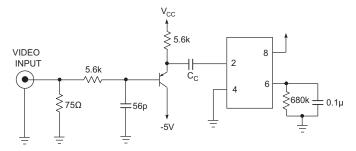

Another way to minimize the amount of attenuation is to control the source resistance seen by the sync separator by using a PNP emitter follower (Figure 5-8). A PNP emitter follower works well to drive the sync separator, and does not require much DC current because the transistor provides the current when it is needed during sync. Figure 5-9 is a typical application circuit that minimizes sync tip clipping.

Figure 5-8: PNP Emitter Follower Buffer

GS1881, GS4881, GS4981 Monolithic Video Sync Separators Data Sheet 6926 - 5 November 2009

Gennum

Figure 5-9: Typical NTSC Application Circuit

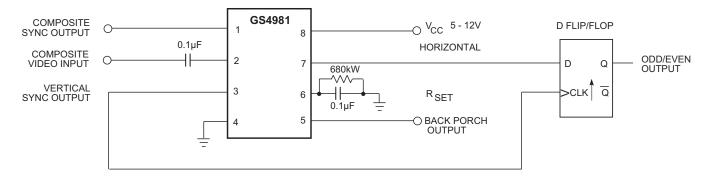

#### 5.3 Deriving Odd/Even Using the GS4981

Odd/even field information can be derived using the vertical and horizontal outputs from the GS4981 along with an external positive edge D flip/flop. The horizontal output is used as the D input and the vertical output as the clock, as shown in Figure 5-10.

At the start of an odd field the vertical output ends in the middle of the horizontal line and a high will be latched. At the start of an even field, the vertical output ends near the beginning of the horizontal line and since the horizontal output is low, a low will be latched. This timing sequence is shown in Figure 5-11.

Figure 5-10: Derivation of Odd/Even with GS4981