Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### GS9090B GenLINX® III 270Mb/s Deserializer for SDI

### **Key Features**

- SMPTE 259M-C compliant descrambling and NRZI to NRZ decoding (with bypass)

- DVB-ASI 8b/10b decoding

- Integrated line-based FIFO for data alignment/delay, clock phase interchange, DVB-ASI data packet extraction and clock rate interchange, and ancillary data packet extraction

- Integrated VCO and reclocker

- User selectable additional processing features including:

- TRS, ANC data checksum, and EDH CRC error detection and correction

- programmable ANC data detection

- illegal code remapping

- Internal flywheel for noise immune H, V, F extraction

- Automatic standards detection and indication

- Enhanced Gennum Serial Peripheral Interface (GSPI)

- JTAG test interface

- Polarity insensitive for DVB-ASI and SMPTE signals

- +1.8V core power supply with optional +1.8V or +3.3V I/O power supply

- Small footprint (8mm x 8mm)

- Low power operation (typically 145mW)

- Pb-free

### **Applications**

- SMPTE 259M-C Serial Digital Interfaces

- **DVB-ASI Serial Digital Interfaces**

### **Description**

The GS9090B is a 270Mb/s reclocking deserializer with an internal FIFO. It provides a complete receive solution for SD-SDI and DVB-ASI applications.

In addition to reclocking and deserializing the input data stream, the GS9090B performs NRZI-to-NRZ decoding, descrambling as per SMPTE 259M-C, and word alignment when operating in SMPTE mode. When operating in DVB-ASI mode, the device will word align the data to K28.5 sync characters and 8b/10b decode the received stream.

The internal reclocker features a very wide input jitter tolerance, and is fully compatible with both SMPTE and DVB-ASI input streams.

The GS9090B includes a range of data processing functions such as EDH support (error detection and handling), and automatic standards detection. The device can also detect and extract SMPTE 352M payload identifier packets and independently identify the received video standard. This information is read from internal registers via the host interface port.

The GS9090B also incorporates a video line-based FIFO. This FIFO may be used in four user-selectable modes to carry out tasks such as data alignment / delay, clock phase interchange, MPEG packet extraction and clock rate interchange, and ancillary data packet extraction.

Parallel data outputs are provided in 10-bit multiplexed format, with the associated parallel clock output signal operating at 27MHz.

The device may also be used in a low-latency data pass through mode where only descrambling and word alignment will be performed in SMPTE mode.

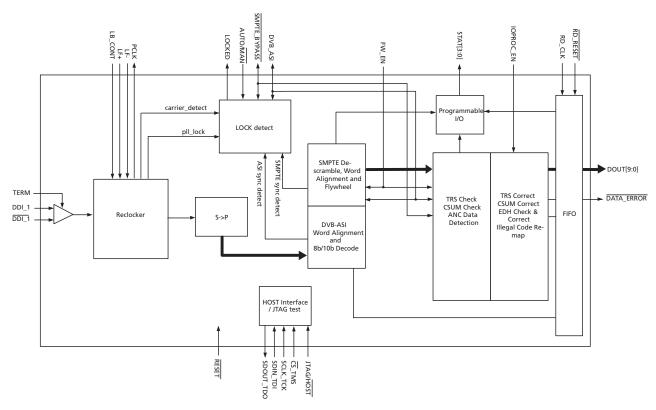

# **Functional Block Diagram**

**GS9090B Functional Block Diagram**

### **Revision History**

| Version | ECR    | PCN   | Date              | Changes and/or Modifications                                                            |

|---------|--------|-------|-------------------|-----------------------------------------------------------------------------------------|

| 5       | 154185 | _     | May 2010          | Converted document back to Data Sheet.                                                  |

| 4       | 152803 | _     | October 2009      | Changed 6.1 Package Dimensions.                                                         |

| 3       | 150198 | 50711 | July 2008         | DVB_ASI operation specification change in Master mode.                                  |

| 2       | 143668 | _     | January 2007      | Added DVB-ASI payload data rate parameter to Table 2-3: AC Electrical Characteristics.  |

| 1       | 143101 | _     | December 2006     | Converting to data sheet. Removed 'Proprietary and Confidential' footer. Added section. |

| 0       | 141913 | -     | September<br>2006 | New Document.                                                                           |

# **Contents**

| Key Features                                             |    |

|----------------------------------------------------------|----|

| Applications                                             | 1  |

| Description                                              | 1  |

| Functional Block Diagram                                 | 2  |

| Revision History                                         | 2  |

| 1. Pin Out                                               | 5  |

| 1.1 Pin Assignment                                       | 5  |

| 2. Electrical Characteristics                            | 12 |

| 2.1 Absolute Maximum Ratings                             | 12 |

| 2.2 DC Characteristics                                   | 12 |

| 2.3 AC Electrical Characteristics                        | 13 |

| 2.4 Solder Reflow Profiles                               |    |

| 2.5 Host Interface Map                                   | 16 |

| 2.5.1 Host Interface Map (R/W registers)                 | 18 |

| 2.5.2 Host Interface Map (Read only registers)           | 20 |

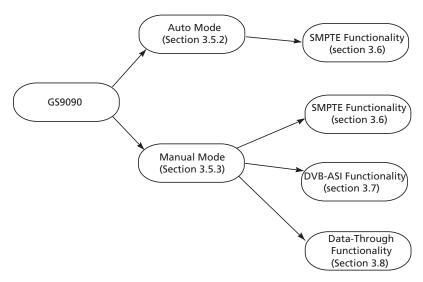

| 3. Detailed Description                                  | 22 |

| 3.1 Functional Overview                                  | 22 |

| 3.2 Serial Digital Input                                 | 22 |

| 3.3 Clock and Data Recovery                              | 23 |

| 3.3.1 Internal VCO and Phase Detector                    |    |

| 3.4 Serial-To-Parallel Conversion                        | 23 |

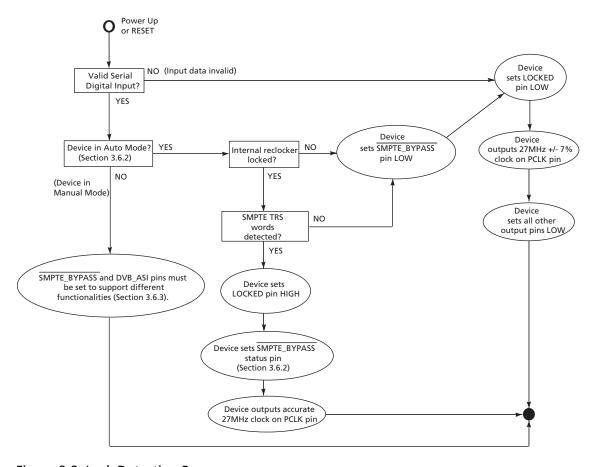

| 3.5 Modes Of Operation                                   | 23 |

| 3.5.1 Lock Detect                                        | 24 |

| 3.5.2 Auto Mode                                          | 26 |

| 3.5.3 Manual Mode                                        | 26 |

| 3.6 SMPTE Functionality                                  | 27 |

| 3.6.1 SMPTE Descrambling and Word Alignment              |    |

| 3.6.2 Internal Flywheel                                  | 27 |

| 3.6.3 Switch Line Lock Handling                          |    |

| 3.6.4 HVF Timing Signal Generation                       |    |

| 3.7 DVB-ASI Functionality                                |    |

| 3.7.1 DVB-ASI 8b/10b Decoding                            |    |

| 3.7.2 Status Signal Outputs                              |    |

| 3.8 Data-Through Functionality                           |    |

| 3.9 Additional Processing Features                       |    |

| 3.9.1 FIFO Load Pulse                                    |    |

| 3.9.2 Ancillary Data Detection and Indication            |    |

| 3.9.3 EDH Packet Detection                               |    |

| 3.9.4 EDH Flag Detection                                 |    |

| 3.9.5 SMPTE 352M Payload Identifier                      |    |

| 3.9.6 Automatic Video Standard and Data Format Detection |    |

| 3.9.7 Error Detection and Indication                     | 39 |

|      | 3.9.8 Additional Processing Functions       | . 44 |

|------|---------------------------------------------|------|

|      | 3.10 Internal FIFO Operation                | . 47 |

|      | 3.10.1 Video Mode                           | . 47 |

|      | 3.10.2 DVB-ASI Mode                         | . 48 |

|      | 3.10.3 Ancillary Data Extraction Mode       | . 52 |

|      | 3.10.4 Bypass Mode                          | . 55 |

|      | 3.11 Parallel Data Outputs                  | . 55 |

|      | 3.11.1 Parallel Data Bus Output Buffers     | . 56 |

|      | 3.11.2 Parallel Output in SMPTE Mode        | . 56 |

|      | 3.11.3 Parallel Output in DVB-ASI Mode      | . 56 |

|      | 3.11.4 Parallel Output in Data-Through Mode | . 56 |

|      | 3.12 Programmable Multi-Function Outputs    | . 56 |

|      | 3.13 GS9090B Low-latency Mode               | . 58 |

|      | 3.14 GSPI Host Interface                    | . 59 |

|      | 3.14.1 Command Word Description             | . 60 |

|      | 3.14.2 Data Read and Write Timing           | . 60 |

|      | 3.14.3 Configuration and Status Registers   |      |

|      | 3.15 JTAG Operation                         | . 63 |

|      | 3.16 Device Power Up                        | . 64 |

| 1. R | eferences & Relevant Standards              | . 66 |

| 5. A | pplication Information                      | . 67 |

|      | 5.1 Typical Application Circuit (Part A)    | . 67 |

|      | 5.2 Typical Application Circuit (Part B)    | . 68 |

| 5. P | ackage & Ordering Information               | . 69 |

|      | 6.1 Package Dimensions                      | . 69 |

|      | 6.2 Recommended PCB Footprint               |      |

|      | 6.3 Packaging Data                          | . 70 |

|      | 6.4 Marking Diagram                         | . 71 |

|      | 6.5 Ordering Information                    | . 71 |

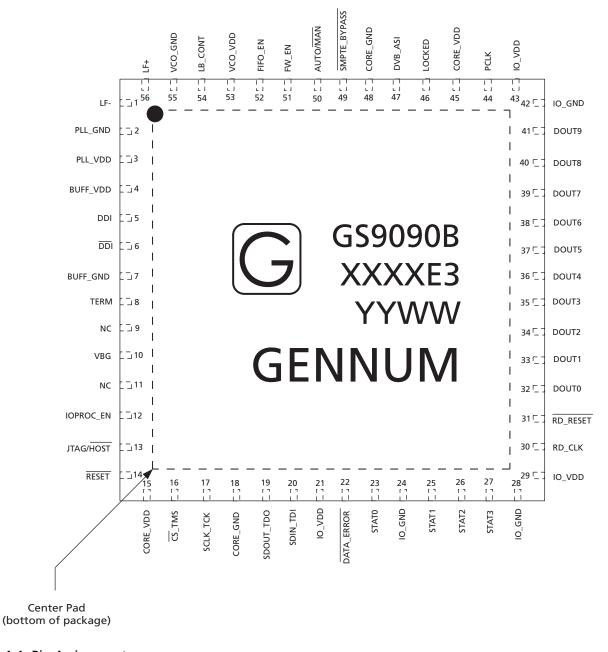

# 1. Pin Out

## 1.1 Pin Assignment

Figure 1-1: Pin Assignment

Table 1-1: Pin List and Description

| Pin Number | Name                | Timing             | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|---------------------|--------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | LF-                 | Analog             | Input          | Loop filter component connection. Connect to pin 56 (LF+) as shown in Typical Application Circuit (Part B) on page 68.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2          | PLL_GND             | Analog             | Input<br>Power | Ground connection for phase-locked loop. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3          | PLL_VDD             | Analog             | Input<br>Power | Power supply connection for phase-locked loop. Connect to +1.8V DC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4          | BUFF_VDD            | Analog             | Input<br>Power | Power supply connection for digital input buffers.  When DDI/DDI are AC coupled, this pin should be left unconnected When DDI/DDI are DC coupled, this pin should be connected to +3.3V as shown in Typical Application Circuit (Part B) on page 68.  See Serial Digital Input on page 22 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5, 6       | DDI, <del>DDI</del> | Analog             | Input          | Serial digital differential input pair.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7          | BUFF_GND            | Analog             | Input<br>Power | Ground connection for serial digital input buffer. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8          | TERM                | Analog             | Input          | Termination for serial digital input. AC couple to BUFF_GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9, 11      | NC                  | _                  | -              | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10         | VBG                 | Analog             | Input          | Bandgap filter capacitor. Connect to GND as shown in Typical Application Circuit (Part B) on page 68.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12         | IOPROC_EN           | Non<br>Synchronous | Input          | CONTROL SIGNAL INPUT Signal Levels are LVCMOS / LVTTL compatible. Used to enable or disable the I/O processing features. When set HIGH, the following I/O processing features of the device are enabled:  • Illegal Code Remapping • EDH CRC Error Correction • Ancillary Data Checksum Error Correction • TRS Error Correction • EDH Flag Detection To enable a subset of these features, keep the IOPROC_EN pin HIGH and disable the individual feature(s) in the IOPROC_DISABLE register accessible via the host interface. When set LOW, the device will enter low-latency mode. NOTE: When the internal FIFO is configured for Video mode or Ancillary Data Extraction mode, the IOPROC_EN pin must be set HIGH (see Internal FIFO Operation on page 47). |

| 13         | JTAG/HOST           | Non<br>Synchronous | Input          | CONTROL SIGNAL INPUT Signal levels are LVCMOS / LVTTL compatible. Used to select JTAG Test Mode or Host Interface Mode. When set HIGH, CS_TMS, SCLK_TCK, SDOUT_TDO, and SDIN_TDI are configured for JTAG boundary scan testing. When set LOW, CS_TMS, SCLK_TCK, SDOUT_TDO, and SDIN_TDI are configured as GSPI pins for normal host interface operation.                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 1-1: Pin List and Description (Continued)

| 14     | RESET     | Non<br>Synchronous  | Input          | CONTROL SIGNAL INPUT Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                                                                       |

|--------|-----------|---------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |           |                     |                | Used to reset the internal operating conditions to default setting or to reset the JTAG test sequence.                                                                                                                                                                                                  |

|        |           |                     |                | Host Mode (JTAG/HOST = LOW): When asserted LOW, all functional blocks will be set to default conditions and all output signals become high impedance with th exception of the STAT pins and the DATA_ERROR pin which will maintain the last state they were in for the duration that RESET is asserted. |

|        |           |                     |                | JTAG Test Mode (JTAG/HOST = HIGH): When asserted LOW, all functional blocks will be set to default and the JTAG test sequence will be held in reset.                                                                                                                                                    |

|        |           |                     |                | When set HIGH, normal operation of the JTAG test sequence resumes.                                                                                                                                                                                                                                      |

|        |           |                     |                | NOTE: See Device Power Up on page 64 for power on reset requirements.                                                                                                                                                                                                                                   |

| 15, 45 | CORE_VDD  | Non<br>Synchronous  | Input<br>Power | Power supply for digital logic blocks. Connect to +1.8V DC.  NOTE: For power sequencing requirements please see Device  Power Up on page 64.                                                                                                                                                            |

| 16     | CS_TMS    | Synchronous<br>with | Input          | CONTROL SIGNAL INPUT Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                                                                       |

|        |           | SCLK_TCK            |                | Chip Select / Test Mode Select                                                                                                                                                                                                                                                                          |

|        |           |                     |                | Host Mode (JTAG/ $\overline{\text{HOST}}$ = LOW): $\overline{\text{CS}}_{-}$ TMS operates as the host interface chip select, $\overline{\text{CS}}_{+}$ , and is active LOW.                                                                                                                            |

|        |           |                     |                | JTAG Test Mode (JTAG/ $\overline{\text{HOST}}$ = HIGH):<br>$\overline{\text{CS}}$ _TMS operates as the JTAG test mode select, TMS, and is active<br>HIGH.                                                                                                                                               |

| 17     | SCLK_TCK  | Non<br>Synchronous  | Input          | CONTROL SIGNAL INPUT Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                                                                       |

|        |           |                     |                | Serial Data Clock / Test Clock. All JTAG / Host Interface address an data are shifted into/out of the device synchronously with this clock.                                                                                                                                                             |

|        |           |                     |                | Host Mode (JTAG/HOST = LOW): SCLK_TCK operates as the host interface serial data clock, SCLK.                                                                                                                                                                                                           |

|        |           |                     |                | JTAG Test Mode (JTAG/ <del>HOST</del> = HIGH):<br>SCLK_TCK operates as the JTAG test clock, TCK.                                                                                                                                                                                                        |

| 18, 48 | CORE_GND  | Non<br>Synchronous  | Input<br>Power | Ground connection for digital logic blocks. Connect to GND.                                                                                                                                                                                                                                             |

| 19     | SDOUT_TDO | Synchronous<br>with | Output         | CONTROL SIGNAL INPUT Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                                                                       |

|        |           | SCLK_TCK            |                | Serial Data Output / Test Data Output                                                                                                                                                                                                                                                                   |

|        |           |                     |                | Host Mode (JTAG/HOST = LOW):<br>SDOUT_TDO operates as the host interface serial output, SDOUT, used to read status and configuration information from the internal registers of the device.                                                                                                             |

|        |           |                     |                | JTAG Test Mode (JTAG/ <del>HOST</del> = HIGH):                                                                                                                                                                                                                                                          |

|        |           |                     |                | SDOUT_TDO operates as the JTAG test data output, TDO.                                                                                                                                                                                                                                                   |

Table 1-1: Pin List and Description (Continued)

|                | IO_GND     |                          |        | configuration of the device and the internal FIFO mode selected. See Programmable Multi-Function Outputs on page 56 for details Ground connection for digital I/O. Connect to GND.                                             |

|----------------|------------|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |            |                          |        | <ul> <li>FIFO_EMPTY</li> <li>These pins are set to certain default values depending on the</li> </ul>                                                                                                                          |

|                |            |                          |        | • FIFO_FULL                                                                                                                                                                                                                    |

|                |            |                          |        | • EDH_DETECT                                                                                                                                                                                                                   |

|                |            |                          |        | ANC_DETECT                                                                                                                                                                                                                     |

|                |            |                          |        | • FIFO_LD                                                                                                                                                                                                                      |

|                |            |                          |        | • F                                                                                                                                                                                                                            |

|                |            |                          |        | • V                                                                                                                                                                                                                            |

|                |            |                          |        | • H                                                                                                                                                                                                                            |

|                |            | _ ·                      |        | the IO_CONFIG register, each pin can output one of the following signals:                                                                                                                                                      |

|                |            | with PCLK or<br>RD_CLK   |        | Signal levels are LVCMOS / LVTTL compatible.  Programmable multi-function outputs. By programming the bits                                                                                                                     |

| 23, 25, 26, 27 | STAT[0:3]  | Synchronous              | Output | MULTI FUNCTION I/O PORT                                                                                                                                                                                                        |

|                |            |                          |        | NOTE: It is possible to program which error conditions are monitored by the device by setting appropriate bits in the ERROR_MASK register HIGH. All error conditions are detected by default.                                  |

|                |            |                          |        | stream has been detected without error.                                                                                                                                                                                        |

|                |            |                          |        | register is read via the host interface.  The DATA_ERROR signal will be HIGH when the received data                                                                                                                            |

|                |            |                          |        | Once an error is detected, DATA_ERROR will remain LOW until th start of the next video frame / field, or until the ERROR_STATUS                                                                                                |

|                |            |                          |        | The DATA_ERROR signal will be LOW when an error within the received data stream has been detected by the device. This pin is a inverted logical 'OR'ing of all detectable errors listed in the internet ERROR_STATUS register. |

| 22             | DATA_ERROR | Synchronous<br>with PCLK | Output | STATUS SIGNAL OUTPUT. Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                             |

| 22             | DATA FROM  | Complexes                | Out    | Power Up on page 64.                                                                                                                                                                                                           |

|                |            |                          |        | NOTE: For power sequencing requirements please see Device                                                                                                                                                                      |

|                |            |                          |        | DC.  For a 5V tolerant I/O, connect pins to a +3.3V DC.                                                                                                                                                                        |

|                |            | Synchronous              | Power  | For a 3.3V tolerant I/O, connect pins to either +1.8V DC or +3.3V                                                                                                                                                              |

| 21, 29, 43     | IO_VDD     | Non                      | Input  | Power supply for digital I/O.                                                                                                                                                                                                  |

|                |            |                          |        | JTAG Test Mode (JTAG/HOST = HIGH): SDIN_TDI operates as the JTAG test data input, TDI.                                                                                                                                         |

|                |            |                          |        | Host Mode (JTAG/HOST = LOW):<br>SDIN_TDI operates as the host interface serial input, SDIN, used to<br>write address and configuration information to the internal<br>registers of the device.                                 |

|                |            | JCLK_TCK                 |        | Serial Data Input / Test Data Input                                                                                                                                                                                            |

|                |            | with<br>SCLK_TCK         |        | Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                   |

Table 1-1: Pin List and Description (Continued)

|         |           | -                                     |                   |                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-----------|---------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30      | RD_CLK    | -                                     | Input             | FIFO READ CLOCK Signal levels are LVCMOS / LVTTL compatible. The parallel data will be clocked out of the FIFO on the rising edg of RD_CLK.                                                                                                                                                                                                                            |

| 31      | RD_RESET  | Synchronous<br>with RD_CLK            | Input             | FIFO READ RESET Signal levels are LVCMOS / LVTTL compatible. Valid input only when the device is in SMPTE mode (SMPTE_BYPA! = HIGH and DVB-ASI = LOW), and the internal FIFO is configured                                                                                                                                                                             |

|         |           |                                       |                   | for video mode (See Video Mode on page 47).  A HIGH to LOW transition will reset the FIFO pointer to address zero of the memory.                                                                                                                                                                                                                                       |

| 32 - 41 | DOUT[0:9] | Synchronous<br>with RD_CLK<br>or PCLK | Output            | PARALLEL VIDEO DATA BUS Signal levels are LVCMOS / LVTTL compatible. When the internal FIFO is enabled and configured for either vide mode or DVB-ASI mode, parallel data will be clocked out of the device on the rising edge of RD_CLK.                                                                                                                              |

|         |           |                                       |                   | When the internal FIFO is in bypass mode, parallel data will be clocked out of the device on the rising edge of PCLK.  DOUT9 is the MSB and DOUT0 is the LSB.                                                                                                                                                                                                          |

| 44      | PCLK      | -                                     | Output            | PIXEL CLOCK OUTPUT Signal levels are LVCMOS / LVTTL compatible. 27MHz parallel clock output.                                                                                                                                                                                                                                                                           |

| 46      | LOCKED    | Synchronous<br>with PCLK              | Output            | STATUS SIGNAL OUTPUT Signal levels are LVCMOS / LVTTL compatible. The LOCKED signal will be HIGH whenever the device has correct received and locked to SMPTE compliant data in SMPTE mode or DVB-ASI compliant data in DVB-ASI mode, or when the reclocker has achieved lock in Data-Through mode. It will be LOW otherwise. When the signal is LOW, all digital outp |

| 47      | DVB_ASI   | Non<br>Synchronous                    | Input /<br>Output | signals will be forced to logic LOW levels.  CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT Signal levels are LVCMOS / LVTTL compatible.  This pin and its function are only supported in Manual mode (AUTO/MAN = LOW).                                                                                                                                                   |

|         |           |                                       |                   | When this pin is set HIGH, the device will be configured to opera in DVB-ASI mode. The SMPTE_BYPASS pin will be ignored.  When set LOW, the device will not support the decoding or word alignment of received DVB-ASI data.                                                                                                                                           |

Table 1-1: Pin List and Description (Continued)

| 49 | SMPTE_BYPASS | Non<br>Synchronous | Input /<br>Output | CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT<br>Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                                                                                        |

|----|--------------|--------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |              |                    |                   | This pin is an input in Manual mode, and an output set by the device in Auto mode.                                                                                                                                                                                                                                                                 |

|    |              |                    |                   | Auto Mode (AUTO/MAN = HIGH): The SMPTE_BYPASS signal will be HIGH only when the device has locked to a SMPTE compliant data stream. It will be LOW otherwise. When the signal is LOW, no I/O processing features are available.                                                                                                                    |

|    |              |                    |                   | Manual Mode (AUTO/MAN = LOW):  When this pin is set HIGH in conjunction with DVB_ASI = LOW, the device will be configured to operate in SMPTE mode. All I/O processing features may be enabled in this mode.                                                                                                                                       |

|    |              |                    |                   | When the SMPTE_BYPASS pin is set LOW, the device will not support the descrambling, decoding, or word alignment of received SMPTE data. No I/O processing features will be available.                                                                                                                                                              |

| 50 | AUTO/MAN     | Non<br>Synchronous | Input             | CONTROL SIGNAL INPUT Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                                                                                                                  |

|    |              | ·,                 |                   | When set HIGH, the GS9090B will operate in Auto mode. The SMPTE_BYPASS pin becomes an output status signal set by the device. In this mode, the GS9090B will automatically detect, reclock, deserialize, and process SMPTE compliant input data.                                                                                                   |

|    |              |                    |                   | When set LOW, the GS9090B will operate in Manual mode. The DVB_ASI and SMPTE_BYPASS pins become input control signals. In this mode, these two external pins must be set for the correct reception of either SMPTE or DVB-ASI data. Manual mode also supports the reclocking and deserializing of data not conforming to SMPTE or DVB-ASI streams. |

| 51 | FW_EN        | Non<br>Synchronous | Input             | CONTOL SIGNAL INPUT Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                                                                                                                   |

|    |              |                    |                   | Used to enable or disable the noise immune flywheel of the device                                                                                                                                                                                                                                                                                  |

|    |              |                    |                   | When set HIGH, the internal flywheel is enabled. This flywheel is used in the extraction of timing signals, the generation of TRS signals, the automatic detection of video standards, and in manus switch line lock handling.                                                                                                                     |

|    |              |                    |                   | When set LOW, the internal flywheel is disabled. Timing based TR errors will not be detected.                                                                                                                                                                                                                                                      |

| 52 | FIFO_EN      | Non<br>Synchronous | Input             | CONTOL SIGNAL INPUT<br>Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                                                                                                                                |

|    |              |                    |                   | Used to enable / disable the internal FIFO.                                                                                                                                                                                                                                                                                                        |

|    |              |                    |                   | When FIFO_EN is HIGH, the internal FIFO will be enabled. Data wi<br>be clocked out of the device on the rising edge of the RD_CLK<br>input pin if the FIFO is in video mode or DVB-ASI mode.                                                                                                                                                       |

|    |              |                    |                   | When FIFO_EN is LOW, the internal FIFO is bypassed and parallel data is clocked out on the rising edge of the PCLK output.                                                                                                                                                                                                                         |

|    |              |                    |                   |                                                                                                                                                                                                                                                                                                                                                    |

Table 1-1: Pin List and Description (Continued)

| 53 | VCO_VDD    | Analog | Input<br>Power | Power supply connection for Voltage-Controlled-Oscillator.<br>Connect to +1.8V DC.                                    |

|----|------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------|

| 54 | LB_CONT    | Analog | Input          | CONTROL SIGNAL INPUT  Control voltage to fine-tune the loop bandwidth of the PLL.                                     |

| 55 | VCO_GND    | Analog | Input<br>Power | Ground connection for Voltage-Controlled-Oscillator. Connect to GND.                                                  |

| 56 | LF+        | Analog | Input          | Loop filter component connection. Connect to pin 1 (LF-) as shown in Typical Application Circuit (Part B) on page 68. |

| -  | Center Pad | -      | Power          | Connect to GND following recommendations in Recommended PCB Footprint on page 70                                      |

# 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                               | Value/Units                      |

|-----------------------------------------|----------------------------------|

| Supply Voltage Core                     | -0.3V to +2.1V                   |

| Supply Voltage I/O                      | -0.3V to +3.47V                  |

| Input Voltage Range (any input)         | -2.0V to + 5.25V                 |

| Ambient Operating Temperature           | -20°C ≤ T <sub>A</sub> ≤ 85°C    |

| Storage Temperature                     | -40°C ≤ T <sub>STG</sub> ≤ 125°C |

| ESD protection on all pins (see Note 1) | 1kV                              |

| Solder Reflow Temperature               | 260°C                            |

| NOTES:                                  |                                  |

| 1. HBM, per JESD22 - A114B              |                                  |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions or at any other condition beyond those indicated in the AC/DC Electrical Characteristic sections is not implied.

### 2.2 DC Characteristics

**Table 2-2: DC Electrical Characteristics**

$V_{DD}$  = 1.8V ±5%, 3.3V ±5%;  $T_A$  = 0°C to 70°C, unless otherwise specified. Typical values:  $V_{CC}$  = 1.8V, 3.3V and  $T_A$  =25°C

| Parameter                       | Symbol         | Condition                                             | Min  | Тур | Max  | Units | Notes |

|---------------------------------|----------------|-------------------------------------------------------|------|-----|------|-------|-------|

| System                          |                |                                                       |      |     |      |       |       |

| Core Power Supply Voltage       | CORE_VDD       | -                                                     | 1.71 | 1.8 | 1.89 | V     | -     |

| Digital I/O Buffer Power Supply | IO_VDD         | 1.8V Operation                                        | 1.71 | 1.8 | 1.89 | V     | _     |

| Voltage                         | IO_VDD         | 3.3V Operation                                        | 3.13 | 3.3 | 3.47 | V     | _     |

| PLL Power Supply Voltage        | PLL_VDD        | _                                                     | 1.71 | 1.8 | 1.89 | V     | _     |

| VCO Power Supply Voltage        | VCO_VDD        | _                                                     | 1.71 | 1.8 | 1.89 | V     | _     |

| Typical System Power            | $P_{D}$        | $CORE\_VDD = 1.8V$ $IO\_VDD = 1.8V$ $T = 25^{\circ}C$ | -    | 145 | -    | mW    | -     |

| Max. System Power               | P <sub>D</sub> | CORE_VDD = 1.89V<br>IO_VDD = 3.47V<br>T = 70°C        | -    | -   | 270  | mW    | -     |

### **Table 2-2: DC Electrical Characteristics (Continued)**

$V_{DD}$  = 1.8V ±5%, 3.3V ±5%;  $T_A$  = 0°C to 70°C, unless otherwise specified. Typical values:  $V_{CC}$  = 1.8V, 3.3V and  $T_A$  =25°C

| Parameter                    | Symbol            | Condition                                     | Min                                   | Тур | Max                                   | Units | Notes |

|------------------------------|-------------------|-----------------------------------------------|---------------------------------------|-----|---------------------------------------|-------|-------|

| Digital I/O                  |                   |                                               |                                       |     |                                       |       |       |

| Input Voltage, Logic LOW     | V <sub>IL</sub>   | 1.8V Operation or 3.3V Operation              | -                                     | _   | 0.35 x<br>IO_VDD                      | V     | -     |

| Input Voltage, Logic HIGH    | $V_{IH}$          | 1.8V Operation or 3.3V Operation              | 0.65 x<br>IO_VDD                      | -   | -                                     | V     | -     |

| Output Voltage, Logic LOW    | $V_{OL}$          | I <sub>OL</sub> = 8mA @ 3.3V,<br>4mA @ 1.8V   | -                                     | -   | 0.4                                   | V     | -     |

| Output Voltage, Logic HIGH   | V <sub>OH</sub>   | I <sub>OL</sub> = -8mA @ 3.3V,<br>-4mA @ 1.8V | IO_VDD -<br>0.4                       | _   | -                                     | V     | =     |

| Serial Digital Inputs        |                   |                                               |                                       |     |                                       |       |       |

| Input Common Mode Voltage    | V <sub>CMIN</sub> | BUFF_VDD<br>connected to 3.3V<br>supply       | BUFF_GND<br>+ (V <sub>DIFF</sub> / 2) | -   | BUFF_VDD<br>- (V <sub>DIFF</sub> / 2) | V     | -     |

| Input Termination Resistance | R <sub>IN</sub>   | _                                             | 37.5                                  | 50  | 62.5                                  | Ω     | -     |

### 2.3 AC Electrical Characteristics

#### **Table 2-3: AC Electrical Characteristics**

$V_{DD}$  = 1.8V ±5%, 3.3V ±5%;  $T_A$  = 0°C to 70°C, unless otherwise specified. Typical values:  $V_{CC}$  = 1.8V, 3.3V and  $T_A$  =25°C

| Parameter                                       | Symbol            | Condition                                                                              | Min | Тур | Max | Units | Notes |

|-------------------------------------------------|-------------------|----------------------------------------------------------------------------------------|-----|-----|-----|-------|-------|

| System                                          |                   |                                                                                        |     |     |     |       |       |

| Asynchronous Lock Time (LOCKED signal set HIGH) | t <sub>LOCK</sub> | Input jitter of 0.2UI,  No data to SMPTE,  SMPTE_BYPASS = HIGH  DVB_ASI = LOW, at 25°C | -   | -   | 235 | us    | 1     |

| Asynchronous Lock Time (LOCKED signal set HIGH) | <sup>t</sup> LOCK | Input jitter of 0.2UI, No data to non-SMPTE, SMPTE_BYPASS = LOW DVB_ASI = LOW, at 25°C | -   | -   | 165 | us    | 1     |

#### Table 2-3: AC Electrical Characteristics (Continued)

$V_{DD}$  = 1.8V ±5%, 3.3V ±5%;  $T_A$  = 0°C to 70°C, unless otherwise specified. Typical values:  $V_{CC}$  = 1.8V, 3.3V and  $T_A$  =25°C

| Parameter                                          | Symbol             | Condition       | Min  | Тур | Max   | Units             | Notes |

|----------------------------------------------------|--------------------|-----------------|------|-----|-------|-------------------|-------|

| Serial Digital Input                               |                    |                 |      |     |       |                   |       |

| Serial Input Data Rate                             | DR <sub>SDI</sub>  | _               | -    | 270 | -     | Mb/s              | -     |

| DVB-ASI Payload Data Rate                          | DR <sub>ASI</sub>  | 204 byte mode   | -    | -   | 213.9 | Mb/s              | 2,4   |

|                                                    |                    | 188 byte mode   | _    | -   | 213.7 | Mb/s              | 3,4   |

| Serial Input Jitter Tolerance                      | IJT                | -               | _    | 0.5 | -     | UI                | 5     |

| Differential Input Voltage Range                   | -                  | BUFF_VDD = 1.8V | 200  | 800 | 1700  | mV <sub>p-p</sub> | -     |

|                                                    | _                  | BUFF_VDD = 3.3V | 100  | 800 | 2200  | mV <sub>p-p</sub> | -     |

| Parallel Output                                    |                    |                 |      |     |       |                   |       |

| Parallel Output Clock Frequency                    | f <sub>PCLK</sub>  | _               | -    | 27  | -     | MHz               | -     |

| Parallel Output Clock Duty Cycle                   | DC <sub>PCLK</sub> | -               | 40   | -   | 60    | %                 | -     |

| Variation of Parallel Output Clock<br>(from 27MHz) | -                  | Device Unlocked | -7.5 |     | +7.5  | %                 | 6     |

| Output Data Hold Time                              | t <sub>OH</sub>    | With 15pF load  | 3    | -   | -     | ns                | 7     |

| Output Delay Time                                  | t <sub>OD</sub>    | With 15pF load  | _    | -   | 10    | ns                | 7     |

| GSPI                                               |                    |                 |      |     |       |                   |       |

| GSPI Input Clock Frequency                         | f <sub>GSPI</sub>  | -               | -    | -   | 54    | MHz               | -     |

| GSPI Clock Duty Cycle                              | DC <sub>GSPI</sub> | -               | 40   | _   | 60    | %                 | _     |

| GSPI Setup Time                                    | t <sub>GS</sub>    | -               | 1.5  | _   | -     | ns                | _     |

| GSPI Hold Time                                     | t <sub>GH</sub>    | -               | _    | _   | 1.5   | ns                | _     |

#### NOTES

- 1. No signal to signal present, or a switch from another data rate to 270Mb/s.

- 2. Transmission format includes 204 byte data packets preceded by two K28.5 synchronization characters. Payload data rate excludes the two K28.5 synchronization characters.

- 3. Transmission format includes 188 byte data packets preceded by two K28.5 synchronization characters. Payload data rate excludes the two K28.5 synchronization characters.

- 4. Maximum payload is achieved via data packet mode, however, any combination of burst and packet mode is supported as long as each byte or packet is preceded by two K28.5 characters.

- 5. Power supply noise  $50 \text{mV}_{pp}$  at 15 kHz, 100 kHz, 1 MHz sinusoidal modulation.

- 6. When the serial input to the GS9090B is removed, the PCLK output signal will continue to operate at 27MHz and the internal VCO will remain at this frequency within +/-7.5%.

- 7. Timing includes the following outputs: DOUT[9:0], H, V, F, ANC, EDH\_DETECT, FIFO\_FULL, FIFO\_EMPTY, FIFO\_LD, WORDERR, SYNCOUT. When the FIFO is enabled, the outputs are measured with respect to RD\_CLK.

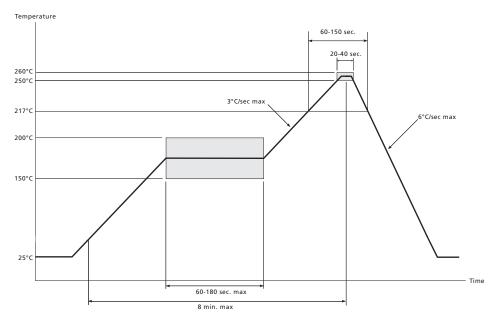

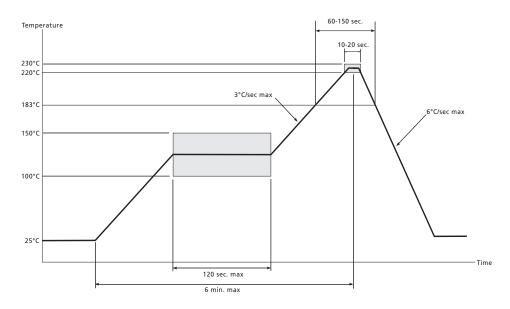

### 2.4 Solder Reflow Profiles

The device is manufactured with Matte-Sn terminations and is compatible with both standard eutectic and Pb-free solder reflow profiles. MSL qualification was performed using the maximum Pb-free reflow profile shown in Figure 2-1. The recommended standard eutectic reflow profile is shown in Figure 2-2.

Figure 2-1: Maximum Pb-free Solder Reflow Profile (Preferred)

Figure 2-2: Standard Pb Solder Reflow Profile

# 2.5 Host Interface Map

**Table 2-4: Host Interface Map**

| Register Name           | Address | 15       | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6                       | 5                       | 4                       | 3                     | 2                | 1                | 0                |

|-------------------------|---------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-------------------------|-------------------------|-------------------------|-----------------------|------------------|------------------|------------------|

| FIFO_LD_POSITION[12:0]  | 28h     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

|                         | 27h     |          |          |          |          |          |          |          |          |          |                         |                         |                         |                       |                  |                  |                  |

|                         | 26h     |          |          |          |          |          |          |          |          |          |                         |                         |                         |                       |                  |                  |                  |

| ERROR_MASK_REGISTER     | 25h     | Not Used | VD_STD_<br>ERR_<br>MASK | FF_CRC_<br>ERR_<br>MASK | AP_CRC_<br>ERR_<br>MASK | LOCK_<br>ERR_<br>MASK | CCS_ERR_<br>MASK | SAV_ERR_<br>MASK | EAV_ERR<br>_MASK |

| FF_PIXEL_END_F1[12:0]   | 24h     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| FF_PIXEL_START_F1[12:0] | 23h     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| FF_PIXEL_END_F0[12:0]   | 22h     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| FF_PIXEL_START_F0[12:0] | 21h     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| AP_PIXEL_END_F1[12:0]   | 20h     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| AP_PIXEL_START_F1[12:0] | 1Fh     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| AP_PIXEL_END_F0[12:0]   | 1Eh     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| AP_PIXEL_START_F0[12:0] | 1Dh     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| FF_LINE_END_F1[10:0]    | 1Ch     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| FF_LINE_START_F1[10:0]  | 1Bh     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| FF_LINE_END_F0[10:0]    | 1Ah     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| FF_LINE_START_F0[10:0]  | 19h     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| AP_LINE_END_F1[10:0]    | 18h     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| AP_LINE_START_F1[10:0]  | 17h     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| AP_LINE_END_F0[10:0]    | 16h     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| AP_LINE_START_F0[10:0]  | 15h     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| RASTER_STRUCTURE4[10:0] | 14h     | Not Used | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

| RASTER_STRUCTURE3[12:0] | 13h     | Not Used | Not Used | Not Used | b12      | b11      | b10      | b9       | b8       | b7       | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

**Table 2-4: Host Interface Map (Continued)**

| Register Name           | Address | 15       | 14            | 13             | 12                      | 11                      | 10                     | 9                      | 8                      | 7                      | 6                      | 5                      | 4                      | 3                      | 2                      | 1                      | 0                      |

|-------------------------|---------|----------|---------------|----------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| RASTER_STRUCTURE2[12:0] | 12h     | Not Used | Not Used      | Not Used       | b12                     | b11                     | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| RASTER_STRUCTURE1[10:0] | 11h     | Not Used | Not Used      | Not Used       | Not Used                | Not Used                | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| VIDEO_FORMAT_OUT_B(4,3) | 10h     | VFO4-b7  | VFO4-b6       | VFO4-b5        | VFO4-b4                 | VFO4-b3                 | VFO4-b2                | VFO4-b1                | VFO4-b0                | VFO3-b7                | VFO3-b6                | VFO3-b5                | VFO3-b4                | VFO3-b3                | VFO3-b2                | VFO3-b1                | VFO3-b0                |

| VIDEO_FORMAT_OUT_A(2,1) | 0Fh     | VFO2-b7  | VFO2-b6       | VFO2-b5        | VFO2-b4                 | VFO2-b3                 | VFO2-b2                | VFO2-b1                | VFO2-b0                | VFO1-b7                | VFO1-b6                | VFO1-b5                | VFO1-b4                | VFO1-b3                | VFO1-b2                | VFO1-b1                | VFO1-b0                |

| ANC_TYPE(5)[15:0]       | 0Eh     | b15      | b14           | b13            | b12                     | b11                     | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| ANC_TYPE(4)[15:0]       | 0Dh     | b15      | b14           | b13            | b12                     | b11                     | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| ANC_TYPE(3)[15:0]       | 0Ch     | b15      | b14           | b13            | b12                     | b11                     | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| ANC_TYPE(2)[15:0]       | 0Bh     | b15      | b14           | b13            | b12                     | b11                     | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| ANC_TYPE(1)[15:0]       | 0Ah     | b15      | b14           | b13            | b12                     | b11                     | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| ANC_LINE_B[10:0]        | 09h     | Not Used | Not Used      | Not Used       | Not Used                | Not Used                | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| ANC_LINE_A[10:0]        | 08h     | Not Used | Not Used      | Not Used       | Not Used                | Not Used                | b10                    | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| FIFO_FULL_OFFSET        | 07h     | Not Used | Not Used      | Not Used       | Not Used                | Not Used                | Not Used               | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| FIFO_EMPTY_OFFSET       | 06h     | Not Used | Not Used      | Not Used       | Not Used                | ANC_<br>DATA_<br>DELETE | Not Used               | b9                     | b8                     | b7                     | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0                     |

| IO_CONFIG               | 05h     | Not Used | Not Used      | Not Used       | ANC_<br>DATA_<br>SWITCH | STAT3_<br>CONFIG<br>b2  | STAT3_<br>CONFIG<br>b1 | STAT3_<br>CONFIG<br>b0 | STAT2_<br>CONFIG<br>b2 | STAT2_<br>CONFIG<br>b1 | STAT2_<br>CONFIG<br>b0 | STAT1_<br>CONFIG<br>b2 | STAT1_<br>CONFIG<br>b1 | STAT1_<br>CONFIG<br>b0 | STAT0_<br>CONFIG<br>b2 | STATO_<br>CONFIG<br>b1 | STATO_<br>CONFIG<br>b0 |

| DATA_FORMAT             | 04h     | Not Used | Not Used      | Not Used       | Not Used                | EDH_<br>FLAG_<br>UPDATE | AP_CRC<br>_V           | FF_CRC<br>_V           | EDH_<br>DETECT         | VERSION_<br>352M       | Not Used               | Not Used               | STD_<br>LOCK           | DATA_<br>FORMAT<br>b3  | DATA_<br>FORMAT<br>b2  | DATA_<br>FORMAT<br>b1  | DATA_<br>FORMAT<br>b0  |

| EDH_FLAG_OUT            | 03h     | Not Used | ANC-UES       | ANC-IDA        | ANC-IDH                 | ANC-EDA                 | ANC-EDH                | FF-UES                 | FF-IDA                 | FF-IDH                 | FF-EDA                 | FF-EDH                 | AP-UES                 | AP-IDA                 | AP-IDH                 | AP-EDA                 | AP-EDH                 |

| EDH_FLAG_IN             | 02h     | Not Used | ANC-UE<br>_IN | ANC-IDA<br>_IN | ANC-IDH<br>_IN          | ANC-EDA<br>_IN          | ANC-EDH<br>_IN         | FF-UES_<br>IN          | FF-IDA_IN              | FF-IDH<br>_IN          | FF-EDA<br>_IN          | FF-EDH<br>_IN          | AP-UES<br>_IN          | AP-IDA_I<br>N          | AP-IDH_I<br>N          | AP-EDA_I<br>N          | AP-EDH_I<br>N          |

| ERROR_STATUS            | 01h     | Not Used | Not Used      | Not Used       | Not Used                | Not Used                | Not Used               | Not Used               | Not Used               | Not Used               | VD_STD_<br>ERR         | FF_CRC_<br>ERR         | AP_CRC_<br>ERR         | LOCK_<br>ERR           | CCS_ERR                | SAV_ERR                | EAV_ERR                |

| IOPROC_DISABLE          | 00h     | Not Used | Not Used      | Not Used       | Not Used                | Not Used                | Not Used               | ANC_PKT<br>_EXT        | FIFO_<br>MODE<br>b1    | FIFO_<br>MODE<br>b0    | H_<br>CONFIG           | Not Used               | Not Used               | ILLEGAL_<br>REMAP      | EDH_CRC<br>_INS        | ANC_<br>CSUM_<br>INS   | TRS_IN                 |

NOTE: Addresses 02Ch to 42Bh store the contents of the internal FIFO. The contents may be accessed in Ancillary Data Extraction mode (see Section 3.10.3).

## 2.5.1 Host Interface Map (R/W registers)

Table 2-5: Host Interface Map (R/W registers)

| Register Name           | Address | 15 | 14 | 13 | 12  | 11  | 10  | 9  | 8  | 7  | 6                       | 5                       | 4                       | 3                     | 2                | 1                | 0                |

|-------------------------|---------|----|----|----|-----|-----|-----|----|----|----|-------------------------|-------------------------|-------------------------|-----------------------|------------------|------------------|------------------|

| FIFO_LD_POSITION[12:0]  | 28h     |    |    |    | b12 | b11 | b10 | b9 | b8 | b7 | b6                      | b5                      | b4                      | b3                    | b2               | b1               | b0               |

|                         | 27h     |    |    |    |     |     |     |    |    |    |                         |                         |                         |                       |                  |                  |                  |

|                         | 26h     |    |    |    |     |     |     |    |    |    |                         |                         |                         |                       |                  |                  |                  |

| ERROR_MASK_REGISTER     | 25h     |    |    |    |     |     |     |    |    |    | VD_STD_<br>ERR_<br>MASK | FF_CRC_<br>ERR_<br>MASK | AP_CRC_<br>ERR_<br>MASK | LOCK_<br>ERR_<br>MASK | CCS_ERR_<br>MASK | SAV_ERR_<br>MASK | EAV_ERR<br>_MASK |