Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**GX3246**

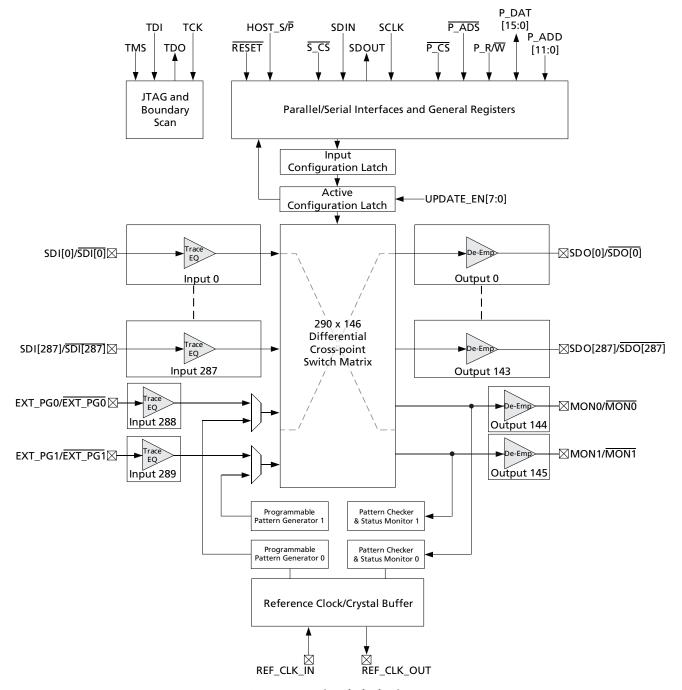

# 290 x 146 3.5Gb/s Crosspoint Switch with Trace Equalization and Output De-emphasis

### **Key Features**

- 290 x 146 crosspoint switch architecture supporting broadcast and multi-cast modes

- Supports all data rates up to 3.5Gb/s

- Low power consumption: 21.47W typical (all channels active)

- Sophisticated, dynamic on-chip power management control

- Independent, programmable input trace equalization to reduce deterministic jitter (ISI)

- Independent, programmable output de-emphasis for driving long board traces

- High-speed, video-optimized control for multi-format applications

- Built-in system test features with on-chip PRBS generators and analyzers

- 2.5V analog core voltage, 1.8V digital core voltage

- Input and output voltages support either 1.2V, 1.8V or 2.5V CML

- JTAG-controlled boundary scan

- Selectable parallel/serial host interface

- 50mm x 50mm BGA (2377 ball)

- Operating temperature range: 0°C to +85°C

- RoHS compliant

### **Applications**

Large m x n cascaded routers/switch fabrics for:

- Professional broadcast applications

- Enterprise and carrier applications

- High-speed automated test equipment

- 10GbE and InfiniBand networks

### **Description**

The GX3246 is a low-power, high-speed  $290 \times 146$  crosspoint switch, with robust signal conditioning circuits for driving and receiving high-speed signals through backplanes.

The device typically consumes 21.47W of power with all channels operational, and features sophisticated, dynamically scalable power management. Unused portions of the core are automatically turned off without affecting the operation of the remaining channels.

The signal conditioning features of the GX3246 include per-input programmable equalization and per-output programmable de-emphasis. The input equalizer removes ISI jitter—typically caused by PCB trace losses—by opening the input data eye in applications where long PCB traces are used. There are four settings available for the input equalizer, allowing flexibility in adjusting the equalization level on a per-input basis.

Output de-emphasis capability provides a boost of the high-frequency content of the output signal, such that the data eye remains open after passing through a long interconnect of PCB traces and connectors. There are four de-emphasis settings that can be enabled on a per-output basis.

Two integrated programmable pattern generators, and two pattern checkers are provided to assist in system test and configuration.

The pattern generators can each be routed to any output of the device without impacting the normal operation of any other channel. Any input can be routed to each of the pattern checkers.

The chip features eight independent strobe inputs, UPDATE\_EN[7:0], which are used to determine the timing of the output updates. Any output can be linked to any strobe.

**GX3246 Functional Block Diagram**

# **Revision History**

| Version | ECO    | PCN | Date         | Changes and/or Modifications                                                                                                                                                                                                                                                   |

|---------|--------|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | 011792 | -   | March 2013   | Corrected second bullet in Section 4.7.1, and added a note in Section 4.4.                                                                                                                                                                                                     |

| 1       | 158398 | -   | October 2012 | Included ESD Voltage Sensitivity in Table 2-1.  Modifications to Table 4-18 and Section 4.12.2 to include Auto-Increment Timing and functionality.  Updates to Appendix - Relevant Documentation with clear reference to correct documents.  Converted document to Data Sheet. |

| 0       | 157404 | -   | March 2012   | Converted document to Preliminary Data Sheet. Updates throughout.                                                                                                                                                                                                              |

| А       | 156968 | -   | October 2011 | New document.                                                                                                                                                                                                                                                                  |

www.semtech.com

### **Contents**

| Key Features                                       | 1  |

|----------------------------------------------------|----|

| Applications                                       | 1  |

| Description                                        | 1  |

| Revision History                                   | 3  |

| 1. Ball Out                                        | 5  |

| 1.1 Ball Assignment                                | 5  |

| 1.2 Ball Descriptions                              | 6  |

| 2. Electrical Characteristics                      | 9  |

| 2.1 Absolute Maximum Ratings                       | 9  |

| 2.2 Recommended Operating Conditions               | 10 |

| 2.3 DC Electrical Characteristics                  | 11 |

| 2.4 AC Electrical Characteristics                  | 15 |

| 3. Input/Output Equivalent Circuits                | 17 |

| 4. Detailed Description                            | 20 |

| 4.1 Serial Data Input                              | 20 |

| 4.2 Serial Data Output                             | 21 |

| 4.3 Crosspoint Switch Matrix Operation             | 23 |

| 4.4 Propagation Delay                              | 24 |

| 4.5 Using Multiple Strobes                         | 24 |

| 4.6 Pattern Generator and Pattern Checker          | 25 |

| 4.6.1 Pattern Generator                            | 25 |

| 4.6.2 Pattern Checker                              | 26 |

| 4.7 Horizontal Eye Measurement                     | 30 |

| 4.7.1 Configuration for Horizontal Eye Measurement | 30 |

| 4.8 Temperature Sensors                            | 30 |

| 4.9 27MHz Reference Clock                          | 33 |

|                                                    |    |

| 4.10 Device Power-Up                           | 33 |

|------------------------------------------------|----|

| 4.11 Device Reset                              | 34 |

| 4.12 Host Interface                            | 34 |

| 4.12.1 Parallel Host Interface Specifications  | 34 |

| 4.12.2 Serial Host Interface Specifications    | 39 |

| 5. Application Information                     | 41 |

| 5.1 Power Supply Filtering and Recommendations | 41 |

| 5.2 Estimated Worst-Case Load Current Steps    | 42 |

| 5.2.1 VCC_25_A Supply                          | 42 |

| 5.2.2 VCC_OUT1, VCC_OUT2 Supplies              | 42 |

| 5.2.3 VCC_IN1, VCC_IN2 Supplies                | 43 |

| 6. Package and Ordering Information            | 44 |

| 6.1 Package Dimensions                         | 44 |

| 6.2 Package Thermal Data and Information       |    |

| 6.3 Marking Diagram                            | 45 |

| 6.4 Solder Reflow Profile                      |    |

| 6.5 Ordering Information                       | 46 |

| Appendix - Relevant Documentation              | 46 |

# 1. Ball Out

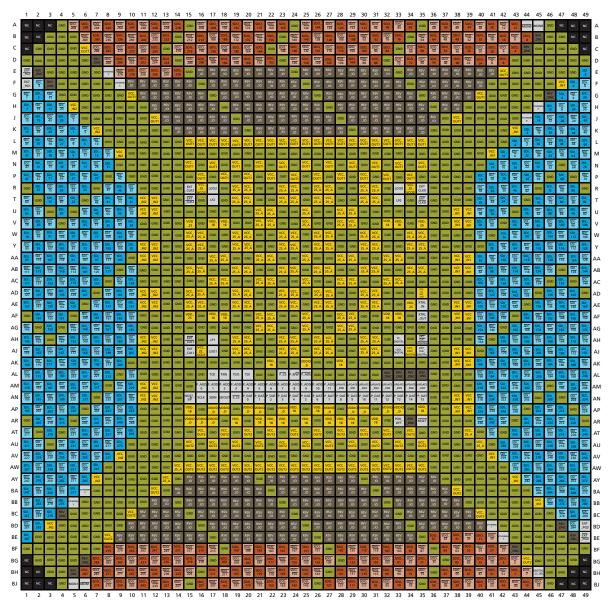

# 1.1 Ball Assignment

Figure 1-1: GX3246 Ball Assignment Overview (Top View)

# **1.2 Ball Descriptions**

Table 1-1 shows the descriptions for selected GX3246 balls. For a comprehensive list of balls from the GX3246 Crosspoint family, please refer to GX3290 (and family) Crosspoint Ball Guide.

**Table 1-1: Ball Descriptions**

| Ball #                 | Ball Name          | I/O | Description                                                                                                                                                                                                        |

|------------------------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Interface I/O   |                    |     |                                                                                                                                                                                                                    |

| AN16                   | SCLK               | I   | Serial Host Interface Clock. If unused, tie to ground.                                                                                                                                                             |

| AN17                   | SDIN               | I   | Serial Host Interface Data Input. If unused, tie to ground.                                                                                                                                                        |

| AN18                   | SDOUT              | 0   | Serial Host Interface Data Output. Leave NC if not used.                                                                                                                                                           |

| AN19                   | <u>s_cs</u>        | ĺ   | Serial Host Interface Chip Select. Active-LOW. Must be tied LOW when HOST_S/ $\overline{P}$ is set LOW.                                                                                                            |

| Parallel Interface I/O |                    |     |                                                                                                                                                                                                                    |

| AL23                   | P_CS               | I   | Parallel host interface chip select. Active-LOW. Must be tied LOW when HOST_S/ $\overline{P}$ is set HIGH.                                                                                                         |

| AL24                   | P_R/W              | I   | Selects between read and write operations on the parallel host interface.<br>HIGH = Read, LOW = Write. If unused, tie to ground.                                                                                   |

| AL25                   | P_ADS              | 1   | Address and Data Strobe. Strobe signal for latching the address and data into the chip. See Section 4.12.1 for timing information. If unused, tie to ground.                                                       |

| AM27 - AM16            | P_ADD[11:0]        | I   | Address bus for the parallel interface. If unused, tie to ground.                                                                                                                                                  |

| AN35 - AN20            | P_DAT[15:0]        | I/O | Bi-directional data bus for the parallel interface. If $\overline{P_{-}CS}$ is HIGH, these pin are configured as inputs. Leave NC if parallel interface is not used. If unused, tie to ground.                     |

| General I/O            |                    |     |                                                                                                                                                                                                                    |

| AN15                   | HOST_S/P           | I   | Host Interface Select pin. Selects between serial and parallel host interfaces. Serial host interface is enabled when HIGH, parallel host interface is enabled when LOW. Must assert RESET after changing this pin |

| AM35 - AM28            | UPDATE_EN<br>[7:0] | I   | Update Strobes used to update the switch matrix configuration (see Section 4.5). If unused, weak pull-down to ground.                                                                                              |

| AR33                   | POR_DFT            | ĺ   | This pin disables the Power On Reset circuitry when HIGH. Weak internal pull-down. Leave NC if not used.                                                                                                           |

| AR35                   | RESET              | I   | Active-LOW reset for entire chip (see Section 4.11 for timing details). Wea internal pull-up. Leave NC if not used.                                                                                                |

| Test Interface         |                    |     |                                                                                                                                                                                                                    |

| AL17                   | TCK                | l   | JTAG test clock. Weak pull-up if not used.                                                                                                                                                                         |

| AL18                   | TMS                | I   | JTAG test mode start. Weak pull-up if not used.                                                                                                                                                                    |

| AL19                   | TDO                | 0   | JTAG test data out. Leave NC if not used.                                                                                                                                                                          |

Table 1-1: Ball Descriptions (Continued)

| Ball #             | Ball Name           | I/O | Description                                                                                                              |

|--------------------|---------------------|-----|--------------------------------------------------------------------------------------------------------------------------|

| AL20               | TDI                 | I   | JTAG test data in. Weak pull-up if not used.                                                                             |

| Filtering          |                     |     |                                                                                                                          |

| R17                | LDO2                | _   | LDO filter capacitor for VCO_2. Connect through a 220nF capacitor to ground.  See Figure 3-3 for configuration.          |

| R33                | LDO0                | _   | LDO filter capacitor for VCO_0. Connect through a 220nF capacitor to ground.  See Figure 3-3 for configuration.          |

| T17                | LF2                 | _   | PLL loop filter capacitor for VCO_2. See Figure 3-3 for configuration. Leave NC if not used.                             |

| Т33                | LF0                 | _   | PLL loop filter capacitor for VCO_0. See Figure 3-3 for configuration. Leave NC if not used.                             |

| AH17               | LF1                 | _   | PLL loop filter capacitor for VCO_1. See Figure 3-3 for configuration. Leave NC if not used.                             |

| AH33               | LF_DIGITAL          | _   | PLL loop filter capacitor for VCO_DIGITAL. Connect through a 47nF capacitor to ground. See Figure 3-3 for configuration. |

| AJ17               | LDO1                | _   | LDO filter capacitor for VCO_1. Connect through a 220nF capacitor to ground. See Figure 3-3 for configuration.           |

| AJ33               | LDO_DIGITAL         | _   | LDO filter capacitor for VCO_DIGITAL. Connect through a 220nF capacitor to ground. See Figure 3-3 for configuration.     |

| Crystal Oscillator |                     |     |                                                                                                                          |

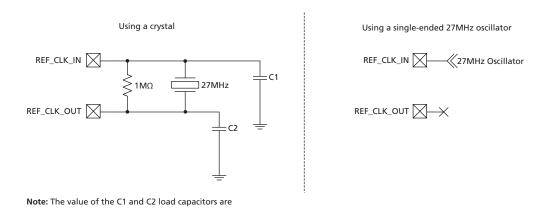

| AE35               | REF_CLK_IN          | _   | Connect a 27MHz crystal between this ball and REF_CLK_OUT. See Section 4.9 and Figure 3-5.                               |

| AF35               | REF_CLK_OUT         | _   | Connect a 27MHz crystal between this ball and REF_CLK_IN. See Section 4.9 and Figure 3-5. Leave NC if not used.          |

| External Clocks    |                     |     |                                                                                                                          |

| R15                | EXT_CLK2            | I   | External CML clock for Pattern Generator 1 (true). Leave NC if not used.                                                 |

| R35                | EXT_CLK0            | I   | External CML clock for Pattern Checker 0 (true). Leave NC if not used.                                                   |

| T15                | EXT_CLK2            | 1   | External CML clock for Pattern Generator 1 (complement). Leave NC if not used.                                           |

| T35                | EXT_CLK0            | ı   | External CML clock for Pattern Checker 0 (complement). Leave NC if not used.                                             |

| AH15               | EXT_CLK1            | ı   | External CML clock for Pattern Checker 1 (complement). Leave NC if not used.                                             |

| AH35               | EXT_CLK<br>_DIGITAL | I   | External CML clock for Pattern Transmitter 0/Digital Core (complement). Leave NC if not used.                            |

| AJ15               | EXT_CLK1            | I   | External CML clock for Pattern Checker 1 (true). Leave NC if not used.                                                   |

Table 1-1: Ball Descriptions (Continued)

| Ball #                                                                                             | Ball Name            | I/O       | Description                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------|----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AJ35                                                                                               | EXT_CLK<br>_DIGITAL  | I         | External CML clock for Pattern Transmitter 0/Digital Core (true). Leave NC i not used.                                                                                               |

| BH45                                                                                               | DIGITAL_CL_SEL       | I         | Clock select between external clock source (EXT_CLK_DIGITAL) and interna VCO (VCO_DIGITAL). This pin has a weak internal pull-up, and should be pulled LOW to use an external clock. |

| Temperature Sensors                                                                                |                      |           |                                                                                                                                                                                      |

| E8                                                                                                 | DTHERMA3             | _         | Thermometer 3 diode terminals. See Section 4.8. Leave NC if not used.                                                                                                                |

| F9                                                                                                 | DTHERMK3             | _         | Thermometer 3 diode terminals. See Section 4.8. Leave NC if not used.                                                                                                                |

| H45                                                                                                | DTHERMA0             | _         | Thermometer 0 diode terminals. See Section 4.8. Leave NC if not used.                                                                                                                |

| J44                                                                                                | DTHERMK0             | _         | Thermometer 0 diode terminals. See Section 4.8. Leave NC if not used.                                                                                                                |

| BA6                                                                                                | DTHERMK2             | _         | Thermometer 2 diode terminals. See Section 4.8. Leave NC if not used.                                                                                                                |

| BB5                                                                                                | DTHERMA2             | _         | Thermometer 2 diode terminals. See Section 4.8. Leave NC if not used.                                                                                                                |

| BD41                                                                                               | DTHERMK1             | _         | Thermometer 1 diode terminals. See Section 4.8. Leave NC if not used.                                                                                                                |

| BE42                                                                                               | DTHERMA1             | _         | Thermometer 1 diode terminals. See Section 4.8. Leave NC if not used.                                                                                                                |

| Monitors                                                                                           |                      |           |                                                                                                                                                                                      |

| A44                                                                                                | MON0                 | 0         | Serial monitoring output 0 (complement). Leave NC if not used.                                                                                                                       |

| A45                                                                                                | MON0                 | 0         | Serial monitoring output 0 (true). Leave NC if not used.                                                                                                                             |

| BJ5                                                                                                | MON1                 | 0         | Serial monitoring output 1 (true). Leave NC if not used.                                                                                                                             |

| BJ6                                                                                                | MON1                 | 0         | Serial monitoring output 1 (complement). Leave NC if not used.                                                                                                                       |

| External Pattern Gener                                                                             | ators                |           |                                                                                                                                                                                      |

| E1                                                                                                 | EXT_PG1              | I         | Serial pattern generator input 1 (complement). Leave NC if not used.                                                                                                                 |

| F1                                                                                                 | EXT_PG1              | I         | Serial pattern generator input 1 (true). Leave NC if not used.                                                                                                                       |

| BD49                                                                                               | EXT_PG0              | I         | Serial pattern generator input 0 (true). Leave NC if not used.                                                                                                                       |

| BE49                                                                                               | EXT_PG0              | I         | Serial pattern generator input 0 (complement). Leave NC if not used.                                                                                                                 |

| Reserved - Do Not Con                                                                              | nect                 |           |                                                                                                                                                                                      |

| B45, C44, D7, E2, F3,<br>G46, AL32, AL33, AL34,<br>AL35, AR34, BC4, BD47,<br>BE48, BF43, BG6, BH5, | RSV_DNC              | _         | Reserved. Do not connect.                                                                                                                                                            |

| SDI/SDO                                                                                            |                      |           |                                                                                                                                                                                      |

| Refer to the GX3290 (and                                                                           | family) Crosspoint B | all Guide | e for a detailed list of SDI and SDO balls.                                                                                                                                          |

| Power                                                                                              |                      |           |                                                                                                                                                                                      |

|                                                                                                    |                      |           | e for a detailed list of power supply balls.                                                                                                                                         |

Refer to the GX3290 (and family) Crosspoint Ball Guide for a detailed list of ground balls.

# 2. Electrical Characteristics

# 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                                                                                                               | Value                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Supply Voltage (VDD_18)                                                                                                                 | -0.3V to +2.1V                                                                            |

| Supply Voltage (VCC_IN1, VCC_IN2, VCC_25_A, VDD_25, VDDIO_D, VCC_OUT1, VCC_OUT2, VCC_25_REF_CLK, VCC_25_VCO0, VCC_25_VCO1, VCC_25_VCO2) | -0.3V to +2.8V                                                                            |

| loout Valtora Banga                                                                                                                     | -0.3 to (0.3 + min[VCC_IN1,<br>VCC_25_A])V<br>for even numbered SDI inputs and<br>EXT_PG0 |

| Input Voltage Range                                                                                                                     | -0.3 to (0.3 + min[VCC_IN2,<br>VCC_25_A])V<br>for odd numbered SDI inputs and<br>EXT_PG1  |

| ESD Voltage (HBM; all balls)                                                                                                            | 1kV                                                                                       |

| ESD Voltage (CDM; all balls)                                                                                                            | 100V                                                                                      |

| Storage Temperature Range                                                                                                               | -50°C to +125°C                                                                           |

| Operating Temperature Range                                                                                                             | 0°C to 85°C                                                                               |

| Solder Reflow Temperature                                                                                                               | 245°C                                                                                     |

# **2.2 Recommended Operating Conditions**

**Table 2-2: Recommended Operating Conditions**

| Parameter                          | Symbol                      | Min                                                                                                                                                                                                                                                                   | Тур | Max   | Units | Notes |

|------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|-------|

|                                    | VCC_25_A,<br>VCC_25_REF_CLK | 2.375                                                                                                                                                                                                                                                                 | 2.5 | 2.625 | V     | 1     |

|                                    |                             | 1.14                                                                                                                                                                                                                                                                  | 1.2 | 1.26  | V     | 2     |

|                                    | VCC_IN1, VCC_IN2            | 1.71                                                                                                                                                                                                                                                                  | 1.8 | 1.89  | V     | 3     |

| Operating Power Supply             | -                           | 2.375                                                                                                                                                                                                                                                                 | 2.5 | 2.625 | V     | 1     |

|                                    |                             | 1.14                                                                                                                                                                                                                                                                  | 1.2 | 1.26  | V     | 2     |

| Operating Power Supply             | VCC_OUT1,<br>VCC_OUT2       | 1.14 1.2 1.26 V 2 1, VCC_IN2 1.71 1.8 1.89 V 3 2.375 2.5 2.625 V 1  1.14 1.2 1.26 V 2 1.71 1.8 1.89 V 3 2.375 2.5 2.625 V 1 2.0UT1, 1.71 1.8 1.89 V 3 2.375 2.5 2.625 V 1  DD_18 1.71 1.8 1.89 V 3 DIO_D 18 1.71 1.8 1.89 V 3 2.375 2.5 2.625 V 1 2.375 2.5 2.625 V 1 | 3   |       |       |       |

|                                    | _                           |                                                                                                                                                                                                                                                                       | 1   |       |       |       |

|                                    | VDD_18                      | 1.71                                                                                                                                                                                                                                                                  | 1.8 | 1.89  | V     | 3     |

|                                    | VDDIO D                     | 1.71                                                                                                                                                                                                                                                                  | 1.8 | 1.89  | V     | 3     |

|                                    | ם_סומטי                     | 2.375                                                                                                                                                                                                                                                                 | 2.5 | 2.625 | V     | 1     |

|                                    | VDD_25                      | 2.375                                                                                                                                                                                                                                                                 | 2.5 | 2.625 | V     | 1     |

| Operating Temperature Range (case) | T <sub>OP</sub>             | 0                                                                                                                                                                                                                                                                     | 25  | 85    | °C    | _     |

| Start-up Temperature Range         | T <sub>SU</sub>             | -40                                                                                                                                                                                                                                                                   | _   | 85    | °C    | _     |

#### Notes:

- 1. 2.5V supply.

- 2. 1.2V supply.

- 3. 1.8V supply.

# 2.3 DC Electrical Characteristics

**Table 2-3: DC Electrical Characteristics**

| Parameter           | Symbol   | Conditions                                                                                                                                                                                             | Min                                                                                | Тур   | Max | Units | Note |

|---------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|-----|-------|------|

| System              |          |                                                                                                                                                                                                        |                                                                                    |       |     |       |      |

|                     |          | All channels active, VCC_IN[1,2] = VCC_OUT[1,2] = 1.2V $\pm$ 5%, $\Delta$ V <sub>OD</sub> = 200mV, $\Delta$ V <sub>SDI</sub> = 800mVppd, de-emphasis=6, without Pattern Generator/Checker, AC-coupled  | _                                                                                  | 21.47 | 24  | W     | 1    |

|                     |          | All channels active, VCC_IN[1,2] = VCC_OUT[1,2] = 1.2V $\pm$ 5%, $\Delta$ V <sub>OD</sub> = 400mV, $\Delta$ V <sub>SDI</sub> = 800mVppd, de-emphasis=6, without Pattern Generator/Checker, AC-coupled  | _                                                                                  | 23.28 | _   | W     | 1    |

| Power               | P        | All channels active, VCC_IN[1,2] = VCC_OUT[1,2] = 2.5V $\pm$ 5%, $\Delta$ V <sub>OD</sub> = 800mV, $\Delta$ V <sub>SDI</sub> = 800mVppd, de-emphasis=6, without Pattern Generator/Checker, AC-coupled  | _                                                                                  | 26.82 | 31  | W     | 1    |

|                     |          | All channels active, VCC_IN[1,2] = VCC_OUT[1,2] = 2.5V $\pm$ 5%, $\Delta$ V <sub>OD</sub> = 1200mV, $\Delta$ V <sub>SDI</sub> = 800mVppd, de-emphasis=6, without Pattern Generator/Checker, AC-coupled | _                                                                                  | 29.36 | 34  | W     | 1    |

|                     |          | PRBS Generator/Checker                                                                                                                                                                                 | _                                                                                  | 1.86  | _   | W     | _    |

| Power in Reset Mode | Р        | RESET = 0                                                                                                                                                                                              | _                                                                                  | 0.5   | _   | W     | _    |

| Current - VCC 25 A  | ICC 25 A | With de-emphasis,<br>without Pattern<br>Generator/Checker                                                                                                                                              | _                                                                                  | 8.1   | 9.5 | А     | _    |

| Current - VCC_25_A  | ICC_25_A | Without de-emphasis,<br>without Pattern<br>Generator/Checker                                                                                                                                           | — 23.28 — W  — 26.82 31 W  — 29.36 34 W  ut  er — 1.86 — W  — 0.5 — W  — 8.1 9.5 A | А     |     |       |      |

**Table 2-3: DC Electrical Characteristics (Continued)**

| Parameter                             | Symbol   | Conditions                                                                               | Min   | Тур  | Max  | Units       | Note |

|---------------------------------------|----------|------------------------------------------------------------------------------------------|-------|------|------|-------------|------|

| Current VCC IN1                       | ICC IN1  | All inputs active,<br>ΔV <sub>SDI</sub> = 1.2Vppd,<br>DC-coupled                         | _     | 0.9  | _    | А           | 2    |

|                                       | ICC_IN1  | All inputs active,<br>$\Delta V_{SDI} = 1.2 Vppd$ ,<br>AC-coupled                        | -0.2  | _    | 0    | А           | 3    |

| Course NGC IN2                        | ICC IND  | All inputs active,<br>ΔV <sub>SDI</sub> = 1.2Vppd,<br>DC-coupled                         | _     | 0.9  | _    | A A A A A A | 2    |

| Current - VCC_IN2                     | ICC_IN2  | All inputs active,<br>$\Delta V_{SDI} = 1.2 Vppd$ ,<br>AC-coupled                        | -0.2  | _    | 0    | А           | 3    |

| Current - VCC_IN2  Current - VCC_OUT1 |          | VCC_OUT1 = 1.2V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 200mV, with De-emphasis  | _     | 0.16 | 0.20 | А           | 4    |

|                                       |          | VCC_OUT1 = 1.2V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 400mV, with De-emphasis  | _     | 0.30 |      | А           | 4    |

|                                       |          | VCC_OUT1 = 1.2V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 800mV, with De-emphasis  | _     | 0.56 | _    | А           | 4, 5 |

|                                       | ICC_OUT1 | VCC_OUT1 = 2.5V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 200mV, with De-emphasis  | _     | 0.17 | _    | А           | 4    |

|                                       |          | VCC_OUT1 = 2.5V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 400mV, with De-emphasis  | - 0.9 | _    | А    | 4           |      |

|                                       |          | VCC_OUT1 = 2.5V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 800mV, with De-emphasis  | _     | 0.62 | 0.75 | А           | 4    |

|                                       |          | VCC_OUT1 = 2.5V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 1200mV, with De-emphasis | _     | 0.82 | 1.15 | Α           | 4    |

**Table 2-3: DC Electrical Characteristics (Continued)**

| Parameter                 | Symbol              | Conditions                                                                                 | Min | Тур  | Max  | Units | Note |

|---------------------------|---------------------|--------------------------------------------------------------------------------------------|-----|------|------|-------|------|

|                           |                     | VCC_OUT2 = 1.2V $\pm 5\%$ , all outputs active, $\Delta V_{OD} = 200$ mV, with De-emphasis | _   | 0.16 | 0.20 | Α     | 4    |

|                           |                     | VCC_OUT2 = 1.2V $\pm 5\%$ , all outputs active, $\Delta V_{OD} = 400$ mV, with De-emphasis | _   | 0.30 | _    | Α     | 4    |

|                           |                     | VCC_OUT2 = 1.2V $\pm 5\%$ , all outputs active, $\Delta V_{OD} = 800$ mV, with De-emphasis | _   | 0.56 | _    | А     | 4, 5 |

| Current - VCC_OUT2        | ICC_OUT2            | VCC_OUT2 = 2.5V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 200mV, with De-emphasis    | _   | 0.17 | _    | А     | 4    |

|                           |                     | VCC_OUT2 = 2.5V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 400mV, with De-emphasis    | _   | 0.30 | _    | А     | 4    |

|                           |                     | VCC_OUT2 = 2.5V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 800mV, with De-emphasis    | _   | 0.62 | 0.75 | А     | 4    |

|                           |                     | VCC_OUT2 = 2.5V $\pm$ 5%, all outputs active, $\Delta V_{OD}$ = 1200mV, with De-emphasis   | _   | 0.82 | 1.15 | Α     | 4    |

| Current - VCC_25_REF_CLK  | ICC_25<br>_REF_CLK  |                                                                                            | _   | 20   | 40   | mA    | _    |

| Current - VCC_VCO_DIGITAL | ICC_VCO<br>_DIGITAL |                                                                                            | _   | 6    | 10   | mA    | _    |

| Current - VCC_25_VCO0     | ICC_25<br>_VCO0     |                                                                                            | _   | 6    | 10   | mA    | _    |

| Current - VCC_25_VCO1     | ICC_25<br>_VCO1     |                                                                                            | _   | 6    | 10   | mA    | _    |

| Current - VCC_25_VCO2     | ICC_25<br>_VCO2     |                                                                                            | _   | 6    | 10   | mA    | _    |

| Current - VDD_18          | IDD_18              | VDD_18 = 1.8V±5%                                                                           | _   | 260  | 750  | mA    | _    |

| Current - VDD_25          | IDD_25              | VDD_25 = 2.5V±5%                                                                           | _   | 20   | 40   | mA    | _    |

| Current - VDDIO_D         |                     | VDDIO_D = $1.8V\pm5\%$ , all inputs active (15pF load)                                     |     | 50   | 100  | mA    | _    |

| Carrent - VDDIO_D         | IDDIO_D             | VDDIO_D = 2.5V±5%,<br>all inputs active<br>(15pF load)                                     | _   | 70   | 140  | mA    | _    |

**Table 2-3: DC Electrical Characteristics (Continued)**

| Parameter                                | Symbol           | Conditions                                                                                                                  | Min                                                 | Тур | Max                                                 | Units            | Note           |

|------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----------------------------------------------------|------------------|----------------|

| High-speed Inputs/Outputs                |                  |                                                                                                                             |                                                     |     |                                                     |                  |                |

| Carial Input Tarmination                 |                  | Differential                                                                                                                | _                                                   | 100 | _                                                   | Ω                | . 6            |

| Serial Input Termination                 |                  | Single-ended                                                                                                                | _                                                   | 50  | _                                                   | Ω                | . 0            |

| Serial Output Termination                |                  | Differential                                                                                                                | _                                                   | 100 | _                                                   | Ω                | _              |

| Serial Input Common Mode<br>Voltage      | V <sub>ICM</sub> | $VCC_IN[1,2] = 1.2V\pm5\%,$<br>$VCC_IN[1,2] = 1.8V\pm5\%,$<br>$VCC_IN[1,2] = 2.5V\pm5\%,$<br>terminated to<br>$VCC_IN[1,2]$ | VCC_IN<br>[1,2] -<br>(ΔV <sub>SDI</sub><br>_max/4)  | _   | VCC_IN<br>[1,2] -<br>(ΔV <sub>SDI</sub><br>_min/4)  | V                | 7, 8,<br>9, 10 |

| Serial Output Common Mode<br>Voltage     | V <sub>OCM</sub> | VCC_OUT[1,2] = 1.2V±5%,<br>VCC_OUT[1,2] = 1.8V±5%,<br>VCC_OUT[1,2] = 2.5V±5%                                                | VCC_OUT<br>[1,2] -<br>(ΔV <sub>OD</sub> _<br>max/4) | _   | VCC_OUT<br>[1,2] -<br>(ΔV <sub>OD</sub> _<br>min/4) | V                | _              |

| Host Interface                           |                  |                                                                                                                             |                                                     |     |                                                     |                  |                |

| Logic HIGH voltage on digital input pins | V <sub>IH</sub>  |                                                                                                                             | 0.7 x<br>VDDIO_D                                    | _   | VDDIO_D<br>+ 0.3                                    | V                | 11             |

| Logic LOW voltage on digital input pins  | V <sub>IL</sub>  |                                                                                                                             | -0.3                                                | _   | 0.3 x<br>VDDIO_D                                    | V                | 11             |

| Outrout Lawis LOW                        | V                | I <sub>OL</sub> = 2mA,<br>2.5V operation                                                                                    | _                                                   | _   | 0.7                                                 | V                | 11             |

| Output Logic LOW                         | V <sub>OL</sub>  | I <sub>OL</sub> = 2mA,<br>1.8V operation                                                                                    | _                                                   | _   | 0.45                                                | V                | 11             |

| Outrout Lawis IIIGU                      | V                | I <sub>OH</sub> = -2mA,<br>2.5V operation                                                                                   | 1.7                                                 | _   | _                                                   | Ω<br>Ω<br>V<br>V | 11             |

| Output Logic HIGH                        | V <sub>OH</sub>  | I <sub>OH</sub> = -2mA,<br>1.8 operation                                                                                    | 1.35                                                | _   | _                                                   | V                | 11             |

#### Notes:

- 1. Total Maximum Power is lower than individual maximum currents multiplied by individual maximum supply voltages because the individual maximum currents can not occur simultaneously (they occur at different conditions).

- 2. The ICC\_IN1 and ICC\_IN2 current flows out of the GX3246 and into the input signal source, and is subject to variability in that source. Some variability in input signal source current draw should be assumed, and up to ±15% is possible.

- 3. When the common mode termination points for AC-coupled inputs are connected to VCC\_IN1, VCC\_IN2, the GX3246 equalizer input bias currents can lead to current flowing out of the VCC\_IN1, VCC\_IN2 supply pins.

- 4. Currents apply for output DC-coupled applications. When AC-coupled, the current draw may be increased by up to 2x.

- 5. For DC-coupled applications only.

- 6. Input termination is selectable between  $100\Omega$  differential and  $50\Omega$  single-ended. See Section 3.

- 7. DC common mode current into/out of each EQ input differential pair should not exceed 14mA, and the current into/out of each half of the differential pair should not exceed 14mA.

- 8. No more than VCC\_IN[1,2]  $\Delta V_{SDI\_actual}/4$ .

- 9. Where it is understood that VCC\_IN[1,2] have a ±5% tolerance.

- 10.In no case should either side of the input differential pair be allowed to rise above VCC\_25\_A + 0.3V or fall below -0.3V.

- 11. Specifications relate to all host interface pins.

# 2.4 AC Electrical Characteristics

**Table 2-4: AC Electrical Characteristics**

| Parameter                                         | Symbol                         | Conditions                                         | Min  | Тур  | Max  | Units             | Notes |

|---------------------------------------------------|--------------------------------|----------------------------------------------------|------|------|------|-------------------|-------|

| System                                            |                                |                                                    |      |      |      |                   |       |

| Serial Input Data Rate                            | DR <sub>SDO</sub>              | _                                                  | _    | _    | 3.5  | Gb/s              | _     |

| Propagation Delay                                 | t <sub>P</sub>                 | _                                                  | _    | _    | 6    | ns                | 1     |

| Propagation Delay Difference                      | $\Delta t_{P}$                 | Between any two channels                           | _    | _    | 5.5  | ns                | 1     |

| High-speed Inputs/Outputs                         |                                |                                                    |      |      |      |                   |       |

| Output Switch Time using Update<br>Enable Strobes |                                |                                                    | 0.9  | _    | 1.8  | μs                | 2     |

| Input Voltage Swing                               | $\Delta V_{SDI}$               | _                                                  | 100  | _    | 1200 | mVppd             | _     |

|                                                   |                                | VCC_OUT[1,2] = 1.2V±5%,<br>Output = 200mVppd       | 150  | 225  | 300  | mVppd             | _     |

|                                                   |                                | VCC_OUT[1,2] = 1.2V±5%,<br>Output = 400mVppd       | 300  | 450  | 600  | mVppd             | _     |

|                                                   | $\Delta V_{OD}$                | VCC_OUT[1,2] = 1.2V±5%,<br>Output = 800mVppd       | 600  | 900  | 1200 | mVppd             | 3     |

|                                                   |                                | VCC_OUT[1,2] = 1.8V±5%,<br>Output = 200mVppd       | 150  | 225  | 300  | mVppd             | _     |

| Output Voltage Swing                              |                                | $VCC_OUT[1,2] = 1.8V\pm5\%$ , Output = 400mVppd    | 300  | 450  | 600  | mVppd             | _     |

|                                                   | ∆v0D                           | VCC_OUT[1,2] = 1.8V±5%<br>Output = 800mVppd        | 600  | 900  | 1200 | mVppd             | _     |

|                                                   |                                | VCC_OUT[1,2] = 2.5V±5%,<br>Output = 200mVppd       | 150  | 225  | 300  | mVppd             | _     |

|                                                   |                                | $VCC_OUT[1,2] = 2.5V\pm5\%$ ,<br>Output = 400mVppd | 300  | 450  | 600  | mVppd             | _     |

|                                                   |                                | VCC_OUT[1,2] = 2.5V±5%,<br>Output = 800mVppd       | 600  | 900  | 1200 | mVppd             | _     |

|                                                   |                                | VCC_OUT[1,2] = 2.5V±5%,<br>Output = 1200mVppd      | 1000 | 1350 | 1700 | mVppd             | _     |

| Output Rise/Fall Time                             | t <sub>r</sub> /t <sub>f</sub> | All output swings.<br>20% to 80%.                  | _    | _    | 150  | ps                |       |

| Duty Cycle Distortion                             |                                | All data rates, all output swings.                 | -50  |      | +50  | ps                |       |

| Additive Jitter                                   |                                | All inputs active,<br>peak-to-peak (PRBS 31)       | _    | _    | 60   | ps <sub>p-p</sub> | _     |

| Input Trace Equalization                          |                                |                                                    | 0    | _    | 12   | dB                | 4     |

| Output De-Emphasis Satting                        |                                | Range                                              | 0    | _    | 11.2 | dB                | 4     |

| Output De-Emphasis Setting                        |                                | Maximum Setting                                    | 9    |      | _    | dB                | 4     |

**Table 2-4: AC Electrical Characteristics (Continued)**

| Parameter                        | Symbol | Conditions | Min | Тур | Max   | Units | Notes   |

|----------------------------------|--------|------------|-----|-----|-------|-------|---------|

| Host Interface                   |        |            |     |     |       |       |         |

| Parallel Rate of Operation       |        |            | 0.1 | _   | 112.5 | Mop/s | 5, 6, 7 |

| Serial Interface Operating Speed |        |            | 0.1 | _   | 25    | MHz   | 5, 8    |

#### Notes:

- 1. See Section 4.4 for more details.

- 2. This parameter is the time it takes for the outputs to change to a new switch matrix configuration when the corresponding strobe signal assigned to that output is asserted.

- 3. DC-coupled.

- 4. Selectable, maximum gain occurs at 3Gb/s (or 1.5GHz).

- 5. Specifications relate to all host interface pins.

- 6. Millions of operations per second.

- 7. For detailed timing specifications, see Section 4.12.1.

- 8. For detailed timing specifications, see Section 4.12.2.

# 3. Input/Output Equivalent Circuits

**Note:** Please refer to the following supplementary documents: Crosspoint Design Guide and EB-GX3290 Schematics, PCB Layout and Bill of Materials.

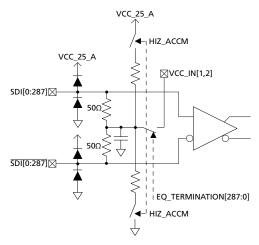

Figure 3-1: Equalizer Input Equivalent Circuit (includes the EXT\_PG0 & EXT\_PG1 inputs)

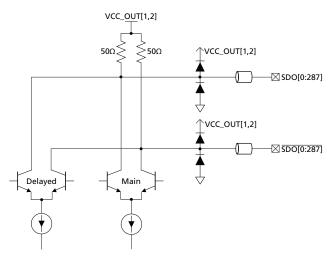

Figure 3-2: Trace Driver Output Equivalent Circuit (includes the MON0 & MON1 outputs)

Note: the MON0 and MON1 outputs are terminated to the VCC\_25\_A supply.

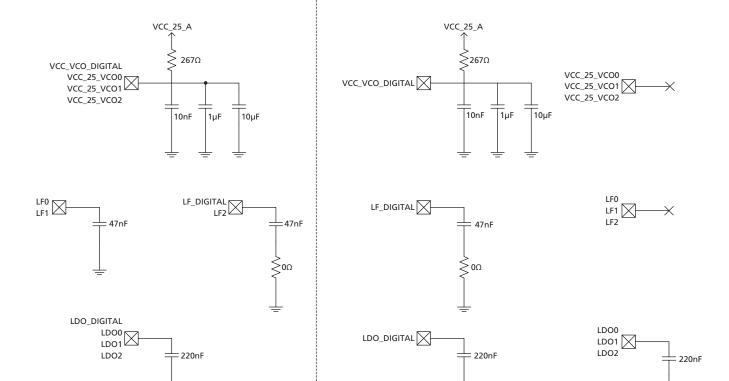

If the internal temperature ADCs, pattern generators, and checkers are used, these connections are required.

If the internal temperature ADCs, pattern generators, and checkers are not used, only these connections are required.

Note 1: Each of the VCC\_VCO\_DIGITAL, VCC\_VCO0, VCC\_VCO1, and VCC\_VCO2 pins require an independent RC network.

Note 2: The LF\_DIGITAL and LF2 pins each require an independent RC network.

Note 3: The LF0 and LF1 pins each require an independent capacitor to ground.

Note 4: Each of the LDO\_DIGITAL, LDO0, LDO1, and LDO2 pins require an independent capacitor to ground.

Note 5: VCC\_VCO\_DIGITAL, LF\_DIGITAL and LDO\_DIGITAL used for pattern generator TX0, digital communication (GSPI and APPI), and the internal temperature ADC for JNCTN\_TEMP\_1. VCC\_VCO\_DIGITAL, LF\_DIGITAL and LDO\_DIGITAL must always be connected.

Note 6: VCC\_25\_VCO0, LF0, LDO0 used for pattern checker RX0 and the internal temperature ADC for JNCTN\_TEMP\_0.

If VCC\_25\_VCO0, LF0, and LD00 are not connected, pattern checker RX0 and the internal temperature ADC for JNCTN\_TEMP\_0 will not operate.

Note 7: VCC\_25\_VCO1, LF1, LDO1 used for pattern checker RX1 and the internal temperature ADC for JNCTN\_TEMP\_2.

If VCC\_25\_VCO1, LF1, and LDO1 are not connected, pattern checker RX1 and the internal temperature ADC for JNCTN\_TEMP\_2 will not operate.

Note 8: VCC\_25\_VCO2, LF2, LDO2 used for pattern generator TX1 and the internal temperature ADC for JNCTN\_TEMP\_3.

If VCC\_25\_VCO2, LF2, and LDO2 are not connected, pattern generator TX1 and the internal temperature ADC for JNCTN\_TEMP\_3 will not operate.

Figure 3-3: Required connections for VCC\_VCO\_DIGITAL, VCC\_25\_VCO0, VCC\_25\_VCO1, VCC\_25\_VCO2, LF\_DIGITAL, LF0, LF1, LF2, LDO\_DIGITAL, LDO0, LDO1 and LDO2

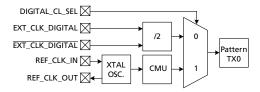

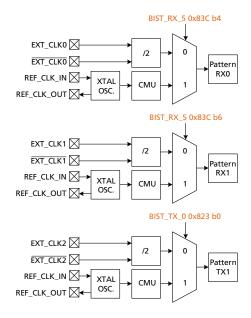

**Note:** The clock used to drive Pattern Generator TX0 is also used to derive the clock timing for the digital core. Therefore, GSPI/APPI interface timing andupdate timing will track the external clock frequency if one is selected from the EXT\_CLK\_DIGITAL/EXT\_CLK\_DIGITAL pins for Pattern Generator TX0.

Figure 3-4: PRBS Generator/Checker Clock Selection

Figure 3-5: Crystal Oscillator

dependent on the chosen crystal.

# 4. Detailed Description

### 4.1 Serial Data Input

Each of the GX3246 SDI inputs provide on-chip  $100\Omega$  differential terminations. Each is compatible with input differential amplitudes from 100 mVppd to 1200 mVppd, and input signal sources having CML outputs referred to DC supplies of 1.2V, 1.8V or 2.5V. Note that for AC-coupled inputs, the recommended supply voltage for VCC\_IN1 and VCC\_IN2 is 1.8V.

Each of the 290 SDI input channels include frequency domain equalization, independently-programmable to one of four levels, to compensate from 0 to 47 inches (119 cm) of FR4 trace at 3Gb/s. The boost at the 1.5GHz Nyquist frequency, and recommended trace length range, are shown under EQ\_BOOST[287:0], EXT PG0 EQ BOOST, EXT PG1 EQ BOOST in Table 4-1. See Figure 3-1.

Each input can be powered-down independently using the corresponding EQ\_POWERDOWN[287:0] or EXT\_PG0\_EQ\_POWERDOWN or EXT\_PG1\_EQ\_POWERDOWN bit.

To accommodate input signal sources with 1.2V supplies and 1200mVppd signal amplitudes, the input common mode point should be terminated to the respective VCC\_IN1 or VCC\_IN2 supply.

The common mode termination connection to the respective VCC\_IN1 or VCC\_IN2 supply of each input can be independently controlled using the EQ\_TERMINATION[287:0] or EXT\_PG0\_EQ\_TERMINATION or EXT\_PG1\_EQ\_TERMINATION bit (see Figure 3-1 and Table 4-1).

**Note 1:** When the HIZ\_ACCM bit is set (register address 0x400h bit 0), inputs with their common mode termination not connected to VCC\_IN1 or VCC\_IN2 are connected to an internal common mode bias.

When an input EQ is powered-down, its common mode termination is automatically disconnected from the corresponding VCC IN1 or VCC IN2.

For each of the inputs, there are control parameters (register address 0x401h to 0x522h). See Table 4-1 below.

**Note 2:** The EXT\_PG01\_SOURCE\_PIN\_PRBSB and EXT\_PG1\_SOURCE\_PIN\_PRBSB bits in the TEST\_SETUP register must be set to connect the EXT\_PG0 and EXT\_PG1 pins to the matrix.

Table 4-1: Serial Data Input

| EQ_BOOST[287:0], EXT_PG0_EQ_BOOST and EXT_PG1_EQ_BOOST bits 1:0 (binary) | Boost Applied (@ nominal 1.5GHz) |                                    |

|--------------------------------------------------------------------------|----------------------------------|------------------------------------|

| 00                                                                       | 0dB boost                        | 0" to 6" (15 cm) trace             |

| 01                                                                       | 3.5dB boost                      | 6" (15 cm) to 16"<br>(40 cm) trace |

**Table 4-1: Serial Data Input (Continued)**

| EQ_BOOST[287:0], EXT_PG0_EQ_BOOST and EXT_PG1_EQ_BOOST bits 1:0 (binary)          | Boost Applied (@ nominal 1.5GHz)                                 |  |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| 10                                                                                | 7.6dB boost 16" (40 cm) to (89 cm) trac                          |  |

| 11                                                                                | 12dB boost 35" (89 cm) to (119 cm) trac                          |  |

| EQ_TERMINATION[287:0], EXT_PG0_EQ_TERMINATION and EXT_PG1_EQ_TERMINATION bits 3:3 | Input Termination Common Mode Point Switch to VCC_IN_1, VCC_IN_2 |  |

| 0                                                                                 | Open (see Figure 3-1)                                            |  |

| 1                                                                                 | Closed (see Figure 3-1)                                          |  |

| EQ_POWERDOWN[287:0], EXT_PG0_EQ_POWERDOWN and EXT_PG1_EQ_POWERDOWN bits 4:4       | Equalizer Power                                                  |  |

| 0                                                                                 | On                                                               |  |

| 1                                                                                 | Off                                                              |  |

# **4.2 Serial Data Output**

Each of the GX3246 SDI outputs have two on-chip  $50\Omega$  single-ended terminations, and can be programmed to output differential amplitudes of 200mVppd, 400mVppd or 800mVppd when the corresponding VCC\_OUT1 or VCC\_OUT2 is connected to either 1.2V or 1.8V, or 200mVppd, 400mVppd, 800mVppd, or 1200mVppd when the corresponding VCC\_OUT1 or VCC\_OUT2 is connected to 2.5V. The selection of the output swing is made using the corresponding OUTPUT\_SWING\_SET[287:0], MON0\_OUTPUT\_SWING\_SET or MON1\_OUTPUT\_SWING\_SET bits, shown in Table 4-3.

If the HIGH\_OP\_V bit is set when either the VCC\_OUT1 or VCC\_OUT2 supplies are 1.2V or 1.8V, the 800mVppd swing setting is no longer valid for that output bank. Swing settings for an output bank connected to a 2.5V supply are unaffected.

Table 4-2: HIGH\_OP\_V Swing Selection

| VCC OUTY                                                         | HIGH_OP_V = 0                              | HIGH_OP_V = 1 |   |

|------------------------------------------------------------------|--------------------------------------------|---------------|---|

| VCC_OUTx Supply Voltage Valid Output Swing (V) Selection (mVppd) | Valid Output Swing<br>Selection<br>(mVppd) | Note          |   |

| 1.2                                                              | 200, 400, 800                              | 200, 400      | 1 |

| 1.8                                                              | 200, 400, 800                              | 200, 400      | _ |

Table 4-2: HIGH OP V Swing Selection (Continued)

| VCC OUTx              | HIGH_OP_V = 0                              | HIGH_OP_V = 1                              |      |

|-----------------------|--------------------------------------------|--------------------------------------------|------|

| Supply Voltage<br>(V) | Valid Output Swing<br>Selection<br>(mVppd) | Valid Output Swing<br>Selection<br>(mVppd) | Note |

| 2.5                   | 200, 400, 800                              | 200, 400, 800, 1200                        | 2    |

#### Notes:

- 1. For an 800mVppd output swing when the corresponding VCC\_OUT1 or VCC\_OUT2 is connected to 1.2V, the output must be DC-coupled to a receiving device terminated to 1.2V.

- 2. When VCC\_OUT1 or VCC\_OUT2 is set to 2.5V, the HIGH\_OP\_V bit must be set to enable 1200mVppd swing selection.

Each of the 146 SDI output channels provide independently programmable de-emphasis, to compensate from 0 to 47 inches (119 cm) of FR4 trace at 3Gb/s. The selection of the amount of output de-emphasis is made using the corresponding OUTPUT\_DEEMPHASIS[287:0], MON0\_OUTPUT\_DEEMPHASIS or MON1\_OUTPUT\_DEEMPHASIS bits, shown in Table 4-3.

Each output can be independently powered-down by the setting of the corresponding bit: ACTIVE\_POWER\_DOWN[287:0], DYNAMIC\_POWER\_DOWN[287:0] together with the assigned strobe, MON0\_POWER\_DOWN, or MON1\_POWER\_DOWN.

The polarity of the signal at each output can be independently inverted by setting the corresponding bit: ACTIVE\_SIGNAL\_INVERT[287:0],

DYNAMIC\_SIGNAL\_INVERT[287:0] together with the assigned strobe, MON0\_SIGNAL\_INVERT, or MON1\_SIGNAL\_INVERT.

**Table 4-3: Serial Data Output**

| OUTPUT_SWING_SET[287:0], MON0_OUTPUT_SWING_SET and MON1_OUTPUT_SWING_SET bits 2:0 (binary)    | Output Swing               |

|-----------------------------------------------------------------------------------------------|----------------------------|

| 000                                                                                           | 200mVppd                   |

| 001                                                                                           | 400mVppd                   |

| 011                                                                                           | 800mVppd                   |

| 110                                                                                           | 1200mVppd                  |

| 111                                                                                           | Reserved. Do not use       |

|                                                                                               |                            |

| OUTPUT_DEEMPHASIS[287:0], MON0_OUTPUT_DEEMPHASIS and MON1_OUTPUT_DEEMPHASIS bits 5:3 (binary) | Level of De-emphasis       |

| MON0_OUTPUT_DEEMPHASIS and MON1_OUTPUT_DEEMPHASIS bits 5:3                                    | Level of De-emphasis Off   |

| MON0_OUTPUT_DEEMPHASIS and MON1_OUTPUT_DEEMPHASIS bits 5:3 (binary)                           | ·                          |

| MON0_OUTPUT_DEEMPHASIS and MON1_OUTPUT_DEEMPHASIS bits 5:3 (binary)                           | Off                        |

| MON0_OUTPUT_DEEMPHASIS and MON1_OUTPUT_DEEMPHASIS bits 5:3 (binary)  000  100                 | Off<br>12" (30 cm) nominal |

Table 4-3: Serial Data Output (Continued)

| ACTIVE_SIGNAL_INVERT[287:0], DYNAMIC_SIGNAL_INVERT[287:0], MON0_SIGNAL_INVERT or MON1_SIGNAL_INVERT | Status       |

|-----------------------------------------------------------------------------------------------------|--------------|

| 0                                                                                                   | Not inverted |

| 1                                                                                                   | Inverted     |

| ACTIVE_POWER_DOWN[287:0], DYNAMIC_POWER_DOWN[287:0], MON0_POWER_DOWN or MON1_POWER_DOWN             | Status       |

| 0                                                                                                   | On           |

| 1                                                                                                   | Off          |

### 4.3 Crosspoint Switch Matrix Operation

The crosspoint switch matrix routes the serial digital input signals (SDI[0:287]/ $\overline{\text{SDI}}$ [0:287], EXT\_PG0/ $\overline{\text{EXT}}$ PG0 or EXT\_PG1/ $\overline{\text{EXT}}$ PG1) to one or more serial digital outputs (SDO[0:287]/ $\overline{\text{SDO}}$ [0:287], MON0/ $\overline{\text{MON0}}$  or MON1/ $\overline{\text{MON1}}$ ). The matrix is configured on a per output basis. Each serial digital output can be configured to accept a signal from one serial digital input. Multiple serial digital outputs can accept input from the same serial digital input.

Updates to the switch matrix take place as soon as they are written to the host interface when controlling the device through the ACTIVE Configuration and Status Registers. These registers are the ACTIVE[287:0], MONO, and MON1 registers found in Section 2 of the Crosspoint (GX3290 and family) Reference Manual (for CSRs) document.

Before the ACTIVE[287:0], MON0, and MON1 registers at addresses 0x200h through 0x321h can be directly used to update the crosspoint switch matrix, an initialization procedure is required. One of the UPDATE\_EN[7:0] pins needs be toggled from a low state to a high state, and back to a low state again.

Alternatively, set the SOFTWARE\_UPDATE\_ENABLE bit in the CONTROL\_SETUP register at address 0xA00h to a value of 1, and then toggle one of the SOFT\_UPDATE\_EN[7:0] bits in the SOFT\_UPDATE\_CONTROL register at address 0xA01h from a value of 0 to a value of 1, and then back to a value of 0.

If the ACTIVE[287:0], MON0, and MON1 registers are not being directly written by the system controller, this procedure is not required. Reading from the ACTIVE[287:0], MON0, and MON1 registers will work regardless of whether or not the above procedure is executed.

Updating the crosspoint switch matrix using the **DYNAMIC[287:0]** registers (discussed below) does not require the initialization procedure described above.

The switch matrix can also be updated using double-buffering when controlling the device through the DYNAMIC Configuration and Status Registers. These registers are DYNAMIC[287:0] in Section 1 of the Crosspoint (GX3290 and family) Reference Manual (for CSRs) document.

When using dynamic configuration, updates to the switch matrix are first written to the DYNAMIC[287:0] registers where they are held until the corresponding update strobe signal, selected using the UPDATE\_SELECT[287:0] bits in the DYNAMIC[287:0] registers, changes state from LOW-to-HIGH.

The source for the update strobes can either be via external pins (UPDATE\_EN[7:0]) or register bits (SOFT\_UPDATE\_EN[7:0]) as selected by the setting of the SOFTWARE\_UPDATE\_ENABLE bit in the CONTROL\_SETUP register. Setting the SOFTWARE\_UPDATE\_ENABLE bit LOW causes the device to use the external UPDATE\_EN[7:0] pins as update strobes for the switch matrix. Setting the SOFTWARE\_UPDATE\_ENABLE bit HIGH causes the device to use the SOFT\_UPDATE\_EN[7:0] bits as update strobes for the switch matrix. See Section 6 of the Crosspoint (GX3290 and family) Reference Manual (for CSRs) document.

When the selected update strobe signal (or bit) transitions from LOW-to-HIGH, the state of all the outputs configured to respond to that update strobe signal (or bit) are updated at that time.

Regardless of which register set is used to configure the switch matrix, the current configuration of the matrix is always available by reading back the ACTIVE[287:0] registers.

**Note:** The MON0 and MON1 outputs can not be powered up/down, switched, or polarity inverted dynamically (Dynamic Configuration). They can only be configured in the Active Configuration mode described above using the settings in registers 0x320h and 0x321h, respectively. Also, the MON0 and MON1 outputs are terminated to the VCC\_25\_A supply.

## 4.4 Propagation Delay

The propagation delay is dependent on the path that the signal takes through the device. Although the delay difference from the shortest path to the longest path could be up to 5.5ns, this difference is at a minimum for connections from inputs numerically close together and on the same side of the device to outputs that are numerically close together and on the same side of the device. Propagation delay differences of less than 750ps can be expected when the inputs are adjacent in the ballout and the outputs are also adjacent in the ballout.

**Note:** The 750ps propagation delay difference (skew) between physically adjacent channels is guaranteed by simulation.

## 4.5 Using Multiple Strobes

The GX3246 has eight fully-independent update strobes.

Outputs 287 to 0 can be assigned to one of the eight strobes through the setting of the UPDATE\_SELECT bits in the corresponding DYNAMIC[287:0] register. The input signal selection, output power switching and signal inversion will take effect on the LOW-to-HIGH edge of its assigned strobe signal or bit. This allows different portions of the crosspoint to be switched at different points in time. This is particularly useful in systems supporting multiple data or video formats, where the switch point/time varies from format to format.

### 4.6 Pattern Generator and Pattern Checker

#### 4.6.1 Pattern Generator

**Note 1:** There are two pattern generator "Tx" blocks in the GX3246. In the following, wherever only TX0 is mentioned, the corresponding is also true for TX1.

**Note 2:** When the PRBS Generator is disabled, the generated signal does not completely terminate. The PRBS polynomial bits must be re-written in order to terminate the signal.