# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ne<mark>x</mark>peria

#### Important notice

Dear Customer,

On 7 February 2017 the former NXP Standard Product business became a new company with the tradename **Nexperia**. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets

In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below.

Instead of <u>http://www.nxp.com</u>, <u>http://www.philips.com/</u> or <u>http://www.semiconductors.philips.com/</u>, use <u>http://www.nexperia.com</u>

Instead of sales.addresses@www.nxp.com or sales.addresses@www.semiconductors.philips.com, use **salesaddresses@nexperia.com** (email)

Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below:

- © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved

Should be replaced with:

- © Nexperia B.V. (year). All rights reserved.

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via **salesaddresses@nexperia.com**). Thank you for your cooperation and understanding,

Kind regards,

Team Nexperia

# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC04 January 1995

#### HEF4016B gates

#### Quadruple bilateral switches

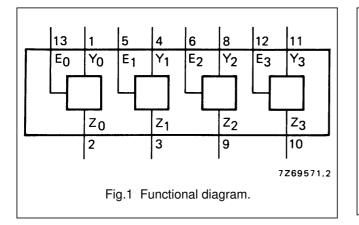

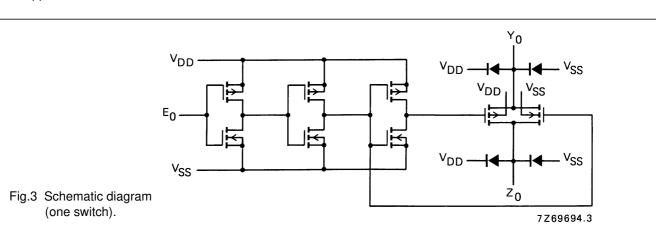

#### DESCRIPTION

The HEF4016B has four independent analogue switches (transmission gates). Each switch has two input/output terminals (Y/Z) and an active HIGH enable input (E). When E is connected to  $V_{DD}$  a low impedance bidirectional path between Y and Z is established (ON condition). When E is connected to  $V_{SS}$  the switch is disabled and a high

#### PINNING

| E <sub>0</sub> to E <sub>3</sub> | enable inputs          |

|----------------------------------|------------------------|

| $Y_0$ to $Y_3$                   | input/output terminals |

| $Z_0$ to $Z_3$                   | input/output terminals |

#### **APPLICATION INFORMATION**

Some examples of applications for the HEF4016B are:

- Signal gating

- Modulation

- Demodulation

- Chopper

# $V_{DD} = E_0 = E_3 + Y_3 + Z_3 + Z_2 + Y_2$ D = HEF4016B $Y_0 = Z_0 + Z_1 + Y_1 + E_1 + E_2 + V_{SS}$

Fig.2 Pinning diagram.

4

2 3

impedance between Y and Z is established (OFF

condition). Current through a switch will not cause

HEF4016BP(N): 14-lead DIL; plastic (SOT27-1)

HEF4016BD(F): 14-lead DIL; ceramic (cerdip) (SOT73)

HEF4016BT(D): 14-lead SO; plastic (SOT108-1)

(): Package Designator North America

#### RATINGS

| Limiting values in accordance with the Absolute Maximum System (IEC 1 | 34) |      |     |

|-----------------------------------------------------------------------|-----|------|-----|

| Power dissipation per switch                                          | Р   | max. | 100 |

| For other RATINGS see Family Specifications                           |     |      |     |

#### DC CHARACTERISTICS

$T_{amb}$  = 25 °C;  $V_{SS}$  = 0 V (unless otherwise specified)

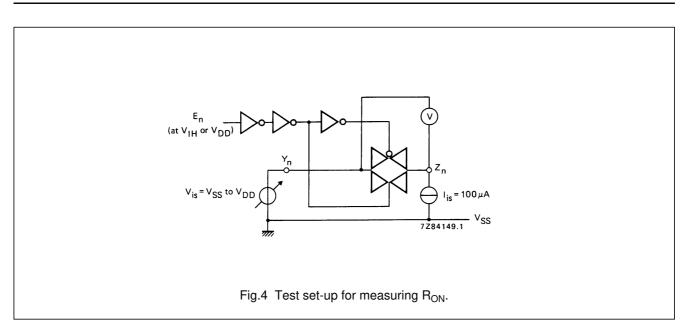

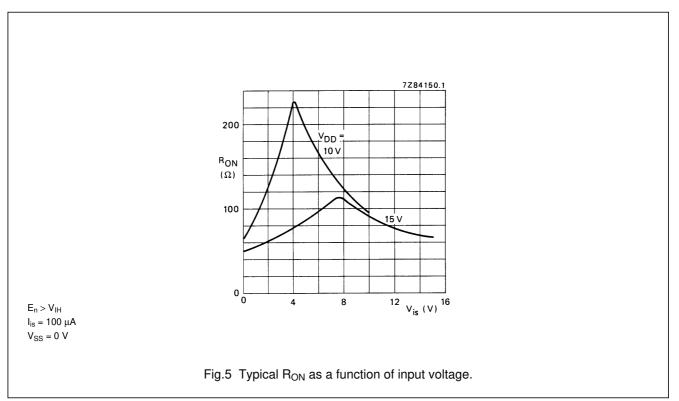

| PARAMETER         | V <sub>DD</sub><br>V | SYMBOL          | TYP. | MAX. | UNIT | CONDITIONS                                                                    |

|-------------------|----------------------|-----------------|------|------|------|-------------------------------------------------------------------------------|

|                   | 5                    |                 | 8000 | _    | Ω    | $E_n$ at V <sub>IH</sub> ; V <sub>is</sub> = 0 to V <sub>DD</sub> ; see Fig.4 |

| ON resistance     | 10                   | R <sub>ON</sub> | 230  | 690  | Ω    |                                                                               |

|                   | 15                   |                 | 115  | 350  | Ω    |                                                                               |

|                   | 5                    |                 | 140  | 425  | Ω    | $E_n$ at $V_{IH}$ ; $V_{is} = V_{SS}$ ; see Fig.4                             |

| ON resistance     | 10                   | R <sub>ON</sub> | 65   | 195  | Ω    |                                                                               |

|                   | 15                   |                 | 50   | 145  | Ω    |                                                                               |

|                   | 5                    |                 | 170  | 515  | Ω    | $E_n$ at $V_{IH}$ ; $V_{is} = V_{DD}$ ; see Fig.4                             |

| ON resistance     | 10                   | R <sub>ON</sub> | 95   | 285  | Ω    |                                                                               |

|                   | 15                   |                 | 75   | 220  | Ω    |                                                                               |

| 'Δ' ON resistance | 5                    |                 | 200  | _    | Ω    | $E_n$ at $V_{IH}$ ; $V_{is} = 0$ to $V_{DD}$ ; see Fig.4                      |

| between any two   | 10                   | $\Delta R_{ON}$ | 15   | _    | Ω    |                                                                               |

| channels          | 15                   |                 | 10   | —    | Ω    |                                                                               |

|                           | V <sub>DD</sub> |                   |      |      | T <sub>amb</sub> | (°C) |      |      |      |                                          |

|---------------------------|-----------------|-------------------|------|------|------------------|------|------|------|------|------------------------------------------|

| PARAMETER                 | V               | SYMBOL            | _    | 40   | +                | 25   | +    | 85   | UNIT | CONDITION                                |

|                           |                 |                   | MIN. | MAX. | MIN.             | MAX. | MIN. | MAX. |      |                                          |

| Quiescent                 | 5               |                   | -    | 1,0  | _                | 1,0  | _    | 7,5  | μA   | V <sub>SS</sub> = 0; all valid           |

| device                    | 10              | I <sub>DD</sub>   | -    | 2,0  | _                | 2,0  | _    | 15,0 | μA   | input combinations;                      |

| current                   | 15              |                   | _    | 4,0  | _                | 4,0  | _    | 30,0 | μA   | $V_I = V_{SS} \text{ or } V_{DD}$        |

| Input leakage             | 15              | ±1                | _    | _    | _                | 300  | _    | 1000 | nA   | E at V ar V                              |

| current at E <sub>n</sub> | 15              | ± I <sub>IN</sub> |      |      |                  |      |      |      | IIA  | $E_n$ at $V_{SS}$ or $V_{DD}$            |

| OFF-state leakage         | 5               |                   | _    | _    | _                | _    | _    | _    | nA   | E <sub>n</sub> at V <sub>IL</sub> ;      |

| current, any              | 10              | I <sub>OZ</sub>   | -    | _    | _                | _    | _    | _    | nA   | $V_{is} = V_{SS} \text{ or } V_{DD};$    |

| channel OFF               | 15              |                   | _    | _    | _                | 200  | _    | _    | nA   | $V_{os} = V_{DD} \text{ or } V_{SS}$     |

| E <sub>n</sub> input      | 5               |                   | _    | 1,5  | _                | 1,5  | _    | 1,5  | V    | switch OFF; see                          |

| voltage LOW               | 10              | V <sub>IL</sub>   | -    | 3,0  | _                | 3,0  | _    | 3,0  | V    | Fig.9 for I <sub>OZ</sub>                |

|                           | 15              |                   | -    | 4,0  | _                | 4,0  | _    | 4,0  | V    |                                          |

| E <sub>n</sub> input      | 5               |                   | 3,5  | _    | 3,5              | _    | 3,5  | _    | V    | low-impedance                            |

| voltage HIGH              | 10              | V <sub>IH</sub>   | 7,0  | _    | 7,0              | _    | 7,0  | _    | v    | between Y and Z (ON                      |

|                           | 15              |                   | 11,0 | -    | 11,0             | -    | 11,0 | -    | V    | condition)<br>see R <sub>ON</sub> switch |

## HEF4016B gates

mW

# HEF4016B gates

HEF4016B gates

#### **AC CHARACTERISTICS**

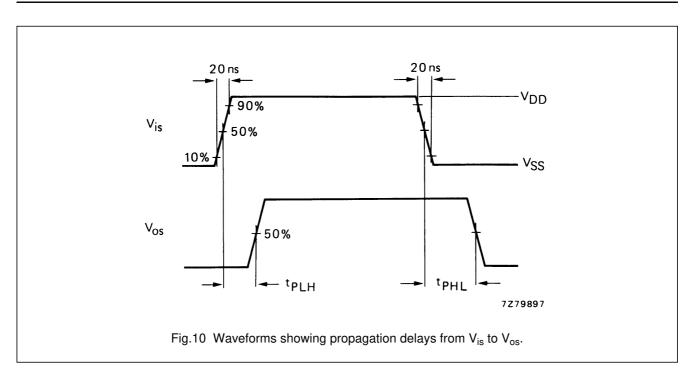

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C; input transition times  $\leq$  20 ns

|                       | V <sub>DD</sub><br>V | SYMBOL           | TYP. | MAX. |     |        |

|-----------------------|----------------------|------------------|------|------|-----|--------|

| Propagation delays    |                      |                  |      |      |     |        |

| $V_{is} \to V_{os}$   | 5                    |                  | 25   | 50   | ns  |        |

| HIGH to LOW           | 10                   | t <sub>PHL</sub> | 10   | 20   | ns  | note 1 |

|                       | 15                   |                  | 5    | 10   | ns  |        |

|                       | 5                    |                  | 20   | 40   | ns  |        |

| LOW to HIGH           | 10                   | t <sub>PLH</sub> | 10   | 20   | ns  | note 1 |

|                       | 15                   |                  | 5    | 10   | ns  |        |

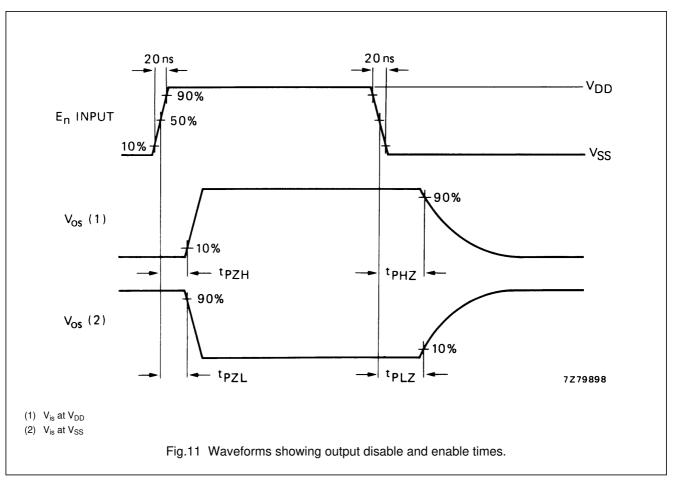

| Output disable times  |                      |                  |      |      |     |        |

| $E_n \to V_{os}$      | 5                    |                  | 90   | 130  | ns  |        |

| HIGH                  | 10                   | t <sub>PHZ</sub> | 80   | 110  | ns  | note 2 |

|                       | 15                   |                  | 75   | 100  | ns  |        |

|                       | 5                    |                  | 85   | 120  | ns  |        |

| LOW                   | 10                   | t <sub>PLZ</sub> | 75   | 100  | ns  | note 2 |

|                       | 15                   |                  | 75   | 100  | ns  |        |

| Output enable times   |                      |                  |      |      |     |        |

| $E_n \to V_{os}$      | 5                    |                  | 40   | 80   | ns  |        |

| HIGH                  | 10                   | t <sub>PZH</sub> | 20   | 40   | ns  | note 2 |

|                       | 15                   |                  | 15   | 30   | ns  |        |

|                       | 5                    |                  | 40   | 80   | ns  |        |

| LOW                   | 10                   | t <sub>PZL</sub> | 20   | 40   | ns  | note 2 |

|                       | 15                   |                  | 15   | 30   | ns  |        |

| Distortion, sine-wave | 5                    |                  | -    |      | %   |        |

| response              | 10                   |                  | 0,08 |      | %   | note 3 |

|                       | 15                   |                  | 0,04 |      | %   |        |

| Crosstalk between     | 5                    |                  | _    |      | MHz |        |

| any two channels      | 10                   |                  | 1    |      | MHz | note 4 |

|                       | 15                   |                  | _    |      | MHz |        |

| Crosstalk; enable     | 5                    |                  | _    |      | mV  |        |

| input to output       | 10                   |                  | 50   |      | mV  | note 5 |

|                       | 15                   |                  | -    |      | mV  |        |

| OFF-state             | 5                    |                  | _    |      | MHz |        |

| feed-through          | 10                   |                  | 1    |      | MHz | note 6 |

|                       | 15                   |                  | -    |      | MHz |        |

| ON-state frequency    | 5                    |                  | -    |      | MHz |        |

| response              | 10                   |                  | 90   |      | MHz | note 7 |

|                       | 15                   |                  | _    |      | MHz |        |

HEF4016B gates

#### Notes

$V_{is}\xspace$  is the input voltage at a Y or Z terminal, whichever is assigned as input.

$V_{os}$  is the output voltage at a Y or Z terminal, whichever is assigned as output.

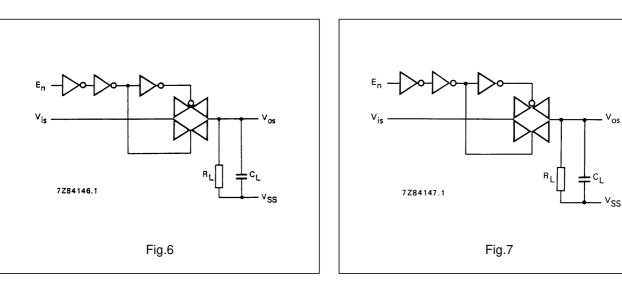

- 1.  $R_L = 10 \text{ k}\Omega$  to  $V_{SS}$ ;  $C_L = 50 \text{ pF}$  to  $V_{SS}$ ;  $E_n = V_{DD}$ ;  $V_{is} = V_{DD}$  (square-wave); see Figs 6 and 10.

- $\begin{array}{ll} \text{2.} & R_L = 10 \ \text{k}\Omega; \ \text{C}_L = 50 \ \text{pF} \ \text{to} \ \text{V}_{SS}; \ \text{E}_n = \text{V}_{DD} \ (\text{square-wave}); \\ & \text{V}_{is} = \text{V}_{DD} \ \text{and} \ R_L \ \text{to} \ \text{V}_{SS} \ \text{for} \ t_{\text{PHZ}} \ \text{and} \ t_{\text{PZH}}; \\ & \text{V}_{is} = \text{V}_{SS} \ \text{and} \ R_L \ \text{to} \ \text{V}_{DD} \ \text{for} \ t_{\text{PLZ}} \ \text{and} \ t_{\text{PZL}}; \ \text{see Figs 6 and 11.} \end{array}$

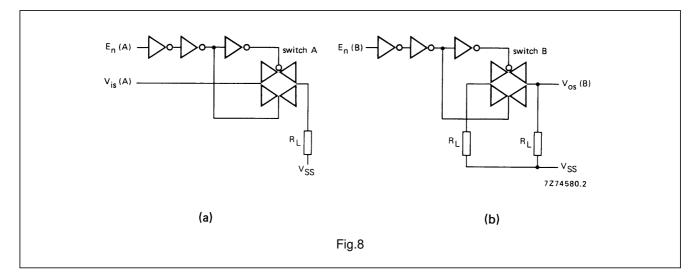

- 3.  $R_L = 10 \text{ k}\Omega$ ;  $C_L = 15 \text{ pF}$ ;  $E_n = V_{DD}$ ;  $V_{is} = \frac{1}{2}V_{DD(p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2}V_{DD}$ );  $f_{is} = 1 \text{ kHz}$ ; see Fig.7.

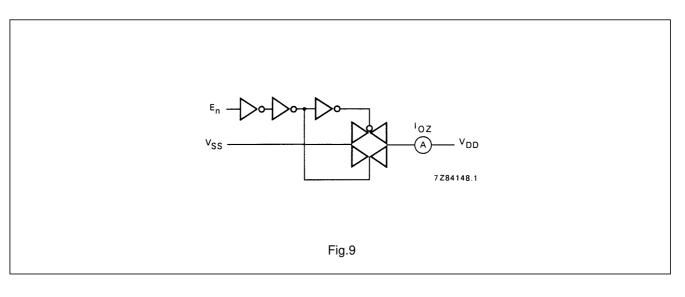

- 4.  $R_L = 1 \ k\Omega; \ V_{is} = \frac{1}{2} V_{DD(p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ );

20 log

$$\frac{V_{os}(B)}{V_{is}(A)}$$

= -50 dB;  $E_n(A)$  =  $V_{SS}$ ;  $E_n(B) = V_{DD}$ ; see Fig. 8.

- 5.  $R_L = 10 \text{ k}\Omega$  to  $V_{SS}$ ;  $C_L = 15 \text{ pF}$  to  $V_{SS}$ ;  $E_n = V_{DD}$  (square-wave); crosstalk is  $|V_{os}|$  (peak value); see Fig.6.

- 6.  $R_L = 1 \ k\Omega; C_L = 5 \ pF; E_n = V_{SS}; V_{is} = \frac{1}{2} V_{DD(p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ );

20 log  $\frac{V_{os}}{V_{is}} =$  –50 dB; see Fig. 7.

7.  $R_L = 1 \ k\Omega; C_L = 5 \ pF; E_n = V_{DD}; V_{is} = \frac{1}{2} V_{DD(p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ );

20 log

$$\frac{V_{os}}{V_{is}}$$

= -3 dB; see Fig. 7.

|                            | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P ( $\mu$ W)                                                              |                                      |

|----------------------------|----------------------|-----------------------------------------------------------------------------------------------|--------------------------------------|

| Dynamic power              | 5                    | 550 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup> | where                                |

| dissipation per            | 10                   | $2~600~f_i + \Sigma~(f_o C_L) \times V_{DD}{}^2$                                              | $f_i = input freq. (MHz)$            |

| package (P) <sup>(1)</sup> | 15                   | $6 \; 500 \; f_i + \Sigma \; (f_o C_L) \times V_{DD}{}^2$                                     | $f_o = output freq. (MHz)$           |

|                            |                      |                                                                                               | $C_L$ = load capacitance (pF)        |

|                            |                      |                                                                                               | $\sum (f_o C_L) = sum of outputs$    |

|                            |                      |                                                                                               | V <sub>DD</sub> = supply voltage (V) |

#### Note

1. All enable inputs switching.

## HEF4016B gates

# HEF4016B gates