# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC04 January 1995

## HEF40374B MSI

### DESCRIPTION

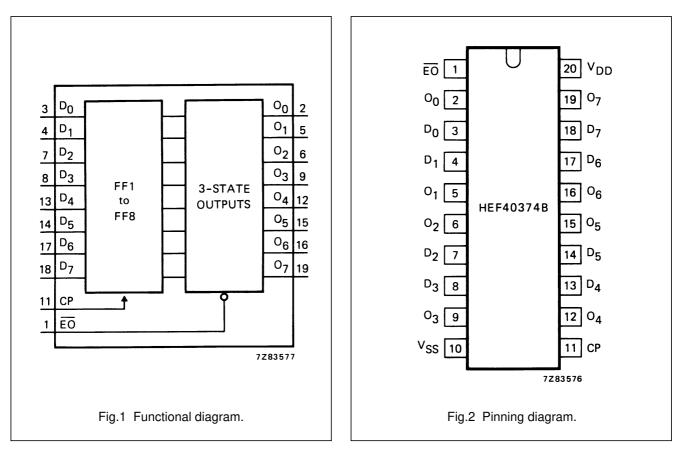

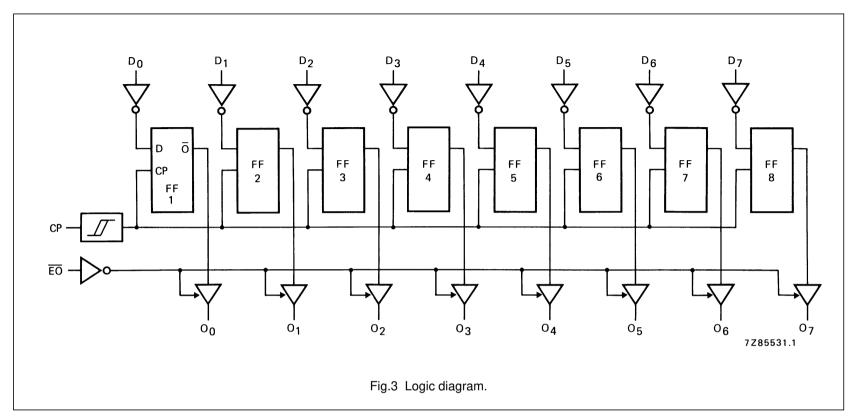

The HEF40374B is an octal D-type flip-flop with 3-state buffered outputs with a common clock input (CP). The device is used primarily as an 8-bit positive edge-triggered storage register for interfacing with a 3-state bus. Data on the D-inputs is transferred to storage during the LOW-to-HIGH transition of the clock (CP) input. The 3-state output buffers are controlled by an active LOW output enable input ( $\overline{EO}$ ). A HIGH on  $\overline{EO}$  forces the eight outputs to a high impedance OFF-state. When  $\overline{EO}$  is LOW, the data in the register appears at the outputs. The output stages have high current output capability suitable for driving highly capacitive loads.

The device features hysteresis on the CP input to improve noise rejection.

Schmitt-trigger action in the E input makes the circuit highly tolerant to slower input rise and fall times.

The HEF40374B is pin and functionally compatible with the TTL '374' device.

Supply voltage range: 3 to 15 V.

| HEF40374BP(N): 20-lea | ad DIL; plastic (SOT146-1) |

|-----------------------|----------------------------|

|-----------------------|----------------------------|

HEF40374BD(F): 20-lead DIL; ceramic (cerdip) (SOT152)

- HEF40374BT(D): 20-lead SO; plastic (SOT163-1)

- (): Package Designator North America

### PINNING

| nputs                       |

|-----------------------------|

| input                       |

| t enable input (active LOW) |

| e buffered outputs          |

|                             |

### FAMILY DATA, I<sub>DD</sub> LIMITS category MSI

See Family Specifications

\_

# Product specification

Octal D-type flip-flop with 3-state outputs

# HEF40374B MSI

### **FUNCTION TABLE**

| OPERATING MODES                 |    | INPUTS   |                | INTERNAL | OUTPUTS                          |  |

|---------------------------------|----|----------|----------------|----------|----------------------------------|--|

| OPERATING MODES                 | EO | СР       | D <sub>n</sub> | REGISTER | O <sub>0</sub> TO O <sub>7</sub> |  |

| load & road register            | L  | 5        | I              | L        | L                                |  |

| load & read register            | L  | <u> </u> | h              | Н        | Н                                |  |

|                                 | Н  | 7        | I              | L        | Z                                |  |

| load register & disable outputs | Н  | _ر       | h              | Н        | Z                                |  |

### Notes

1. H = HIGH state (the more positive voltage)

h = HIGH state (one set-up time prior to the LOW-to-HIGH clock transition)

L = LOW state (the less positive voltage)

I = LOW state (one set-up time prior to the LOW-to-HIGH clock transition)

Z = high impedance OFF-state

$\checkmark$  = LOW-to-HIGH clock transition

# HEF40374B MSI

### RATINGS

| Limiting values in accordance with the Absolute Maximum System (IEC 134)<br>See Family Specifications, except for: |             |      |        |  |  |

|--------------------------------------------------------------------------------------------------------------------|-------------|------|--------|--|--|

| D.C. current into any input                                                                                        | $\pm I_{I}$ | max. | 10 mA  |  |  |

| D.C. source or sink current into any output                                                                        | $\pm I_{O}$ | max. | 25 mA  |  |  |

| D.C. current into the supply terminals                                                                             | ±Ι          | max. | 100 mA |  |  |

### DC CHARACTERISTICS

$V_{\rm SS}=0~V$

|                  | V <sub>DD</sub> | V <sub>OH</sub> | V <sub>OL</sub> | SYMBOL           |      |      |      | T <sub>amb</sub> (° | C)   |      |    |

|------------------|-----------------|-----------------|-----------------|------------------|------|------|------|---------------------|------|------|----|

|                  | v               | v               | V               | STMBOL           | _4   | 10   | +    | 25                  | + 8  | 85   |    |

|                  |                 |                 |                 |                  | MIN. | TYP. | MIN. | TYP.                | MIN. | TYP. |    |

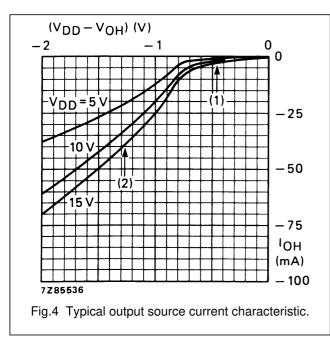

| Output current   | 5               | 4,6             |                 |                  | 0,75 |      | 0,6  | 1,2                 | 0,45 |      | mA |

| HIGH             | 10              | 9,5             |                 | –I <sub>OH</sub> | 1,85 |      | 1,5  | 3,0                 | 1,1  |      | mA |

|                  | 15              | 13,5            |                 |                  | 14,5 |      | 15   | 50                  | 15,5 |      | mA |

| Output current   | 5               | 3,6             |                 |                  | 9,3  |      | 10   | 24                  | 10,7 |      | mA |

| HIGH             | 10              | 8,4             |                 | –I <sub>OH</sub> | 14,4 |      | 15   | 46                  | 15,0 |      | mA |

|                  | 15              | 13,2            |                 |                  | 19,5 |      | 20   | 62                  | 19,8 |      | mA |

| Output current   | 5               |                 | 0,4             |                  | 2,9  |      | 2,3  | 5,4                 | 1,75 |      | mA |

| LOW              | 10              |                 | 0,5             | I <sub>OL</sub>  | 9,5  |      | 7,6  | 17                  | 5,50 |      | mA |

|                  | 15              |                 | 1,5             |                  | 30,0 |      | 25   | 45                  | 19,0 |      | mA |

| Hysteresis       | 5               |                 |                 |                  |      |      |      | 220                 |      |      | mV |

| voltage at       | 10              |                 |                 | V <sub>H</sub>   |      |      |      | 250                 |      |      | mV |

| clock input (CP) | 15              |                 |                 |                  |      |      |      | 320                 |      |      | mV |

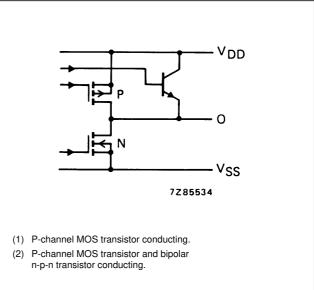

Fig.5 Schematic diagram of output stage.

# HEF40374B MSI

### AC CHARACTERISTICS

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                                                    | V <sub>DD</sub><br>V | SYMBOL            | MIN. | TYP. | MAX. |    | TYPICAL EXTRAPOLATION<br>FORMULA     |

|----------------------------------------------------|----------------------|-------------------|------|------|------|----|--------------------------------------|

| Propagation delays                                 |                      |                   |      |      |      |    |                                      |

| $CP \rightarrow O_n$                               | 5                    |                   |      | 125  | 250  | ns | 113 ns + (0,24 ns/pF) C <sub>L</sub> |

| HIGH to LOW                                        | 10                   | t <sub>PHL</sub>  |      | 55   | 110  | ns | 54 ns + (0,01 ns/pF) C <sub>L</sub>  |

|                                                    | 15                   |                   |      | 40   | 80   | ns | 36 ns + (0,07 ns/pF) C <sub>L</sub>  |

| $CP \rightarrow O_n$                               | 5                    |                   |      | 125  | 250  | ns | 122 ns + (0,06 ns/pF) C <sub>L</sub> |

| LOW to HIGH                                        | 10                   | t <sub>PLH</sub>  |      | 55   | 110  | ns | 53 ns + (0,03 ns/pF) C <sub>L</sub>  |

|                                                    | 15                   |                   |      | 40   | 80   | ns | 39 ns + (0,02 ns/pF) C <sub>L</sub>  |

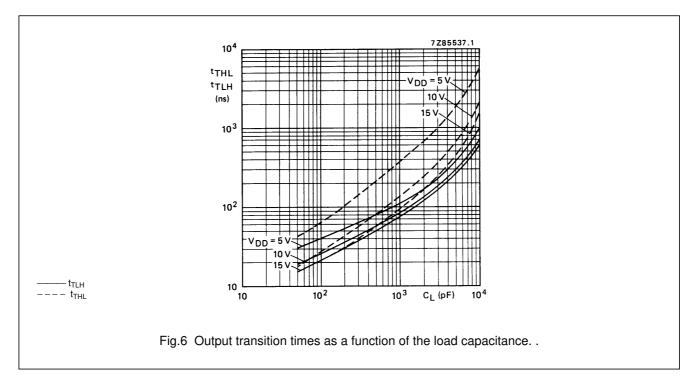

| Output transition                                  | 5                    |                   |      | 40   | 80   | ns |                                      |

| times                                              | 10                   | t <sub>THL</sub>  |      | 20   | 40   | ns |                                      |

| HIGH to LOW                                        | 15                   |                   |      | 15   | 30   | ns | see Fig.6                            |

|                                                    | 5                    |                   |      | 30   | 60   | ns | See Fig.o                            |

| LOW to HIGH                                        | 10                   | t <sub>TLH</sub>  |      | 20   | 40   | ns |                                      |

|                                                    | 15                   |                   |      | 15   | 30   | ns |                                      |

| 3-state propagation delays<br>Output disable times |                      |                   |      |      |      |    |                                      |

| $\overline{\text{EO}} \rightarrow \text{O}_n$      | 5                    |                   |      | 60   | 120  | ns |                                      |

| HIGH                                               | 10                   | t <sub>PHZ</sub>  |      | 30   | 60   | ns |                                      |

|                                                    | 15                   |                   |      | 24   | 48   | ns |                                      |

|                                                    | 5                    |                   |      | 70   | 140  | ns |                                      |

| LOW                                                | 10                   | t <sub>PLZ</sub>  |      | 35   | 70   | ns |                                      |

|                                                    | 15                   |                   |      | 30   | 60   | ns |                                      |

| Output enable times                                |                      |                   |      |      |      |    |                                      |

| $\overline{EO}\toO_n$                              | 5                    |                   |      | 65   | 130  | ns |                                      |

| HIGH                                               | 10                   | t <sub>PZH</sub>  |      | 30   | 60   | ns |                                      |

|                                                    | 15                   |                   |      | 24   | 48   | ns |                                      |

|                                                    | 5                    |                   |      | 85   | 170  | ns |                                      |

| LOW                                                | 10                   | t <sub>PZL</sub>  |      | 35   | 70   | ns |                                      |

|                                                    | 15                   |                   |      | 25   | 50   | ns |                                      |

| Set-up time                                        | 5                    |                   | 20   | 0    |      | ns |                                      |

| $D_n \rightarrow CP$                               | 10                   | t <sub>su</sub>   | 20   | 2    |      | ns |                                      |

|                                                    | 15                   |                   | 20   | 5    |      | ns |                                      |

| Hold time                                          | 5                    |                   | 20   | 10   |      | ns |                                      |

| $D_n \rightarrow CP$                               | 10                   | t <sub>hold</sub> | 15   | 2    |      | ns |                                      |

|                                                    | 15                   |                   | 10   | 0    |      | ns |                                      |

# HEF40374B MSI

|                  | V <sub>DD</sub><br>V | SYMBOL            | MIN. | TYP. | MAX. | TYPICAL EXTRAPOLATION<br>FORMULA |

|------------------|----------------------|-------------------|------|------|------|----------------------------------|

| Minimum clock    | 5                    |                   | 50   | 25   | ns   |                                  |

| pulse width; LOW | 10                   | t <sub>WCPL</sub> | 25   | 12   | ns   |                                  |

|                  | 15                   |                   | 20   | 10   | ns   |                                  |

| Maximum clock    | 5                    |                   | 25   | 5    | MHz  |                                  |

| pulse frequency  | 10                   | f <sub>max</sub>  | 6    | 12   | MHz  |                                  |

|                  | 15                   |                   | 8    | 17   | MHz  |                                  |

### AC CHARACTERISTICS

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C; input transition times  $\leq$  20 ns

|                 | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P ( $\mu$ W)                                                                 |                                        |

|-----------------|----------------------|--------------------------------------------------------------------------------------------------|----------------------------------------|

| Dynamic power   | 5                    | $3~775~f_i + \Sigma~(f_o C_L) \times V_{DD}^2$                                                   | where                                  |

| dissipation per | 10                   | 15 700 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup> | f <sub>i</sub> = input freq. (MHz)     |

| package (P)     | 15                   | 40 575 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup> | $f_o = output freq. (MHz)$             |

|                 |                      |                                                                                                  | C <sub>L</sub> = load capacitance (pF) |

|                 |                      |                                                                                                  | $\Sigma (f_o C_L) = sum of outputs$    |

|                 |                      |                                                                                                  | V <sub>DD</sub> = supply voltage (V)   |