# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC04 January 1995

#### DESCRIPTION

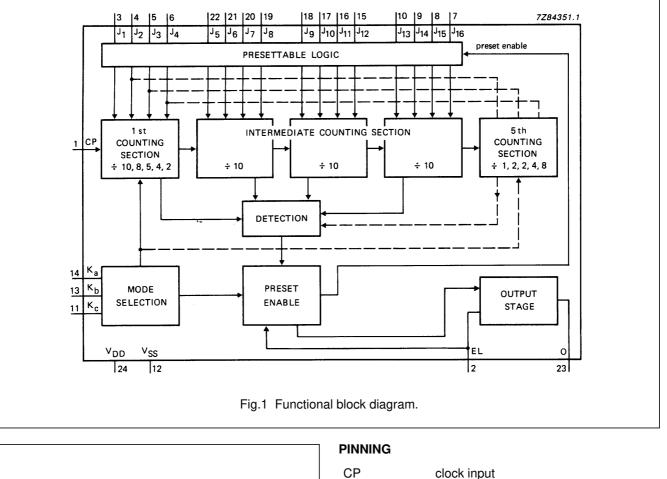

The HEF4059B is a divide-by-n counter which can be programmed to divide an input frequency by any number *n* from 3 to 15 999. The output signal is a one clock-cycle

wide pulse and occurs at a rate equal to the input frequency divided by *n*. The single output (O) has TTL drive capability. The down counter is preset by means of 16 jam inputs (J1 to J16); continued on next page.

#### FAMILY DATA, $I_{\text{DD}}$ LIMITS category LSI

See Family Specifications

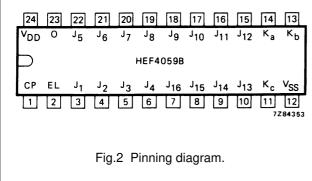

| CP                                               | clock input                   |

|--------------------------------------------------|-------------------------------|

| K <sub>a</sub> , K <sub>b</sub> , K <sub>c</sub> | mode select inputs            |

| $J_1$ to $J_{16}$                                | programmable jam inputs (BCD) |

| EL                                               | latch enable input            |

| 0                                                | divide-by-n output            |

|                                                  |                               |

| HEF4059BP(N):                        | 24-lead DIL; plastic (SOT101-1)       |  |  |  |  |  |  |

|--------------------------------------|---------------------------------------|--|--|--|--|--|--|

| HEF4059BD(F):                        | 24-lead DIL; ceramic (cerdip) (SOT94) |  |  |  |  |  |  |

| HEF4059BT(D):                        | 24-lead SO; plastic (SOT137-1)        |  |  |  |  |  |  |

| (): Package Designator North America |                                       |  |  |  |  |  |  |

2

#### HEF4059B LSI

#### Product specification

#### HEF4059B LSI

The three mode selection inputs  $K_a$ ,  $K_b$  and  $K_c$  determine the modulus ('divide-by' number) of the first and last counting sections in accordance with Table 1.

Programmable divide-by-n counter

Every time the first (fastest) counting section goes through one cycle, it reduces, by 1, the number that has been preset (jammed) into the three decades of the intermediate counting section and into the last counting section (which consists of flip-flops that are not needed for operating the first counting section).

For example, in the ÷ 2 mode, only one flip-flop is needed in the first counting section. Therefore the last (5th) counting section has three flip-flops that can be preset to a maximum count of seven with a place value of thousands. This counting mode is selected when K<sub>a</sub>, K<sub>b</sub> and K<sub>c</sub> are set to HIGH. In this case input J<sub>1</sub> is used to preset the first counting section and J<sub>2</sub> to J<sub>4</sub> are used to preset the last (5th) counting section.

If  $\div$  10 mode is desired for the first section, K<sub>a</sub> is set HIGH,  $K_b$  to HIGH and  $K_c$  to LOW. The jam inputs  $J_1$  to  $J_4$  are used to preset the first counting section and there is no last counting section. The intermediate counting section consists of three cascaded BCD decade (÷ 10) counters, presettable by means of the jam inputs  $J_5$  to  $J_{16}$ . When clock pulses are applied to the clock input after a

number n has been preset into the counter, the counter counts down until the DETECTION circuit detects the zero state. At this time the PRESET ENABLE circuit is enabled to preset again the number *n* into the counter and to produce an output pulse.

The preset of the counter to a desired  $\div$  *n* is achieved as follows:

$n = (MODE^*) (1000 \times decade 5 \text{ preset} +$

$100 \times \text{decade 4 preset} + 10 \times \text{decade 3 preset} +$ 1 × decade 2 preset) + decade 1 preset.

\* MODE = first counting section divider (10, 8, 5, 4 or 2).

To calculate preset values for any n count, divide the n count by the selected mode. The resultant is the corresponding preset values of the 5th to the 2nd decade with the remainder being equal to the 1st decade value.

preset value =

$$\frac{n}{mode}$$

.

If n = 8479, and the selected mode = 5, the preset value =  $8479 \div 5 = 1695$  with a remainder of 4, thus the jam inputs must be set as follows:

|                | 4     |                | 1              |       | Ę              | 5     |                |    | ę               | 9               |                 |                 | (        | 6               |                 |

|----------------|-------|----------------|----------------|-------|----------------|-------|----------------|----|-----------------|-----------------|-----------------|-----------------|----------|-----------------|-----------------|

| J <sub>1</sub> | $J_2$ | J <sub>3</sub> | J <sub>4</sub> | $J_5$ | J <sub>6</sub> | $J_7$ | J <sub>8</sub> | J9 | J <sub>10</sub> | J <sub>11</sub> | J <sub>12</sub> | J <sub>13</sub> | $J_{14}$ | J <sub>15</sub> | J <sub>16</sub> |

| L              | L     | Н              | н              | н     | L              | Н     | L              | н  | L               | L               | Н               | L               | Н        | н               | L               |

The mode select inputs permit frequency-synthesizer channel separations of 10, 12,5, 20, 25 and 50 parts. These inputs set the maximum value of n at 9999 (when the first counting section divides by 5 or 10) or at 15 999 (when the first counting section divides by 8, 4 or 2). The three decades of the intermediate counting section can be preset to a binary 15 instead of a binary 9. In this case the first cycle of a counter consists of 15 count pulses, the next cycles consisting of 10 count pulses. Thus the place value of the three decades are still 1, 10 and 100. For example, in the ÷ 8 mode, the number from which the intermediate counting section begins to count-down can be preset to:

| 3rd | decade: | 1500 |

|-----|---------|------|

| 2nd | decade: | 150  |

| 1st | decade: | 15   |

|     |         | 1665 |

The last counting section can be preset to a maximum of 1, with a place value of 1000. The total of these numbers (2665) times 8 equals 21 320. The first counting section can be preset to a maximum of 7. Therefore, 21 327 is the maximum possible count in the ÷ 8 mode. The highest count of the various modes is shown in Table 1, in the column entitled 'extended counter range'. Control inputs K<sub>b</sub> and K<sub>c</sub> can be used to initiate and lock the counter in the 'master preset' mode. In this condition the flip-flops in the counter are preset in accordance with the jam inputs and the counter remains in that mode as long as K<sub>b</sub> and K<sub>c</sub> both remain LOW. The counter begins to run down from the preset state when a counting mode other than the 'master preset' mode is selected. Whenever the 'master preset' mode is used, control signals  $K_b = L$  and  $K_c = L$ must be applied for at least 3 full clock pulses. After the master preset mode inputs have been changed to one of the counting modes, the next positive-going clock transition changes an internal flip-flop so that the count-down can begin at the second positive-going clock transition. Thus, after a 'master preset' mode, there is always one extra count before the output goes HIGH.

## HEF4059B LSI

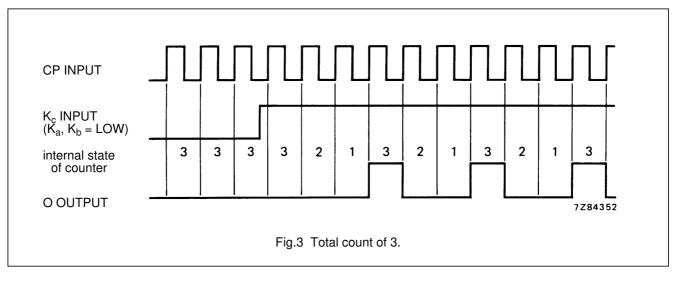

Figure 3 illustrates the operation of the counter in mode ÷ 8 starting from the preset state 3.

If the 'master preset' mode is started two clock cycles or less before an output pulse, the output pulse will appear at the time due. If the 'master preset' mode is not used the counter is preset in accordance with the 'jam inputs when the output pulse appears. A HIGH level at the latch enable input (EL) will cause the counter output to go HIGH once an output pulse occurs, and remain in the HIGH state until EL input returns to LOW. If the EL input is LOW, the output pulse will remain HIGH for only one cycle of the clock input signal. When  $K_a = L$ ,  $K_b = H$ ,  $K_c = L$  and EL = L, the counter operates in the 'preset inhibit' mode, with which the dividend of the counter is fixed to 10 000, independent of the state of the jam inputs.

When in the same state of mode select inputs EL = H, the counter operates in the normal  $\div$  10 mode, however, without the latch operation at the output.

Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

## HEF4059B LSI

#### **FUNCTION TABLE**

| LATCH<br>ENABLE<br>INPUT | S  | MODE<br>ELEC<br>NPUT | T  | FIRST COUNTING<br>SECTION<br>DECADE 1 |                         |                       | LÆ           | LAST COUNTING<br>SECTION<br>DECADE 5 |                               |                 | NTER<br>NGE    | OPERATION                     |  |

|--------------------------|----|----------------------|----|---------------------------------------|-------------------------|-----------------------|--------------|--------------------------------------|-------------------------------|-----------------|----------------|-------------------------------|--|

| LE                       | Ka | Kb                   | Kc | MODE                                  | MAX.<br>PRESET<br>STATE | JAM<br>INPUTS<br>USED | DIVIDE<br>BY | MAX.<br>PRESET<br>STATE              | JAM<br>INPUTS<br>USED         | BCD<br>MAX.     | BINARY<br>MAX. | OPERATION                     |  |

| Н                        | Н  | Н                    | Н  | 2                                     | 1                       | J <sub>1</sub>        | 8            | 7                                    | $J_2J_3J_4$                   | 15 999          | 17 331         |                               |  |

| Н                        | L  | Н                    | Н  | 4                                     | 3                       | $J_1J_2$              | 4            | 3                                    | $J_3J_4$                      | 15 999          | 18 663         |                               |  |

| Н                        | Н  | L                    | Н  | 5                                     | 4                       | $J_1J_2J_3$           | 2            | 1                                    | $J_4$                         | 9 999           | 13 329         | timer mode                    |  |

| Н                        | L  | L                    | Н  | 8                                     | 7                       | $J_1J_2J_3$           | 2            | 1                                    | J <sub>4</sub>                | 15 999          | 21 327         |                               |  |

| Н                        | Н  | Н                    | L  | 10                                    | 9                       | $J_1J_2J_3J_4$        | 1            | 0                                    | -                             | 9 999           | 16 659         |                               |  |

| L                        | Н  | Н                    | Н  | 2                                     | 1                       | J <sub>1</sub>        | 8            | 7                                    | $J_2J_3J_4$                   | 15 999          | 17 331         |                               |  |

| L                        | L  | Н                    | Н  | 4                                     | 3                       | $J_1J_2$              | 4            | 3                                    | J <sub>3</sub> J <sub>4</sub> | 15 999          | 18 663         |                               |  |

| L                        | Н  | L                    | Н  | 5                                     | 4                       | $J_1J_2J_3$           | 2            | 1                                    | $J_4$                         | 9 999           | 13 329         | -<br>- Nordel - Jacobia and - |  |

| L                        | L  | L                    | Н  | 8                                     | 7                       | $J_1J_2J_3$           | 2            | 1                                    | J <sub>4</sub>                | 15 999          | 21 327         | divide-by-n mode              |  |

| L                        | Н  | Н                    | L  | 10                                    | 9                       | $J_1J_2J_3J_4$        | 1            | 0                                    | _                             | 9 999           | 16 659         |                               |  |

| Н                        | L  | Н                    | L  | 10                                    | 9                       | $J_1J_2J_3J_4$        | 1            | 0                                    | _                             | 9 999           | 16 659         |                               |  |

| L                        | L  | Н                    | L  | preset inhibited                      |                         |                       | р            | reset inhib                          | ited                          | fixed<br>10 000 | _              | divide-by-10 000<br>mode      |  |

| х                        | х  | L                    | L  | master preset                         |                         |                       | r            | naster pre                           | set                           | _               | -              | master preset<br>mode         |  |

#### Note

- 1. It is recommended that the device is in the master preset mode (K<sub>b</sub> = K<sub>c</sub> = logic 0) in order to correctly initialize the device prior to start up.

- 2. H = HIGH voltage level

L = LOW voltage level

X = don't care

#### **DC CHARACTERISTICS**

$V_{\rm SS}=0~V$

|                 | V                    |                  |             | T <sub>amb</sub> (°C) |              |      |                                                               |

|-----------------|----------------------|------------------|-------------|-----------------------|--------------|------|---------------------------------------------------------------|

|                 | V <sub>DD</sub><br>V | SYMBOL           | -40<br>MIN. | + 25<br>MIN.          | + 85<br>MIN. | UNIT |                                                               |

| Output (sink)   | 4,75                 |                  | 2,7         | 2,3                   | 1,8          | mA   | $V_{O} = 0.4 \text{ V}; V_{I} = 0 \text{ or } 4.75 \text{ V}$ |

| current LOW     | 10                   | I <sub>OL</sub>  | 9,5         | 8                     | 6,3          | mA   | $V_{O} = 0.5 \text{ V}; V_{I} = 0 \text{ or } 10 \text{ V}$   |

|                 | 15                   |                  | 24          | 20                    | 16           | mA   | $V_{O} = 1,5 V; V_{I} = 0 \text{ or } 15 V$                   |

| Output (source) | 5                    |                  | 0,8         | 0,7                   | 0,5          | mA   | $V_{O} = 4,6 \text{ V}; V_{I} = 0 \text{ or } 5 \text{ V}$    |

| current HIGH    | 10                   | –I <sub>OH</sub> | 2,4         | 2                     | 1,6          | mA   | $V_{O} = 9,5 V; V_{I} = 0 \text{ or } 10 V$                   |

|                 | 15                   |                  | 8,4         | 7                     | 5,6          | mA   | $V_{O} = 13,5 \text{ V}; V_{I} = 0 \text{ or } 15 \text{ V}$  |

| Output (source) |                      |                  |             |                       |              |      |                                                               |

| current HIGH    | 5                    | –I <sub>OH</sub> | 2,4         | 2                     | 1,6          | mA   | $V_{O} = 2,5 \text{ V}; V_{I} = 0 \text{ or } 5 \text{ V}$    |

## HEF4059B LSI

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0  $\,$  V;  $T_{amb}$  = 25 °C; input transition times  $\leq$  20 ns

|                    | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P ( $\mu$ W)                                                                       |                                      |

|--------------------|----------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|

| Dynamic power      | 5                    | 1 100 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup>        | where                                |

| dissipation per    | 10                   | 5 500 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) $\times$ V <sub>DD</sub> <sup>2</sup> | f <sub>i</sub> = input freq. (MHz)   |

| package (P); n = 3 | 15                   | 15 000 $f_i + \Sigma (f_o C_L) \times V_{DD}{}^2$                                                      | f <sub>o</sub> = output freq. (MHz)  |

|                    | 5                    | 500 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup>          | $C_L = load capacitance (pF)$        |

| n = 1000           | 10                   | 3 500 $f_i + \Sigma (f_o C_L) \times V_{DD}{}^2$                                                       | $\Sigma(f_o C_L) = sum of outputs$   |

|                    | 15                   | 9 000 f_i + $\Sigma(f_o C_L) \times V_{DD}{}^2$                                                        | V <sub>DD</sub> = supply voltage (V) |

#### AC CHARACTERISTICS

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                         | V <sub>DD</sub><br>V | SYMBOL           | MIN. | TYP. | MAX. |     | TYPICAL EXTRAPOLATION<br>FORMULA    |

|-------------------------|----------------------|------------------|------|------|------|-----|-------------------------------------|

| Propagation delays      | 5                    |                  |      | 90   | 180  | ns  | 78 ns + (0,25 ns/pF) C <sub>L</sub> |

| $CP \rightarrow O$      | 10                   | t <sub>PHL</sub> |      | 45   | 90   | ns  | 40 ns + (0,10 ns/pF) C <sub>L</sub> |

| HIGH to LOW             | 15                   |                  |      | 35   | 70   | ns  | 32 ns + (0,07 ns/pF) C <sub>L</sub> |

|                         | 5                    |                  |      | 100  | 200  | ns  | 76 ns + (0,48 ns/pF) C <sub>L</sub> |

| LOW to HIGH             | 10                   | t <sub>PLH</sub> |      | 50   | 100  | ns  | 40 ns + (0,20 ns/pF) C <sub>L</sub> |

|                         | 15                   |                  |      | 40   | 80   | ns  | 33 ns + (0,15 ns/pF) C <sub>L</sub> |

| Output transition times | 5                    |                  |      | 30   | 60   | ns  | 10 ns + (0,40 ns/pF) C <sub>L</sub> |

| HIGH to LOW             | 10                   | t <sub>THL</sub> |      | 15   | 30   | ns  | 6 ns + (0,18 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  |      | 10   | 20   | ns  | 4 ns + (0,13 ns/pF) C <sub>L</sub>  |

|                         | 5                    |                  |      | 45   | 90   | ns  | 10 ns + (0,70 ns/pF) C <sub>L</sub> |

| LOW to HIGH             | 10                   | t <sub>TLH</sub> |      | 25   | 50   | ns  | 9 ns + (0,33 ns/pF) C <sub>L</sub>  |

|                         | 15                   |                  |      | 16   | 32   | ns  | 5 ns + (0,23 ns/pF) C <sub>L</sub>  |

| Maximum clock           | 5                    |                  | 3,5  | 7    |      | MHz |                                     |

| pulse frequency         | 10                   | f <sub>max</sub> | 7,5  | 15   |      | MHz |                                     |

|                         | 15                   |                  | 10,0 | 20   |      | MHz |                                     |