Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 60 GHz Millimeterwave Transmitter, 57 GHz to 64 GHz

Data Sheet HMC6300

#### **FEATURES**

Frequency band: 57 GHz to 64 GHz RF signal bandwidth: up to 1.8 GHz

Output power for 1 dB compression: 15 dBm

Gain: 5 dB to 35 dB

Digital and analog RF and IF gain control

Integrated frequency synthesizer Integrated image reject filter Partially external loop filter

Support for external local oscillator (LO)

On-chip temperature sensor

**Support for 256 QAM modulation**

Integrated minimum shift keying (MSK) modulator

Universal analog I/Q baseband interface

3-wire serial digital interface

65-ball, RoHS compliant, wafer level ball grid array

#### **APPLICATIONS**

Small cell backhaul

60 GHz industrial, scientific, and medical (ISM) band

data transfer

Multiple Gbps data communication

WiGig/802.11ad radio

High definition video transmission

Radar/high resolution imaging

#### **GENERAL DESCRIPTION**

The HMC6300 is a complete millimeterwave transmitter integrated circuit in a 6 mm  $\times$  4 mm RoHS compliant wafer level ball grid array (WLBGA) that operates from 57 GHz to 64 GHz with up to 1.8 GHz modulation bandwidth.

An integrated synthesizer provides tuning in 250 MHz, 500 MHz, or 540 MHz steps with excellent phase noise to support up to 64 QAM modulation. Optionally, an external LO can be injected allowing for user selectable LO characteristics or phase coherent transmit and receive operation, as well as modulation up to 256 QAM. Support for a wide variety of modulation formats is provided through a universal analog baseband I/Q interface. The transmitter chip optionally supports dedicated frequency-shift keying (FSK), minimum shift keying (MSK), and on-off keying (OOK) modulation formats for lower cost and lower power serial data links without the need for high speed data converters.

A differential output provides up to 15 dBm linear output power into a 100  $\Omega$  load. Single-ended operation is also supported up to 12 dBm. Together with the HMC6301, a complete 60 GHz transceiver chipset is provided for multiple Gbps operation in the unlicensed 60 GHz ISM band.

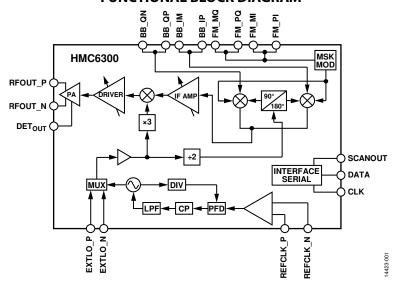

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **HMC6300\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

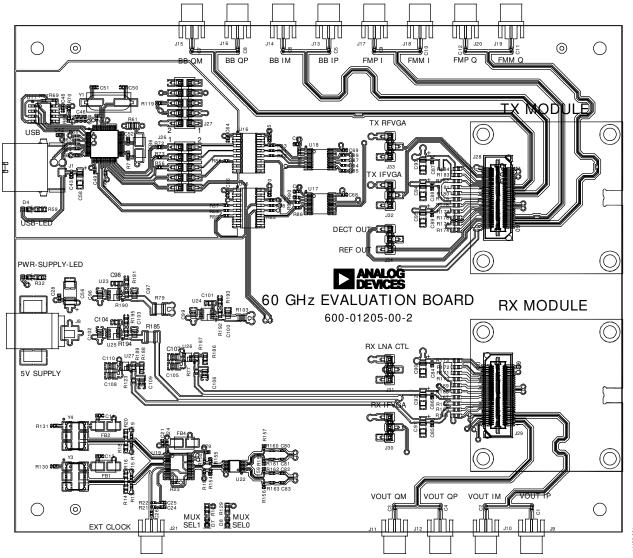

## **EVALUATION KITS**

· HMC6300 Evaluation Board

### **DOCUMENTATION**

#### **Data Sheet**

HMC6300: 60 GHz Millimeterwave Transmitter, 57 GHz to 64 GHz Data Sheet

#### **User Guides**

UG-1031: Getting Started with the EK1HMC6350 Evaluation Kit and Software

# DESIGN RESOURCES 🖵

- HMC6300 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### **DISCUSSIONS**

View all HMC6300 EngineerZone Discussions.

### SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

# TECHNICAL SUPPORT 🖳

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features 1                                             |

|--------------------------------------------------------|

| Applications1                                          |

| General Description1                                   |

| Functional Block Diagram1                              |

| Revision History2                                      |

| Specifications3                                        |

| Electrical Specifications, 57 GHz to 63 GHz3           |

| Electrical Specifications, 63 GHz to 64 GHz4           |

| Recommended Operating Conditions5                      |

| Power Consumption6                                     |

| Absolute Maximum Ratings                               |

| REVISION HISTORY                                       |

| 12/2016—Rev. A to Rev. B                               |

| Changes to Figure 11 and Figure 1411                   |

| Changes to Ordering Guide                              |

| 9/2016—v00.0716 to Rev. A                              |

| Updated FormatUniversal                                |

| Added Minimum Gain Parameter, Table 13                 |

| Changes to Recommended Operating Conditions, Table 3 5 |

| Changes to Figure 1714                                 |

| Added Ordering Guide Section                           |

|                                                        |

7/2016—Revision v00.0716: Initial Version

| ESD Caution                                    |    |

|------------------------------------------------|----|

| Pin Configuration and Function Descriptions    | 8  |

| Typical Performance Characteristics            | 10 |

| Theory of Operation                            | 13 |

| Register Array Assignment and Serial Interface | 13 |

| Transmitter Register Array Assignments         | 14 |

| Synthesizer Settings                           | 20 |

| Applications Information                       | 22 |

| Outline Dimensions                             | 25 |

| Ordering Guide                                 | 25 |

# **SPECIFICATIONS**

$T_A$  = 25°C, reference frequency = 71.4286 MHz, IF bandwidth = maximum, input impedance = 100  $\Omega$  differential, output impedance = 100  $\Omega$  differential, input signal level (high modulator gain) = -36 dBm on each of the four baseband inputs, power amplifier configuration is differential, unless otherwise noted.

### **ELECTRICAL SPECIFICATIONS, 57 GHz TO 63 GHz**

Table 1. Electrical Specifications, 57 GHz to 63 GHz

| Parameter                                  | Test Conditions/Comments                       | Min  | Тур        | Max | Unit   |

|--------------------------------------------|------------------------------------------------|------|------------|-----|--------|

| FREQUENCY STEP SIZE                        | With 71.4286 MHz reference clock               |      | 250        |     | MHz    |

|                                            | With 142.857 MHz reference clock               |      | 500        |     | MHz    |

|                                            | With 154.2857 MHz reference clock              |      | 540        |     | MHz    |

| MODULATION BANDWIDTH                       | Full I/Q bandwidth                             |      | 1.8        |     | GHz    |

| GAIN                                       |                                                |      |            |     |        |

| Minimum Gain                               |                                                |      | 5          |     | dB     |

| Maximum Gain                               |                                                | 32.5 | 35         |     | dB     |

| Modulator Gain Control                     | High and low gain settings                     |      | 9          |     | dB     |

| IF Gain Control                            |                                                |      | 14         |     | dB     |

| RF Gain Control                            |                                                |      | 22         |     | dB     |

| OUTPUT POWER                               |                                                |      |            |     |        |

| Output Power for 1 dB Compression (P1dB)   | Balanced into 100 $\Omega$                     |      | 15         |     | dBm    |

| Saturated Output Power (PSAT)              | Balanced into 100 $\Omega$                     | 13.9 | 17         |     | dBm    |

| Output Power for 1 dB Compression (P1dB)   | Singled-ended into $50\Omega$                  |      | 12         |     | dBm    |

| Saturated Output Power (P <sub>SAT</sub> ) | Singled-ended into $50\Omega$                  |      | 14         |     | dBm    |

| Detector Power Range                       |                                                |      | -10 to +15 |     | dBm    |

| TEMPERATURE SENSOR RANGE                   | Four levels                                    | -40  |            | +85 | °C     |

| SUPPRESSION AND REJECTION                  |                                                |      |            |     |        |

| Sideband Suppression                       |                                                | 15   | 30         |     | dBc    |

| Image Rejection                            |                                                |      | 40         |     | dBc    |

| LO Suppression                             | At 6/7 of RF carrier frequency (3 $\times$ LO) | 10   | 20         |     | dBc    |

| Carrier Suppression                        | Without calibration                            |      | 30         |     | dBc    |

| PHASE                                      |                                                |      |            |     |        |

| Phase Noise                                |                                                |      |            |     |        |

| @ 100 kHz Offset                           |                                                |      | <b>–75</b> |     | dBc/Hz |

| @ 1 MHz Offset                             |                                                |      | <b>-93</b> |     | dBc/Hz |

| @ 10 MHz Offset                            |                                                |      | -114       |     | dBc/Hz |

| @ 100 MHz Offset                           |                                                |      | -122       |     | dBc/Hz |

| Phase-Locked Loop (PLL) Bandwidth          | Using internal filter                          |      | 300        |     | kHz    |

| POWER DISSIPATION                          |                                                |      |            |     |        |

| Balanced                                   |                                                |      | 1.0        |     | W      |

| Single-Ended                               |                                                |      | 0.88       |     | W      |

| Balanced, External LO                      |                                                |      | 0.75       |     | W      |

## **ELECTRICAL SPECIFICATIONS, 63 GHz TO 64 GHz**

Table 2. Electrical Specifications, 63 GHz to 64 GHz

| Parameter                                  | Test Conditions/Comments                       | Min  | Тур             | Max | Unit   |

|--------------------------------------------|------------------------------------------------|------|-----------------|-----|--------|

| FREQUENCY STEP SIZE                        | With 71.4286 MHz reference clock               |      | 250             |     | MHz    |

|                                            | With 142.857 MHz reference clock               |      | 500             |     | MHz    |

|                                            | With 154.2857 MHz reference clock              |      | 540             |     | MHz    |

| MODULATION BANDWIDTH                       | Full I/Q bandwidth                             |      | 1.8             |     | GHz    |

| GAIN                                       |                                                |      |                 |     |        |

| Maximum Gain                               |                                                | 30.5 | 32              |     | dB     |

| Modulator Gain Control                     | High and low gain settings                     |      | 9               |     | dB     |

| IF Gain Control                            |                                                |      | 14              |     | dB     |

| RF Gain Control                            |                                                |      | 22              |     | dB     |

| OUTPUT POWER                               |                                                |      |                 |     |        |

| Output Power for 1 dB Compression (P1dB)   | Balanced into 100 $\Omega$                     |      | 15              |     | dBm    |

| Saturated Output Power (P <sub>SAT</sub> ) | Balanced into 100 $\Omega$                     | 13.9 | 17              |     | dBm    |

| Output Power for 1 dB Compression (P1dB)   | Singled-ended into 50 $\Omega$                 |      | 12              |     | dBm    |

| Saturated Output Power(P <sub>SAT</sub> )  | Singled-ended into $50\Omega$                  |      | 14              |     | dBm    |

| Detector Power                             |                                                |      | -10 to +15      |     | dBm    |

| TEMPERATURE SENSOR RANGE                   | Four levels                                    | -40  |                 | +85 | °C     |

| SUPPRESSION AND REJECTION                  |                                                |      |                 |     |        |

| Sideband Suppression                       |                                                | 15   | 30              |     | dBc    |

| Image Rejection                            |                                                |      | 40              |     | dBc    |

| LO Suppression                             | At 6/7 of RF carrier frequency (3 $\times$ LO) | 10   | 20              |     | dBc    |

| Carrier Suppression                        | Without calibration                            |      | 30              |     | dBc    |

| PHASE                                      |                                                |      |                 |     |        |

| Phase Noise @ 100 kHz Offset               |                                                |      | <del>-</del> 75 |     | dBc/Hz |

| Phase Noise @ 1 MHz Offset                 |                                                |      | <b>-93</b>      |     | dBc/Hz |

| Phase Noise @ 10 MHz Offset                |                                                |      | -114            |     | dBc/Hz |

| Phase Noise @ 100 MHz Offset               |                                                |      | -122            |     | dBc/Hz |

| PLL Bandwidth                              | Using internal filter                          |      | 300             |     | kHz    |

| POWER DISSIPATION                          |                                                |      |                 |     |        |

| Balanced                                   |                                                |      | 1.0             |     | W      |

| Single-Ended                               |                                                |      | 0.88            |     | W      |

| Balanced, External LO)                     |                                                |      | 0.75            |     | W      |

### **RECOMMENDED OPERATING CONDITIONS**

Table 3.

| Parameter                               | Symbol                                  | Min   | Тур                         | Max   | Unit   |

|-----------------------------------------|-----------------------------------------|-------|-----------------------------|-------|--------|

| POWER SUPPLY                            |                                         |       |                             |       |        |

| Power Amplifier                         | VCC <sub>PAN</sub> , VCC <sub>PAP</sub> | 3.9   | 4                           | 4.1   | V dc   |

| ·                                       | VDD <sub>PA</sub>                       | 2.565 | 2.7                         | 2.835 | V dc   |

| Driver                                  | VCC <sub>DRV</sub>                      | 2.565 | 2.7                         | 2.835 | V dc   |

| Divider                                 | VCC <sub>DIV</sub>                      | 2.565 | 2.7                         | 2.835 | V dc   |

| Mixer                                   | VCC <sub>MIX</sub>                      | 2.565 | 2.7                         | 2.835 | V dc   |

| Intermediate Frequency                  | VCC <sub>IF</sub>                       | 2.565 | 2.7                         | 2.835 | V dc   |

| Radio Frequency Variable Gain Amplifier | VCC <sub>RFVGA</sub>                    | 2.565 | 2.7                         | 2.835 | V dc   |

| Tripler                                 | VCC <sub>TRIP</sub>                     | 2.565 | 2.7                         | 2.835 | V dc   |

| VCO                                     | VCC <sub>vco</sub>                      | 2.565 | 2.7                         | 2.835 | V dc   |

| Digital Circuit                         | VDD <sub>D</sub>                        | 1.3   | 1.35                        | 1.48  | V dc   |

| Synthesizer                             | VDD <sub>SYN</sub>                      | 1.3   | 1.35                        | 1.48  | V dc   |

| INPUT VOLTAGE RANGE                     |                                         |       |                             |       |        |

| Serial Digital Interface                | DATA, ENABLE, CLK, RESET                |       |                             |       |        |

| Logic High                              |                                         | 0.9   | 1.2                         | 1.4   | V      |

| Logic Low                               |                                         | -0.05 | +0.1                        | +0.3  | V      |

| REFERENCE CLOCK                         |                                         |       |                             |       |        |

| Reference Clock, Positive               | REFCLK_P                                |       | 3.3 V or 2.5 V LVPECL/LVDS, |       | V      |

|                                         |                                         |       | 1.2 V CMOS                  |       | V      |

| Reference Clock, Negative               | REFCLK_N                                |       | 3.3 V or 2.5 V LVPECL/LVDS, |       | V      |

|                                         |                                         |       | 1.2 V CMOS                  |       | V      |

| BASEBAND I/Q                            |                                         |       |                             |       |        |

| In-Phase Baseband Input                 |                                         |       |                             |       |        |

| Negative                                | BB_IM                                   | 5     | 100                         | 750   | mV p-p |

| Positive                                | BB_IP                                   | 5     | 100                         | 750   | mV p-p |

| Quadrature Baseband Input               |                                         |       |                             |       |        |

| Negative                                | BB_QN                                   | 5     | 100                         | 750   | mV p-p |

| Positive                                | BB_QP                                   | 5     | 100                         | 750   | mV p-p |

| BASEBAND I/Q, COMMON MODE               |                                         |       |                             |       |        |

| In-Phase Baseband Input                 |                                         |       |                             |       |        |

| Negative                                | BB_IM                                   |       | 1.6                         |       | V      |

| Positive                                | BB_IP                                   |       | 1.6                         |       | V      |

| Quadrature Baseband Input               |                                         |       |                             |       |        |

| Negative                                | BB_QN                                   |       | 1.6                         |       | V      |

| Positive                                | BB_QP                                   |       | 1.6                         |       | V      |

| MSK DATA                                |                                         |       |                             |       |        |

| MSK In-Phase Input                      |                                         |       |                             |       |        |

| Negative (Minus)                        | FM_MI                                   | 200   | 500                         | 750   | mV p-p |

| Positive                                | FM_PI                                   | 200   | 500                         | 750   | mV p-p |

| MSK Quadrature Input                    |                                         |       |                             |       |        |

| Negative (Minus)                        | FM_MQ                                   | 200   | 500                         | 750   | mV p-p |

| Positive                                | FM_PQ                                   | 200   | 500                         | 750   | mV p-p |

| MSK COMMON MODE                         |                                         |       | 1.1                         |       | V      |

| ANALOG GAIN CONTROL                     |                                         |       |                             |       |        |

| RF Variable Gain Amplifier              | ANA <sub>RFVGA</sub>                    | 0.1   | 1.1                         | 2.5   | V      |

| IF Variable Gain Amplifier              | ANA <sub>IFVGA</sub>                    | 0.1   | 1.1                         | 2.5   | V      |

| EXTERNAL LO                             |                                         |       |                             |       |        |

| Positive                                | EXTLO_P                                 | 0     | 3                           | 5     | dBm    |

| Negative                                | EXTLO_N                                 | 0     | 3                           | 5     | dBm    |

| Parameter             | Symbol | Min Typ | Max Unit |

|-----------------------|--------|---------|----------|

| DRAIN CURRENT         |        |         |          |

| 1.35 V                |        | 10      | mA       |

| 2.7 V                 |        | 277     | mA       |

| 4.0 V (Balanced)      |        | 58      | mA       |

| 4.0 V (Singled-Ended) |        | 29      | mA       |

### **POWER CONSUMPTION**

Table 4.

| Parameter          | Voltage (V) | Typical Current (mA) | Typical Power Consumption (mW) |  |

|--------------------|-------------|----------------------|--------------------------------|--|

| VCC <sub>PAN</sub> | 4.0         | 29                   | 116                            |  |

| $VCC_{PAP}$        | 4.0         | 29                   | 116                            |  |

| $VCC_{DRV}$        | 2.7         | 32                   | 86                             |  |

| $VCC_{DIV}$        | 2.7         | 46                   | 124                            |  |

| $VCC_{MIX}$        | 2.7         | 32                   | 86                             |  |

| $VCC_{IF}$         | 2.7         | 31                   | 84                             |  |

| $VCC_{RFVGA}$      | 2.7         | 20                   | 54                             |  |

| $VCC_{TRIP}$       | 2.7         | 56                   | 151                            |  |

| VCC <sub>vco</sub> | 2.7         | 52                   | 140                            |  |

| $VCC_{PA}$         | 2.7         | 8                    | 22                             |  |

| $VCC_D$            | 1.35        | 0.08                 | 0.1                            |  |

| VCC <sub>SYN</sub> | 1.35        | 10                   | 13                             |  |

# **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Parameter                                                        | Rating           |

|------------------------------------------------------------------|------------------|

| VCC <sub>DRV</sub>                                               | 2.85 V           |

| VCC <sub>DIV</sub>                                               | 2.85 V           |

| VCC <sub>PAN</sub> , VCC <sub>PAP</sub>                          | 4.2 V            |

| VCC <sub>vco</sub>                                               | 2.85 V           |

| VCC <sub>RFVGA</sub>                                             | 2.85 V           |

| VCC <sub>IF</sub>                                                | 2.85 V           |

| VCC <sub>MIX</sub>                                               | 2.85 V           |

| VCC <sub>TRIP</sub>                                              | 2.85 V           |

| VDD <sub>SYN</sub>                                               | 1.6 V            |

| $VDD_{PA}$                                                       | 2.85 V           |

| $VDD_D$                                                          | 1.6 V            |

| Serial Digital Interface Input Voltage                           | 1.5 V            |

| Thermal Resistance (R <sub>TH</sub> ), Junction to Ground Paddle | 9.57°C           |

| Baseband Inputs: BB, FM (Each)                                   | 0.75 V p-p       |

| Storage Temperature                                              | −55°C to +150°C  |

| Operating Temperature                                            | −40°C to 85°C    |

| Reflow Temperature (Maximum Peak)                                | 260°C            |

| ESD Sensitivity, Charged Device Model (CDM)                      | Class C3 (250 V) |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

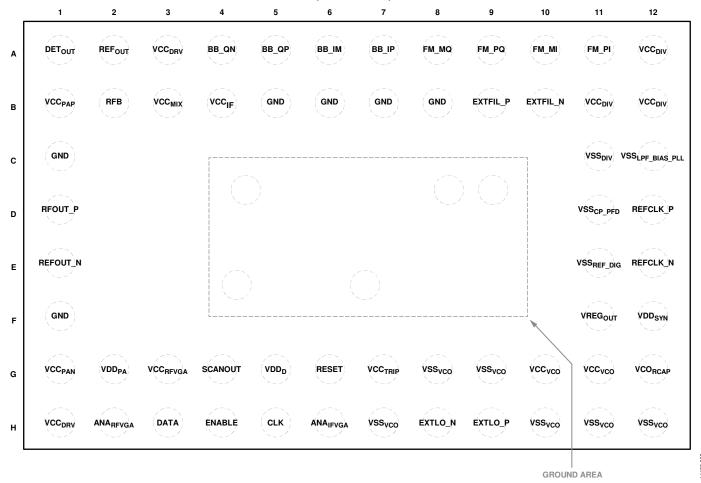

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

HMC6300 TOP VIEW (BALL SIDE DOWN)

Figure 2. Pin Configuration Diagram

**Table 6. Pin Function Descriptions**

| Pin No.          | Mnemonic           | Description                                                                                |

|------------------|--------------------|--------------------------------------------------------------------------------------------|

| A1               | DET <sub>out</sub> | Detector Output (0.6 V dc to 2.6 V dc).                                                    |

| A2               | REF <sub>out</sub> | Detector Reference Output (0.6 V dc).                                                      |

| A3, H1           | VCC <sub>DRV</sub> | Driver Power Supply (2.7 V dc).                                                            |

| A4               | BB_QN              | Quadrature Negative Baseband Input. This pin is dc-coupled and matched to 50 $\Omega$ .    |

| A5               | BB_QP              | Quadrature Positive Baseband Input. This pin is dc-coupled and matched to 50 $\Omega$ .    |

| A6               | BB_IM              | In-Phase Negative Baseband Input. This pin is dc-coupled and matched to 50 $\Omega$ .      |

| A7               | BB_IP              | In-Phase Positive Baseband Input. This pin is dc-coupled and matched to 50 $\Omega$ .      |

| A8               | FM_MQ              | FSK Negative (Minus) Quadrature Input. This pin is dc-coupled and matched to 50 $\Omega$ . |

| A9               | FM_PQ              | FSK Positive Quadrature Input. This pin is dc-coupled and matched to 50 $\Omega$ .         |

| A10              | FM_MI              | FSK Negative (Minus) In-Phase Input. This pin is dc-coupled and matched to 50 $\Omega$ .   |

| A11              | FM_PI              | FSK Positive In-Phase Input. This pin is dc-coupled and matched to 50 $\Omega$ .           |

| A12, B11, B12    | VCC <sub>DIV</sub> | Divider Power Supply (2.7 V dc).                                                           |

| B1               | VCC <sub>PAP</sub> | Power Amplifier Power Supply (4.0 V dc).                                                   |

| B2               | RFB                | Detector Circuit Feedback.                                                                 |

| В3               | VCC <sub>MIX</sub> | Mixer Power Supply (2.7 V dc).                                                             |

| B4               | VCC <sub>IF</sub>  | IF Power Supply (2.7 V dc).                                                                |

| B5 to B8, C1, F1 | GND                | Analog Ground Connect.                                                                     |

| Pin No.                | Mnemonic                    | Description                                                                                                                                                                  |

|------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B9                     | EXTFIL_P                    | External PLL Filter (Positive).                                                                                                                                              |

| B10                    | EXTFIL_N                    | External PLL Filter (Negative).                                                                                                                                              |

| C11                    | VSS <sub>DIV</sub>          | Digital Ground for the Synthesizer.                                                                                                                                          |

| C12                    | VSS <sub>LPF_BIAS_PLL</sub> | Digital Ground for Synthesizer.                                                                                                                                              |

| D1                     | RFOUT_P                     | Radio Frequency Output (Positive). This pin is ac-coupled and is differentially matched to $100~\Omega$ . This output port is disabled when single-ended output is selected. |

| D11                    | VSS <sub>CP_PFD</sub>       | Digital Ground for Synthesizer.                                                                                                                                              |

| D12                    | REFCLK_P                    | External Reference Clock (Positive). This pin can be dc or ac matched to 50 $\Omega$ .                                                                                       |

| E1                     | RFOUT_N                     | Radio Frequency Output (Negative). This pin is ac coupled and is diff matched to 100 $\Omega$ . This pin is used if single-ended output is selected.                         |

| E11                    | VSS <sub>REF_DIG</sub>      | Digital Ground for Synthesizer.                                                                                                                                              |

| E12                    | REFCLK_N                    | External Reference Clock (Negative). This pin can be dc or ac matched to 50 $\Omega$ .                                                                                       |

| F11                    | VREGOUT                     | VCO Regulator Output.                                                                                                                                                        |

| F12                    | VDD <sub>SYN</sub>          | Synthesizer Power Supply (1.3 V dc).                                                                                                                                         |

| G1                     | VCC <sub>PAN</sub>          | Power Amplifier Power Supply (4.0 V dc).                                                                                                                                     |

| G2                     | VDD <sub>PA</sub>           | Power Amplifier Power Supply (2.7 V dc).                                                                                                                                     |

| G3                     | VCC <sub>RFVGA</sub>        | RF VGA Power Supply (2.7 V dc).                                                                                                                                              |

| G4                     | SCANOUT                     | Serial Digital Interface Output (1.2 V CMOS).                                                                                                                                |

| G5                     | $VDD_D$                     | Digital Circuits Power Supply (1.3 V dc).                                                                                                                                    |

| G6                     | RESET                       | Serial Digital Interface Reset (1.2 V CMOS).                                                                                                                                 |

| G7                     | VCC <sub>TRIP</sub>         | Tripler Power Supply (2.7 V dc).                                                                                                                                             |

| G8, G9, H7, H10 to H12 | VSS <sub>vco</sub>          | Digital Ground for the VCO.                                                                                                                                                  |

| G10, G11               | VCC <sub>vco</sub>          | VCO Power Supply (2.7 V dc).                                                                                                                                                 |

| G12                    | VCO <sub>RCAP</sub>         | External Capacitor Connection for the VCO Regulator.                                                                                                                         |

| H2                     | ANA <sub>RFVGA</sub>        | 0.1 V to 2.4 V RF VGA Analog Control. Connect Pin H2 to 2.7 V dc for digital control.                                                                                        |

| H3                     | DATA                        | Serial Digital Interface Data (1.2 V CMOS).                                                                                                                                  |

| H4                     | ENABLE                      | Serial Digital Interface Enable (1.2 V CMOS).                                                                                                                                |

| H5                     | CLK                         | Serial Digital Interface Clock (1.2 V CMOS).                                                                                                                                 |

| H6                     | ANA <sub>IFVGA</sub>        | 0.1 V to 2.4 V IF VGA Analog Control. Connect Pin H6 to 2.7 V dc for digital control.                                                                                        |

| H8                     | EXTLO_N                     | External LO (Negative) Input.                                                                                                                                                |

| H9                     | EXTLO_P                     | External LO (Positive) Input.                                                                                                                                                |

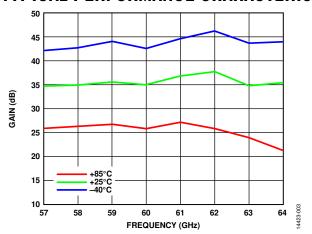

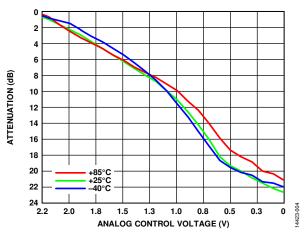

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. Maximum Gain vs. Frequency over Temperature, IF and RF Attenuation = 0 dBm

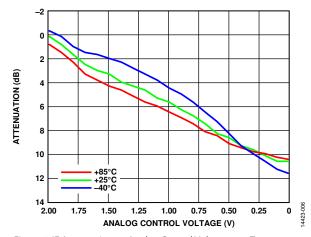

Figure 4. RF Attenuation vs. Analog Control Voltage over Temperature, Measurement Taken at 60 GHz, IF Attenuation = 0 dBm

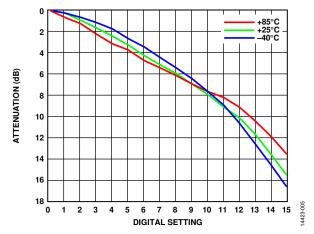

Figure 5. RF Attenuation vs. Digital Setting over Temperature, Measurement Taken at 60 GHz, IF Attenuation = 0 dBm

Figure 6. IF Attenuation vs. Analog Control Voltage over Temperature, Measurement Taken at 60 GHz, RF Attenuation = 0 dBm

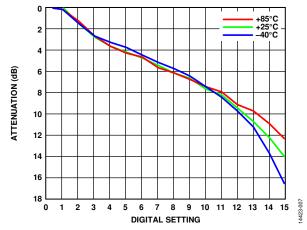

Figure 7. IF Attenuation vs. Digital Setting over Temperature, Measurement Taken at 60 GHz, RF Attenuation = 0 dBm

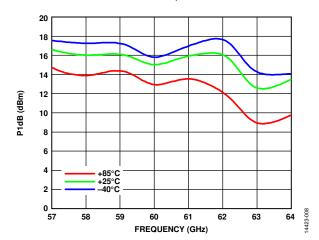

Figure 8. Output P1dB vs. Frequency over Temperature, IF and RF Attenuation = 0 dBm

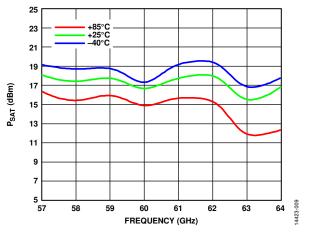

Figure 9. Output Saturated Power ( $P_{SAT}$ ) vs. Frequency over Temperature, IF and RF Attenuation = 0 dBm

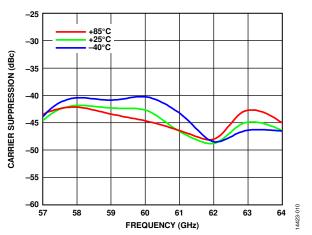

Figure 10. Carrier Suppression vs. Frequency over Temperature, IF and RF Attenuation = 0 dBm

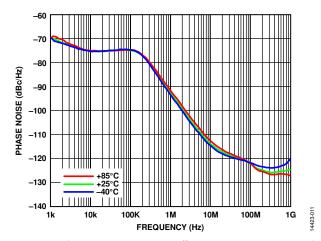

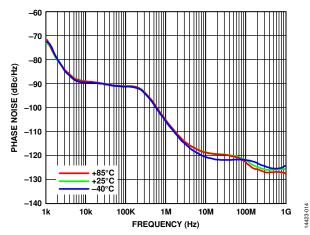

Figure 11. Phase Noise vs. Frequency Offset over Temperature, Internal LO, Measurement Taken at 60 GHz

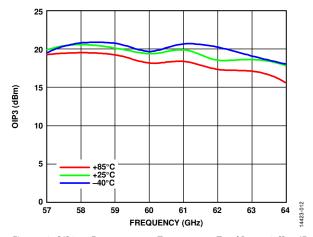

Figure 12. OIP3 vs. Frequency over Temperature, Total  $P_{OUT} = 0 dBm$ , IF and RF Attenuation = 0 dBm

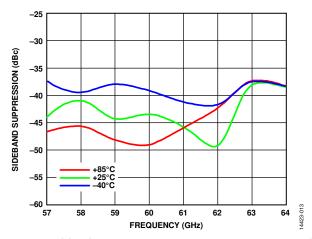

Figure 13. Sideband Suppression vs. Frequency over Temperature, IF and RF Attenuation = 0 dBm

Figure 14. Phase Noise vs. Frequency Offset over Temperature, External LO, Measurement Taken at 60 GHz

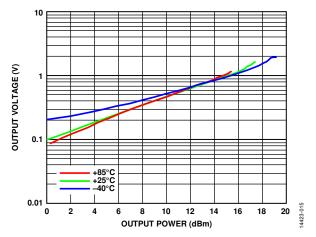

Figure 15. Detector Output Voltage vs. Output Power over Temperature, Measurement Taken at 60 GHz, and 1.15 k $\Omega$  Connecting DET $_{OUT}$  and RFB Pins

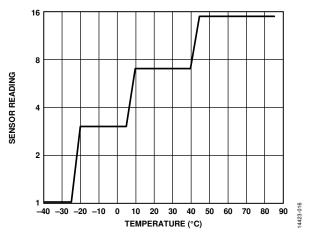

Figure 16. Temperature Sensor Reading vs. Temperature

### THEORY OF OPERATION

An integrated frequency synthesizer creates a low phase noise LO between 16.3 GHz and 18.3 GHz. The step size of the synthesizer equates to 250 MHz steps at RF when used with a 71.42857 MHz reference crystal or 500 MHz if used with a 142.857 reference crystal. To support IEEE channels (ISM band) with a 540 MHz step size, use a 154.2857 MHz reference crystal.

If the chip is configured for I/Q baseband input, these signals are quadrature modulated onto an 8 GHz to 9.1 GHz sliding IF using the synthesized LO divided by two. There are also options to input AM/FM/FSK/MSK waveforms directly to the on-chip IF modulators. The IF signal is then filtered and amplified with 14 dB of variable gain, then mixed with three times the LO frequency to upconvert to an RF frequency between 57 GHz and 64 GHz.

Integrated notch filters attenuate the lower mixing product at 40 GHz to 46 GHz. Three RF amplifier stages provide gain to allow up to 15 dBm of linear and differential output power with 22 dB of variable gain. IF and RF gain can be controlled using either analog voltages or the digital SPI. For lower power consumption, half of the power amplifier can be disabled to run in a single-ended configuration; this drops the output power by 3 dB.

An on-chip power detector can be used to monitor the rms output power. The detector output pin (DET\_{OUT}) is connected through an external resistor to the RFB pin. A resistor value of 1.15  $k\Omega$  is recommended for optimal coverage up to the P1dB point of the transmitter. The REF\_{OUT} pin provides the reference voltage for the detector, and the difference between DET\_{OUT} and REF\_{OUT} is used to estimate the output power.

The phase noise and quadrature balance of the on-chip synthesizer is sufficient to support up to 64 QAM modulation. For higher order modulation (up to 256 QAM or less than 250 MHz step size), the HMC6300 can be operated using an external LO.

The HMC6300 transmitter is ideal for FDD operation together with the HMC6301 receiver chip. However, both devices can

support TDD operation by enabling and disabling the circuits. All of the enables are placed in register array, four of which allow for full chip enable or disable in one SPI write.

There are no special power sequencing requirements for the HMC6300; all voltages are to be applied simultaneously.

# REGISTER ARRAY ASSIGNMENT AND SERIAL INTERFACE

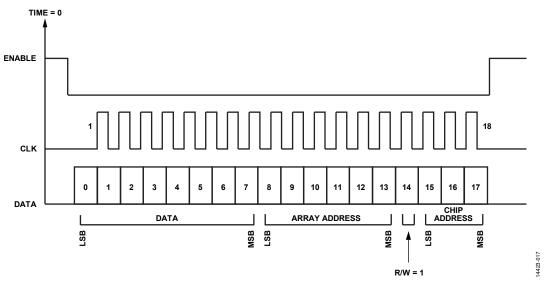

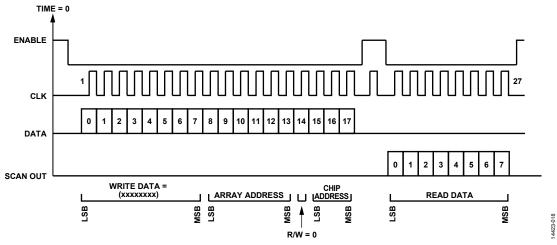

The register arrays for both the transmitter and receiver are organized into 32 rows of 8 bits. Using the serial interface, the arrays are written or read one row at a time, as shown in Figure 17 and Figure 18, respectively. Figure 17 shows the sequence of signals on the ENABLE, CLK, and DATA lines to write one 8-bit row of the register array. The ENABLE line goes low, the first of 18 data bits (Bit 0) is placed on the DATA line, and 2 ns or longer after the DATA line stabilizes, the CLK line goes high to clock in Data Bit 0. The DATA line should remain stable for at least 2 ns after the rising edge of CLK.

A write operation requires 18 data bits and 18 clock pulses, as shown in Figure 17. The 18 data bits contain the 8-bit register array row data (LSB is clocked in first), followed by the register array row address (ROW 0 through ROW 23, 000000 to 001111, LSB first), the read/write bit (set to 1 to write), and finally the Tx Chip Address 110, LSB first).

The Tx IC supports a serial interface running up to several hundred megahertz, and the interface is 1.2 V CMOS levels.

Note that the register array row address is six bits, but only four are used to designate 32 rows, the two MSBs are 0.

After the 18th clock pulse of the write operation, the ENABLE line returns high to load the register array on the IC; prior to the rising edge of the ENABLE line, no data is written to the array. The CLK line should have stabilized in the low state at least 2 ns prior to the rising edge of the ENABLE line.

Figure 17.Timing Diagram for Writing a Row of the Transmitter Serial Interface

Figure 18. Timing Diagram for Reading a Row of the Transmitter Serial Interface

### TRANSMITTER REGISTER ARRAY ASSIGNMENTS

In the following table, N/A means not applicable. All register arrays are read/write, unless otherwise indicated.

Table 7. Transmitter Register Array Assignments

| Register Array Row<br>and Bit | Internal Signal Name | Signal Function                                                           |

|-------------------------------|----------------------|---------------------------------------------------------------------------|

| ROW0                          | N/A                  | Not used.                                                                 |

| ROW1                          |                      |                                                                           |

| ROW1, Bit 7                   | pa_sel_vgbs<3>       | Controls the regulator for the base voltage of the power amplifier output |

| ROW1, Bit 6                   | pa_sel_vgbs<2>       | transistors.                                                              |

| ROW1, Bit 5                   | pa_sel_vgbs<1>       | ROW1, Bits[7:3] = 1100 for normal operation.                              |

| ROW1, Bit 4                   | pa_sel_vgbs<0>       |                                                                           |

| ROW1, Bit 3                   | ifvga_q_cntrl<0>     |                                                                           |

| ROW1, Bit 2                   | pa_sel_vref<2>       | Controls the bias current for the power amplifier output transistors.     |

| ROW1, Bit 1                   | pa_sel_vref<1>       | ROW1, Bits[2:0] = 010 for normal operation.                               |

| ROW1, Bit 0                   | pa_sel_vref<0>       |                                                                           |

| Register Array Row<br>and Bit | Internal Signal Name | Signal Function                                                                                                 |

|-------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------|

| ROW2                          |                      |                                                                                                                 |

| ROW2, Bit 7                   | pa_sel_alc_dac<3>    | Factory diagnostics; ROW2.                                                                                      |

| ROW2, Bit 6                   | pa_sel_alc_dac<2>    | Bits[7:4] = 1111 for normal operation.                                                                          |

| ROW2, Bit 5                   | pa_sel_alc_dac<1>    |                                                                                                                 |

| ROW2, Bit 4                   | pa_sel_alc_dac<0>    |                                                                                                                 |

| ROW2, Bit 3                   | pa_sep_pa_pwrdn_fast | Active high for normal operation.                                                                               |

| ROW2, Bit 2                   | pa_pwrdwn_fast       | Active high for normal operation.                                                                               |

| ROW2, Bit 1                   | pa_se_sel            | Control for Tx output interface; active low for differential Tx output; active high for Tx single-ended output. |

| ROW2, Bit 0                   | power_det_pwrdn      | Active low to enable Tx power detector.                                                                         |

| ROW3                          |                      |                                                                                                                 |

| ROW3, Bit 7                   | driver_bias<2>       | Controls the bias current for the power amplifier driver.                                                       |

| ROW3, Bit 6                   | driver_bias<1>       | ROW3, Bits[7:5] = 111 for normal operation.                                                                     |

| ROW3, Bit 5                   | driver_bias<0>       |                                                                                                                 |

| ROW3, Bit 4                   | driver_bias2<2>      | Controls the bias current for the Power Amplifier Predriver 2.                                                  |

| ROW3, Bit 3                   | driver_bias2<1>      | ROW3, Bits[4:2] = 101 for normal operation.                                                                     |

| ROW3, Bit 2                   | driver_bias2<0>      |                                                                                                                 |

| ROW3, Bit 1                   | en_ifmix_HiCG        | Active high to enable high gain mode in IF mixer.                                                               |

| ROW3, Bit 0                   | en_tempflash         | Active high to enable temperature sensor.                                                                       |

| ROW4                          | cn_temphasn          | Active high to chable temperature sensor.                                                                       |

| ROW4, Bit 7                   | driver_pwrdn         | Active high to power down the driver amplifier.                                                                 |

|                               | ·                    |                                                                                                                 |

| ROW4, Bit 6                   | upmixer_pwrdn        | Active high to power down the upmixer.                                                                          |

| ROW4, Bit 5                   | ifvga_pwrdn          | Active high to power down the IF VGA.                                                                           |

| ROW4, Bit 4                   | divider_pwrdn        | Active high to power down the divider.                                                                          |

| ROW4, Bit 3                   | pa_pwrdn             | Active high to power down the power amplifier.                                                                  |

| ROW4, Bit 2                   | rfvga_pwrdn          | Active high to power down the RF VGA.                                                                           |

| ROW4, Bit 1                   | tripler_pwrdn        | Active high to power down the tripler.                                                                          |

| ROW4, Bit 0                   | if_upmixer_pwrdn     | Active high to power down the IF upmixer.                                                                       |

| ROW5                          | <del>_</del>         |                                                                                                                 |

| ROW5, Bit 7                   | tripler_bias<13>     | Controls bias of frequency tripler.                                                                             |

| ROW5, Bit 6                   | tripler_bias<12>     | ROW5, Bits[7:0] = 11111111 for normal operation.                                                                |

| ROW5, Bit 5                   | tripler_bias<11>     |                                                                                                                 |

| ROW5, Bit 4                   | tripler_bias<10>     |                                                                                                                 |

| ROW5, Bit 3                   | tripler_bias<9>      |                                                                                                                 |

| ROW5, Bit 2                   | tripler_bias<8>      |                                                                                                                 |

| ROW5, Bit 1                   | tripler_bias<7>      |                                                                                                                 |

| ROW5, Bit 0                   | tripler_bias<6>      |                                                                                                                 |

| ROW6                          |                      |                                                                                                                 |

| ROW6, Bit 7                   | tripler_bias<5>      | Controls bias of frequency tripler.                                                                             |

| ROW6, Bit 6                   | tripler_bias<4>      | ROW6, Bits[7:2] = 111011 for normal operation.                                                                  |

| ROW6, Bit 5                   | tripler_bias<3>      |                                                                                                                 |

| ROW6, Bit 4                   | tripler_bias<2>      |                                                                                                                 |

| ROW6, Bit 3                   | tripler_bias<1>      |                                                                                                                 |

| ROW6, Bit 2                   | tripler_bias<0>      |                                                                                                                 |

| ROW6, Bit 1                   | N/A                  | Not used.                                                                                                       |

| ROW6, Bit 0                   |                      |                                                                                                                 |

| ROW7                          | •                    | ·                                                                                                               |

| ROW7, Bit 7                   | ifvga_vga_adj<3>     | IF variable gain amplifier gain control bits.                                                                   |

| ROW7, Bit 6                   | ifvga_vga_adj<2>     | ROW7, Bits[7:4] = 0000 is highest gain and 1101 is lowest gain.                                                 |

| ROW7, Bit 5                   | ifvga_vga_adj<1>     | Attenuation is $\approx$ 1.3 dB per step, $\approx$ 17 dB maximum.                                              |

| ROW7, Bit 4                   | ifvga_vga_adj<0>     |                                                                                                                 |

| ROW7, Bit 4                   | ifvga_vga_adj<0>     |                                                                                                                 |

| Register Array Row and Bit                                                                                                                                                                                                                                                                                                                  | Internal Signal Name                                                                                                                                                                                                                                                            | Signal Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROW7, Bit 3                                                                                                                                                                                                                                                                                                                                 | ifvga_tune<3>                                                                                                                                                                                                                                                                   | Controls the tuning of the IF filter for the variable gain amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ROW7, Bit 2                                                                                                                                                                                                                                                                                                                                 | ifvga_tune<2>                                                                                                                                                                                                                                                                   | ROW7, Bits[3:0] = 1111 for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ROW7, Bit 1                                                                                                                                                                                                                                                                                                                                 | ifvga_tune<1>                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROW7, Bit 0                                                                                                                                                                                                                                                                                                                                 | ifvga_tune<0>                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROW8                                                                                                                                                                                                                                                                                                                                        | •                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROW8, Bit 7                                                                                                                                                                                                                                                                                                                                 | ifvga_bias<3>                                                                                                                                                                                                                                                                   | Controls the bias current of the IF variable gain amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ROW8, Bit 6                                                                                                                                                                                                                                                                                                                                 | ifvga_bias<2>                                                                                                                                                                                                                                                                   | ROW8, Bits[7:4] = 1000 for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ROW8, Bit 5                                                                                                                                                                                                                                                                                                                                 | ifvga_bias<1>                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROW8, Bit 4                                                                                                                                                                                                                                                                                                                                 | ifvga_bias<0>                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROW8, Bit 3                                                                                                                                                                                                                                                                                                                                 | if_upmixer_tune<3>                                                                                                                                                                                                                                                              | Controls the tuning of the IF filter for the IF to RF upmixer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ROW8, Bit 2                                                                                                                                                                                                                                                                                                                                 | if_upmixer_tune<2>                                                                                                                                                                                                                                                              | ROW8, Bits[3:0] = 1111 for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ROW8, Bit 1                                                                                                                                                                                                                                                                                                                                 | if_upmixer_tune<1>                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROW8, Bit 0                                                                                                                                                                                                                                                                                                                                 | if_upmixer_tune<0>                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |