# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ANALOG DEVICES

# 25 MHz to 3000 MHz Fractional-N PLL with Integrated VCO

### **Data Sheet**

### FEATURES

RF bandwidth: 25 MHz to 3000 MHz 3.3 V supply Maximum phase detector rate: 100 MHz Ultralow phase noise -110 dBc/Hz in band (typical), f<sub>o</sub> at 1600 MHz Fractional figure of merit (FOM): -226 dBc/Hz 24-bit step size, 3 Hz typical resolution Exact frequency mode with 0 Hz frequency error Fast frequency hopping 40-lead, 6 mm × 6 mm LFCSP package: 36 mm<sup>2</sup>

### **APPLICATIONS**

Cellular infrastructure Microwave radios WiMax, WiFi Communications test equipment CATV equipment DDS replacement Military Tunable reference sources for spurious-free performance

### **GENERAL DESCRIPTION**

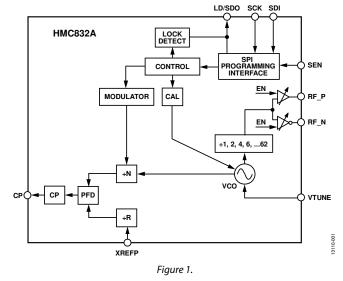

The HMC832A is a 3.3 V, high performance, wideband, fractional-N, phase-locked loop (PLL) that features an integrated voltage controlled oscillator (VCO) with a fundamental frequency of 1500 MHz to 3000 MHz and an integrated VCO output divider (divide by 1, 2, 4, 6, ... 62) that enables the HMC832A to generate continuous frequencies from 25 MHz to 3000 MHz. The integrated phase detector (PD) and  $\Sigma$ - $\Delta$ modulator, capable of operating at up to 100 MHz, permit wider loop bandwidths and faster frequency tuning with excellent spectral performance.

Industry leading phase noise and spurious performance, across all frequencies, enable the HMC832A to minimize blocker effects, and to improve receiver sensitivity and transmitter spectral purity. A low noise floor (–160 dBc/Hz eliminates any contribution to modulator/mixer noise floor in transmitter applications.

# HMC832A

### FUNCTIONAL BLOCK DIAGRAM

The HMC832A is footprint compatible to the HMC830 PLL with an integrated VCO. It features 3.3 V supply and innovative programmable performance technology that enables the HMC832A to tailor current consumption and corresponding noise floor performance to individual applications by selecting either a low current consumption mode or a high performance mode for improved noise floor performance.

Additional features of the HMC832A include 12 dB of RF output gain control in 1 dB steps; an output mute function to automatically mute the output during frequency changes when the device is not locked; selectable output return loss; programmable differential or single-ended outputs, with the ability to select either output in single-ended mode; a  $\Sigma$ - $\Delta$  modulator exact frequency mode that enables users to generate output frequencies with 0 Hz frequency error; and a register configurable 3.3 V or 1.8 V serial port interface (SPI).

Rev. B

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# HMC832A\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

HMC832A Evaluation Board

### **DOCUMENTATION**

### **Data Sheet**

HMC832A: 25 MHz to 3000 MHz Fractional-N PLL with Integrated VCO Data Sheet

### TOOLS AND SIMULATIONS $\square$

ADIsimFrequency Planner Tool

### REFERENCE MATERIALS

### **Quality Documentation**

- Package/Assembly Qualification Test Report: LP6, LP6C, LP6G (QTR: 2014-00368)

- Semiconductor Qualification Test Report: BiCMOS-A (QTR: 2013-00235)

### DESIGN RESOURCES

- HMC832A Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all HMC832A EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# TABLE OF CONTENTS

| Features                                      |

|-----------------------------------------------|

| Applications                                  |

| Functional Block Diagram 1                    |

| General Description                           |

| Revision History 2                            |

| Specifications                                |

| Timing Specifications6                        |

| Absolute Maximum Ratings7                     |

| Recommended Operating Conditions7             |

| ESD Caution7                                  |

| Pin Configuration and Function Descriptions   |

| Typical Performance Characteristics           |

| Theory of Operation15                         |

| PLL Subsystem Overview15                      |

| VCO Subsystem Overview15                      |

| SPI Configuration of PLL and VCO Subsystems15 |

| VCO Subsystem                                 |

| PLL Subsystem                                 |

| Soft Reset and Power-On Reset                 |

| Power-Down Mode28                             |

| General-Purpose Output (GPO)                  |

| Chip Identification                           |

| Serial Port Interface (SPI)                   |

| Applications Information                      |

| Power Supply                                  |

| 11 /                                          |

| Programmable Performance Technology           |

|                                               |

| Programmable Performance Technology           |

| Programmable Performance Technology           |

### **REVISION HISTORY**

11/15—Revision B: Initial Version

| ID, Read Address, and Reset (RST) Registers                                                   | 35 |

|-----------------------------------------------------------------------------------------------|----|

| Reference Divider (REFDIV), Integer, and Fractional<br>Frequency Registers                    | 35 |

| VCO SPI Register                                                                              | 36 |

| Σ-Δ Configuration Register                                                                    | 36 |

| Lock Detect Register                                                                          | 37 |

| Analog Enable (EN) Register                                                                   | 37 |

| Charge Pump Register                                                                          | 38 |

| Autocalibration Register                                                                      | 38 |

| Phase Detector (PD) Register                                                                  | 39 |

| Exact Frequency Mode Register                                                                 | 39 |

| General-Purpose, SPI, and Reference Divider<br>(GPO_SPI_RDIV) Register                        | 40 |

| VCO Tune Register                                                                             | 41 |

| Sucessive Approximation Register                                                              | 41 |

| General-Purpose 2 Register                                                                    | 41 |

| Built-In Self Test (BIST) Register                                                            | 41 |

| VCO Subsystem Register Map                                                                    | 42 |

| VCO Enable Register                                                                           | 42 |

| VCO Output Divider Register                                                                   | 43 |

| VCO Configuration Register                                                                    | 43 |

| VCO Calibration/Bias, Center Frequency Calibration<br>(CF_CAL), and MSB Calibration Registers | 44 |

| VCO Output Power Control                                                                      | 44 |

| Evaluation Printed Circuit Board (PCB)                                                        | 45 |

| Changing Evaluation Board Reference Frequency and CH<br>Current Configuration                 |    |

| Evaluation Kit Contents                                                                       | 46 |

| Outline Dimensions                                                                            | 47 |

| Ordering Guide                                                                                | 48 |

## **SPECIFICATIONS**

VPPCP, VDDLS, VCC1, VCC2, RVDD, AVDD, DVDD, VCCPD, VCCHF, VCCPS = 3.3 V minimum and maximum specified across the temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

| Table 1.                                            |                                                                                           | 1     | _           |          |        |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------------|----------|--------|

| Parameter                                           | Test Conditions/Comments                                                                  | Min   | Тур         | Max      | Unit   |

| RF OUTPUT CHARACTERISTICS                           |                                                                                           |       |             |          |        |

| Output Frequency                                    |                                                                                           | 25    |             | 3000     | MHz    |

| VCO Frequency at PLL Input                          |                                                                                           | 1500  |             | 3000     | MHz    |

| RF Output Frequency at f <sub>vco</sub>             |                                                                                           | 1500  |             | 3000     | MHz    |

| OUTPUT POWER                                        |                                                                                           |       |             |          |        |

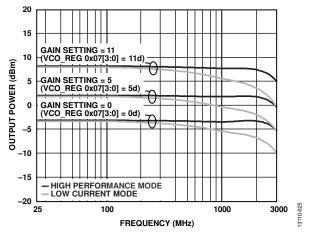

| RF Output Power                                     | Across all frequencies (see Figure 25), high<br>performance mode (VCO_REG 0x03[1:0] = 3d) |       |             |          |        |

|                                                     | Maximum gain setting (VCO_REG 0x07[3:0] = 0xB), single-ended                              |       | 7           |          | dBm    |

|                                                     | Gain Setting 6 (VCO_REG 0x07[3:0] = 6d),<br>differential                                  |       | 2           |          | dBm    |

| Output Power Control Range                          | 1 dB steps                                                                                |       | 12          |          | dB     |

| HARMONICS FOR FUNDAMENTAL MODE                      |                                                                                           |       |             |          |        |

| f <sub>o</sub> Mode at 2 GHz                        | Second/third/fourth harmonics                                                             |       | -20/-29/-45 |          | dBc    |

| $f_0/2$ Mode at 2 GHz/2 = 1 GHz                     | Second/third/fourth harmonics                                                             |       | -26/-10/-34 |          | dBc    |

| $f_{0}/30$ Mode at 3 GHz/30 = 100 MHz               | Second/third/fourth harmonics                                                             |       | -33/-10/-40 |          | dBc    |

| f <sub>o</sub> /62 Mode at 1550 MHz/62 = 25 MHz     | Second/third/fourth harmonics                                                             |       | -40/-6/-43  |          | dBc    |

| VCO OUTPUT DIVIDER                                  |                                                                                           |       |             |          |        |

| VCO RF Divider Range                                | 1, 2, 4, 6, 8, 62                                                                         | 1     |             | 62       |        |

| PLL RF DIVIDER CHARACTERISTICS                      | .,_,,,,,,,,.,.,                                                                           |       |             |          |        |

| 19-Bit N-Divider Range (Integer)                    | $Maximum = 2^{19} - 1$                                                                    | 16    |             | 524,287  |        |

| 19-Bit N-Divider Range (Fractional)                 | Fractional nominal divide ratio varies (±4)                                               | 20    |             | 524,283  |        |

| 19 bit N Divider Hange (Hactional)                  | dynamically maximum                                                                       | 20    |             | 52 1,205 |        |

| REFERENCE (XREFP PIN) INPUT<br>CHARACTERISTICS      |                                                                                           |       |             |          |        |

| Maximum XREFP Input Frequency                       |                                                                                           |       |             | 350      | MHz    |

| XREFP Input Level                                   | AC-coupled <sup>1</sup>                                                                   | -6    |             | +12      | dBm    |

| XREFP Input Capacitance                             |                                                                                           |       |             | 5        | рF     |

| 14-Bit R-Divider Range                              |                                                                                           | 1     |             | 16,383   | 1.     |

| PHASE DETECTOR (PD) <sup>2</sup>                    |                                                                                           |       |             |          |        |

| PD Frequency Fractional Mode <sup>3</sup>           |                                                                                           | DC    |             | 100      | MHz    |

| PD Frequency Integer Mode                           |                                                                                           | DC    |             | 100      | MHz    |

| CHARGE PUMP                                         |                                                                                           | DC    |             | 100      | 11112  |

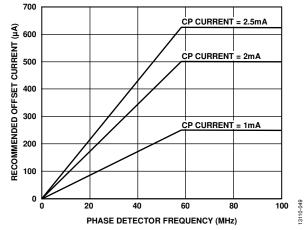

| Output Current                                      |                                                                                           | 0.02  |             | 2.54     | mA     |

| Charge Pump Gain Step Size                          |                                                                                           | 0.02  | 20          | 2.34     | μA     |

| PD/Charge Pump Single Sideband (SSB)<br>Phase Noise | 50 MHz reference, input referred                                                          |       | 20          |          | μΛ     |

| 1 kHz                                               |                                                                                           |       | -143        |          | dBc/Hz |

| 10 kHz                                              | Add 2 dB for fractional mode                                                              |       | -150        |          | dBc/Hz |

| 100 kHz                                             | Add 3 dB for fractional mode                                                              |       | -152        |          | dBc/Hz |

| LOGIC INPUTS                                        | 1.8 V and 3.3 V modes                                                                     |       | 172         |          |        |

|                                                     |                                                                                           |       |             |          |        |

| Input Voltage                                       |                                                                                           |       |             | 0.75     | v      |

| Low $(V_{\mu})$                                     |                                                                                           | 1 1 5 |             | 0.75     | V      |

| High (V <sub>IH</sub> )                             |                                                                                           | 1.15  | 6           | 50       | -      |

| SCK Clock Frequency Rate                            |                                                                                           |       | 6           | 50       | MHz    |

| Parameter                                          | Test Conditions/Comments                                                              | Min                      | Тур                   | Max      | Unit  |

|----------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------|-----------------------|----------|-------|

| LD/SDO LOGIC OUTPUT                                |                                                                                       |                          |                       |          |       |

| Output High Voltage                                |                                                                                       |                          |                       |          |       |

| High (V <sub>oH</sub> )                            | CMOS 1.8 V mode (Register 0x0F[9:8] = 00b,<br>Register 0x0B[22] = 0)                  | 1.3                      |                       | 2.3      | V     |

|                                                    | CMOS 3.3 V mode (Register 0x0F[9:8] = 00b,<br>Register 0x0B[22] = 1)                  | V <sub>DD</sub> –<br>0.2 |                       | $V_{DD}$ | V     |

|                                                    | Open-drain mode (Register $0x0F[9:8] = 01b)^4$                                        | 1.8                      |                       |          | V     |

| Low (V <sub>oL</sub> )                             | CMOS mode (Register 0x0F[9:8] = 00b)                                                  |                          |                       | 0.1      | V     |

|                                                    | Open-drain mode (Register 0x0F[9:8] = 01b) <sup>5</sup>                               |                          | 0.4                   |          |       |

| SCK Clock Frequency Rate                           | CMOS mode (Register0x0F[9:8] = 00b) <sup>6</sup>                                      |                          | 6                     | 50       | MHz   |

|                                                    | Open-drain mode (Register0x0F[9:8] = $01b$ ) <sup>7</sup>                             |                          | 5                     | 10       | MHz   |

| Capacitive Load                                    | CMOS mode (Register0x0F[9:8] = 00b)                                                   |                          | 10                    | 20       | pF    |

|                                                    | Open-drain mode (Register0x0F[9:8] = $01b$ ) <sup>8</sup>                             |                          |                       | 10       | pF    |

| Load Current                                       | CMOS mode (Register0x0F[9:8] = 00b) <sup>9</sup>                                      |                          |                       | 3.6      | mA    |

|                                                    | Open-drain mode (Register0x0F[9:8] = $01b$ ) <sup>10</sup>                            |                          |                       | 7.2      | mA    |

| Output Resistance When Driver Is Low $(R_{_{ON}})$ | Open-drain mode (Register0x0F[9:8] = 01b)                                             |                          | 100                   | 200      | Ω     |

| Pull-Up Resistor (R <sub>UP</sub> )                | Open-drain mode (Register0x0F[9:8] = 01b)                                             | 500                      | 1000                  |          | Ω     |

| Rise Time                                          | CMOS mode (Register0x0F[9:8] = 00b) <sup>11</sup>                                     |                          | $0.5 + 0.3(C_{LOAD})$ | 7        | ns    |

| Fall Time                                          | CMOS mode (Register0x0F[9:8] = 00b) <sup>11</sup>                                     |                          | $1.5 + 0.2(C_{LOAD})$ | 10       | ns    |

| SCK to SDO Turnaround Time                         | CMOS mode (Register0x0F[9:8] = 00b) <sup>11</sup>                                     |                          | $0.9 + 0.1(C_{LOAD})$ | 12       | ns    |

| Output Impedance (R <sub>out</sub> )               | 1.8 V mode (Register 0x0B[22] = 0)                                                    | 100                      |                       | 200      | Ω     |

| POWER SUPPLY VOLTAGES                              |                                                                                       |                          |                       |          |       |

| 3.3 V Supplies                                     | AVDD, VCCHF, VCCPS, VCCPD, RVDD, DVDD, VPPCP, VDDLS, VCC1, VCC2                       | 3.1                      | 3.3                   | 3.5      | V     |

| POWER SUPPLY CURRENTS                              |                                                                                       |                          |                       |          |       |

| High Performance Mode                              | VCO_REG 0x03[1:0] = $3d^{12}$                                                         |                          |                       |          |       |

| 2500 MHz, 11 dB Gain                               | 11 dB gain (VCO_REG 0x07[3:0] = 11d),<br>single-ended output (VCO_REG 0x03[3:2] = 2d) |                          | 219                   |          | mA    |

| 800 MHz, 11 dB Gain                                | Single-ended output                                                                   |                          | 230                   |          | mA    |

| 2500 MHz, 6 dB Gain                                | 6 dB gain (VCO_REG 0x07[3:0] = 6d),<br>differential output (VCO_REG 0x03[3:2] = 3d)   |                          | 226                   |          | mA    |

| 800 MHz, 6 dB Gain                                 | Differential output                                                                   |                          | 237                   |          | mA    |

| 2500 MHz, 1 dB Gain                                | 1 dB gain (VCO_REG 0x07[3:0] = 1d),<br>differential output (VCO_REG 0x03[3:2] = 3d)   |                          | 210                   |          | mA    |

| 800 MHz, 1 dB Gain                                 | Differential output                                                                   |                          | 221                   |          | mA    |

| Low Current Mode                                   | VCO_REG 0x03[1:0] = $1d^{12}$                                                         |                          |                       |          |       |

| 2500 MHz, 6 dB Gain                                | 6 dB gain (VCO_REG 0x07[3:0] = 6d),<br>differential output (VCO_REG 0x03[3:2] = 3d)   |                          | 195                   |          | mA    |

| 800 MHz, 6 dB Gain                                 | Differential output                                                                   |                          | 205                   |          | mA    |

| 2500 MHz, 1 dB Gain                                | 1 dB gain (VCO_REG 0x07[3:0] = 1d),<br>differential output (VCO_REG 0x03[3:2] = 3d)   |                          | 180                   |          | mA    |

| 800 MHz, 1 dB Gain                                 | Differential output                                                                   |                          | 192                   |          | mA    |

| Power-Down                                         |                                                                                       |                          |                       |          |       |

| Crystal Off                                        | Register 0x01 = 0, crystal not clocked                                                |                          | 10                    |          | μΑ    |

| Crystal On, 100 MHz                                | Register 0x01 = 0, crystal clocked at 100 MHz                                         |                          | 5                     |          | mA    |

| POWER-ON RESET                                     |                                                                                       |                          |                       |          |       |

| Typical Reset Voltage on DVDD                      |                                                                                       |                          | 700                   |          | mV    |

| Minimum DVDD Voltage for No Reset                  |                                                                                       | 1.5                      |                       |          | V     |

| Power-On Reset Delay                               |                                                                                       |                          | 250                   |          | μs    |

| VCO CLOSED-LOOP PHASE NOISE                        |                                                                                       |                          |                       |          |       |

| f <sub>o</sub> at 1600 MHz, 10 kHz Offset          | See Figure 3                                                                          |                          | -110                  |          | dBc/⊦ |

|                                                    |                                                                                       |                          |                       |          |       |

| Parameter                                        | Test Conditions/Comments                                                                                         | Min | Тур                                                    | Max | Unit    |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------|-----|---------|

| VCO OPEN-LOOP PHASE NOISE                        |                                                                                                                  |     |                                                        |     |         |

| f <sub>o</sub> at 2 GHz <sup>13</sup>            |                                                                                                                  |     |                                                        |     |         |

| 10 kHz Offset                                    |                                                                                                                  |     | -88                                                    |     | dBc/Hz  |

| 100 kHz Offset                                   |                                                                                                                  |     | -116                                                   |     | dBc/Hz  |

| 1 MHz Offset                                     |                                                                                                                  |     | -139                                                   |     | dBc/Hz  |

| 10 MHz Offset                                    |                                                                                                                  |     | -157                                                   |     | dBc/Hz  |

| 100 MHz Offset                                   |                                                                                                                  |     | -162                                                   |     | dBc/Hz  |

| $f_0 at 2 GHz/2 = 1 GHz^{13}$                    |                                                                                                                  |     |                                                        |     |         |

| 10 kHz Offset                                    |                                                                                                                  |     | -93                                                    |     | dBc/Hz  |

| 100 kHz Offset                                   |                                                                                                                  |     | -122                                                   |     | dBc/Hz  |

| 1 MHz Offset                                     |                                                                                                                  |     | -145                                                   |     | dBc/Hz  |

| 10 MHz Offset                                    |                                                                                                                  |     | -159                                                   |     | dBc/Hz  |

| 100 MHz Offset                                   |                                                                                                                  |     | -162                                                   |     | dBc/Hz  |

| $f_0$ at 3 GHz/30 = 100 MHz <sup>13</sup>        |                                                                                                                  |     |                                                        |     |         |

| 10 kHz Offset                                    |                                                                                                                  |     | -110                                                   |     | dBc/Hz  |

| 100 kHz Offset                                   |                                                                                                                  |     | -139                                                   |     | dBc/Hz  |

| 1 MHz Offset                                     |                                                                                                                  |     | -160                                                   |     | dBc/Hz  |

| 10 MHz Offset                                    |                                                                                                                  |     | -163                                                   |     | dBc/Hz  |

| 100 MHz Offset                                   |                                                                                                                  |     | -163                                                   |     | dBc/Hz  |

|                                                  |                                                                                                                  |     | 105                                                    |     | 000/112 |

| 250 kHz Offset f <sub>0</sub> <sup>13</sup>      | Over manufacturing process variations with 3.3 V power supply at 25°C                                            |     |                                                        |     |         |

| f <sub>o</sub> = 1584 MHz                        |                                                                                                                  |     | -124.5                                                 |     | dBc/Hz  |

| $f_0 = 1998 \text{ MHz}$                         |                                                                                                                  |     | -122.5                                                 |     | dBc/Hz  |

| $f_0 = 2416 \text{ MHz}$                         |                                                                                                                  |     | -122.0                                                 |     | dBc/Hz  |

| $f_0 = 2812 \text{ MHz}$                         |                                                                                                                  |     | -121.0                                                 |     | dBc/Hz  |

| PLL                                              |                                                                                                                  |     |                                                        |     |         |

| Phase Noise at 20 kHz Offset, 50 MHZ<br>PFD Rate | Over process with 3.3 V power supply at 25°C, measured with >200 kHz loop bandwidth                              |     |                                                        |     |         |

| f <sub>o</sub> = 1582.896 MHz                    |                                                                                                                  |     | -113.5                                                 |     | dBc/Hz  |

| f <sub>o</sub> = 1998.25 MHz                     |                                                                                                                  |     | -113.5                                                 |     | dBc/Hz  |

| f <sub>o</sub> = 2415.735 MHz                    |                                                                                                                  |     | -112.5                                                 |     | dBc/Hz  |

| $f_0 = 2811.21 \text{ MHz}$                      |                                                                                                                  |     | -109.5                                                 |     | dBc/Hz  |

| Lock Time                                        | Depends on loop filter bandwidth, PFD rate,<br>and definition of lock (to within ±Hz or<br>±degrees of settling) |     | 500                                                    |     | μs      |

| Frequency Resolution                             | Depends on PFD rate and VCO output divider setting                                                               |     |                                                        |     |         |

| Fundamental Mode                                 | 1.5 GHz to 3 GHz output; at typical phase detector frequency ( $f_{PD}$ ) of 50 MHz, typical resolution = 3 Hz   |     | $f_{PD}^{}/2^{24}$                                     |     | Hz      |

| Divider Mode                                     | <1.5 GHz output, resolution depends on VCO output divider setting                                                |     | f <sub>PD</sub> /(2 <sup>24</sup> ×<br>output divider) |     | Hz      |

| Reference Spurs                                  | -                                                                                                                |     | -85                                                    |     | dBc/Hz  |

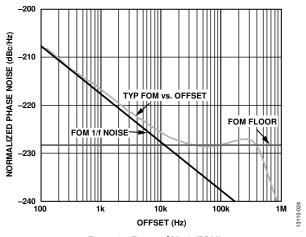

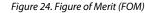

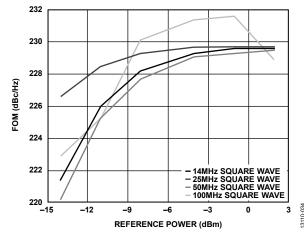

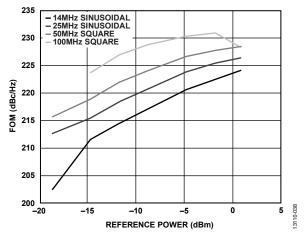

| FIGURE OF MERIT (FOM)                            | Normalized to 1 Hz (see Figure 24)                                                                               |     |                                                        |     |         |

| Floor Integer Mode                               |                                                                                                                  |     | -229                                                   |     | dBc/Hz  |

| Floor Fractional Mode                            |                                                                                                                  |     | -226                                                   |     | dBc/Hz  |

| Flicker (Both Modes)                             |                                                                                                                  |     | -268                                                   |     | dBc/Hz  |

# HMC832A

| Parameter                        | Test Conditions/Comments                   | Min | Тур  | Max | Unit  |

|----------------------------------|--------------------------------------------|-----|------|-----|-------|

| VCO CHARACTERISTICS              |                                            |     |      |     |       |

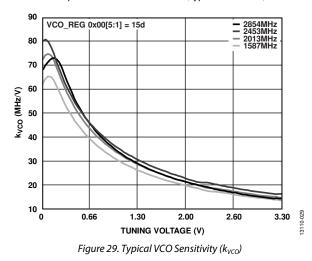

| VCO Tuning Sensitivity           | Measured with 1.5 V on VTUNE (see Figure 2 | 29) |      |     |       |

| 2800 MHz                         |                                            |     | 24.6 |     | MHz/V |

| 2400 MHz                         |                                            |     | 25.8 |     | MHz/V |

| 2000 MHz                         |                                            |     | 25.2 |     | MHz/V |

| 1600 MHz                         |                                            |     | 24.3 |     | MHz/V |

| VCO Supply Pushing <sup>14</sup> | Measured with 1.5 V on VTUNE               |     | 2.8  |     | MHz/V |

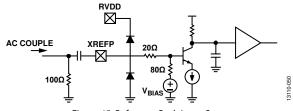

$^{1}$  Measured with 100  $\Omega$  external termination. See the Reference Input Stage section for more details.

<sup>2</sup> Slew rate of ≥0.5 ns/V is recommended. See the Reference Input Stage section for more details. Frequency is guaranteed across process voltage and temperature from -40°C to +85°C.

<sup>3</sup> This maximum PD frequency can only be achieved if the minimum N value is respected. For example, in the case of fractional mode, the maximum PD frequency =  $f_{VCO}/20$  or 100 MHz, whichever is less.

<sup>4</sup> External 1 kΩ pull-up resistor to 1.8 V.

$^5$  Limited by the 1 k $\Omega$  pull-up resistor and NMOS  $R_{_{ON}}$  .

<sup>6</sup> 10 pF load capacitor.

<sup>7</sup> 10 pF load capacitor, 1 kΩ pull-up resistor. In general, open-drain mode can support higher frequencies at the expense of maximum  $V_{OL}$ . The maximum frequency for a given pull-up resistor and load capacitor is approximately 1/(10 ×  $R_{PULL-UP} × C_{LOAD}$ ). For example, a 10 pF load capacitor and 1 kΩ pull-up resistor can support up to 10 MHz, where  $V_{OL}$  maximum =  $V_{DD} × R_{ON}/(1 k\Omega + R_{ON}) \approx 164$  mV. With a 500 Ω pull-up resistance and a 10 pF load, a 20 MHz maximum frequency is possible, and the maximum  $V_{OL}$  increases to 300 mV.

<sup>8</sup> 1 kΩ pull-up resistor.

$^9$  The minimum resistive load to ground in CMOS mode is 1 k $\!\Omega.$

<sup>10</sup> The LD/SDO pin does not have short-circuit protection. The maximum current of 7.2 mA must not be exceeded under any condition.

<sup>11</sup>  $C_{LOAD}$  in pF.  $C_{LOAD}$  maximum = 20 pF.

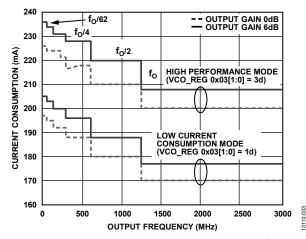

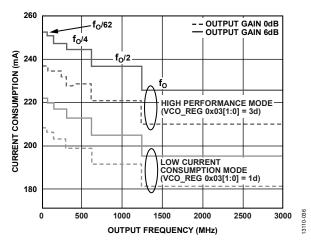

<sup>12</sup> For detailed current consumption information, refer to Figure 33 and Figure 36.

<sup>13</sup> Gain setting = 6 (VCO\_REG 0x07[3:0] = 6d) in high performance mode (VCO\_REG 0x03[1:0] = 3d).

<sup>14</sup> Pushing refers to a change in VCO frequency due to a change in the power supply voltage.

### TIMING SPECIFICATIONS

#### SPI Write Timing Characteristics

AVDD = DVDD = 3 V, exposed pad (EP) = 0 V. See Figure 47.

#### Table 2.

| Parameter        | Test Conditions/Comments                            | Min | Тур | Max | Unit |

|------------------|-----------------------------------------------------|-----|-----|-----|------|

| t <sub>1</sub>   | SDI setup time to SCK rising edge                   | 3   |     |     | ns   |

| t <sub>2</sub>   | SCK rising edge to SDI hold time                    | 3   |     |     | ns   |

| t <sub>3</sub>   | SEN low duration                                    | 10  |     |     | ns   |

| t <sub>4</sub>   | SEN high duration                                   | 10  |     |     | ns   |

| t <sub>5</sub>   | SCK 32 <sup>nd</sup> rising edge to SEN rising edge | 10  |     |     | ns   |

| t <sub>6</sub>   | Recovery time                                       | 20  |     |     | ns   |

| f <sub>scк</sub> | Maximum serial port clock speed                     |     | 50  |     | MHz  |

#### SPI Read Timing Characteristics

AVDD = DVDD = 3 V, exposed pad (EP) = 0 V. See Figure 48.

#### Table 3.

| Parameter                   | Test Conditions/Comments                            | Min | Тур | Max                | Unit |

|-----------------------------|-----------------------------------------------------|-----|-----|--------------------|------|

| t <sub>1</sub>              | SDI setup time to SCK rising edge                   | 3   |     |                    | ns   |

| t <sub>2</sub>              | SCK rising edge to SDI hold time                    | 3   |     |                    | ns   |

| t <sub>3</sub>              | SEN low duration                                    | 10  |     |                    | ns   |

| t <sub>4</sub>              | SEN high duration                                   | 10  |     |                    | ns   |

| t <sub>5</sub> <sup>1</sup> | SCK rising edge to SDO time                         |     |     | 8.2 ns + 0.2 ns/pF | ns   |

| t <sub>6</sub>              | Recovery time                                       | 10  |     |                    | ns   |

| t <sub>7</sub>              | SCK 32 <sup>nd</sup> rising edge to SEN rising edge | 10  |     |                    | ns   |

<sup>1</sup> An extra 0.2 ns delay is required for every 1 pF load on SDO.

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| Parameter                                                   | Rating           |

|-------------------------------------------------------------|------------------|

| AVDD, RVDD, DVDD, VCCPD, VCCHF, VCCPS                       | –0.3 V to +3.6 V |

| VPPCP, VDDLS, VCC1                                          | –0.3 V to +3.6 V |

| VCC2                                                        | –0.3 V to +3.6 V |

| Operating Temperature Range                                 | –40°C to +85°C   |

| Storage Temperature Range                                   | –65°C to +150°C  |

| Maximum Junction Temperature                                | 150°C            |

| Thermal Resistance ( $\theta_{JC}$ ) (Junction to Case, EP) | 9°C/W            |

| Reflow Soldering                                            |                  |

| Peak Temperature                                            | 260°C            |

| Time at Peak Temperature                                    | 40 sec           |

| ESD Sensitivity, Human Body Model (HBM)                     | Class 1B         |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **RECOMMENDED OPERATING CONDITIONS**

#### Table 5. Recommended Operating Conditions

| Parameter                         | Min | Тур | Max | Unit |

|-----------------------------------|-----|-----|-----|------|

| Temperature                       |     |     |     |      |

| Junction Temperature <sup>1</sup> |     |     | 125 | °C   |

| Ambient Temperature               | -40 |     | +85 | °C   |

| Supply Voltage                    |     |     |     |      |

| AVDD, RVDD, DVDD, VCCPD,          | 3.1 | 3.3 | 3.5 | V    |

| VCCHF, VCCPS, VPPCP, VDDLS,       |     |     |     |      |

| VCC1, VCC2                        |     |     |     |      |

<sup>1</sup> Using the layout design guidelines set out in the Qualification Test Report is strongly recommended.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

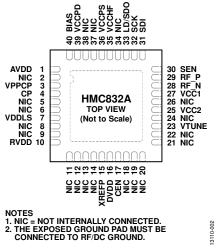

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

#### **Table 6. Pin Function Descriptions**

| Pin Number                                                  | Mnemonic | Description                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                           | AVDD     | DC Power Supply for Analog Circuitry.                                                                                                                                                                                                                                                                    |

| 2, 5, 6, 8, 9, 11 to<br>14, 18 to 22, 24, 26,<br>34, 37, 38 | NIC      | Not Internally Connected. These pins are not connected internally; however, it is recommended to connect these pins to RF/dc ground externally.                                                                                                                                                          |

| 3                                                           | VPPCP    | Power Supply for the Charge Pump Analog Section.                                                                                                                                                                                                                                                         |

| 4                                                           | СР       | Charge Pump Output.                                                                                                                                                                                                                                                                                      |

| 7                                                           | VDDLS    | Power Supply for the Charge Pump Digital Section.                                                                                                                                                                                                                                                        |

| 10                                                          | RVDD     | Reference Supply.                                                                                                                                                                                                                                                                                        |

| 15                                                          | XREFP    | Reference Oscillator Input.                                                                                                                                                                                                                                                                              |

| 16                                                          | DVDD     | DC Power Supply for Digital (CMOS) Circuitry.                                                                                                                                                                                                                                                            |

| 17                                                          | CEN      | PLL Subsystem Enable. Note that CEN has no effect on the VCO subsystem. Connect CEN to logic high for normal operation.                                                                                                                                                                                  |

| 23                                                          | VTUNE    | VCO Varactor. VTUNE is the tuning port input.                                                                                                                                                                                                                                                            |

| 25                                                          | VCC2     | VCO Analog Supply 2.                                                                                                                                                                                                                                                                                     |

| 27                                                          | VCC1     | VCO Analog Supply 1.                                                                                                                                                                                                                                                                                     |

| 28                                                          | RF_N     | RF Negative Output.                                                                                                                                                                                                                                                                                      |

| 29                                                          | RF_P     | RF Positive Output.                                                                                                                                                                                                                                                                                      |

| 30                                                          | SEN      | PLL Serial Port Enable (CMOS) Logic Input.                                                                                                                                                                                                                                                               |

| 31                                                          | SDI      | PLL Serial Port Data (CMOS) Logic Input.                                                                                                                                                                                                                                                                 |

| 32                                                          | SCK      | PLL Serial Port Clock (CMOS) Logic Input.                                                                                                                                                                                                                                                                |

| 33                                                          | LD/SDO   | Lock Detect/Serial Data Output. This pin can also function as a general-purpose (CMOS) logic output (GPO). See the General-Purpose Output (GPO) section for more information. The drive voltage level on this pin can be either 1.8 V or 3.3 V and is set via Register 0x0B[22].                         |

| 35                                                          | VCCHF    | DC Power Supply for Analog Circuitry.                                                                                                                                                                                                                                                                    |

| 36                                                          | VCCPS    | DC Power Supply for Analog Prescaler.                                                                                                                                                                                                                                                                    |

| 39                                                          | VCCPD    | DC Power Supply for Phase Detector.                                                                                                                                                                                                                                                                      |

| 40                                                          | BIAS     | External Bypass Decoupling for Precision Bias Circuits. The 1.920 V $\pm$ 20 mV reference voltage (BIAS) is generated internally and cannot drive an external load. It must be measured with a 10 G $\Omega$ meter, such as the Agilent 34410A; a 10 M $\Omega$ digital voltage meter reads erroneously. |

|                                                             | EP       | Exposed Pad. The exposed pad must be connected to RF/dc ground.                                                                                                                                                                                                                                          |

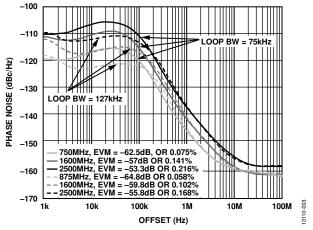

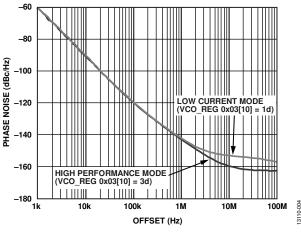

## TYPICAL PERFORMANCE CHARACTERISTICS

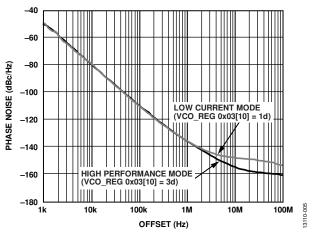

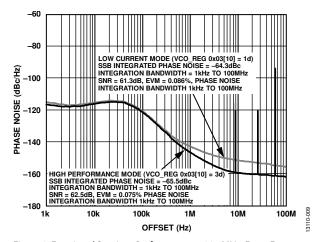

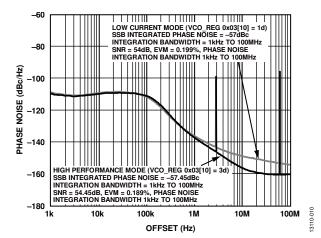

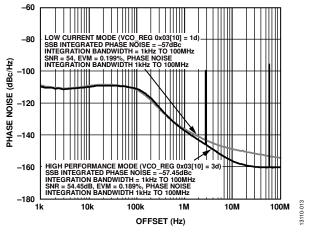

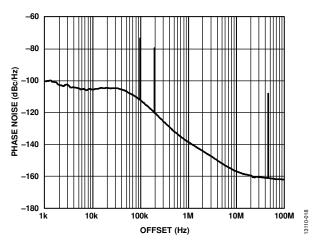

Figure 3. Typical Closed-Loop Integer Phase Noise, 50 MHz PD Frequency, Output Gain = 6 (VCO\_REG 0x07[3:0] = 6d), High Performance Mode (VCO\_REG 0x03[1:0] = 3d), Phase Noise Integrated from 1 kHz to 100 MHz, See Table 13

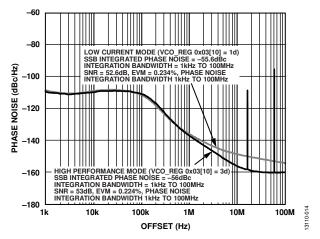

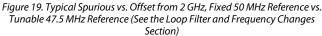

Figure 4. Open-Loop VCO Phase Noise at 1800 MHz

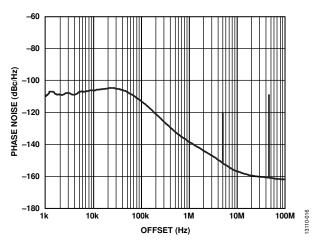

Figure 5. Free Running VCO Phase Noise at 3000 MHz

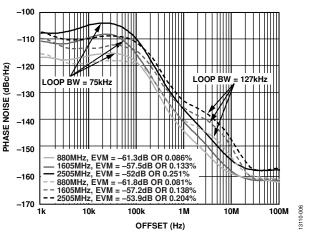

Figure 6. Typical Closed-Loop Fractional Phase Noise, 50 MHz PD Frequency, Output Gain = 6 (VCO\_REG 0x07[3:0] = 6d), High Performance Mode (VCO\_REG 0x03[1:0] = 3d), Phase Noise Integrated from 1 kHz to 100 MHz, See Table 13

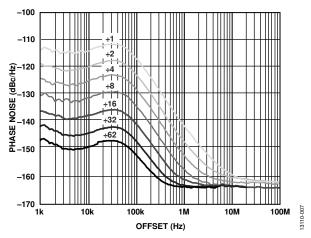

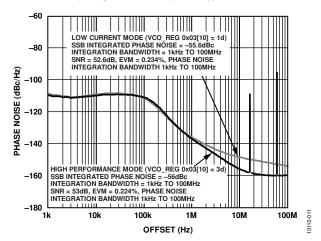

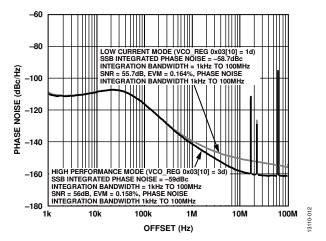

Figure 7. Closed-Loop Phase Noise at 1800 MHz, Divided by 1 to 62, PD Frequency, Loop Filter Bandwidth = 75 kHz (Type 2 from Table 13), High Performance Mode (VCO\_REG 0x03[1:0] = 3d), Subset of Available Output Divide Ratios Shown; Full Range of Output Divide Values Includes 1, 2, 4, 6, 8, ... 58, 60, 62

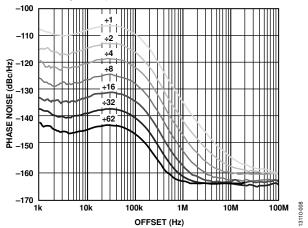

Figure 8. Closed-Loop Phase Noise at 3000 MHz, Divided by 1 to 62, PD Frequency, Loop Filter Bandwidth = 75 kHz (Type 2 from Table 13), High Performance Mode (VCO\_REG 0x03[1:0] = 3d), Subset of Available Output Divide Ratios is Shown; Full Range of Output Divide Values Includes 1, 2, 4, 6, 8, ... 58, 60, 62

Figure 9. Fractional Spurious Performance at 904 MHz, Exact Frequency Mode On, 122.88 MHz XTAL, PFD = 61.44 MHz, Channel Spacing = 200 kHz, Loop Filter Type 2 (See Table 13)

Figure 10. Fractional Spurious Performance at 2118.24 MHz, Exact Frequency Mode On, 122.88 MHz XTAL, PFD = 61.44 MHz, Channel Spacing = 240 kHz, Loop Filter Type 2 (See Table 13)

Figure 11. Fractional Spurious Performance at 2646.96 MHz, Exact Frequency Mode On, 122.88 MHz XTAL, PFD = 61.44 MHz, Channel Spacing = 240 kHz, Loop Filter Type 2 (See Table 13)

Figure 12. Fractional Spurious Performance at 1804 MHz, Exact Frequency Mode On, 122.88 MHz XTAL, PFD = 61.44 MHz, Channel Spacing = 200 kHz, Loop Filter Type 2 (See Table 13)

Figure 13. Fractional Spurious Performance at 2118.24 MHz, Identical Configuration to Figure 10 with Exact Frequency Mode Off

Figure 14. Fractional Spurious Performance at 2646.96 MHz, Identical Configuration to Figure 11 with Exact Frequency Mode Off

#### -120 -130 PHASE NOISE (dBc/Hz) -140 MHz -150 -160 25MHz OUTPUT -170 ∟ 100 1k 10k 100k 1M 10M 100M 3110-015 OFFSET (Hz)

Figure 15. Low Frequency Performance, 100 MHz XTAL, PD Frequency = 50 MHz, Loop Filter Type 3 (See Table 13), Integer Mode, 50 MHz Low-Pass Filter at the Output of HMC832A for the 25 MHz Curve Only, Charge Pump Set to Maximum Value

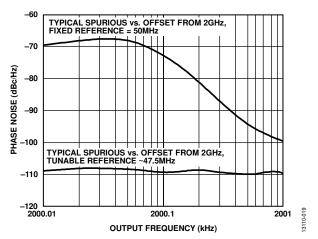

Figure 16. Typical Spurious Emissions at 2000.1 MHz, Tunable 47.5 MHz Reference, Loop Filter Type 2 (see Table 13 and the Loop Filter and Frequency Changes Section)

Figure 17. Open-Loop Phase Noise

Figure 18. Typical Spurious Emissions at 2000.1 MHz, 50 MHz Fixed Reference, 50 MHz PD Frequency, Integer Boundary Spur Inside the Loop Filter Bandwidth (See the Loop Filter and Frequency Changes Section)

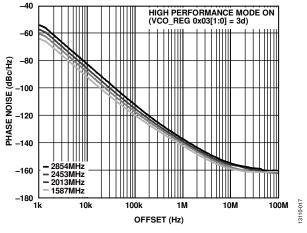

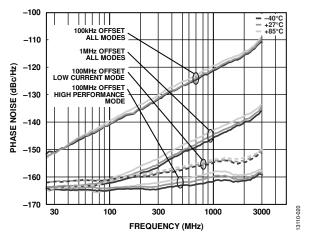

Figure 20. Open-Loop Phase Noise vs. Frequency at Various Temperatures

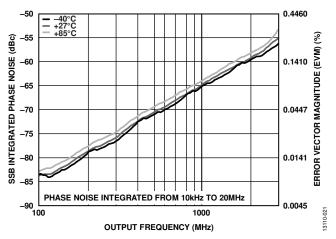

Figure 21. Single Sideband (SSB) Integrated Phase Noise, High Performance Mode, Loop Filter Type 2 (See Table 13)

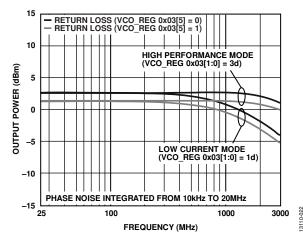

Figure 22. Typical Single-Ended Output Power vs. Frequency (Mid Gain Setting 6 (VCO\_REG 0x07[3:0] = 6d))

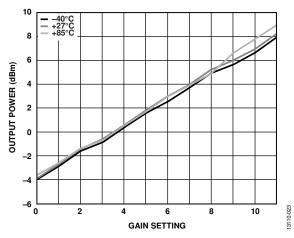

Figure 23. Typical RF Output Power at 2 GHz (Single-Ended) vs. Temperature

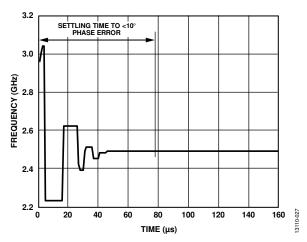

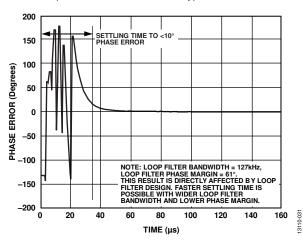

Figure 27. Frequency Settling After Frequency Change, Autocalibration Enabled, Loop Filter Bandwidth = 127 kHz (Type 1, See Table 13)

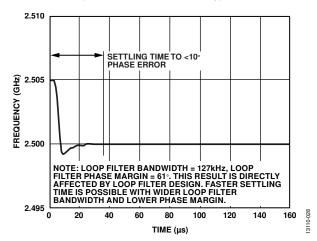

Figure 28. Frequency Settling After Frequency Change, Manual Calibration, Loop Filter Bandwidth = 127 kHz (Type 1 in Table 13)

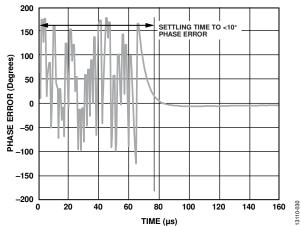

Figure 30. Phase Settling After Frequency Change, Autocalibration Enabled Loop Filter Bandwidth = 127 kHz (Type 1, See Table 13)

Figure 31. Phase Settling After Frequency Change, Manual Calibration

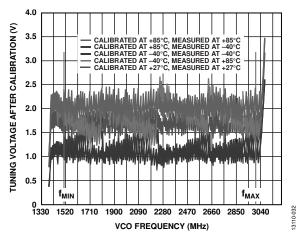

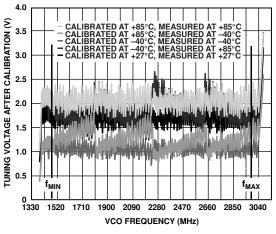

Figure 32. Typical Tuning Voltage After Calibration (See the Loop Filter and Frequency Changes Section)

Figure 33. Current Consumption in Single-Ended Output Configuration, Output Gain Configured in VCO\_REG 0x07[3:0], Differential or Single-Ended Mode Programmed in VCO\_REG 0x03[3:2]

Figure 34. Reference Input Sensitivity, Square Wave, Measured from a 50  $\Omega$ Source with a 100  $\Omega$  External Resistor Termination

Figure 36. Current Consumption in Differential Output Configuration, Output Gain Configured in VCO\_REG 0x07[3:0], Differential or Single-Ended Mode Programmed in VCO\_REG 0x03[3:2]

Figure 37. Reference Input Sensitivity, Sinusoidal Wave, Measured from a 50  $\Omega$  Source with a 100  $\Omega$  External Resistor Termination

O RF\_N

O RF\_P

VTUNE

13110-043

#### SEN C SDL O REF BUEF CONTROL RF BUFFFR FN SCK O LD/SDO C 3 VSPI CNTRL MODULATOR VSPI CHARGE CAI CP C f<sub>O</sub> OR ÷N OR ×2 PUMP Ľ BUFF VCO EN CAL N DIVIDER 님 PHASE REQUENC R DIVIDER PLL BUFF XREFP C CEN C PLL ONLY

# THEORY OF OPERATION

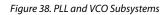

The HMC832A PLL with integrated VCO is composed of two subsystems: PLL subsystem and VCO subsystem, as shown in Figure 38.

### PLL SUBSYSTEM OVERVIEW

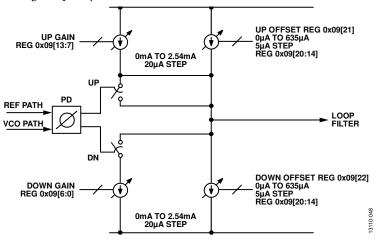

The PLL subsystem divides down the VCO output to the desired comparison frequency via the N-divider (integer value set in Register 0x03, fractional value set in Register 0x04), compares the divided VCO signal to the divided reference signal (reference divider set in Register 0x02) in the phase detector (PD), and drives the VCO tuning voltage via the charge pump (CP) (configured in Register 0x09) to the VCO subsystem. Some of the additional PLL subsystem functions include

- $\Sigma$ - $\Delta$  configuration (Register 0x06).

- Exact frequency mode (configured in Register 0x0C, Register 0x03, and Register 0x04).

- Lock detect (LD) configuration (use Register 0x07 to configure LD and Register 0x0F to configure the LD/SDO output pin).

- External CEN pin used for the hardware PLL enable pin. The CEN pin does not affect the VCO subsystem.

Typically, only writes to the divider registers (integer part uses Register 0x03, fractional part uses Register 0x04) of the PLL subsystem are required for HMC832A output frequency changes.

The divider registers of the PLL subsystem (Register 0x03 and Register 0x04) set the fundamental frequency (1500 MHz to 3000 MHz) of the VCO subsystem. Output frequencies ranging from 25 MHz to 1500 MHz are generated by tuning to the appropriate fundamental VCO frequency (1500 MHz to 3000 MHz) by programming the N divider (Register 0x03 and Register 0x04) and programming the output divider (divide by 1 to 62, in VCO\_REG 0x02) in the VCO subsystem.

For detailed frequency tuning information and an example, see the Frequency Tuning section.

### VCO SUBSYSTEM OVERVIEW

The VCO subsystem consists of a capacitor switched step tuned VCO and an output stage. In typical operation, the VCO subsystem is programmed with the appropriate capacitor switch setting that is executed automatically by the PLL subsystem autocalibration state machine when autocalibration is enabled (Register 0x0A[11] = 0; see the VCO Calibration section for more information). The VCO tunes to the fundamental frequency (1500 MHz to 3000 MHz), and is locked by the CP output from the PLL subsystem. The VCO subsystem controls the output stage of the HMC832A, enabling configuration of

- User defined performance settings (see the Programmable Performance Technology section) that are configured via VCO\_REG 0x03[1:0].

- VCO output divider settings that are configured in VCO\_REG 0x02 (divide by 2 to 62 to generate frequencies from 25 MHz to 1500 MHz, or divide by 1 to generate fundamental frequencies between 1500 MHz and 3000 MHz).

- Output gain settings (VCO\_REG 0x07[3:0]).

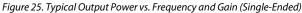

- Output return loss setting (VCO\_REG 0x03[5]). See Figure 26 for more information.

- Single-ended or differential output operation (VCO\_REG 0x03[3:2]).

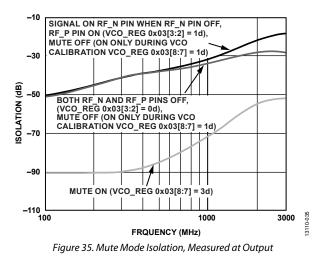

- Mute (VCO\_REG 0x03[8:7]).

# SPI CONFIGURATION OF PLL AND VCO SUBSYSTEMS

The two subsystems (PLL subsystem and VCO subsystem) have their own register maps as shown in the PLL Register Map and VCO Subsystem Register Map sections. Typically, writes to both register maps are required for initialization and frequency tuning operations.

As shown in Figure 38, the PLL subsystem is connected directly to the SPI of the HMC832A, whereas the VCO subsystem is connected indirectly through the PLL subsystem to the

HMC832A SPI. As a result, writes to the PLL register map are written directly and immediately, whereas the writes to the VCO subsystem register map are written to the PLL Register 0x05 and forwarded via the internal VCO SPI (VSPI) to the VCO subsystem. This is a form of indirect addressing.

VCO subsystem registers are write only and cannot be read. For more information, see the VCO Serial Port Interface (VSPI) section.

### VCO Serial Port Interface (VSPI)

The HMC832A communicates with the internal VCO subsystem via an internal 16-bit VCO SPI. The internal serial port controls the step tuned VCO and other VCO subsystem functions.

The internal VSPI runs at the rate of the autocalibration finite state machine (FSM) clock,  $t_{FSM}$  (see the VCO Autocalibration section), where the FSM clock frequency cannot be greater than 50 MHz. The VSPI clock rate is set by Register 0x0A[14:13].

Writes to the control registers of the VCO are handled indirectly via writes to Register 0x05 of the HMC832A. A write to Register 0x05 causes the internal PLL subsystem to forward the packet, MSB first, across its internal serial link to the VCO subsystem, where it is interpreted.

### VSPI Use of Register 0x05

The packet data written into Register 0x05 is subparsed by logic at the VCO subsystem into the following three fields:

Field 1—Bits[2:0]: 3-bit VCO\_ID, target subsystem address = 000b.

Field 2—Bits[6:3]: 4-bit VCO\_REGADDR, the internal register address inside the VCO subsystem.

Field 3—Bits[15:7]: 9-bit VCO\_DATA, the data field to write to the VCO register.

For example, to write 0 1111 1110 into Register 2 of the VCO subsystem (VCO\_ID = 000b), and set the VCO output divider to divide by 62, the following must be written to Register 0x05 = 0 1111 1110b, 0010b, 000b or, equivalently, Register 0x05 = 0x7F10.

During autocalibration, the autocalibration controller writes into the VCO register address specified by the VCO\_ID and VCO\_REGADDR, as stored in Register 0x05[2:0] and Register 0x05[6:3], respectively. Autocalibration requires that these values be zero (Register 0x05[6:0] = 0); otherwise, when they are not zero (Register  $0x05[6:0] \neq 0$ ), autocalibration does not function.

To ensure that the autocalibration functions, it is critical to write Register 0x05[6:0] = 0 after the last VCO subsystem write but prior to an output frequency change that is triggered by a write to either Register 0x03 or Register 0x04.

However, it is impossible to write only Register 0x05[6:0] = 0 (VCO\_ID and VCO\_REGADDR) without writing VCO\_DATA (Register 0x05[15:7]). Therefore, to ensure that VCO\_DATA (Register 0x05[15:7]) is not changed, it is required to read the switch settings provided in Register 0x10[7:0], and then rewrite them to Register 0x05[15:7], as follows:

- 1. Read Register 0x10.

- Write to Register 0x05[15:14] = Register 0x10[7:6]; Register 0x05[13] = 1 (reserved bit); Register 0x05[12:8] = Register 0x10[4:0]; and Register 0x05[7:0] = 0.

Changing the VCO subsystem configuration (see the VCO Subsystem Register Map section) without following this procedure results in a failure to lock to the desired frequency.

For applications not using the read functionality of the HMC832A SPI, in which Register 0x10 cannot be read, it is possible to write Register 0x05 = 0x0 to set Register 0x05[6:0] = 0, which also sets the VCO subband setting equal to zero (Register 0x05[15:7] = 0), effectively programming incorrect VCO subband settings and causing the HMC832A to lose lock. This procedure is then immediately followed by a write to

- Register 0x03, if in integer mode

- Register 0x04, if in fractional mode

This write effectively retriggers the autocalibration state machine, forcing the HMC832A to relock whether in integer or fractional mode.

This procedure causes the HMC832A to lose lock and relock after every VCO subsystem change. Typical output frequency and lock time is shown in Figure 27 and Figure 30, respectively. Lock time is typically in the order of 100  $\mu$ s for a phase settling of 10°, and is dependent on loop filter design (loop filter bandwidth and loop filter phase margin).

### VCO SUBSYSTEM

Figure 40. Simplified Step Tuned VCO

The HMC832A contains a VCO subsystem that can be configured to operate in

- Fundamental frequency (fo) mode (1500 MHz to 3000 MHz).

- Divide by N mode, where N = 2, 4, 6, 8 ... 58, 60, 62 (25 MHz to 1500 MHz).

All modes are VCO register programmable, as shown in Figure 39. One loop filter design can be used for the entire frequency of operation of the HMC832A.

### VCO Calibration

#### **VCO** Autocalibration

The HMC832A uses a step tuned type VCO. A simplified step tuned VCO is shown in Figure 40. A step tuned VCO is a VCO with a digitally selectable capacitor bank allowing the nominal center frequency of the VCO to be adjusted or stepped by switching in and out of the VCO tank capacitors. More than one capacitor can be switched in at a time.

A step tuned VCO allows the user to center the VCO on the required output frequency while keeping the varactor tuning voltage optimized near the midvoltage tuning point of the

HMC832A charge pump. This enables the PLL charge pump to tune the VCO over the full range of operation with both a low tuning voltage and a low tuning sensitivity ( $k_{VCO}$ ).

The VCO switches are normally controlled automatically by the HMC832A using the autocalibration feature. The autocalibration feature is implemented in the internal state machine. It manages the selection of the VCO subband (capacitor selection) when a new frequency is programmed. The VCO switches can also be controlled directly via Register 0x05 for testing or for special purpose operations. Other control bits specific to the VCO are also sent via Register 0x05.

To use a step tuned VCO in a closed loop, the VCO must be calibrated such that the HMC832A knows which switch position on the VCO is optimum for the desired output frequency. The HMC832A supports autocalibration of the step tuned VCO. The autocalibration fixes the VCO tuning voltage at the optimum midpoint of the charge pump output, then measures the free running VCO frequency while searching for the setting, which results in the free running output frequency that is closest to the desired phase-locked frequency. This procedure results in a phase-locked oscillator that locks over a narrow voltage range on the varactor. A typical tuning curve for a step tuned VCO is shown in Figure 41. Note that the tuning voltage stays in a narrow range over a wide range of output frequencies.

Figure 41. Typical VCO Tuning Voltage After Calibration

The calibration is normally run automatically, once for every change of frequency. This autocalibration ensures optimum selection of VCO switch settings vs. time and temperature. The user does not normally need to be concerned about which switch setting is used for a given frequency because this is handled by the autocalibration routine.

The accuracy required in the calibration affects the amount of time required to tune the VCO. The calibration routine searches for the best step setting that locks the VCO at the current programmed frequency and ensures that the VCO stays locked and performs well over its full temperature range without additional calibration, regardless of the temperature at which the VCO was calibrated. Autocalibration can also be disabled, thereby allowing manual VCO tuning. Refer to the Manual VCO Calibration for Fast Frequency Hopping section for more information about manual tuning.

### Autocalibration Using Register 0x05

Autocalibration transfers switch control data to the VCO subsystem via Register 0x05. The address of the VCO subsystem in Register 0x05 is not altered by the autocalibration routine. The address and ID of the VCO subsystem in Register 0x05 must be set to the correct value before autocalibration is executed. For more information, see the VCO Serial Port Interface (VSPI) section.

#### Automatic Relock on Lock Detect Failure

It is possible, by setting Register 0x07[13], to have the VCO subsystem automatically rerun the calibration routine and relock itself if the lock detect indicates an unlocked condition for any reason. With this option, the system attempts to relock only once.

### VCO Autocalibration on Frequency Change

Assuming Register 0x0A[11] = 0, the VCO calibration starts automatically whenever a frequency change is requested. To rerun the autocalibration routine for any reason at the same frequency, rewrite the frequency change with the same value, and the autocalibration routine executes again without changing the final frequency.

### VCO Autocalibration Time and Accuracy

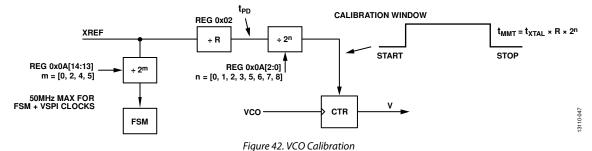

The VCO frequency is counted for  $t_{MMT}$ , the period of a single autocalibration measurement cycle.

$$t_{MMT} = t_{XTAL} \times R \times 2^n \tag{1}$$

where:

$t_{XTAL}$  is the period of the external reference (crystal) oscillator. *R* is the reference path division ratio currently in use, set in Register 0x02.

*n* is set by Register 0x0A[2:0] and results in measurement periods that are multiples of the PD period,  $t_{XTAL} \times R$ .

The VCO autocalibration counter, on average, expects to register N counts, rounded down (floor) to the nearest integer, for every PD cycle.

N is the ratio of the target VCO frequency,  $f_{\rm VCO}$ , to the frequency of the PD,  $f_{\rm PD}$ , where N can be any rational number supported by the N divider.

N is set by the integer and fractional register contents using Equation 2.

$$N = N_{INT} + N_{FRAC}/2^{24}$$

(2)

where:

$N_{INT}$  is the integer set in Register 0x03.

$N_{FRAC}$  is the fractional part set in Register 0x04.

13110-046

The autocalibration state machine and the data transfers to the internal VCO VSPI run at the rate of the FSM clock,  $t_{FSM}$ , where the FSM clock frequency cannot be greater than 50 MHz.

$$t_{FSM} = t_{XTAL} \times 2^m \tag{3}$$

where *m* is 0, 2, 4, or 5 as determined by Register 0x0A[14:13].

The expected number of VCO counts, V, is given by

$$V = floor \left(N \times 2^n\right) \tag{4}$$

The nominal VCO frequency measured,  $f_{VCOM}$ , is given by

$$f_{VCOM} = \mathbf{V} \times f_{XTAL} / (2^n \times R) \tag{5}$$

where the worst case measurement error,  $f_{ERR}$ , is

$$f_{ERR} \approx \pm f_{PD} / 2^{n+1} \tag{6}$$

A 5-bit step tuned VCO, for example, nominally requires five measurements for calibration or in the worst case, six measurements, and therefore, seven VSPI data transfers of 20 clock cycles each. The measurement has a programmable number of wait states, k, of 128 FSM cycles defined by Register 0x0A[7:6] = k. Total calibration time, worst case, is given by

$$t_{CAL} = k128 t_{FSM} + 6t_{PD} 2^n + 7 \times 20 t_{FSM}$$

(7)

or equivalently

$$t_{CAL} = t_{XTAL} \left( 6R \times 2^n + (140 + (k \times 128)) \times 2^m \right)$$

(8)

For guaranteed hold of lock, across temperature extremes, the resolution must be better than 1/8<sup>th</sup> of the frequency step caused by a VCO subband switch change. Better resolution settings show no improvement.

#### VCO Autocalibration Example

The VCO subsystem must satisfy the maximum  $f_{PD}$  limited by the two following conditions:

$$N \ge 16 (f_{INT}), N \ge 20.0 (f_{FRAC})$$

where:

$N = f_{VCO}/f_{PD}$ .  $f_{PD} \le 100$  MHz.  $f_{INT}$  is integer mode.

$f_{FRAC}$  is fractional-N mode. The minimum N values changes depending on the operating mode.

For example, if the VCO subsystem output frequency is to operate at 2.01 GHz and the crystal frequency is  $f_{XTAL} = 50$  MHz, R = 1, and m = 0 (see Figure 42), then  $t_{FSM} = 20$  ns (50 MHz).

When using autocalibration, the maximum autocalibration FSM clock cannot exceed 50 MHz (see Register 0x0A[14:13]). The FSM clock does not affect the accuracy of the measurement; it only affects the time to produce the result. This same clock clocks the 16-bit VCO serial port.

If the time to change frequencies is not a concern, the calibration time for maximum accuracy can be set and, therefore, the measurement resolution is of no concern.

Using an input crystal of 50 MHz (R = 1 and  $f_{\rm PD}$  = 50 MHz), the times and accuracies for calibration using Equation 6 and Equation 8 are listed in Table 7, where minimal tuning time is  $1/8^{\rm th}$  of the VCO band spacing.

Table 7. Autocalibration Example with  $f_{XTAL} = 50$  MHz, R = 1, m = 0

| Control Value Register 0x0A[2:0] | n | <b>2</b> <sup>n</sup> | t <sub>MMT</sub> (μs) | t <sub>caL</sub> (μs) | f <sub>err</sub> Maximum |

|----------------------------------|---|-----------------------|-----------------------|-----------------------|--------------------------|

| 0                                | 0 | 1                     | 0.02                  | 4.92                  | ±25 MHz                  |

| 1                                | 1 | 2                     | 0.04                  | 5.04                  | ±12.5 MHz                |

| 2                                | 2 | 4                     | 0.08                  | 5.28                  | ±6.25 MHz                |