# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### Product data sheet COMPANY PROPRIETARY

## 1. General description

The HITAG product line is well known and established in the contactless identification market.

Due to the open marketing strategy of NXP Semiconductors there are various manufacturers well established for both the transponders / cards as well as the Read/Write Devices. All of them supporting HITAG transponder IC's.

With the new HITAG RO64, NXP is addressing the low end LF market, by offering a preprogrammed, read-only IC variant.

The advantages of this transponder IC are:

- proven HITAG performance

- · easy to assemble because of mega-bumps

- strong RF-modulation

- low cost manufacturing because of preprogrammed TTF code and 210 pF Cres

HITAG RO64 operates in an continuos TTF mode where he modulates the readerfield with it's preprogrammed 64 bit memory content

### 2. Features

#### 2.1 Features list

- Integrated Circuit for Contactless Identification Transponders and Cards

- Integrated resonance capacitor of 210 pF with ± 5% tolerance over full production

- Frequency range 100 to 150 kHz.

- 64 bit preprogrammed TTF response

- 10 years data retention

- Delivery form: sawn, gold-megabumped 8" Wafer

## 3. Ordering information

| Table 1. Ordering inform | nation  |                             |         |

|--------------------------|---------|-----------------------------|---------|

| Type number              | Package |                             |         |

|                          | Name    | Description                 | Version |

| HTCICC6401EW/C1          | Wafer   | Au-bumped die on sawn wafer | -       |

**HITAG RO64**

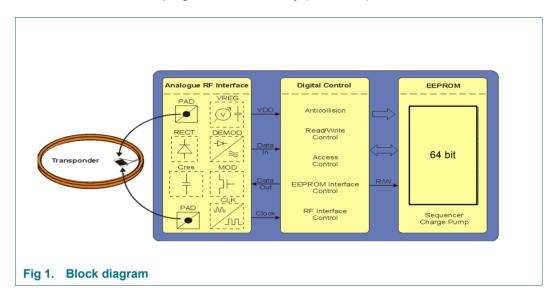

### 4. Block diagram

The HITAG RO64 Transponder requires no external power supply. The contactless interface generates the power supply and the system clock via the resonant circuitry by inductive coupling to the Read/Write Device (RWD). The interface also demodulates data transmitted from the RWD to the HITAG RO64 Transponder, and modulates the magnetic field for data transmission from the HITAG RO64 Transponder to the RWD.

Data are stored in a non-programmable memory (EEPROM).

## 5. Functional description

#### TIF ID7 MSB LSB 1 1 TTF ID6 MSB LSB VBit07 VBit 06 VBit 05 VBit04 P VBit 07-04 VBit 03 VBit02 TIF IDS: MSE LSB VBit00 P VBit03-00 DBit 31 DBit30 DBit 29 PDBit 31-28 VBit 01 DBit 28 TIF ID4: LSB MSE DBit 27 DBit26 DBit 25 DBit 24 PDBit 27-24 DBit 23 DBit 2 DBit 2 TIF ID3: LSB MSE PDBit 23-20 DBit 19 DBit 18 DBit17 DBit 16 P DBit 19-16 DBit 20 DBit15 TTF ID2: LSB MSE DBit 14 DBit13 DBit 12 P DBit 15-12 DBit11 DBit 10 DB it 9 DBit 8 TIF IDI: MSB LSB PDBit 11-8 DBit 4 PDBit 7-4 DBit 7 DBit 6 DB it S DB it 3 DBit 2 TIF ID0: LSB MSE DBit 1 DBit 0 P DBit 3-0 P Colum 0 P Colum 1 PColum 2 P Colum 3 Stopbit P Cloum 0: DBit 31 DBit 27 DBit 23 DBit 19 DBit 15 DBit 11 DBit 7 DBit 3 P Cloum 1: DBit 30 DBit 26 DBit 22 DBit 18 DBit 14 DBit 10 DBit 6 DBit 2 P Cloum 2: DBit 1 DBit 29 DBit 25 DBit 21 DBit 17 DBit 13 DBit 9 DBit 5 P Cloum 3: DBit 28 DBit 24 DBit 20 DBit 16 DBit 8 DBit 4 DBit 0 DBit 12 Fig 2. Memory organization

5.1 Memory organization

The memory is preprogrammed as shown in <u>Figure 2</u>. This data gets continuously sent back as soon as the transponder has sufficient energy.

**HITAG RO64**

## 6. Protocol timing

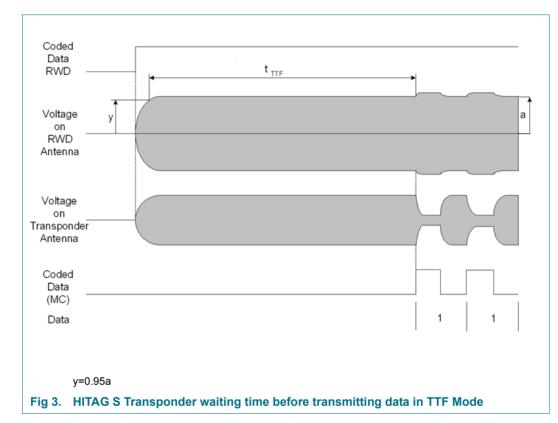

## 6.1 HITAG RO64 Transponder waiting time before transmitting data in TTF Mode

After switching on the powering field, the HITAG RO64 Transponder waits a time  $t_{TTF}$  before transmitting data if it is configured in TTF Mode.

#### Table 2. HITAG RO Transponder programming time

|                  | Min | Тур | Мах | Unit           |  |

|------------------|-----|-----|-----|----------------|--|

| t <sub>TTF</sub> | 565 | 585 | 625 | T <sub>0</sub> |  |

## 7. State Diagram

#### 7.1 General Description of States

#### **Power Off**

The powering magnetic field is switched off or the HITAG RO64 Transponder is out of field.

#### Transponder Talks First (TTF)

The HITAG RO64 Transponder enters this State after being powered up. Entered this State, the HITAG RO64 Transponder continuously transmits the preprogrammed memory data. This data gets transmitted Manchester coded with 2kbit/s.

## 8. Mechanical specification

#### 8.1 Wafer

| <ul> <li>Diameter:</li> </ul> | 200 mm         |

|-------------------------------|----------------|

| Thickness:                    | 280 μm ± 15 μm |

| PGDW:                         | 25080          |

PCM location: reticle area

#### 8.2 Wafer backside

| Material:  | Si                        |

|------------|---------------------------|

| Treatment: | ground and stress release |

• Roughness: R<sub>a</sub> max. 0.5 μm, R<sub>t</sub> max. 5 μm

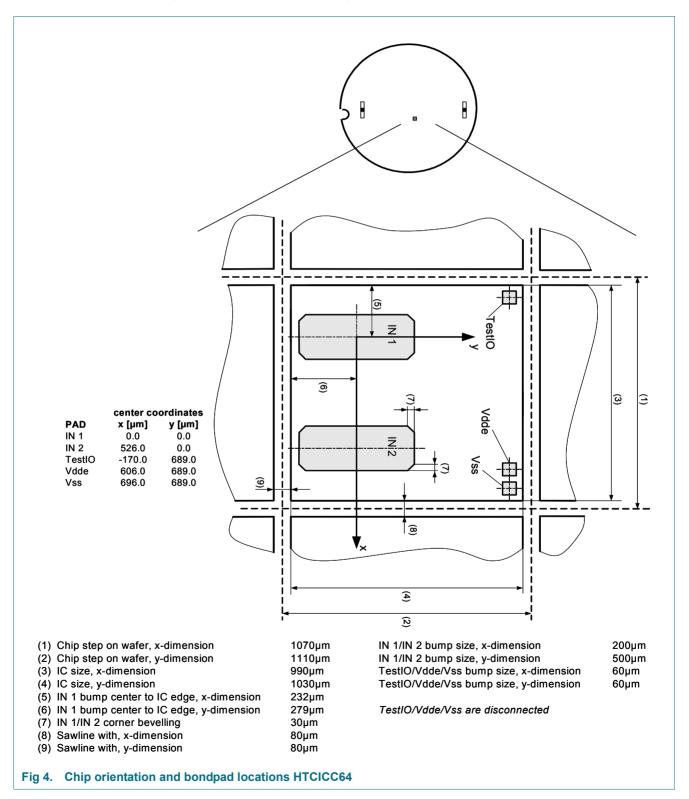

#### 8.3 Chip dimensions

| Chip size:   | x = 1030 μm, y = 990 μm        |

|--------------|--------------------------------|

| Scribe line: | x-line: 80 μm<br>y-line: 80 μm |

#### 8.4 Passivation on front

| <ul> <li>Type:</li> </ul> | Sandwich structure     |

|---------------------------|------------------------|

| Material:                 | PSG / Nitride (on top) |

| Thickness:                | 500 nm / 600 nm        |

#### 8.5 Au bump

- Bump material: > 99.9 % pure Au

- Bump hardness: 35 80 HV 0.005

- Bump shear strength: > 70 MPa

- Bump height: 18 μm

- Bump height uniformity:

- within a die:  $\pm 2 \,\mu m$

- within a wafer:  $\pm 3 \,\mu m$

- wafer to wafer:  $\pm 4 \,\mu m$

- Bump flatness: ± 1.5 μm

- Bump size:

- IN1, IN2: 200 x 500 μm

- VSS, Vdde, TestIO1: 60 x 60 μm

- Bump size variation: ± 5 μm

- Under bump metallization: sputtered TW

#### 8.6 Fail die identification

All fail dies are inked according to electrical test results.

Electronic wafer mapping covers the electrical test results and additionally the results of mechanical / visual inspection.

Remark: Ink dots are not corrected after mechanical/visual inspection.

<sup>1.</sup> Pads  $V_{SS}$ ,  $V_{dde}$  and TestIO are disconnected for sawn wafers

## 9. Chip orientation and bondpad locations

#### 9.1 Chip orientation and bondpad locations

#### **10.1** Absolute maximum ratings

#### Table 3. Absolute maximum ratings<sup>[1][2]</sup>

| Symbol           | Parameter                  | Conditions                                  | Min | Тур | Max  | Unit               |

|------------------|----------------------------|---------------------------------------------|-----|-----|------|--------------------|

| T <sub>stg</sub> | storage temperature range  | -                                           | -55 | -   | +140 | °C                 |

| Tj               | junction temperature       | -                                           | -55 | -   | +140 | °C                 |

| V <sub>ESD</sub> | ESD voltage immunity       | JEDEC<br>JESD 22-A114-B<br>Human Body Model | -   | ±2  | _    | kV <sub>peak</sub> |

| Imax IN1-IN2     | maximum input peak current | -                                           | -   | ±20 | _    | mA <sub>peak</sub> |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the Operating Conditions and Electrical Characteristics section of this specification is not implied.

[2] This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

## 11. Recommended operating conditions

#### Table 4.Operating conditions

| Symbol                  | Parameter                 | Conditions | Min | Typ <mark>[1]</mark> | Max  | Unit               |

|-------------------------|---------------------------|------------|-----|----------------------|------|--------------------|

| T <sub>op</sub>         | operating temperature     | -          | -25 | -                    | +85  | °C                 |

| I <sub>IN1-IN2</sub>    | input current             | -          | -   | -                    | ±10  | mA <sub>peak</sub> |

| V <sub>IN1-IN2 rd</sub> | minimum operating voltage | -          | -   | ±3.5                 | ±4.5 | $V_{\text{peak}}$  |

| f <sub>op</sub>         | operating frequency       | -          | 100 | 125                  | 150  | kHz                |

[1] Typical ratings are not guaranteed. These values listed are at room temperature.

**HITAG RO64**

## **12. Characteristics**

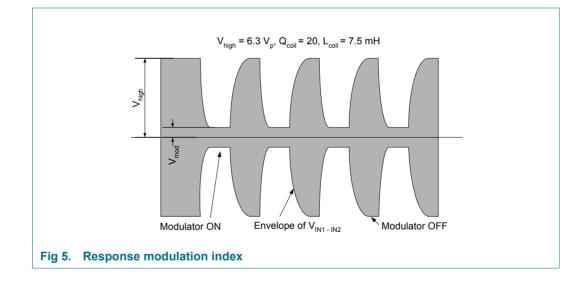

## Table 5.Characteristics $T_{op}$ = -25 to +85 °C

| Symbol              | Parameter                                             | Conditions                                                | Min | Typ <mark>[1]</mark> | Мах | Unit             |

|---------------------|-------------------------------------------------------|-----------------------------------------------------------|-----|----------------------|-----|------------------|

| C <sub>res</sub>    | input capacitance between IN1<br>- IN2 <sup>[2]</sup> | V <sub>IN1-IN2</sub> = 2 V <sub>rms</sub>                 | 199 | 210                  | 221 | pf               |

| P <sub>min rd</sub> | minimum operating supply power <sup>[3][4]</sup>      | V <sub>IN1-IN2</sub> = V <sub>IN1-IN2 rd</sub>            | -   | 20                   | -   | μW               |

| V <sub>clk</sub>    | clock recovery sensitivity                            |                                                           | -   | -                    | 100 | mV <sub>pp</sub> |

| m <sub>mod</sub>    | response modulation index <sup>[5]</sup>              | $m_{mod} = \frac{V_{high} - V_{mod}}{V_{high} + V_{mod}}$ | -   | 85                   | -   | %                |

| t <sub>ret</sub>    | data retention                                        | T <sub>amb</sub> ≤ 55 °C                                  | 10  | -                    | -   | years            |

[1] Typical ratings are not guaranteed. These values listed are at room temperature.

[2] Measured with an HP4285A LCR meter at 125 kHz.

[3] Including losses in resonant capacitor and rectifier.

[4] Determined with:  $Q_{coil}$  = 20,  $L_{coil}$  = 7.5 mH, optimal tuned resonance circuit.

[5] Definition according to Figure 5

## **13. Final wafertest specification**

Minimum yield per wafer: 30 % of 25080 potential good dies.

## 14. References

- [1] General quality specification

- [2] General specification for 8" wafer

- [3] Bumped wafer specification

- [4] Application note HITAG S coil design guide

## **15. Revision history**

| Document ID | Release date  | Data sheet status                                          | Change notice               | Supersedes |

|-------------|---------------|------------------------------------------------------------|-----------------------------|------------|

| 152131      | 20080717      | Product data sheet                                         |                             | 152130     |

|             |               | f the sentence "Data are s<br>" in Section 4 "Block diagra | tored in a non-programmable | memory     |

|             |               | III Section 4 Diock diagra                                 | ann on page z               |            |

| 152130      | 18 March 2008 | Product data sheet add                                     | <u> </u>                    | -          |

## **16. Legal information**

#### **16.1 Data sheet status**

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### 16.2 Definitions

**Short data sheet** — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 16.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk. **Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

**Limiting values** — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

#### 16.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

HITAG - is a trademark of NXP B.V.

## 17. Contact information

For additional information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, send an email to: salesaddresses@nxp.com

## 18. Tables

| Table 1. | Ordering information                       | .1 |

|----------|--------------------------------------------|----|

| Table 2. | HITAG RO Transponder programming time      | .4 |

| Table 3. | Absolute maximum ratings <sup>[1][2]</sup> | .8 |

## **19. Figures**

| Fig 1. | Block diagram                           |

|--------|-----------------------------------------|

| Fig 2. | Memory organization                     |

| Fig 3. | HITAG S Transponder waiting time before |

|        | transmitting data in TTF Mode4          |

| Table 4. | Operating conditions |

|----------|----------------------|

| Table 5. | Characteristics      |

| Table 6: | Revision history 11  |

| Fig 4. | Chip orientation and bondpad locations |

|--------|----------------------------------------|

|        | HTCICC647                              |

| Fig 5. | Response modulation index9             |

## 20. Contents

| 1          | General description 1                      |

|------------|--------------------------------------------|

| 2          | Features 1                                 |

| 2.1        | Features list 1                            |

| 3          | Ordering information 1                     |

| 4          | Block diagram 2                            |

| 5          | Functional description 3                   |

| 5.1        | Memory organization 3                      |

| 6          | Protocol timing 4                          |

| 6.1        | HITAG RO64 Transponder waiting time before |

|            | transmitting data in TTF Mode              |

| 7          | State Diagram 5                            |

| 7.1        | General Description of States 5            |

| 8          | Mechanical specification 5                 |

| 8.1        | Wafer 5                                    |

| 8.2        | Wafer backside                             |

| 8.3<br>8.4 | Chip dimensions                            |

| o.4<br>8.5 | Au bump                                    |

| 8.6        | Fail die identification                    |

| 9          | Chip orientation and bondpad locations 7   |

| 9.1        | Chip orientation and bondpad locations 7   |

| 10         | Limiting values                            |

| 10.1       | Absolute maximum ratings                   |

| 11         | Recommended operating conditions 8         |

| 12         | Characteristics                            |

| 13         | Final wafertest specification              |

| 14         | References                                 |

| 15         | Revision history 11                        |

| 16         | Legal information                          |

| 16.1       | Data sheet status 12                       |

|            |                                            |

16.2

Definitions

12

16.3

Disclaimers

12

16.4

Trademarks

12

17

Contact information

12

18

Tables

13

19

Figures

13

20

Contents

13

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2011.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 17 July 2008 Document identifier: 152131

All rights reserved.