# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### No High-Voltage Bias, Low Harmonic Distortion, 32-Channel, High-Voltage Analog Switch

#### Features

- 32-Channel, High-Voltage Analog Switch

- No High-Voltage Supplies Required

- 32-Channel, Single-Pole, Single-Throw (SPST) Individual Switching or Bank Switching

- 3.3V CMOS Input Logic Level

- 66 MHz Data Shift Clock Frequency

- Silicon-on-Insulator (SOI) High-Voltage Technology for High Performance

- · Standby mode for Low-Power Dissipation

- · Low-Parasitic Capacitance

- DC to 50 MHz Analog Small-Signal Frequency

- 200 kHz to 50 MHz Large-Signal Frequency

- -70 dB Typical Off Isolation at 5.0 MHz

- Excellent Noise Immunity

- Cascadable Serial Data Register with Latches

- Integrated Bleed Resistors on the Outputs (both sides for HV2903, one side for HV2904)

### Applications

- Medical Ultrasound Imaging

- Non-Destructive Testing (NDT) Metal Flaw

Detection

- Piezoelectric Transducer Drivers

- · Inkjet Printer Heads

- · Optical MEMS Modules

### **General Description**

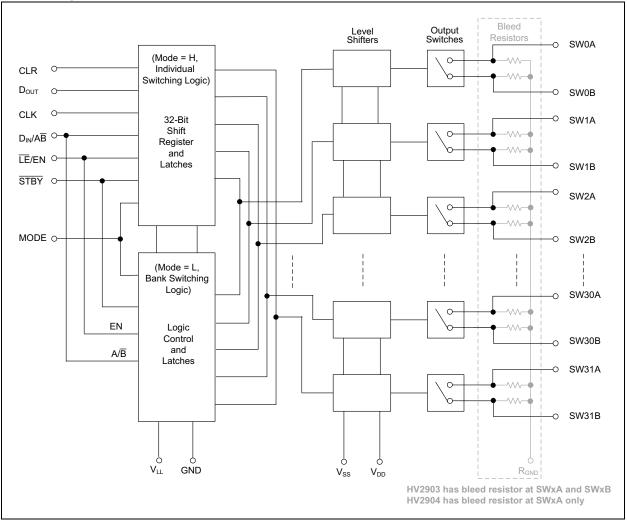

The HV2803/HV2903/HV2904 devices are low harmonic distortion, low charge injection, 32-channel, high-voltage analog switches without high-voltage supplies. They are intended for use in applications requiring high-voltage switching controlled by low-voltage control signals, such as medical ultrasound imaging, driving piezoelectric transducers and printers.

The HV2903 device has integrated bleed resistors at both sides of the switches; the HV2904 device has bleed resistors at one side only, while the HV2803 device has no bleed resistors. The bleed resistor eliminates voltage build-up on capacitive loads, such as piezoelectric transducers.

The HV2803/HV2903/HV2904 devices have two modes of operation determined by the MODE pin input. MODE input high enables an individual Switching mode of 32-channel SPST switches and MODE input low enables a Bank Switching mode of 16-Pole Double-Throw (16PDT) switches to support bank switching for probe selection.

The devices require only  $\pm 6V$  or  $\pm 5V$  low-voltage supplies and no high-voltage supplies. However, all of the analog switches can transmit  $\pm 100V$  high-voltage pulses.

#### Package Type

|   |            |            |            |            | (T         | ор         | Vi         | ew         | *)         |            |            |    |            |            |

|---|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|----|------------|------------|

|   | 1          | 2          | 3          | 4          | 5          | 6          | 7          | 8          | 9          | 10         | 11         | 12 | 13         | 14         |

| A | $\bigcirc$ | Õ          | $\bigcirc$ | Õ          | Õ          | Õ          | Õ          | Õ          | Õ          | $\bigcirc$ | Õ          | Õ  | Õ          | Õ          |

| в |            |            |            |            |            |            |            |            |            |            |            |    |            | Õ          |

| с | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            |            |            |            |            |    | $\bigcirc$ | $\bigcirc$ |

| D | $\bigcirc$ | (          |            |            |            |            |            |            |            |            |            |    | ()         | $\bigcirc$ |

| Е | (          | (          |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | (          |            |    | ()         | ()         |

| F | $\bigcirc$ | $\bigcirc$ |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | Õ          | Õ          | $\bigcirc$ |            |    | ()         | (          |

| G | $\bigcirc$ | (          |            |            | $\bigcirc$ | Õ          | $\bigcirc$ | (          | $\bigcirc$ | (          |            |    | ()         | ()         |

| н | ()         | (          |            |            | $\bigcirc$ | (          | (          | (          | ()         | (_)        |            |    | ()         | ()         |

| J | $\bigcirc$ | _          |            |            | (          | (          | (          | (          | (          | ()         |            |    | (_)        | (          |

| к | $\bigcirc$ | (          |            |            | $\bigcirc$ | $\bigcirc$ | (          | (          | (          | ()         |            |    | ()         | (          |

| L | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            |            |            |            |            |    | $\bigcirc$ | $\bigcirc$ |

| М | $\bigcirc$ | (          |            |            |            |            |            |            |            |            |            |    | $\bigcirc$ | $\bigcirc$ |

| Ν | $\bigcirc$ | $\bigcirc$ | (          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | Õ          | Õ          | $\bigcirc$ | $\bigcirc$ | (  | (          | $\bigcirc$ |

| Р | $\bigcirc$ | $\bigcirc$ | (          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | Õ          | Õ          | $\bigcirc$ | $\bigcirc$ | (  | (          | $\bigcirc$ |

### **Block Diagram**

### 1.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings†

| Logic Supply Voltage (V <sub>LL</sub> )               | -0.5V to +6.6V                 |

|-------------------------------------------------------|--------------------------------|

| Positive Supply Voltage (V <sub>DD</sub> )            | -0.5V to +6.6V                 |

| Negative Supply Voltage (V <sub>SS</sub> )            | +0.5V to -6.6V                 |

| Logic Input Voltage (V <sub>IN</sub> )                | 0.5V to V <sub>LL</sub> + 0.3V |

| DGND to GND                                           | -0.3V to +0.3V                 |

| Analog Signal Range (V <sub>SIG</sub> )               | 110V to +110V                  |

| Peak Analog Signal Current/Channel (I <sub>PK</sub> ) | 3A                             |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**<sup>(1,2,3)</sup>

| Parameters                         | Sym.             | Min.                | Тур. | Max.                | Units | Conditions |

|------------------------------------|------------------|---------------------|------|---------------------|-------|------------|

| Logic Supply Voltage               | $V_{LL}$         | 3                   |      | 3.6                 | V     |            |

| Positive Supply Voltage            | $V_{DD}$         | 4.5                 | _    | 6.3                 | V     |            |

| Negative Supply Voltage            | V <sub>SS</sub>  | -6.3                | _    | -4.5                | V     |            |

| High-Level Input Voltage           | V <sub>IH</sub>  | 0.9 V <sub>LL</sub> | _    | $V_{LL}$            | V     |            |

| Low-Level Input Voltage            | V <sub>IL</sub>  | 0                   | _    | 0.1 V <sub>LL</sub> | V     |            |

| Analog Signal Voltage Peak-to-Peak | V <sub>SIG</sub> | -100                | _    | 100                 | V     |            |

**Note 1:** Power-up sequence is  $V_{SS}$ ,  $V_{DD}$  and then  $V_{LL}$ . Power-down sequence is the reverse of power-up.

**2:**  $V_{SIG}$  must be  $V_{SS} \le V_{SIG} \le V_{DD}$  or floating during power-up/down transition.

3: Rise and fall times of power supplies,  $V_{LL}$ ,  $V_{DD}$  and  $V_{SS}$  should be greater than 1.0 ms.

### DC ELECTRICAL CHARACTERISTICS

Unless otherwise specified,  $V_{DD}$  = 6.0V,  $V_{SS}$  = -6.0V,  $V_{LL}$  = 3.3V,  $T_{AMB}$  = +25°C. **Boldface** specifications apply over the full operating temperature range.

| Parameters                                          | Sym.              | Min. | Тур. | Max. | Units | Conditions                                                                        |

|-----------------------------------------------------|-------------------|------|------|------|-------|-----------------------------------------------------------------------------------|

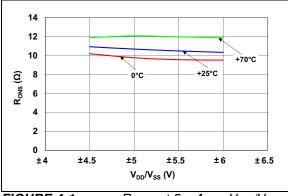

| Small-Signal Switch                                 | R <sub>ONS</sub>  | _    | 10   | 15   | Ω     | I <sub>SIG</sub> = 5 mA                                                           |

| On-Resistance                                       |                   | _    | 10.4 | —    | Ω     | V <sub>DD</sub> = +5V, V <sub>SS</sub> = -5V, I <sub>SIG</sub> = 5 mA<br>(Note 1) |

|                                                     |                   | —    | 10   | 15   | Ω     | I <sub>SIG</sub> = 200 mA                                                         |

| Small-Signal Switch<br>On-Resistance Matching       | ΔR <sub>ONS</sub> | —    | 5    | 20   | %     | I <sub>SIG</sub> = 5 mA                                                           |

| Large-Signal Switch<br>On-Resistance                | R <sub>ONL</sub>  | —    | 9    | —    | Ω     | V <sub>SIG</sub> = 90V, I <sub>SIG</sub> = 1A<br>(Note 1)                         |

| Value of Output Bleed Resistor (HV2903/HV2904 only) | R <sub>INT</sub>  | 20   | 35   | 50   | kΩ    | Output switch to R <sub>GND</sub> ,<br>I <sub>RINT</sub> = 0.1 mA                 |

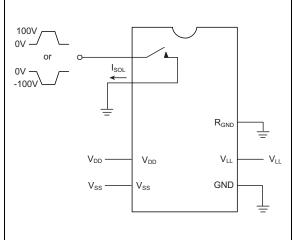

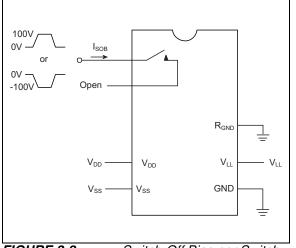

| Switch Off Leakage per SW                           | I <sub>SOL</sub>  | —    | —    | 3    | μA    | At 49 μs with V <sub>SIG</sub> = +100V,<br>50 μs pulse (see Figure 3-1)           |

|                                                     |                   |      | _    | 3    | μA    | At 49 μs with V <sub>SIG</sub> = -100V,<br>50 μs pulse (see Figure 3-1)           |

Note 1: Specification is obtained by characterization and is not 100% tested.

**2:** Design guidance only.

### DC ELECTRICAL CHARACTERISTICS (CONTINUED)

| Parameters                                       | Sym.              | Min.     | Тур. | Max. | Units | Conditions                                                                |

|--------------------------------------------------|-------------------|----------|------|------|-------|---------------------------------------------------------------------------|

| HV2803                                           |                   |          |      |      | I     |                                                                           |

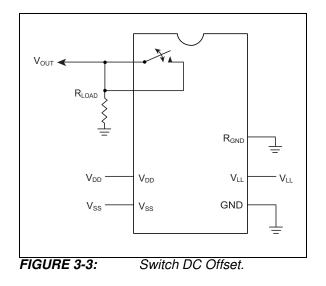

| Switch Off Bias per SW                           | I <sub>SOB</sub>  | -        | -    | 3    | μA    | V <sub>SIG</sub> = +100V, 400 μs pulse<br>(see Figure 3-2)                |

|                                                  |                   | —        | —    | 4    | mA    | V <sub>SIG</sub> = -100V, 12 μs pulse<br>(see Figure 3-2) <b>(Note 1)</b> |

| HV2903                                           | ·                 |          |      |      |       |                                                                           |

| Switch Off Bias per SW                           | I <sub>SOB</sub>  | —        | —    | 3    | μA    | V <sub>SIG</sub> = +100V, 400 µs pulse<br>(see Figure 3-2)                |

|                                                  |                   | —        | —    | 8    | mA    | V <sub>SIG</sub> = -100V, 12 μs pulse<br>(see Figure 3-2) <b>(Note 1)</b> |

| HV2904                                           |                   |          |      |      |       |                                                                           |

| Switch Off Bias per SWA (with bleed resistor)    | I <sub>SOB</sub>  | _        | _    | 3    | μA    | V <sub>SIG</sub> = +100V, 400 μs pulse<br>(see Figure 3-2)                |

|                                                  |                   | —        | —    | 8    | mA    | V <sub>SIG</sub> = -100V, 12 μs pulse<br>(see Figure 3-2) <b>(Note 1)</b> |

| Switch Off Bias per SWB (without bleed resistor) |                   | —        | -    | 3    | μA    | V <sub>SIG</sub> = +100V, 400 µs pulse<br>(see Figure 3-2)                |

|                                                  |                   | —        | -    | 4    | mA    | V <sub>SIG</sub> = -100V, 12 μs pulse<br>(see Figure 3-2) <b>(Note 1)</b> |

| Switch Off DC Offset                             | V <sub>OS</sub>   | _        | 1    | 10   | mV    | R <sub>LOAD</sub> = 25 kΩ (HV2803), 50 kΩ (HV2904                         |

| Switch On DC offset                              |                   | —        | 1    | 10   |       | No load (HV2903) (see Figure 3-3)                                         |

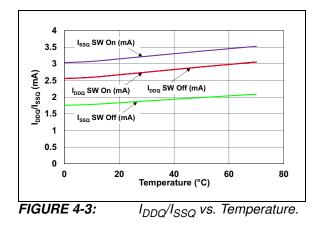

| Quiescent V <sub>DD</sub> Supply Current         | I <sub>DDQ</sub>  | —        | —    | 7    | mA    | All switches off                                                          |

| Quiescent V <sub>SS</sub> Supply Current         | I <sub>SSQ</sub>  |          |      | 5    | mA    |                                                                           |

| Quiescent V <sub>DD</sub> Supply Current         | I <sub>DDQ</sub>  |          | _    | 8    | mA    | All switches on, V <sub>SW</sub> = 1V                                     |

| Quiescent V <sub>SS</sub> Supply Current         | I <sub>SSQ</sub>  |          | —    | 8    | mA    |                                                                           |

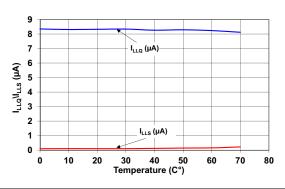

| Quiescent V <sub>LL</sub> Supply Current         | I <sub>LLQ</sub>  | —        | 1    | 10   | μA    | All logic inputs are static                                               |

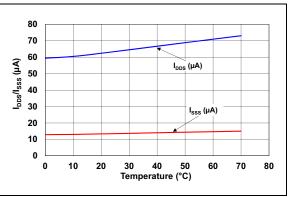

| Standby V <sub>DD</sub> Supply Current           | I <sub>DDS</sub>  |          | 63   | 150  | μA    | STBY = 0V                                                                 |

| Standby V <sub>SS</sub> Supply Current           | I <sub>SSS</sub>  |          | 13   | 100  | μA    |                                                                           |

| Standby V <sub>LL</sub> Supply Current           | I <sub>LLS</sub>  | <u> </u> | —    | 2    | μA    | STBY = 0V                                                                 |

| Switch Output Peak Current                       | I <sub>SW</sub>   | 2        | 3    |      | A     | V <sub>SIG</sub> duty cycle < 0.1% (Note 1)                               |

| Output Switching Frequency                       | f <sub>SW</sub>   |          | —    | 50   | kHz   | Duty cycle = 50% (Note 1)                                                 |

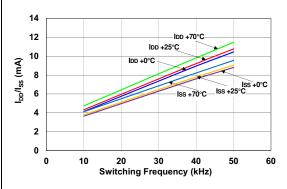

| Average V <sub>DD</sub> Supply Current           | I <sub>DD</sub>   | <u> </u> | 11   | 25   | mA    | All output switches are turning on and off                                |

| Average V <sub>SS</sub> Supply Current           | I <sub>SS</sub>   | <u> </u> | 9    | 20   | mA    | at 50 kHz with no load, V <sub>SIG</sub> = 0V                             |

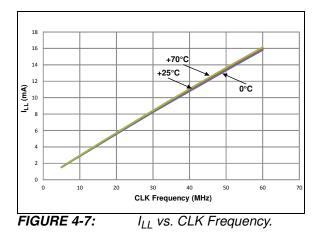

| Average V <sub>LL</sub> Supply Current           | ILL               | <u> </u> | 3    | 6    | mA    | f <sub>CLK</sub> = 5.0 MHz                                                |

| Data Out Source Current                          | I <sub>SOR</sub>  | 10       |      | -    | mA    | $V_{OUT} = V_{LL} - 0.7V$                                                 |

| Data Out Sink Current                            | I <sub>SINK</sub> | 10       | —    |      | mA    | V <sub>OUT</sub> = 0.7V                                                   |

| Logic Input Capacitance                          | C <sub>IN</sub>   | —        | 8    | —    | pF    | (Note 2)                                                                  |

**Note 1:** Specification is obtained by characterization and is not 100% tested.

**2:** Design guidance only.

### **AC ELECTRICAL CHARACTERISTICS**

Unless otherwise specified,  $V_{DD}$  = 6.0V,  $V_{SS}$  = -6.0V,  $V_{LL}$  = 3.3V,  $T_{AMB}$  = +25°C. **Boldface** specifications apply over the full operating temperature range.

| the full operating temperature ra  | nge.                            |      | i    | i    | i     |                                                                                             |

|------------------------------------|---------------------------------|------|------|------|-------|---------------------------------------------------------------------------------------------|

| Parameters                         | Sym.                            | Min. | Тур. | Max. | Units | Conditions/Comments                                                                         |

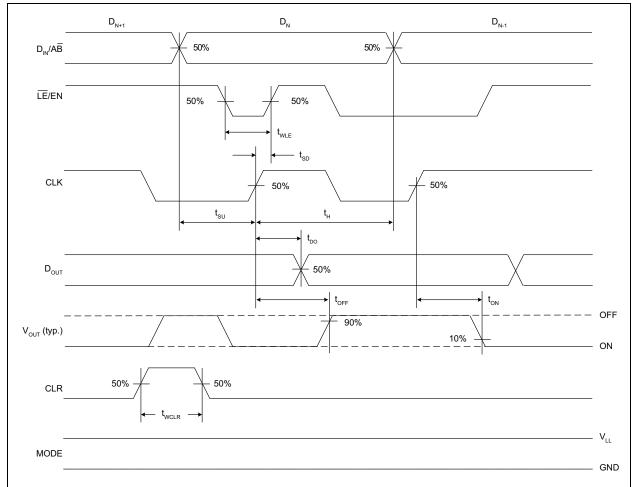

| Setup Time before LE/EN Rises      | t <sub>SD</sub>                 | 25   | _    | _    | ns    | (Note 1)                                                                                    |

| Time Width of LE/EN                | t <sub>WLE</sub>                | 12   | _    | _    | ns    | (Note 1)                                                                                    |

| Clock Delay Time to Data Out       | t <sub>DO</sub>                 | _    | —    | 13.5 | ns    |                                                                                             |

| Time Width of CLR                  | t <sub>WCLR</sub>               | 55   | —    | —    | ns    | (Note 1)                                                                                    |

| Setup Time Data to Clock           | t <sub>SU</sub>                 | 1.5  |      |      | ns    | (Note 1)                                                                                    |

| Hold Time Data from Clock          | t <sub>H</sub>                  | 1.5  | —    | —    | ns    | (Note 1)                                                                                    |

| Clock Frequency                    | f <sub>CLK</sub>                | —    | _    | 66   | MHz   | 50% duty cycle, $f_{DIN} = (1/2)f_{CLK}$ ,<br>C <sub>DOUT</sub> = 20 pF (Note 1)            |

| Clock Rise and Fall Times          | t <sub>R</sub> , t <sub>F</sub> | —    | —    | 50   | ns    |                                                                                             |

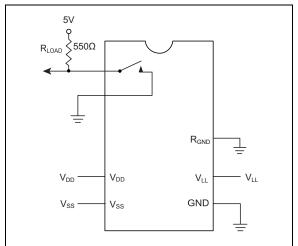

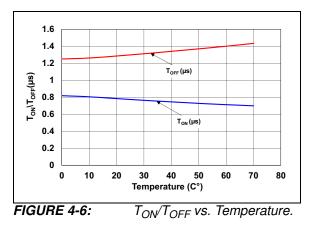

| Turn-On Time                       | t <sub>ON</sub>                 | —    | —    | 5    | μs    | $V_{SIG}$ = 5V, $R_{LOAD}$ = 550 $\Omega$                                                   |

| Turn-Off Time                      | t <sub>OFF</sub>                | —    |      | 5    |       | (see Figure 3-4)                                                                            |

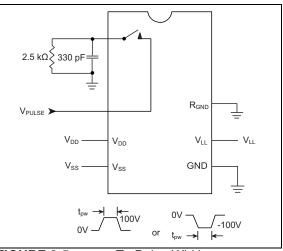

| Input Large-Signal Pulse Width     | t <sub>PW</sub>                 | _    | _    | 2.5  | μs    | V <sub>PULSE</sub> = 0V to ±100V,<br>Measured at 90% amplitude<br>(see Figure 3-5) (Note 1) |

| Wake-up Time from Standby to       | t <sub>WU</sub>                 |      |      | 10   | μs    | Bank Switching mode (MODE = L)                                                              |

| Digital Logic Normal Operation     |                                 |      | —    | 10   | μs    | Individual Switching mode<br>(MODE = H) (Note 1)                                            |

| Maximum V <sub>SIG</sub> Slew Rate | dv/dt                           | _    | _    | 20   | V/ns  | (Note 1)                                                                                    |

| Analog Small-Signal Frequency      | f <sub>BWS</sub>                | —    | 50   | —    | MHz   | (Note 1)                                                                                    |

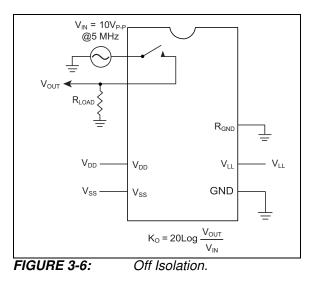

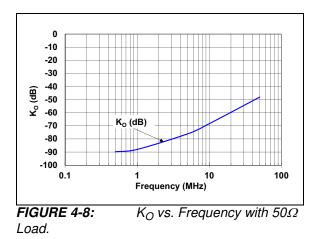

| Off Isolation                      | K <sub>O</sub>                  | _    | -57  | -51  | dB    | f = 5.0 MHz,1.0 kΩ/15 pF load<br>(see Figure 3-6) <b>(Note 1)</b>                           |

|                                    |                                 | _    | -70  | -65  |       | f = 5.0 MHz, 50Ω load<br>(see Figure 3-6) <b>(Note 1)</b>                                   |

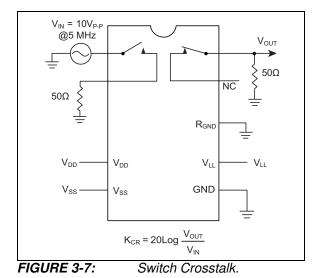

| Switch Crosstalk                   | K <sub>CR</sub>                 | _    | -70  | -60  | dB    | f = 5.0 MHz, 50Ω load<br>(see Figure 3-7) <b>(Note 1)</b>                                   |

| Off Capacitance SW to GND          | C <sub>SG(OFF)</sub>            |      | 9    |      | pF    | V <sub>SIG</sub> = 50 mV@1 MHz, no load                                                     |

| On Capacitance SW to GND           | C <sub>SG(ON)</sub>             |      | 27   |      |       | (Note 1)                                                                                    |

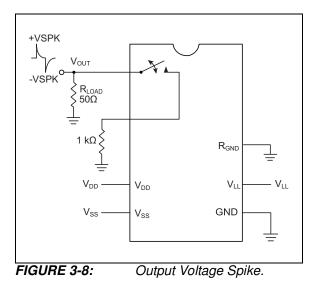

| Output Voltage Spike at SWA,       | +V <sub>SPK</sub>               | _    | —    | 100  | mV    | $R_{LOAD} = 50\Omega$ . (see Figure 3-8)                                                    |

| SWB                                | -V <sub>SPK</sub>               | -150 |      |      |       | (Note 1)                                                                                    |

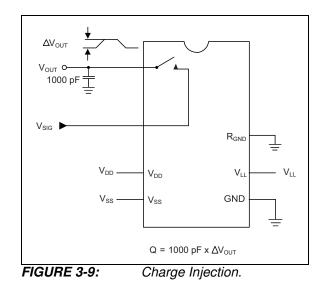

| Charge Injection                   | QC                              |      | 200  |      | рС    | See Figure 3-9 (Note 1)                                                                     |

| Second Harmonic Distortion         | HD2                             | —    | -68  | -60  | dBc   | V <sub>SIG</sub> = 1.5 V <sub>PP</sub> @ 5 MHz,<br>50Ω load <b>(Note 1)</b>                 |

|                                    |                                 |      | -65  | -60  | dBc   | V <sub>SIG</sub> = 1.5 V <sub>PP</sub> @ 5 MHz,<br>1 kΩ/15 pF load <b>(Note 1)</b>          |

**Note 1:** Specification is obtained by characterization and is not 100% tested.

### **TEMPERATURE SPECIFICATION**

| Parameters                         | Sym.           | Min. | Тур. | Max. | Units | Conditions |

|------------------------------------|----------------|------|------|------|-------|------------|

| Temperature Range                  |                | _    |      |      |       |            |

| Operating Temperature Range        | T <sub>A</sub> | 0    | —    | +70  | °C    |            |

| Storage Temperature Range          | T <sub>A</sub> | -65  | —    | +150 | °C    |            |

| Maximum Junction Temperature       | Т <sub>Ј</sub> | -    | —    | +125 | °C    |            |

| Package Thermal Resistance         |                | _    |      |      |       |            |

| Thermal Resistance, 132-Ball TFBGA | $\theta_{JA}$  | _    | 22   | —    | °C/W  |            |

### 1.1 Logic Timing and Truth Table

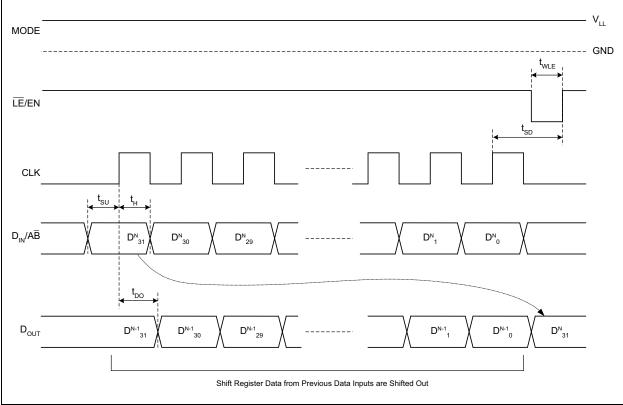

Figure 1-1 shows the timing of the AC characteristic parameters graphically.

FIGURE 1-1: Logic Input Timing Diagram.

| IADLE |          |          |           |      | ADL |     |   | -   |             |       | -   |      |       |     |         |         |      |         |

|-------|----------|----------|-----------|------|-----|-----|---|-----|-------------|-------|-----|------|-------|-----|---------|---------|------|---------|

| STBY  | MODE     | D0       | <b>D1</b> |      | D15 | D16 |   | D31 | $D_{IN}/AB$ | LE/EN | CLR | SW0  | SW1   |     | SW15    | SW16    |      | SW31    |

| Н     | Н        | L        | —         |      | —   |     |   | _   | Х           | L     | L   | OFF  |       |     | —       | —       |      | _       |

| Н     | Н        | Н        | _         |      | _   | _   |   | _   | Х           | L     | L   | ON   | _     |     | —       | —       |      | Ι       |

| Н     | Н        |          | L         |      | _   |     |   | _   | Х           | L     | L   |      | OFF   |     | —       | —       |      | _       |

| Н     | Н        | —        | Н         |      | _   | _   |   |     | Х           | L     | L   | _    | ON    |     |         | —       |      | _       |

| Н     | Н        | —        | —         |      |     |     |   |     | Х           | L     | L   |      |       |     |         | —       |      | _       |

| Н     | Н        | —        | —         |      |     |     |   |     | Х           | L     | L   | _    | _     |     |         |         |      | _       |

| Н     | Н        | —        | —         |      | L   | _   |   |     | Х           | L     | L   | _    | _     |     | OFF     | —       |      | _       |

| Н     | Н        | —        | —         | •••• | Н   | _   |   |     | Х           | L     | L   | _    | _     |     | ON      | —       |      | _       |

| Н     | Н        | —        | —         |      |     | L   |   |     | Х           | L     | L   | _    | _     |     |         | OFF     |      | —       |

| Н     | Н        | —        | —         |      |     | Н   |   |     | Х           | L     | L   | _    | _     |     |         | ON      |      | _       |

| Н     | Н        | —        | —         |      |     | _   |   |     | Х           | L     | L   | _    | _     |     |         | —       |      | —       |

| Н     | Н        | —        | —         |      |     | _   |   |     | Х           | L     | L   | _    | _     |     |         | —       |      | _       |

| Н     | Н        | —        | —         |      |     | _   |   | L   | Х           | L     | L   | _    | _     |     |         | —       |      | OFF     |

| Н     | Н        | —        | —         |      |     |     |   | Н   | Х           | L     | L   | _    | _     |     |         |         |      | ON      |

| Н     | Н        | Х        | Х         | Х    | Х   | Х   | Х | Х   | Х           | Н     | L   |      | HC    | DLD | PREVIC  | OUS STA | ΤE   |         |

| Н     | Н        | Х        | Х         | Х    | Х   | Х   | Х | Х   | Х           | Х     | Н   |      |       | ۹LL | SWITCH  | HES OFF | =    |         |

| Н     | L        | Х        | Х         | Х    | Х   | Х   | Х | Х   | L           | Н     | Х   | EVEN | SWITC | CHE | S OFF & | ODD SV  | NITO | CHES ON |

| Н     | L        | Х        | Х         | Х    | Х   | Х   | Х | Х   | Н           | Н     | Х   | EVEN | SWITC | CHE | SON&    | ODD SW  | /ITC | HES OFF |

| Н     | L        | Х        | Х         | Х    | Х   | Х   | Х | Х   | Х           | L     | Х   |      |       | 4LL | SWITCH  | HES OFF | =    |         |

| L     | Х        | Х        | Х         | Х    | Х   | Х   | Х | Х   | Х           | Х     | Х   | AL   | L SWI | тсн | IES OFF | , STANE | SY S | TATE    |

|       | d. V - I | <b>.</b> |           |      |     |     |   |     |             |       |     |      |       |     |         |         |      |         |

### TABLE 1-1: TRUTH TABLE<sup>(1,2,3,4,5,6)</sup>

**Legend:** X = Don't care; L = Low; H = High.

Note 1: The 32 switches operate independently (when MODE = H).

- 2: Serial data is clocked in on the L to H transition of the CLK (when MODE = H).

- **3:** All 32 switches go to a state retaining their latched condition at the rising edge of LE/EN. When LE/EN is low, the shift registers' data flows through the latch (when MODE = H).

- 4:  $D_{OUT}$  is high when data in Register 31 is high (when MODE = H).

- 5: Shift register clocking has no effect on the switch states if  $\overline{\text{LE}}/\text{EN}$  is high (when MODE = H).

- **6:** The CLR (clear) input overrides all the inputs (when MODE = H).

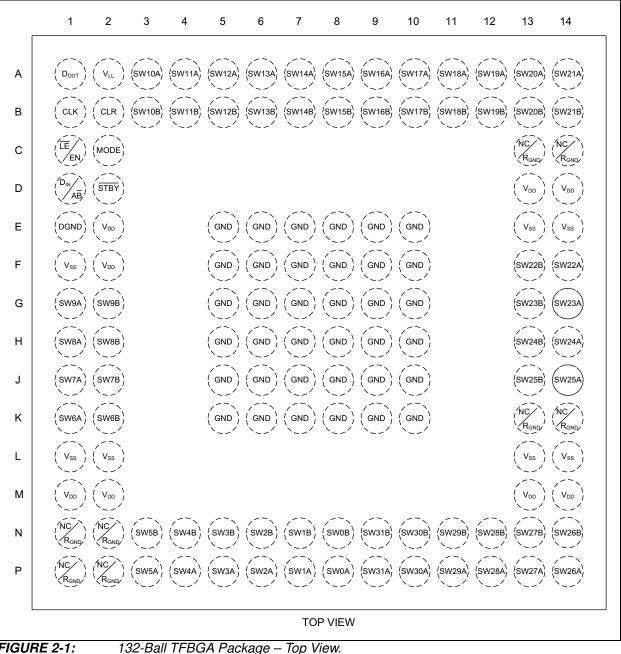

#### 2.0 **PACKAGE PIN CONFIGURATION AND** FUNCTION DESCRIPTION

This section details the pin designation for the 132-Ball TFBGA package (Figure 2-1). The description of the pins are listed in Table 2-1.

FIGURE 2-1:

|            | Syı                 | nbol                |                                                                                                                                        |

|------------|---------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | HV2803              | HV2903,<br>HV2904   | Description                                                                                                                            |

| A1         | D <sub>OUT</sub>    | D <sub>OUT</sub>    | Data Out Logic Output                                                                                                                  |

| A2         | V <sub>LL</sub>     | V <sub>LL</sub>     | Logic Supply Voltage                                                                                                                   |

| A3         | SW10A               | SW10A               | Analog Switch 10 Terminal A                                                                                                            |

| A4         | SW11A               | SW11A               | Analog Switch 11 Terminal A                                                                                                            |

| A5         | SW12A               | SW12A               | Analog Switch 12 Terminal A                                                                                                            |

| A6         | SW13A               | SW13A               | Analog Switch 13 Terminal A                                                                                                            |

| A7         | SW14A               | SW14A               | Analog Switch 14 Terminal A                                                                                                            |

| A8         | SW15A               | SW15A               | Analog Switch 15 Terminal A                                                                                                            |

| A9         | SW16A               | SW16A               | Analog Switch 16 Terminal A                                                                                                            |

| A10        | SW17A               | SW17A               | Analog Switch 17 Terminal A                                                                                                            |

| A11        | SW18A               | SW18A               | Analog Switch 18 Terminal A                                                                                                            |

| A12        | SW19A               | SW19A               | Analog Switch 19 Terminal A                                                                                                            |

| A13        | SW20A               | SW20A               | Analog Switch 20 Terminal A                                                                                                            |

| A14        | SW21A               | SW21A               | Analog Switch 21 Terminal A                                                                                                            |

| B1         | CLK                 | CLK                 | Clock Logic Input for Shift Register                                                                                                   |

| B2         | CLR                 | CLR                 | Latch Clear Logic Input                                                                                                                |

| B3         | SW10B               | SW10B               | Analog Switch 10 Terminal B                                                                                                            |

| B4         | SW11B               | SW11B               | Analog Switch 11 Terminal B                                                                                                            |

| B5         | SW12B               | SW12B               | Analog Switch 12 Terminal B                                                                                                            |

| B6         | SW13B               | SW13B               | Analog Switch 13 Terminal B                                                                                                            |

| B7         | SW14B               | SW14B               | Analog Switch 14 Terminal B                                                                                                            |

| B8         | SW15B               | SW15B               | Analog Switch 15 Terminal B                                                                                                            |

| B9         | SW16B               | SW16B               | Analog Switch 16 Terminal B                                                                                                            |

| B10        | SW17B               | SW17B               | Analog Switch 17 Terminal B                                                                                                            |

| B11        | SW18B               | SW18B               | Analog Switch 18 Terminal B                                                                                                            |

| B12        | SW19B               | SW19B               | Analog Switch 19 Terminal B                                                                                                            |

| B13        | SW20B               | SW20B               | Analog Switch 20 Terminal B                                                                                                            |

| B14        | SW21B               | SW21B               | Analog Switch 21 Terminal B                                                                                                            |

| C1         | LE/EN               | LE/EN               | Latch Enable Logic Input, Low Active when in Individual Switching mode;<br>Enable Logic Input when in Bank Switching mode              |

| C2         | MODE                | MODE                | Logic Input to decide the Switching mode; L = Bank Switching,<br>H = Individual Switching                                              |

| C13, C14   | NC                  | R <sub>GND</sub>    | No Connect/Ground for Bleed Resistor                                                                                                   |

| D1         | D <sub>IN</sub> /AB | D <sub>IN</sub> /AB | Data in Logic Input when in Individual Switching mode; Logic Input to select Even SWs Bank or Odd SWs Bank when in Bank Switching mode |

| D2         | STBY                | STBY                | Logic Input for Standby State; L = Standby mode (default),<br>H = Normal Operation                                                     |

| D13, D14   | V <sub>DD</sub>     | V <sub>DD</sub>     | Positive Supply Voltage                                                                                                                |

| E1         | DGND                | DGND                | Digital Ground                                                                                                                         |

| E2         | V <sub>DD</sub>     | V <sub>DD</sub>     | Positive Supply Voltage                                                                                                                |

| E5-E10     | GND                 | GND                 | Ground                                                                                                                                 |

| E13, E14   | V <sub>SS</sub>     | V <sub>SS</sub>     | Negative Supply Voltage                                                                                                                |

### TABLE 2-1:PIN FUNCTION TABLE

### TABLE 2-1: PIN FUNCTION TABLE (CONTINUED)

|            | Syr             | nbol              |                                      |

|------------|-----------------|-------------------|--------------------------------------|

| Pin Number | HV2803          | HV2903,<br>HV2904 | Description                          |

| F1         | V <sub>SS</sub> | V <sub>SS</sub>   | Negative Supply Voltage              |

| F2         | V <sub>DD</sub> | V <sub>DD</sub>   | Positive Supply Voltage              |

| F5-F10     | GND             | GND               | Ground                               |

| F13        | SW22B           | SW22B             | Analog Switch 22 Terminal B          |

| F14        | SW22A           | SW22A             | Analog Switch 22 Terminal A          |

| G1         | SW9A            | SW9A              | Analog Switch 9 Terminal A           |

| G2         | SW9B            | SW9B              | Analog Switch 9 Terminal B           |

| G5-G10     | GND             | GND               | Ground                               |

| G13        | SW23B           | SW23B             | Analog Switch 23 Terminal B          |

| G14        | SW23A           | SW23A             | Analog Switch 23 Terminal A          |

| H1         | SW8A            | SW8A              | Analog Switch 8 Terminal A           |

| H2         | SW8B            | SW8B              | Analog Switch 8 Terminal B           |

| H5-H10     | GND             | GND               | Ground                               |

| H13        | SW24B           | SW24B             | Analog Switch 24 Terminal B          |

| H14        | SW24A           | SW24A             | Analog Switch 24 Terminal A          |

| J1         | SW7A            | SW7A              | Analog Switch 7 Terminal A           |

| J2         | SW7B            | SW7B              | Analog Switch 7 Terminal B           |

| J5-J10     | GND             | GND               | Ground                               |

| J13        | SW25B           | SW25B             | Analog Switch 25 Terminal B          |

| J14        | SW25A           | SW25A             | Analog Switch 25 Terminal A          |

| K1         | SW6A            | SW6A              | Analog Switch 6 Terminal A           |

| K2         | SW6B            | SW6B              | Analog Switch 6 Terminal B           |

| K5-K10     | GND             | GND               | Ground                               |

| K13, K14   | NC              | R <sub>GND</sub>  | No Connect/Ground for Bleed Resistor |

| L1, L2     | V <sub>SS</sub> | V <sub>SS</sub>   | Negative Supply Voltage              |

| L13, L14   | V <sub>SS</sub> | V <sub>SS</sub>   | Negative Supply Voltage              |

| M1, M2     | V <sub>DD</sub> | V <sub>DD</sub>   | Positive Supply Voltage              |

| M13, M14   | V <sub>DD</sub> | V <sub>DD</sub>   | Positive Supply Voltage              |

| N1, N2     | NC              | R <sub>GND</sub>  | No Connect/Ground for Bleed Resistor |

| N3         | SW5B            | SW5B              | Analog Switch 5 Terminal B           |

| N4         | SW4B            | SW4B              | Analog Switch 4 Terminal B           |

| N5         | SW3B            | SW3B              | Analog Switch 3 Terminal B           |

| N6         | SW2B            | SW2B              | Analog Switch 2 Terminal B           |

| N7         | SW1B            | SW1B              | Analog Switch 1 Terminal B           |

| N8         | SW0B            | SW0B              | Analog Switch 0 Terminal B           |

| N9         | SW31B           | SW31B             | Analog Switch 31 Terminal B          |

| N10        | SW30B           | SW30B             | Analog Switch 30 Terminal B          |

| N11        | SW29B           | SW29B             | Analog Switch 29 Terminal B          |

| N12        | SW28B           | SW28B             | Analog Switch 28 Terminal B          |

| N13        | SW27B           | SW27B             | Analog Switch 27 Terminal B          |

| N14        | SW26B           | SW26B             | Analog Switch 26 Terminal B          |

|            | Syn    | nbol              |                                      |  |  |  |  |  |  |

|------------|--------|-------------------|--------------------------------------|--|--|--|--|--|--|

| Pin Number | HV2803 | HV2903,<br>HV2904 | Description                          |  |  |  |  |  |  |

| P1, P2     | NC     | R <sub>GND</sub>  | No Connect/Ground for Bleed Resistor |  |  |  |  |  |  |

| P3         | SW5A   | SW5A              | Analog Switch 5 Terminal A           |  |  |  |  |  |  |

| P4         | SW4A   | SW4A              | Analog Switch 4 Terminal A           |  |  |  |  |  |  |

| P5         | SW3A   | SW3A              | Analog Switch 3 Terminal A           |  |  |  |  |  |  |

| P6         | SW2A   | SW2A              | Analog Switch 2 Terminal A           |  |  |  |  |  |  |

| P7         | SW1A   | SW1A              | Analog Switch 1 Terminal A           |  |  |  |  |  |  |

| P8         | SW0A   | SW0A              | Analog Switch 0 Terminal A           |  |  |  |  |  |  |

| P9         | SW31A  | SW31A             | Analog Switch 31 Terminal A          |  |  |  |  |  |  |

| P10        | SW30A  | SW30A             | Analog Switch 30 Terminal A          |  |  |  |  |  |  |

| P11        | SW29A  | SW29A             | Analog Switch 29 Terminal A          |  |  |  |  |  |  |

| P12        | SW28A  | SW28A             | Analog Switch 28 Terminal A          |  |  |  |  |  |  |

| P13        | SW27A  | SW27A             | Analog Switch 27 Terminal A          |  |  |  |  |  |  |

| P14        | SW26A  | SW26A             | Analog Switch 26 Terminal A          |  |  |  |  |  |  |

TABLE 2-1: PIN FUNCTION TABLE (CONTINUED)

### 3.0 TEST CIRCUIT EXAMPLES

This section details a few examples of test circuits.

FIGURE 3-1: Switch-Off Leakage per Switch.

FIGURE 3-2:

Switch-Off Bias per Switch.

FIGURE 3-4: T

### 4.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

FIGURE 4-1:

R<sub>ONS</sub> at 5 mA vs. V<sub>DD</sub>/V<sub>SS.</sub>

FIGURE 4-2: I<sub>DD</sub>/I<sub>SS</sub> vs. Switching Frequency.

I<sub>DDS</sub>/I<sub>SSS</sub> vs. Temperature.

FIGURE 4-5: I<sub>LLQ</sub>/I<sub>LLS</sub> vs. Temperature.

Note: Unless otherwise indicated, V\_{DD} = 6.0V, V\_{SS} = -6.0V, V\_{LL} = 3.3V, T\_{AMB} = +25^{\circ}C.

#### 5.0 DETAILED DESCRIPTION AND **APPLICATION INFORMATION**

#### 5.1 **Device Overview**

The HV2803/HV2903/HV2904 devices are low harmonic distortion, low charge injection, 32-channel, high-voltage analog switches, which do not require high-voltage supplies.

The devices require no high-voltage supplies, only ±6V or ±5V low-voltage supplies. However, all of the analog switches can transmit ±100V high-voltage pulses with typical 10 $\Omega$  on-resistance and 50 MHz bandwidth for small-signals.

The HV2803/HV2903/HV2904 devices are distinguished by bleed resistors that eliminate voltage build-up in capacitance loads, such as piezoelectric transducers. The devices have two digital logics and controls for two Switch Control modes: Individual Switching mode and Bank Switching mode.

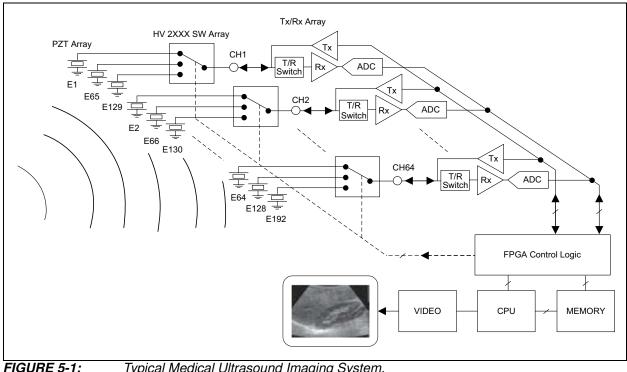

Figure 5-1 shows a typical medical ultrasound imaging system, comprising 64 channels of transmit pulsers, 64 channels of receivers (LNA and ADC) and 64 channels of T/R switches, connecting to 192 elements of an ultrasound probe via a HV2XXX high-voltage analog switch array.

Typical Medical Ultrasound Imaging System.

## 5.2 Individual Switching Mode and Bank Switching Mode

The HV2803/HV2903/HV2904 devices have two logic circuitries that support two Switching modes determined by the MODE pin logic input. One mode is the Individual Switching mode and the other mode is the Bank Switching mode. When the MODE pin is high, the

devices operate in Individual Switching mode and can control 32-channel SPST switches individually through a digital serial interface. When the MODE pin is low, they operate in Bank Switching mode, which works as a 16PDT switch for probe selection. Table 5-1 shows the functional difference of the logic pins in the two modes. When the MODE input is changed from low-to-high, all the shift registers are reset to zero.

|                    | LOCIC DING AT INDIVIDUAL SWITCHING VS. DANK SWITCHING |

|--------------------|-------------------------------------------------------|

| <b>TABLE 5-1</b> : | LOGIC PINS AT INDIVIDUAL SWITCHING VS. BANK SWITCHING |

| Pin Name            | Individu         | al Switching Mode (MODE = H)                       | Bank Switching Mode (MODE = L)                  |                                                                                                     |  |

|---------------------|------------------|----------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

|                     | Function         | Description                                        | Function                                        | Description                                                                                         |  |

| STBY                | STBY             | L = Standby mode (default)<br>H = Normal operation | STBY                                            | L = Standby mode (default)<br>H = Normal operation                                                  |  |

| D <sub>IN</sub> /AB | D <sub>IN</sub>  | Data in logic input                                | A/B                                             | Logic input to select on bank<br>H = Even SWs on and Odd SWs off<br>L = Even SWs off and Odd SWs on |  |

| LE/EN               | LE               | Latch enable logic input                           | EN                                              | Logic input for enable/disable bank switch<br>H = Enable<br>L = Disable (all SWs off)               |  |

| CLR                 | CLR              | Latch clear logic input                            | GND                                             | Should connect to GND                                                                               |  |

| CLK                 | CLK              | Clock logic input for shift register               | ut for shift register GND Should connect to GND |                                                                                                     |  |

| D <sub>OUT</sub>    | D <sub>OUT</sub> | Data out logic output                              | gic output high Z High-Impedance                |                                                                                                     |  |

### 5.3 Individual Switching Mode Logic Input Timing

When the MODE pin logic input is high, the HV2803/HV2903/HV2904 devices operate in the Individual Switching mode. The HV2803/HV2903/HV2904 devices have a digital serial interface consisting of Data In ( $D_{IN}$ /AB), Clock (CLK), Data Out ( $D_{OUT}$ ), Latch Enable (LE/EN) and Clear (CLR) for the Individual Switching mode. The digital circuits are supplied by V<sub>11</sub>. The serial clock frequency is up to 66 MHz.

The switch state configuration data is shifted into the shift registers on the rising edge (low-to-high transition) of the clock. The Switch Configuration bit of SW31 is shifted in first and the Configuration bit of SW0 is shifted in last. To change all the switch states at the same time, the Latch Enable Input (LE/EN) should remain high while the 32-bit Data In signal is shifted into the 32-bit register. After the valid 32-bit data completes shifting into the shift registers, the high-to-low transition of the LE/EN signal transfers the contents of the shift registers into the latches. Finally, setting the LE/EN high again, allows all the latches to keep the current state while new data can now be shifted into the shift registers without disturbing the latches.

It is recommended to change all the latch states at the same time through this method to avoid possible clock feed through noise (see Figure 5-2 for details).

When the CLR input is set high, it resets the data of all 32 latches to low. Consequently, all the high-voltage switches are set to an OFF state. However, the CLR signal does not affect the contents of the shift register, so the shift register can operate independently of the CLR signal. Therefore, when the CLR input is low, the shift register still retains the previous data.

FIGURE 5-2: Latch Enable Timing Diagram.

### 5.4 Multiple Devices Connection in Individual Switching Mode

The serial input interface of the HV2803/HV2903/ HV2904 devices allows multiple devices to daisy-chain together. In this configuration, the  $D_{OUT}$  pin of a device is connected to the  $D_{IN}/AB$  pin of the subsequent device, and so forth. The last  $D_{OUT}$  pin of the daisy-chained HV2803/HV2903/HV2904 devices can be either floating or fed back to an FPGA (Field Programmable Gate Array) to check the previously stored shift register data.

To control all the high-voltage analog switch states in daisy-chained N devices, N-times 32 clocks and N-times 32 bits of data are shifted into the shift registers, while LE/EN remains high and CLR remains low. After all the data finishes shifting in, one single negative pulse of the LE/EN pin transfers the data from all shift registers to all the latches simultaneously. Consequently, all N-times 32 high-voltage analog switches change states simultaneously.

### 5.5 Bank Switching Mode

When the MODE pin logic input is low, the HV2803/HV2903/HV2904 devices operate in the Bank Switching mode.

The  $D_{IN}/A\overline{B}$  pin is used as the A/B input and the  $\overline{LE}/EN$  pin is used as the EN input in the Bank Switching mode. The CLR and CLK logic inputs are not used and are recommended to drive logic low. The  $D_{OUT}$  pin is in a high-impedance state. See Table 1-1 for details on Bank Switching mode.

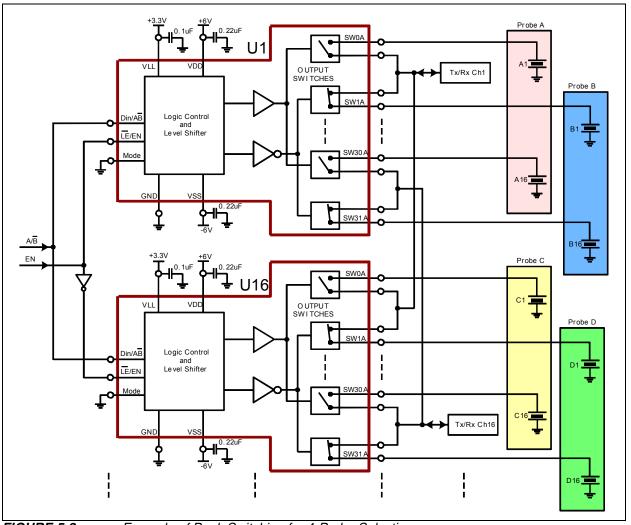

The EN function allows the HV2803/HV2903/HV2904 devices to be configured as either a 2:1 or 4:1 multiplexer/ demultiplexer. The HV2803/HV2903/HV2904 devices can replace the relay in a medical ultrasound system. Compared to the mechanical relay, the HV2803/HV2903/ HV2904 devices are faster switching, less power consuming and no audible noise emitting switches. Figure 5-3 shows an application example of a 4-probe selection configuration using the HV2803/HV2903/ HV2904 Bank Switching mode. Please note that the MODE pin is connected to GND.

FIGURE 5-3: Example of Bank Switching for 4-Probe Selection.

### 5.6 Standby Mode

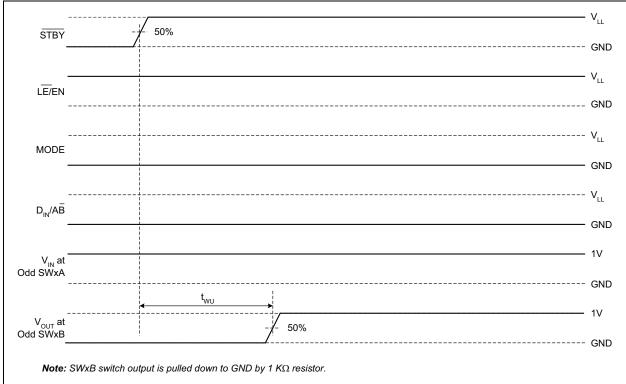

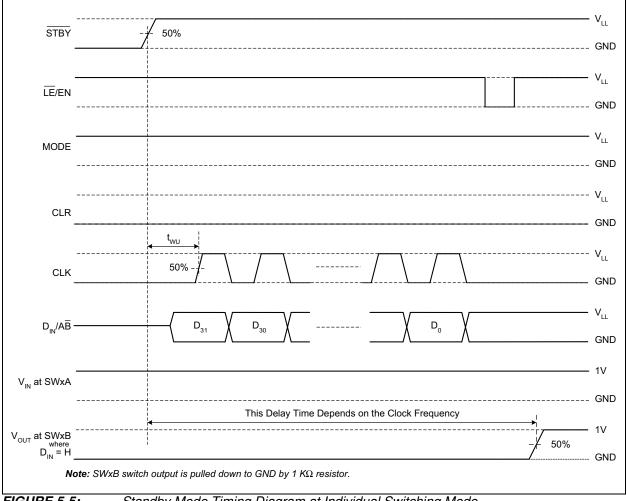

To reduce the current consumption during the Idle time, the HV2803/HV2903/HV2904 devices include Standby mode. If the  $\overline{STBY}$  logic input is low, the device is in Standby mode to reduce the current consumption by shutting down most of the circuity. If the  $\overline{STBY}$  logic input is changed from low to high, the devices are out of Standby mode and the digital logic

circuitry starts operating normally after the wake-up time,  $t_{WU}$ . Figure 5-4 and Figure 5-5 show the Standby mode timing diagram at Bank Switching mode and Individual Switching mode, respectively. The default logic condition is the standby state. The STBY logic input has the highest priority in logic control. See Table 1-1 for details.

FIGURE 5-4: Standby Mode Timing Diagram at Bank Switching Mode.

Standby Mode Timing Diagram at Individual Switching Mode. FIGURE 5-5:

### 5.7 Power-up Sequence

The HV2803/HV2903/HV2904 devices have a recommended power-up sequence. It is recommended that  $V_{SS}$  and  $V_{DD}$  are powered up first, and then  $V_{LL}$  is powered up. The power-down sequence is in reverse order of the power-up sequence.

During the power-up/down period, all the analog switch inputs should be within  $V_{\text{DD}}$  and  $V_{\text{SS}}$  or floating.

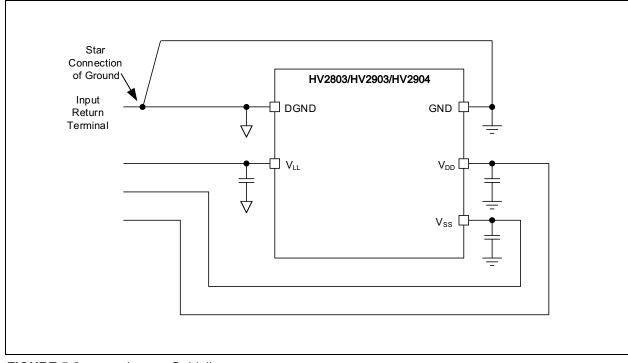

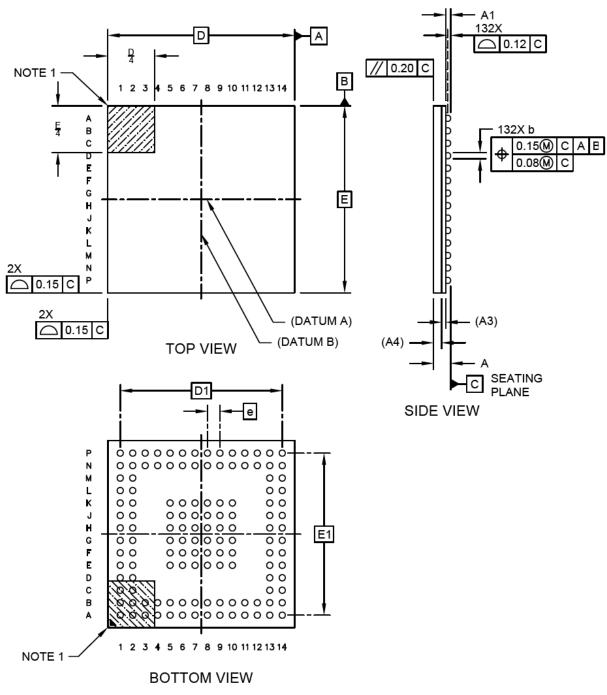

### 5.8 Layout Considerations

The HV2803/HV2903/HV2904 devices have two separate ground connections. DGND is the ground connection for digital circuitry, and GND is the ground

connection for analog switches and substrate. It is important to have a good PCB layout which minimizes noise and ground bounce. It is recommended that two separate ground planes be used in the PCB and those ground planes be connected together at the return terminal of the input power line, as shown in Figure 5-6. It is recommended that 0.1  $\mu$ F or larger ceramic decoupling capacitors, with low-ESR (Equivalent Series Resistance) and appropriate voltage ratings, be connected between ground and power supplies, as shown in Figure 5-6. The decoupling capacitor of V<sub>LL</sub> should be connected to DGND, whereas the decoupling capacitors of V<sub>DD</sub> and V<sub>SS</sub> should be connected to the device.

### 6.0 PACKAGING INFORMATION

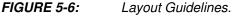

### 6.1 Package Marking Information

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@8<br>*                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e8))<br>can be found on the outer packaging for this package. |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         | In the event the full Microchip part number cannot be marked on one lin<br>be carried over to the next line, thus limiting the number of a<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |  |  |

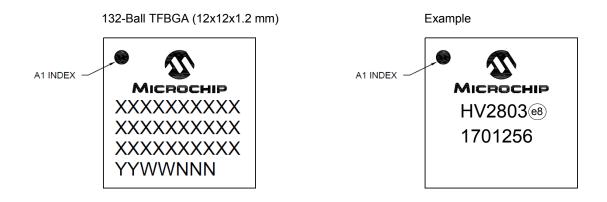

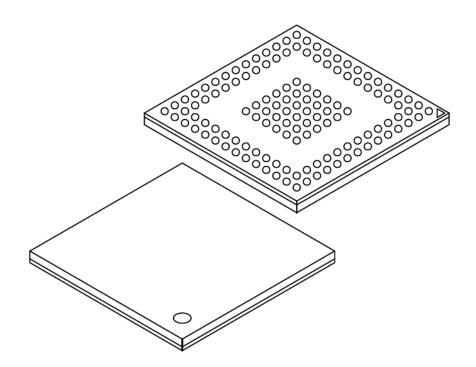

### 132-Ball Thin Fine Pitch Ball Grid Array (AHA) - 12x12x1.2mm Body [TFBGA]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-1193 Rev B Sheet 1 of 2

#### 132-Ball Thin Fine Pitch Ball Grid Array (AHA) - 12x12x1.2mm Body [TFBGA]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |      |      |  |  |

|--------------------------|-------------|-----------|------|------|--|--|

| Dimension                | n Limits    | MIN       | NOM  | MAX  |  |  |

| Number of Terminals      | Ν           | 132       |      |      |  |  |

| Pitch                    | е           | 0.80 BSC  |      |      |  |  |

| Overall Height           | Α           | -         | -    | 1.20 |  |  |

| Standoff                 | A1          | 0.27      | 0.32 | 0.37 |  |  |

| Substrate Thickness      | A2          | 0.26 REF  |      |      |  |  |

| Mold Cap Thickness       | A4          | 0.53 REF  |      |      |  |  |

| Overall Length           | D           | 12.00 BSC |      |      |  |  |

| Overall Terminal Centers | D1          | 10.40 BSC |      |      |  |  |

| Overall Width            | E           | 12.00 BSC |      |      |  |  |

| Overall Terminal Centers | E1          | 10.40 BSC |      |      |  |  |

| Terminal Diameter        | b           | 0.35      | 0.40 | 0.45 |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-1193 Rev B Sheet 2 of 2