Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **High-Voltage Ring Generator**

#### **Features**

- ▶ 105Vrms ring signal

- Output overcurrent protection

- 5.0V CMOS logic control

- Logic enable/disable to save power

- Adjustable deadband in single-control mode

- Power-on reset

- Fault output for problem detection

### **Applications**

- Line access cards

- Set-top/Street box

### **General Description**

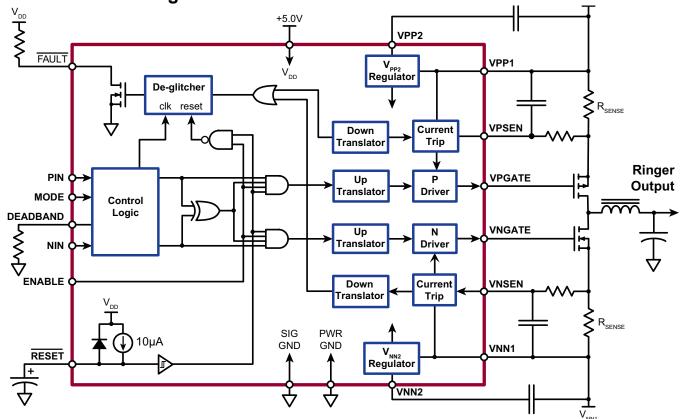

The Supertex HV430 is a high voltage PWM ring generator integrated circuit. The high voltage outputs,  $V_{PGATE}$  and  $V_{NGATE}$ , are used to drive the gates of external high voltage N-channel and P-channel MOSFETs in a push-pull configuration. Overcurrent protection is implemented for both the P-channel and N-channel MOSFETs. External sense resistors set the over-current trip point.

The RESET input functions as a power-on reset when connected to an external capacitor. The FAULT output indicates an overcurrent condition and is cleared after 4 consecutive cycles with no overcurrent condition. A logic low on RESET or ENABLE clears the FAULT output. It is active-low and open-drain to allow wire OR'ing of multiple drivers.

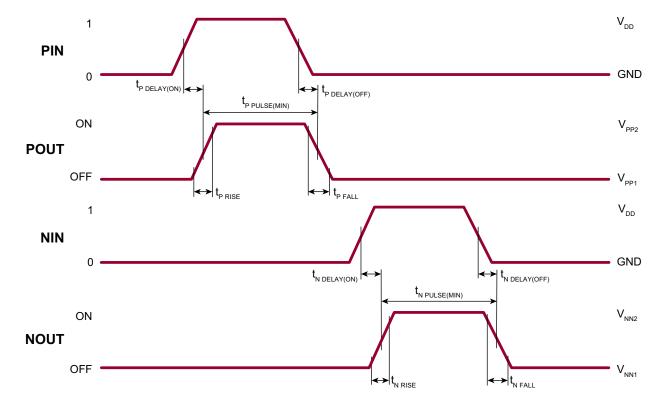

$P_{\text{GATE}}$  and  $N_{\text{GATE}}$  are controlled independently by logic inputs  $P_{\text{IN}}$  and  $N_{\text{IN}}$  when the MODE pin is at logic high. A logic high on  $P_{\text{IN}}$  will turn on the external P-channel MOSFET. Similarly, a logic high on  $N_{\text{IN}}$  will turn on the external N-channel MOSFET. Lockout circuitry prevents the N and P switches from turning on simultaneously. A pulse width limiter restricts pulse widths to no less than 100 - 200ns.

For applications where a single control input is desired, the MODE pin should be connected to SGND. The PWM control signal is then input to the  $N_{\rm IN}$  pin. A user-adjustable deadband in the control logic ensures break-before-make on the outputs, thus avoiding cross conduction on the high voltage output during switching. A logic high on  $N_{\rm IN}$  will turn the external P-Channel MOSFET on and the N-Channel off, and vice versa. The IC can be powered down by applying a logic low on the ENABLE pin, placing both external MOSFETs in the off state.

### **Functional Block Diagram**

### **Ordering Information**

| Part Number | Package Option | Packing   |

|-------------|----------------|-----------|

| HV430WG-G   | 20-Lead SOW    | 1000/Reel |

<sup>-</sup>G denotes a lead (Pb)-free / RoHS compliant package

### **Absolute Maximum Ratings**

| Parameter                                            | Value           |

|------------------------------------------------------|-----------------|

| $V_{PP1}$ - $V_{NN1}$ , power supply voltage         | +340V           |

| V <sub>PP1</sub> , positive high voltage supply      | +220V           |

| V <sub>PP2</sub> , positive gate voltage supply      | +220V           |

| $V_{_{\mathrm{NN1}}}$ , negative high voltage supply | -220V           |

| $V_{_{NN2}}$ , negative gate voltage supply          | -220V           |

| V <sub>DD</sub> , logic supply                       | +7.5V           |

| Operating temperature range                          | -40°C to +85°C  |

| Storage temperature range                            | -65°C to +150°C |

| Power dissipation                                    | 600mW           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Pin Configuration**

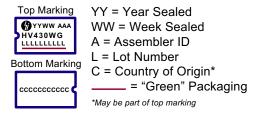

### **Product Marking**

Package may or may not include the following marks: Si or 🌎

20-Lead SOW

## **Typical Thermal Resistance**

| Package     | $oldsymbol{	heta}_{j_{oldsymbol{a}}}$ |

|-------------|---------------------------------------|

| 20-Lead SOW | 66°C/W                                |

# **Electrical Characteristics** (Over operating supply voltage unless otherwise specified. $T_A$ = -40°C to +85°C)

| Sym               | Parameter                          | Parameter Min Typ     |     | Max  | Units | Conditions                                                           |  |  |  |  |  |

|-------------------|------------------------------------|-----------------------|-----|------|-------|----------------------------------------------------------------------|--|--|--|--|--|

| Externa           | External Supplies                  |                       |     |      |       |                                                                      |  |  |  |  |  |

| V <sub>PP1</sub>  | High voltage positive supply       | 50                    | -   | 200  | V     |                                                                      |  |  |  |  |  |

| I <sub>PP1Q</sub> | V <sub>PP1</sub> quiescent current | -                     | 250 | 500  | μA    | $P_{IN} = N_{IN} = 0V$                                               |  |  |  |  |  |

| I <sub>PP1</sub>  | V <sub>PP1</sub> operating current | -                     | -   | 2.0  | mA    | No load, V <sub>OUTP</sub> and V <sub>OUTN</sub> switching at 100KHz |  |  |  |  |  |

| V <sub>NN1</sub>  | High voltage negative supply       | V <sub>PP1</sub> -325 | -   | -50  | V     |                                                                      |  |  |  |  |  |

| I <sub>NN1Q</sub> | V <sub>NN1</sub> quiescent current | -                     | 250 | 500  | μA    | $P_{IN} = N_{IN} = 0V, R_{DB} = 18k\Omega$                           |  |  |  |  |  |

| I <sub>NN1</sub>  | V <sub>NN1</sub> operating current | -                     | -   | 1.0  | mA    | No load, V <sub>OUTP</sub> and V <sub>OUTN</sub> switching at 100KHz |  |  |  |  |  |

| V <sub>DD</sub>   | Logic supply voltage               | 4.50                  | -   | 5.50 | V     |                                                                      |  |  |  |  |  |

| I <sub>DDQ</sub>  | V <sub>DD</sub> quiescent current  | -                     | 300 | 400  | μA    | $P_{IN} = N_{IN} = 0V, R_{DB} = 18k\Omega$                           |  |  |  |  |  |

| I <sub>DD</sub>   | V <sub>DD</sub> operating current  | -                     | -   | 1.0  | mA    | $P_{IN} = N_{IN} = 100KHz,$ $R_{DB} = 18k\Omega$                     |  |  |  |  |  |

# **Electrical Characteristics** (cont.) (Over operating supply voltage unless otherwise specified. $T_A = -40$ °C to +85°C)

| Sym                   | Parameter                                                   | Min                    | Тур                   | Max                    | Units | Conditions                                        |

|-----------------------|-------------------------------------------------------------|------------------------|-----------------------|------------------------|-------|---------------------------------------------------|

| Internal              | Supplies                                                    | '                      |                       | •                      | '     | •                                                 |

| V <sub>PP2</sub>      | Positive linear regulator output voltage                    | V <sub>PP1</sub> -16   | -                     | V <sub>PP1</sub> -10   | V     |                                                   |

| $V_{_{\mathrm{NN2}}}$ | Negative linear regulator output voltage                    | V <sub>PP1</sub> +10   | -                     | V <sub>PP1</sub> +14   | V     |                                                   |

| Positive              | High Voltage Output                                         |                        |                       |                        |       |                                                   |

| $V_{PGATE}$           | Output voltage swing                                        | V <sub>PP2</sub>       | -                     | V <sub>PP1</sub>       | V     | No load on V <sub>PGATE</sub>                     |

| R <sub>SOURCEP</sub>  | V <sub>PGATE</sub> source resistance                        | -                      | -                     | 12.5                   | Ω     | I <sub>OUT</sub> = 80mA                           |

| $R_{\text{SINKP}}$    | V <sub>PGATE</sub> sink resistance                          | -                      | -                     | 12.5                   | Ω     | I <sub>OUT</sub> = -80mA                          |

| t <sub>RISEP</sub>    | V <sub>PGATE</sub> rise time                                | -                      | -                     | 50                     | ns    | C <sub>LOAD</sub> = 1.4nF                         |

| t <sub>FALLP</sub>    | V <sub>PGATE</sub> fall time                                | -                      | -                     | 50                     | ns    | C <sub>LOAD</sub> = 1.4nF                         |

| $t_{\text{PWP(MIN)}}$ | V <sub>PGATE</sub> minimum pulse width (internally limited) | 100                    | 150                   | 200                    | ns    |                                                   |

| t <sub>DELAYP</sub>   | P <sub>IN</sub> to P <sub>GATE</sub> delay time             | -                      | -                     | 300                    | ns    | Mode = 1                                          |

| V <sub>PSEN</sub>     | V <sub>PGATE</sub> current sense voltage                    | V <sub>PP1</sub> -0.85 | V <sub>PP1</sub> -1.0 | V <sub>PP1</sub> -1.15 | V     |                                                   |

| t <sub>SHORTP</sub>   | V <sub>PGATE</sub> current sense off time                   | -                      | -                     | 150                    | ns    |                                                   |

|                       | e High Voltage Output                                       |                        |                       | 1                      |       |                                                   |

| V <sub>NGATE</sub>    | Output voltage swing                                        | V <sub>NN2</sub>       | -                     | V <sub>NN1</sub>       | V     | No load on V <sub>NGATE</sub>                     |

| R <sub>SOURCEN</sub>  | V <sub>NGATE</sub> source resistance                        | -                      | -                     | 15.0                   | Ω     | I <sub>OUT</sub> = 80mA                           |

| R <sub>SINKN</sub>    | V <sub>NGATE</sub> sink resistance                          | -                      | -                     | 15.0                   | Ω     | I <sub>OUT</sub> = 80mA                           |

| t <sub>RISEN</sub>    | V <sub>NGATE</sub> rise time                                | -                      | -                     | 50                     | ns    | C <sub>LOAD</sub> = 1.4nF                         |

| t <sub>FALLN</sub>    | V <sub>NGATE</sub> fall time                                | -                      | -                     | 50                     | ns    | C <sub>LOAD</sub> = 1.4nF                         |

| t <sub>PWN(MIN)</sub> | V <sub>NGATE</sub> minimum pulse width (internally limited) | 100                    | 150                   | 200                    | ns    |                                                   |

| t <sub>DELAYN</sub>   | N <sub>IN</sub> to N <sub>GATE</sub> delay time             | -                      | -                     | 300                    | ns    | Mode = 1                                          |

| V <sub>NSEN</sub>     | V <sub>NGATE</sub> current sense voltage                    | V <sub>NN1</sub> +0.85 | V <sub>NN1</sub> +1.0 | V <sub>NN1</sub> +1.15 | V     |                                                   |

| t <sub>shortn</sub>   | V <sub>NGATE</sub> current sense off time                   | -                      | -                     | 150                    | ns    |                                                   |

|                       | Circuitry                                                   |                        |                       | 1                      |       |                                                   |

| V <sub>IL</sub>       | Logic input low voltage                                     | 0                      | -                     | 0.60                   | V     | V <sub>DD</sub> = 5.0V                            |

| V <sub>IH</sub>       | Logic input high voltage                                    | 2.7                    | -                     | 5.0                    | V     | V <sub>DD</sub> = 5.0V                            |

| I <sub>INDN</sub>     | Input pull-down current                                     | 0.5                    | 1.0                   | 5.0                    | μA    | P <sub>IN</sub> , N <sub>IN</sub> , ENABLE        |

| R <sub>UP</sub>       | Input pull-up resistance                                    | 100                    | 200                   | 300                    | ΚΩ    | MODE                                              |

| V <sub>OL</sub>       | Logic output low voltage                                    | -                      | -                     | 0.50                   | V     | V <sub>DD</sub> = 5.0V, I <sub>OUT</sub> = -0.5mA |

| V <sub>OH</sub>       | Logic output high voltage                                   | 4.50                   | -                     | -                      | V     | $V_{DD} = 5.0V, I_{OUT} = +0.5mA$                 |

| V <sub>RST(OFF)</sub> | RESET voltage, device off                                   | 3.2                    | -                     | 3.5                    | V     | V <sub>DD</sub> = 5.0V                            |

| V <sub>RST(ON)</sub>  | RESET voltage, device on                                    | 3.7                    | -                     | 4.0                    | V     | V <sub>DD</sub> = 5.0V                            |

### **Electrical Characteristics** (cont.)(over operating supply voltage unless otherwise specified. $T_A = -40$ °C to +85°C)

| Sym                            | Parameter                                                            | Min | Тур | Max | Units                                   | Conditions                         |

|--------------------------------|----------------------------------------------------------------------|-----|-----|-----|-----------------------------------------|------------------------------------|

| V <sub>RST(HYS)</sub>          | RESET hysteresis voltage                                             | 0.3 | -   | -   | V                                       | V <sub>DD</sub> = 5.0V             |

| I <sub>RESET</sub>             | RESET pull-up current                                                | 7.0 | 10  | 13  | μA                                      | V <sub>RESET</sub> = 0 - 4.5V      |

| t <sub>RST(ON)</sub>           | RESET on delay                                                       | -   | -   | 1.0 | μs                                      |                                    |

| t <sub>RST(ON)</sub>           | RESET off delay                                                      | -   | -   | 1.0 | μs                                      |                                    |

| t <sub>EN(ON)</sub>            | ENABLE on delay                                                      | 50  | 100 | 150 | μs                                      |                                    |

| t <sub>EN(OFF)</sub>           | ENABLE off delay                                                     | -   | -   | 1.0 | μs                                      |                                    |

| t <sub>FLT(HOLD)</sub>         | FAULT hold time                                                      | -   | 4   | -   | N <sub>IN</sub> /P <sub>IN</sub> cycles | ENABLE = 1                         |

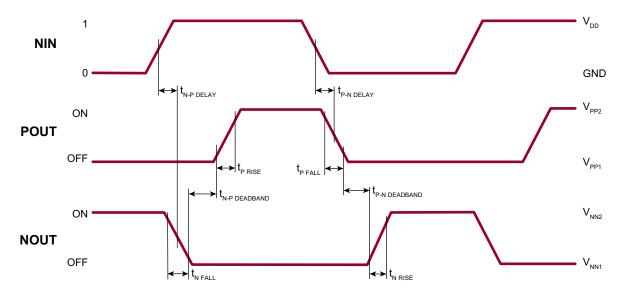

| 4                              | Deadband time                                                        | 35  | 50  | 70  | no                                      | Mode = 0, $R_{DB}$ = 5.6k $\Omega$ |

| t <sub>DB</sub>                | Deadband line                                                        | 105 | 140 | 175 | ns                                      | Mode = 0, $R_{DB}$ = $18k\Omega$   |

| t <sub>DELAY(N-P)</sub>        | N-off to P-on transistion delay                                      | -   | -   | 300 | ns                                      | Mode = 0, $R_{DB}$ < 27k $\Omega$  |

| t <sub>DELAY(P-N)</sub>        | P-off to N-on transistion delay                                      | -   | -   | 300 | ns                                      | Mode = 0, $R_{DB}$ < 27k $\Omega$  |

| $\Delta t_{\text{DELAY(N-P)}}$ | Delay difference: t <sub>delayN(off)</sub> - t <sub>delayP(on)</sub> | -80 | 0   | 80  | ns                                      | Mode = 1                           |

| $\Delta t_{\text{DELAY(P-N)}}$ | Delay difference: t <sub>delayP(off)</sub> - t <sub>delayN(on)</sub> | -80 | 0   | 80  | ns                                      | Mode = 1                           |

# **Truth Table**

|                 | Logic           | Inputs* |    |                           | Output                    |                           |  |  |  |  |

|-----------------|-----------------|---------|----|---------------------------|---------------------------|---------------------------|--|--|--|--|

| N <sub>IN</sub> | P <sub>IN</sub> | Mode    | EN | RESET                     | Externel N-Channel MOSFET | Externel P-Channel MOSFET |  |  |  |  |

| L               | L               | Н       | Н  | >V <sub>RESET(ON)</sub>   | OFF                       | OFF                       |  |  |  |  |

| L               | Н               | Н       | Н  | >V <sub>RESET(ON)</sub>   | OFF                       | ON                        |  |  |  |  |

| Н               | L               | Н       | Н  | >V <sub>RESET(ON)</sub>   | ON                        | OFF                       |  |  |  |  |

| Н               | Н               | Н       | Н  | >V <sub>RESET(ON)</sub>   | OFF                       | OFF                       |  |  |  |  |

| Н               | X               | L       | Н  | >V <sub>RESET(ON)</sub>   | OFF                       | ON                        |  |  |  |  |

| L               | X               | L       | Н  | >V <sub>RESET(ON)</sub>   | ON                        | OFF                       |  |  |  |  |

| Х               | Х               | Х       | L  | X                         | OFF                       | OFF                       |  |  |  |  |

| Х               | Х               | X       | Х  | <v<sub>RESET(OFF)</v<sub> | OFF                       | OFF                       |  |  |  |  |

Note.

<sup>\*</sup> Unused logic inputs should be connected to VDD or GND.

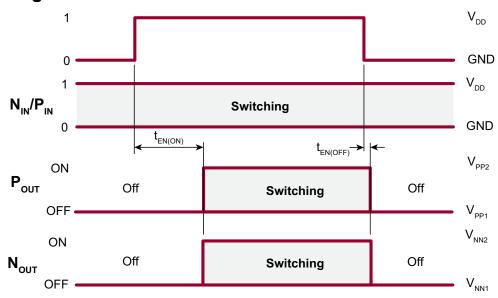

# **Single-Control Mode Timing**

### **Dual-Control Mode Timing**

# **ENABLE Timing**

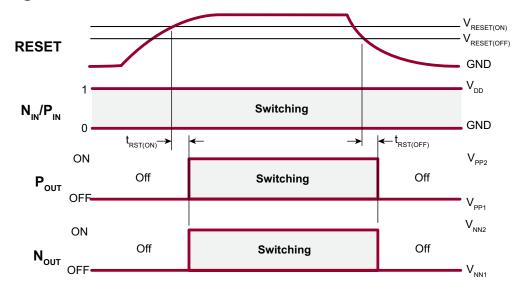

# **RESET Timing**

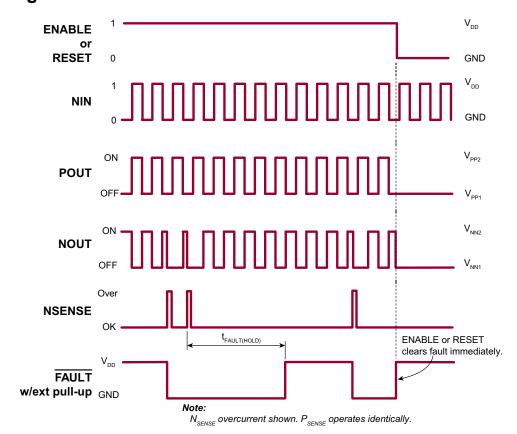

# **FAULT Timing**

# **Pin Description**

|       | Vamo     |                                                                                                                                                                                                                                                       |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin # | Name     | Description                                                                                                                                                                                                                                           |

| 1     | VDD      | Logic supply voltage.                                                                                                                                                                                                                                 |

| 2     | FAULT    | Logic output. Fault is at logic low when either current limit sense pin, VPSEN or VNSEN, is activated. Remains active until overcurrent condition clears or ENABLE = 0 or RESET = 0.                                                                  |

| 3     | MODE     | Logic mode input. 0 = single-control; 1 = dual-control. When MODE is high, NIN and PIN independently control $N_{OUT}$ and $P_{OUT}$ , respectively. When MODE is low, NIN controls both outputs in a complementary manner. (See Truth Table)         |

| 4     | PIN      | Logic control input. When mode is high, logic input high turns on the external high voltage P-channel MOSFET. Internally pulled low.                                                                                                                  |

| 5     | NIN      | Logic control input. When mode is high, logic input high turns on the external high voltage N-channel MOSFET. Internally pulled low.                                                                                                                  |

| 6     | ENABLE   | Logic enable input. Logic high enables IC. Internally pulled low.                                                                                                                                                                                     |

| 7     | RESET    | Power-on reset. A capacitor connected between this pin and ground determines the delay time between application of VDD and when the device outputs are enabled. Low leakage tantalum recommended.                                                     |

| 8     | DEADBAND | A resistor between this pin and ground sets the 'break-before-make' time between output transitions. Applicable only in single-control mode. For minimum deadtime, a $5.6k\Omega$ resistor to ground should be used. For dual-input mode, tie to VDD. |

| 9     | SGND     | Low voltage logic ground.                                                                                                                                                                                                                             |

| 10    | PGND     | High voltage logic ground.                                                                                                                                                                                                                            |

| 11    | VNN2     | Negative gate voltage supply. Generated by an internal linear regulator. A 25V, 100nF capacitor should beconnected between VNN2 and VNN1.                                                                                                             |

| 12    | VNN1     | Negative high voltage supply.                                                                                                                                                                                                                         |

| 13    | VNSEN    | Pulse by pulse over current sensing for N-Channel MOSFET.                                                                                                                                                                                             |

| 14    | VNGATE   | Gate drive for external N-channel MOSFET.                                                                                                                                                                                                             |

| 15    |          |                                                                                                                                                                                                                                                       |

| 16    | N/C      | No connect.                                                                                                                                                                                                                                           |

| 17    | VPGATE   | Gate drive for external P-channel MOSFET.                                                                                                                                                                                                             |

| 18    | VPSEN    | Pulse by pulse over current sensing for P-Channel MOSFET.                                                                                                                                                                                             |

| 19    | VPP1     | Positive high voltage supply.                                                                                                                                                                                                                         |

| 20    | VPP2     | Positive gate voltage supply. Generated by an internal linear regulator. A 25V, 100nF capacitor should beconnected between VPP2 and VPP1.                                                                                                             |

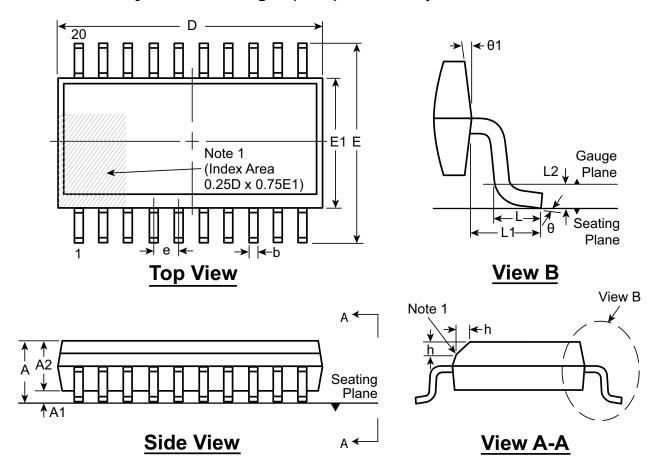

# 20-Lead SOW (Wide Body) Package Outline (WG)

12.80x7.50mm body, 2.65mm height (max), 1.27mm pitch

#### Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo          | ol  | Α     | <b>A</b> 1 | A2    | b    | D      | E      | E1    | е           | h    | L    | L1          | L2          | θ          | θ1         |

|----------------|-----|-------|------------|-------|------|--------|--------|-------|-------------|------|------|-------------|-------------|------------|------------|

|                | MIN | 2.15* | 0.10       | 2.05  | 0.31 | 12.60* | 9.97*  | 7.40* |             | 0.25 | 0.40 |             |             | <b>0</b> ° | <b>5</b> ° |

| Dimension (mm) | NOM | -     | -          | -     | -    | 12.80  | 10.30  | 7.50  | 1.27<br>BSC | -    | -    | 1.40<br>REF | 0.25<br>BSC | -          | -          |

| ()             | MAX | 2.65  | 0.30       | 2.55* | 0.51 | 13.00* | 10.63* | 7.60* |             | 0.75 | 1.27 |             |             | <b>8</b> º | 15°        |

JEDEC Registration MS-013, Variation AC, Issue E, Sep. 2005.

Drawings are not to scale.

Supertex Doc. #: DSPD-20SOWWG, Version D041309.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2014 **Supertex Inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.